All hardware description languages and RTLs contain some sort of generate statement.

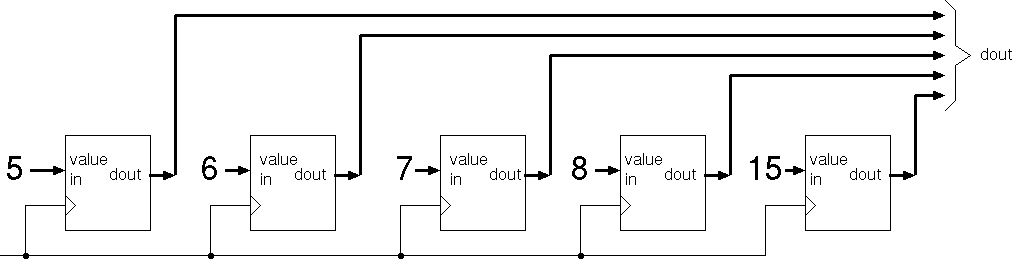

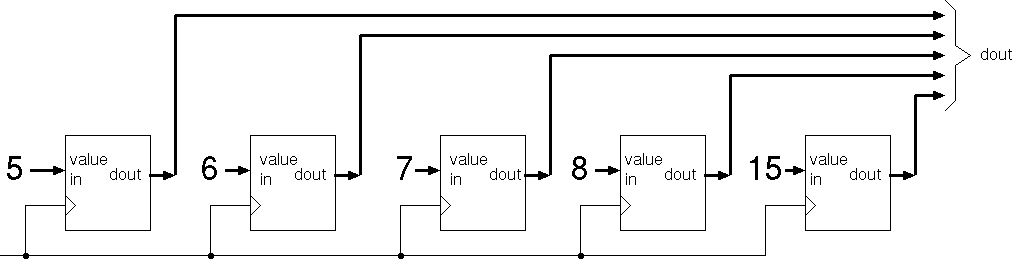

A generate statement is an iterative construct that is executed (elaborated) at compile time to generate multiple instances of a component and its wiring. In the recent Chisel and Bluespec languages, a powerful, higher-order functional language is available, but in SystemVerilog we follow a more mundane style such as:

wire dout[39:0];

reg[3:0] values[0:4] = {5, 6, 7, 8, 15};

generate

genvar i;

for (i=0; i < 5; i++) begin

MUT mut[i] (

.out(dout[i*8+7:i*8]),

.value_in(values[i]),

.clk(clk),

);

end

endgenerate

| 11: (C) 2008-18, DJ Greaves, University of Cambridge, Computer Laboratory. | |