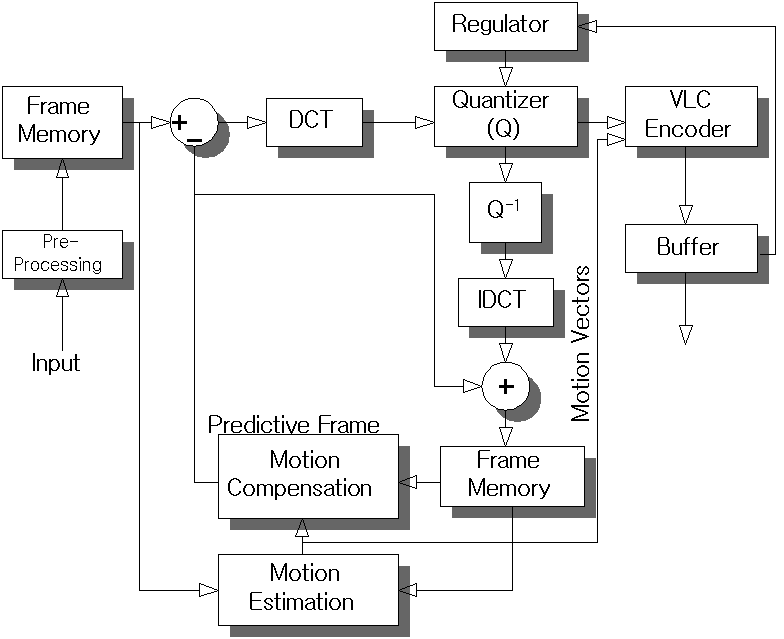

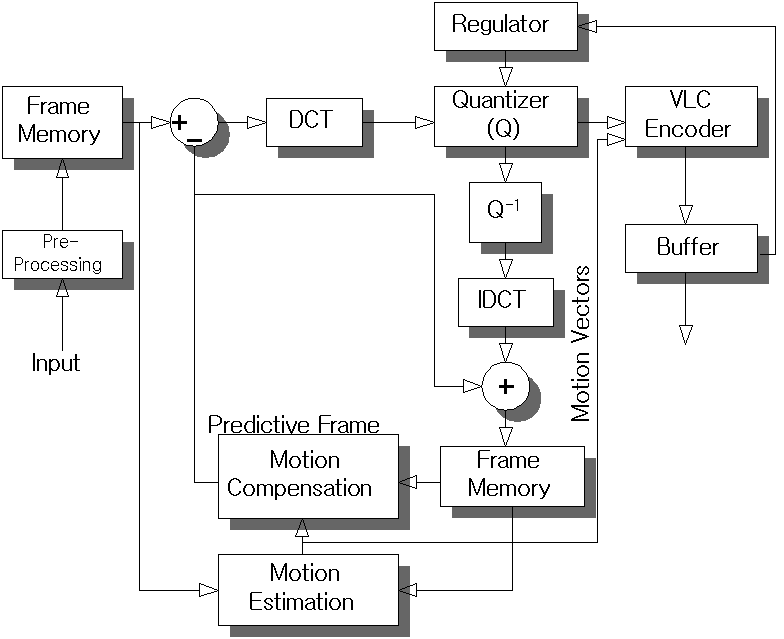

Flow chart for MPEG video compression.

A collection of algorithms and functional requirements must be implemented using one or more pieces of silicon.

Each major piece of silicon contains one or more custom or standard microprocessors.

Some silicon is custom for a high-volume product, some is shared over several product lines and some is third party or standard parts.

The result of the architectural design process is a mapping of the design into physical components. Certain electronic requirements, such as high voltage, microwave radio frequencies and optimum memory bit density are still met with optimised silicon (or GaAs) processes, but today, almost everything is either a `standard part' or else can be mapped onto a single System-on-Chip. Beyond fundamental silicon capabilities, the design partition process must take into account non-technical aspects, such as stability of requirements, design lifetime, ease of reuse, and other market forces such as whether a third party source is required by the target customers.

When designing a sub-system we must choose what to have as hardware, what to have as software and whether custom or standard processors are needed.

When designing the complete SoC we must think about sharing of sub-system load over the chosen processors. .par Estimates of the instruction fetch and data bandwidth for each processor are needed for deciding how many memories to instantiate and which processors will operate out of which memories. .par The envisioned system data flow between sub-systems is another important consideration in terms of how busses should be interconnected or whether a NoC is justified. .par When a SoC is intended for a single target application there is greater certainty about the likely data flow compared with a general purpose chip. Although transistor count does not present a significant design constraint in modern VLSI, hard-wired datapaths are more efficient than switched structures, wiring length and hence energy is minimised when less area is used. A solution providing non-blocking, full crossbar interconnection will generally be over-engineered for all applications.

Energy efficiency is today also often a critical consideration: whether for battery-operation or in a server farm, low-power design principles are applicable and power control mechanisms will affect the design at all levels.

Design Partition: Deciding on the number of processors, number of custom processors, and number of custom hardware blocks.

The system architect must make these decisions. SystemC helps them rapidly explore various possibilities.

Co-design and co-synthesis: two basic methods (can do different parts of the chip differently):

Co-synthesis is still not in mainstream use (2018).

Example algorithm: MPEG compression:

| 1: (C) 2008-18, DJ Greaves, University of Cambridge, Computer Laboratory. |