HOME

UP

PREV

FURTHER NOTES

NEXT (Circuit Switching)

FPGA - Field Programmable Gate Array

About 25 to 40 percent of chip sale revenue now comes from field-programmable logic devices. These are chips that can be programmed electronically on the user's site to provide the desired function.

PALs and CPLDs are forms of programmable logic that are fast and small. But the most important form today is the FPGA.

Recall the Xilinx/Altera FPGA parts used in the Part IB E+A classes.

Field-programmable devices may be volatile (need programming every

time after power up), reprogrammable or one-time programmable. This

depends on how the programming information is stored inside the

devices, which can be in RAM cells or in any of the ways used for ROM,

such as electrostatic charge storage (e.g. FLASH).

Except for niche applications (such as GaAs instead of Si), FPGAs are now always used instead of masked gate arrays and are starting to kill ASCIs (see link above).

Example: The part Ib practical classes use FPGAs from Altera:

»ECAD and Architecture Practical Classes

Summary data for a Virtex 5 Xilinx FPGA:

| Part number | XC5VLX110T-2FFG1136C |

| Vendor | Xilinx Inc |

| Category | Integrated Circuits (ICs) |

| Number of Gates | 110000 |

| Number of I /O | 640 |

| Number of Logic Blocks/Elements | 8640 |

| Package / Case | 1136-FCBGA |

| Operating Temperature | 0C ~ 85C |

| Voltage - Supply | 1.14 V ~ 3.45 V |

Circa 2009, 65 nm technology, 6-input LUT, 64 bit D/P RAMs.

Today Xilinx has the Virtex 7 series that includes the Zync SoC (of which more later)

»wikipedia: Virtex FPGA

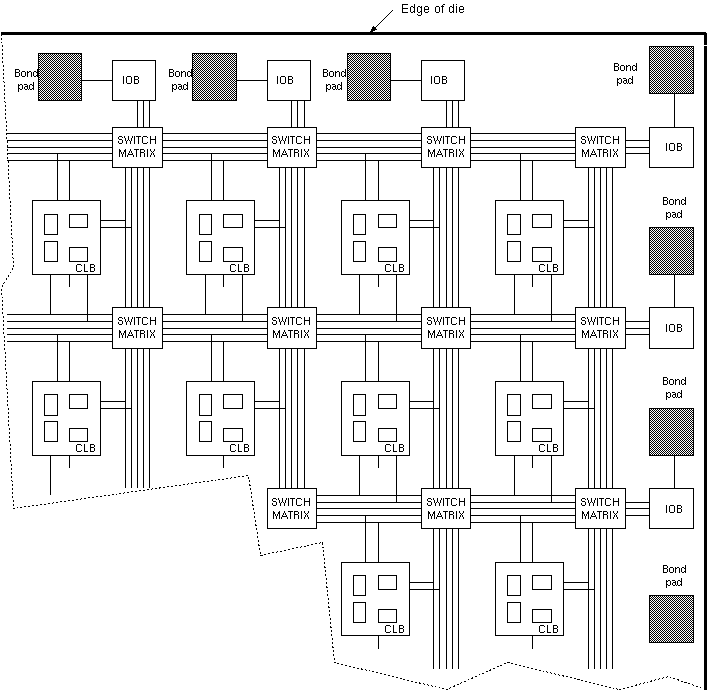

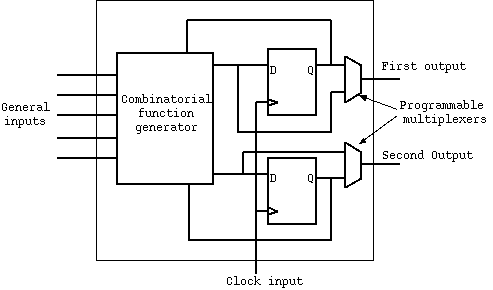

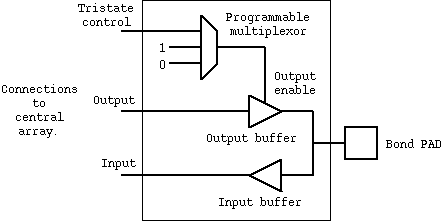

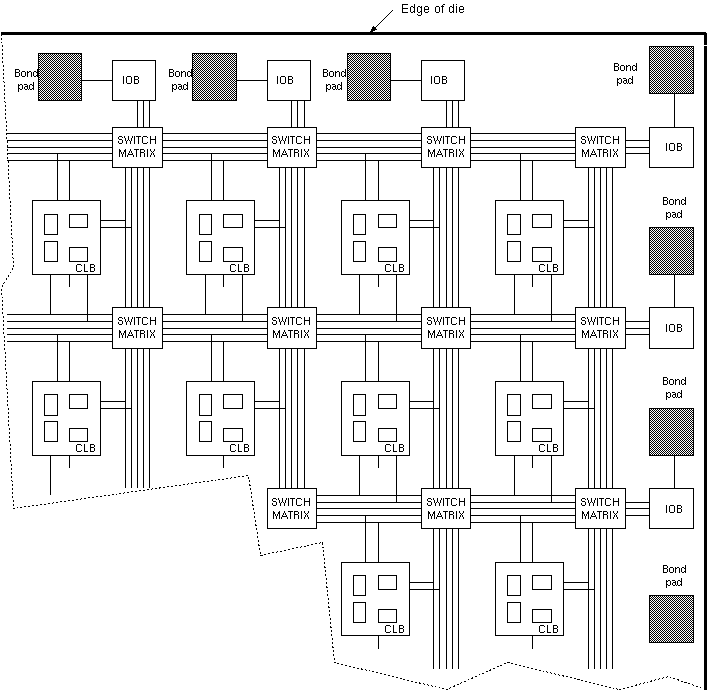

Field-programmable gate array structure, showing I/O blocks around the edge, interconnection matrix blocks and configurable logic blocks. In recent parts, the regular structure is broken up by custom blocks, including RAMs and multiplier (aka DSP) blocks.