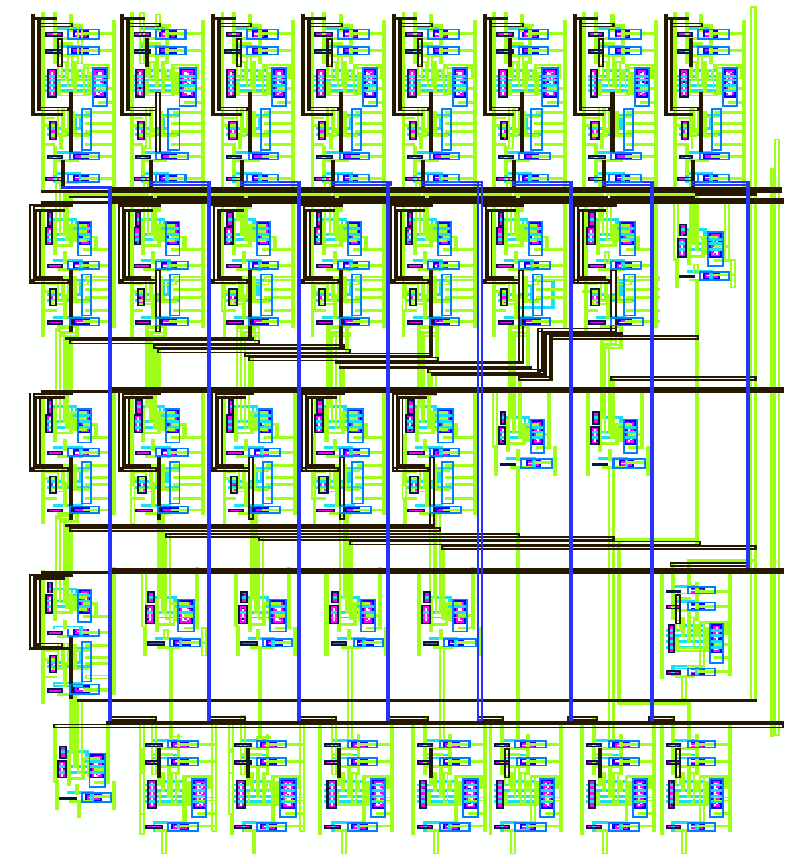

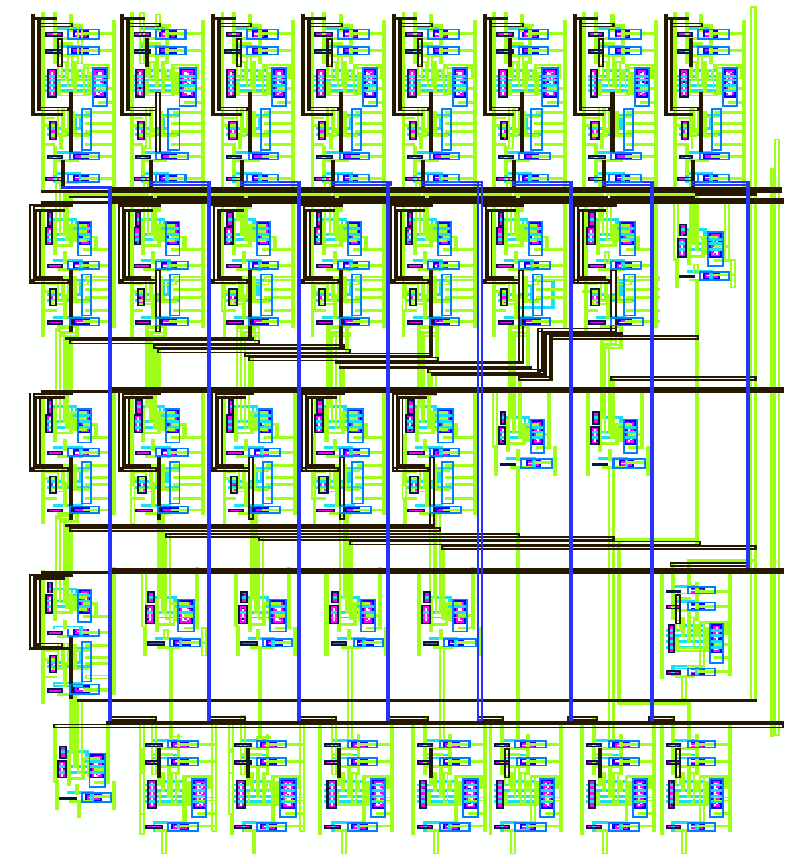

Standard cell layout for a Kogge-Stone adder. Taken from a student project (PDF on course web site).

The figure shows a cell from the data book for a standard cell library. This device has twice the `normal' drive power, which indicates one of the compromises implicit in standard cell over full-custom, which is that the size (driving power) of transistors used in a cell is not tuned on a per-instance basis. Mask-programmed gate array has been mostly replaced with the field-programmed FPGA except for analog/mixed-signal niches, such the example from »TRIAD

In standard cell designs, cells from the library can freely be placed anywhere on the silicon and the number of I/O pads and the size of the die can be freely chosen. Clearly this requires that all of the masks used for a chip are unique to that design and cannot be used again. Mask making is one of the largest costs in chip design. »(When) Will FPGAs Kill ASICs?

| 21: (C) 2008-18, DJ Greaves, University of Cambridge, Computer Laboratory. |