HOME

UP

PREV

NEXT (Landauer Limit and Reversible Computation)

Energy of Computation (1)

It is critical to understand where the energy goes in hardware in physical terms.

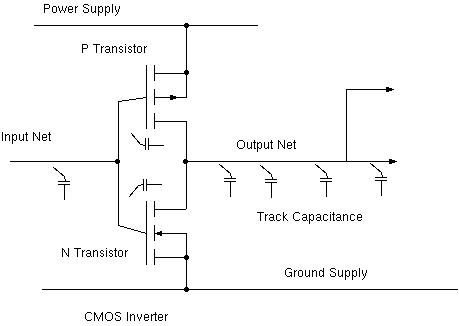

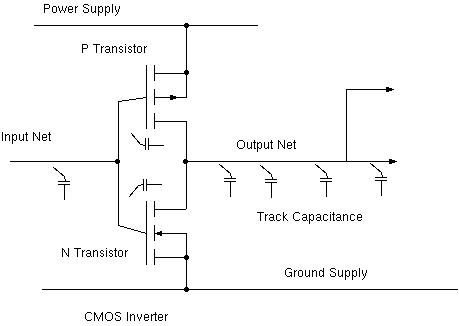

Gate current I = Static Current (leakage) + Dynamic Current.

Dynamic current = Short-circuit current + Dynamic charge current.

Early CMOS (VCC 5 volts): negligible static current,

but today at VCC of 0.9 to 1.3 volts it can be 30 percent of consumption for some (high-leakage) designs.

The short-circuit power can generally be neglected. It is the energy wasted when both the P and N transistors are briefly conducting at once as the output. It is only significant when an input is left floating or slowly changing.

| Dynamic charge current computation:

- All energy in a net is wasted each time output goes from one to zero.

- The energy in a capacitor was E = CV^2/2.

- The same amount of energy is wasted charging it up.

- Dominant capacitance is proportional to net length.

- Gate input and output capacitance also contribute to C.

Activity ratio, a: percentage of clock cycles that see a transition from 0 to 1.

The net toggle rate = 2 x Clock frequency x activity ratio = f x a.

For leakage and short-circuit power see cell library.

|

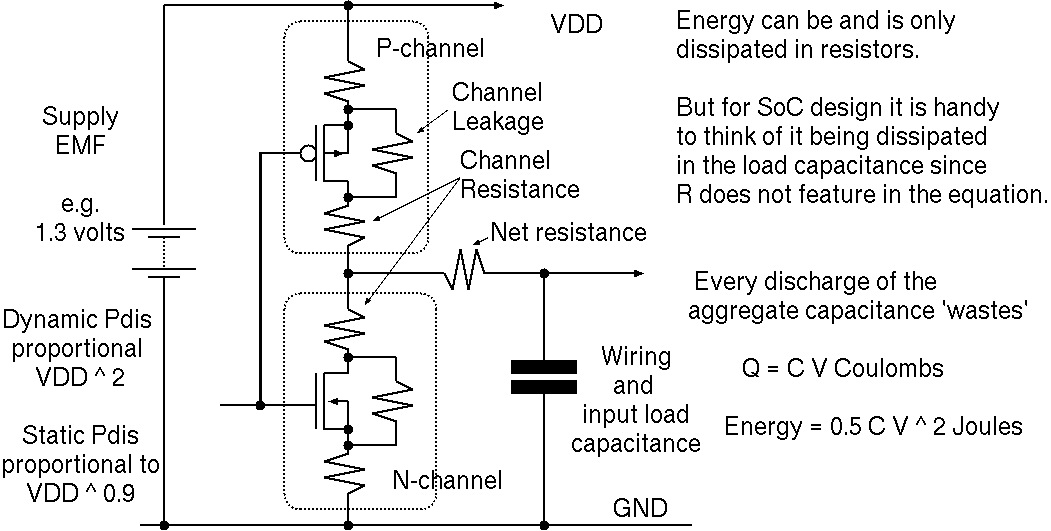

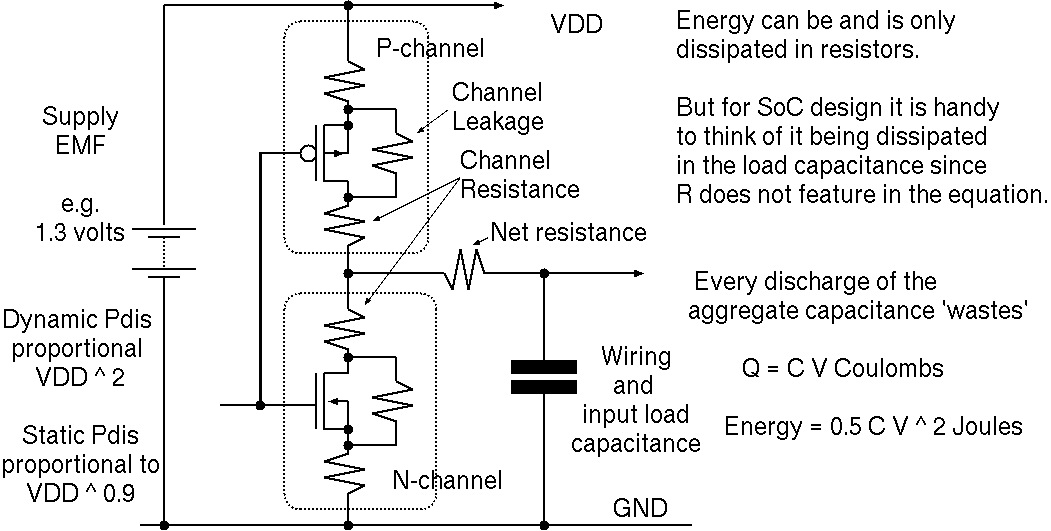

Capacitors do not consume energy - they only store it temporarily.

Capacitors do not consume energy - they only store it temporarily.

Only resistors dissipate energy in logic circuits, but their resistance

does not feature in the energy use formula.

The energy in the wiring capacitance is `wasted' on each complete transistion cycle.

If the clock frequency is f and a net has activity ratio \alpha (the fraction of clock cycles it transitions from one to zero) then the energy used is

Energy = f * alpha * C * V^2

As we increase voltage, dynamic power grows quadraticly. Static power

grows a little better than (i.e. less than) linear since transistors may turn off more fully.

Note that although we divide by two as part of the standard formula for the

energy in a capacitor, this quantity of energy is wasted both in the

charging network on the zero-to-one transition and in the discharging

network on the one-to-zero transition. So we can drop the half.

Note: static power consumption is static current multiplied by supply voltage (P=IV).

Page 30 or so of this cell library has real-word examples:

»90nm Cell Library

See also the power formula on the 7400A data sheet:

»74LVC00A.pdf

Further details:

»Power Management in CPU Design.