# INTELECTRONICS & LONG BUTCH STATE OF THE STA

September 1985 85p

Electronic music

Burglar alarm

Maveform analyser

> Australia Denmark Germany Greece Holland

3.30 Italy

38.00 Spain

7.00 Switzerland

24.00 Singapore

9.00 U.S.A.

L 4200 Pts. 370.00 SFr. 8.00 MS 7.00

# gital polyphonic «Eyboard

Digipoly is a versatile keyboard instrument capable of producing many electronic organ, piano and synthesizer sounds. It is entirely digital, with a Midi interface, and includes an 8088-based control processor and a high-speed t.t.l. signal processor with other potential applications.

Most current electronic keyboard instruments use a combination of digital and analogue circuits. Output of these instruments is typically generated by sixteen conventional analogue oscillators whose frequency, and subsequent filtering/amplification, is digitally controlled.

Digipoly is the outcome of an investigation into the possibilities of producing a musical instrument using entirely digital note generation techniques. The result is a useful piece of equipment capable of synthesizing many conventional electronic organ sounds and also many synthesizer and electonic-piano sounds. However, the basic instrument is not capable of producing any voice for which the harmonic structure of the sound changes during the note.

The main advantage of Digipoly over older analogue designs is the simplicity and versatility of its digital circuits. A standard Midi (musical-instrument digital interface) bus connection is included so that Digipoly can be used with other instruments, sequencers and under remote computer control.

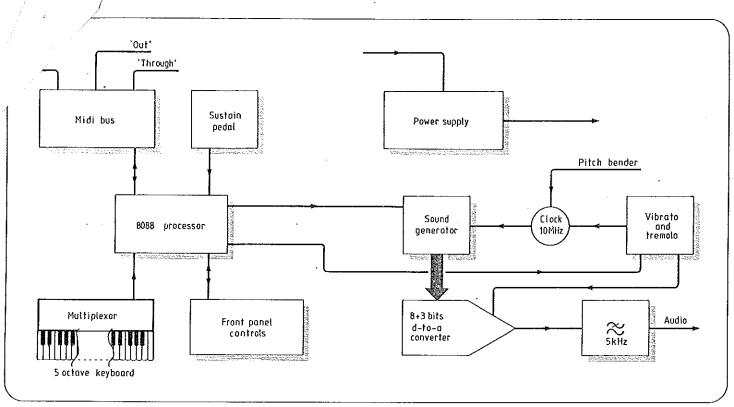

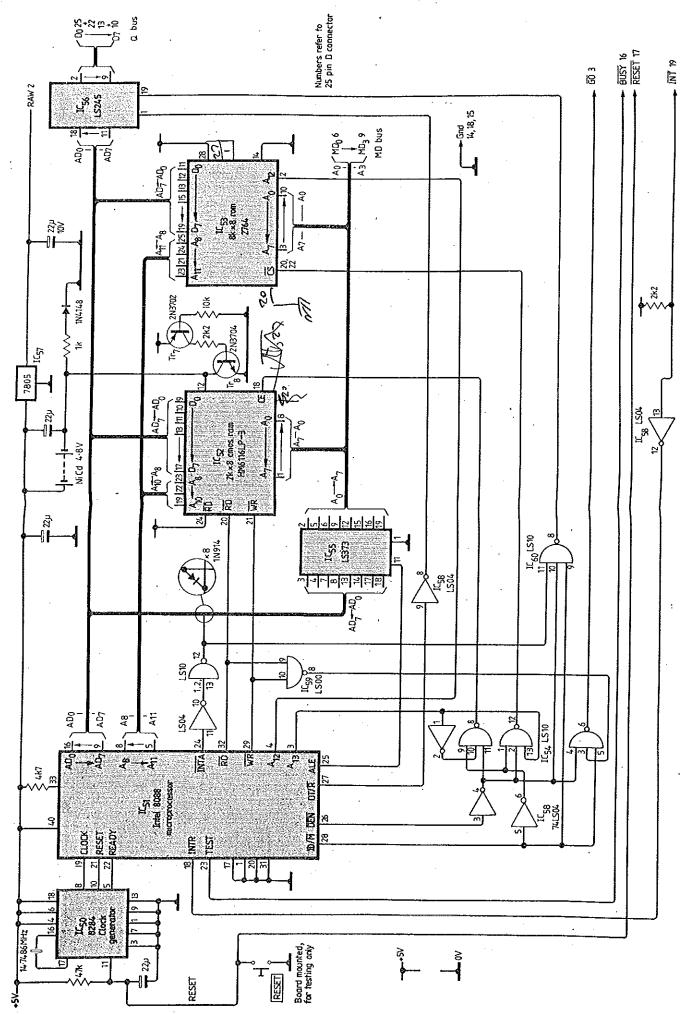

Figure one shows the interconnection of Digipoly's various parts. On its own board at the heart of the system is an 8088 microprocessor which controls all instrument functions. It has an 8Kbyte eprom for its program and lookup tables and 2Kbyte of cmos

ram with battery back-up to retain user settings for userdefined voices when the main power source is removed.

The 8088 microprocessor controls all of the instrument through 16 eight-bit parallel i/o ports. This means that for development and debugging purposes, the complete microprocessor board can be removed from the instrument and replaced by a cable to a microcomputer which addresses the same 16 ports. Software for Digipoly was developed in this way on an 8088-based computer.

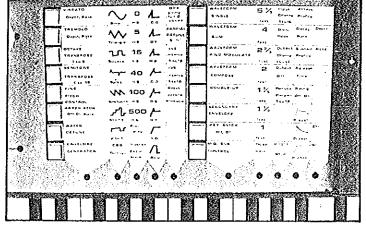

Front panel controls of the instrument are polled by the microprocessor. For economy, I chose a simple front panel with push buttons and leds, Fig.2. Two rotary controls are also used, one for the master volume setting and the second, connected to the a-to-d converter, whose function depends on the push-button selection.

The sprung-action keyboard is a standard 61-note C-to-C plastic one. It is scanned every 2ms by the microprocessor and appears as an array of 61 ones and zeros reflecting the state of

by D.J.Greaves B.A.

David Greaves is a postgraduate research student at St John's College Cambridge working with new computer architecture, in particular on natural language processing algorithms.

David is three time a winner of the Esso-sponsored Design Technology competition, holder of an IEE Jubilee Scholarship and a former contestant on BBC tv's Young Scientist of the Year programme. He plays the guitar and, being a lover of most types of music, is fascinated by anything that combines electronics, music and computer algorithms.

His many designs include a digital spectrum analyser, several digital sound effect units and an ever growing computer which he started building in 1977. This 200Kbyte computer with hard disc drives runs home-written software including a Basic interpreter, BCPL compiler and assemblers.

ELECTRONICS & WIRELESS WORLD SEPTEMBER 1985

## DIGITAL KEYBOARD

Fig.1.Block diagram of the digital polyphonic keyboard instrument, All control functions are handled by the 8088 microprocessor.

the keys. Front-panel controls allow keyboard pitch to be stepped up or down over six octaves and also transposed up and down by six semitones. Absolute pitch can be varied over one semitone to allow tuning to other instruments.

Digipoly is equipped with a midi interface which is a fast serial data link to other instruments. Bit serialization is performed by the 8088 microprocessor and timed using software delays from the processor's 15MHz crystal. Received-data start bits are used to interrupt the microprocessor whose interrupt routine then assembles a byte which is stored in a queue in memory. This queue is polled by the main program for new commands which are then interpreted according to the Midi standard.

Sound generation is performed by a microcode program running on a simple processor built from discrete t.t.l. i.cs. This processor, performing around five million instructions each second, simulates eight asynchronous oscillators whose frequency can be varied in 0.5Hz steps from zero to 16kHz. Waveforms of these oscillators are stored digitally in a 129-by-256 element array and their amplitude is adjustable over 64 linear steps. Each oscillator sends a new value to the output digital-to-analogue (d-to-a) converter at about 35kHz.

Having eight separate note channels within the instrument means that it is normally possible to hold eight keyboard keys together and hear all eight notes polyphonically. The 8088 microprocessor automatically assignes a new channel for each key. In 'double-up' mode, which is selected from the front panel, two channels are used for each key so only four keys may be used together. Reduction in the number of channels available is also sometimes caused by the automatic arpeggio effect, the Midi bus and the sustain pedal.

Output from the d-to-a converter is fed through a three-pole low-pass filter with a 5kHz cut-off frequency which remove steps from the digital waveform and sums the eight

oscillators. The d-to-a converter is eight bits wide and used eight times for each sample, giving an effective dynamic range for all voices of 66dB; when no key is pressed, converter output is zero so the signal-to-noise figure is generally better than this figure. Filter output is fed through the volume control to a ¼in jack output socket.

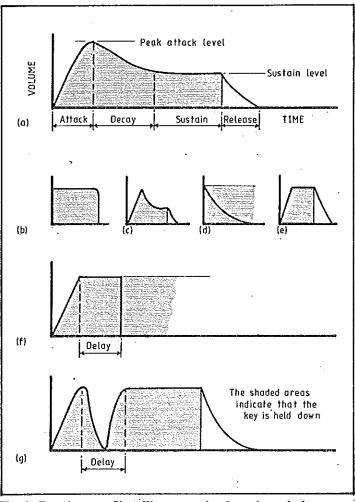

Figure 3 shows some of the envelope possibilities. A variable 0.1 to 5Hz sinewave oscillator is included to apply vibrato and tremolo modulation to the output; speed and depth of these effects are controlled digitally by the 8088

microprocessor.

#### Frequency synthesizer

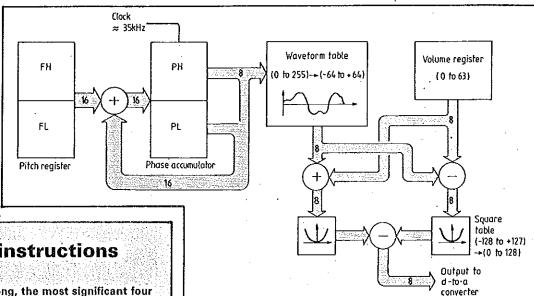

Figure 4 shows a notegeneration channel. Eight such channels are implemented by the t.t.l. microprocessor in microcode and each channel has two sixteen-bit registers. P and F. Frequency of the oscillator is determined by the F register and is set by the 8088 processor before a note starts. In each channel, the P register holds the current phase of the oscillator and has the contents of the F register added to it at regular intervals of 28µs.

The rate at which the P register overflows and returns to zero is the fundamental frequency of the note being

Fig. 2. Front panel legend. There is a variable-context button by each row in the two legend sections. A led under each column indicates when a column is in use.

duced by the channel. Being obits, the P register can count up to 65536; if the F register holds unity then the synthsized frequency is (1/0.000028)/65536 which is 0.5Hz. Hence the frequency of the channel is 0.5Hz multiplied by the value in the F register.

Indexing of the waveform table is carried out by the P register's eight most-significant bits. The waveform table, held in an array in the t.t.l. processor address space,

### T.t.l. processor instructions

All Instructions are one byte long, the most significant four bits giving the instruction opcode and the lower four bits giving the addressing mode where pertinent.

For instructions that do not specify an m value, the loworder four bits of the opcode should be zero. The INCV instruction adds one to the V register modulo n where n is the number of sound channels that the Digipoly has. This is set by links to eight. The INCV instruction has the same opcode as the HOST instruction so that the two can be performed at once. Other unused opcodes are decoded in hardware and so can easily be used to add new features to the instruction set.

#### Bit patterns for the opcodes are

|      |              | 하는 그는 그들은 눈이 있는 생생이는 그 회사의 전 생각 외원에 취임되었다. 이번 생각하게 보인다고 되었다. 그렇게 |

|------|--------------|------------------------------------------------------------------|

| 0000 | LOAD m       | load m into the accumulator                                      |

| 1000 | STORE m      | store the accumulator at m                                       |

| 0001 | ADD m        | add the m into the                                               |

|      | Andrew State | accumulator                                                      |

| 0101 | ADC m        | as add but include the carry                                     |

|      |              | bit in the result                                                |

| 0110 | SUB m        | subtract m from the                                              |

| P.XC |              | accumulator                                                      |

| 0011 | CLEAR        | zero the accumulator                                             |

| 1010 | LOOP         | execute the next instruction                                     |

|      |              | and jump to zero                                                 |

| 1011 | INCV         | increment the V register                                         |

| 1011 | HOST         | enable 8088 d.m.a. into                                          |

|      |              | memory                                                           |

| 1111 | NOP          | no operation                                                     |

|      |              |                                                                  |

#### The addressing mode bit patterns (m) are

| 0000                 | PL,V           | Low order byte of the P array                   |

|----------------------|----------------|-------------------------------------------------|

| 0001                 | PH,V           | using V<br>high order byte of the P array       |

| 0010                 | FL,V           | using V<br>low order byte of the F array        |

| 0011                 | FH,V           | using V<br>high order byte of the Farray        |

| 0100                 | VOL,V          | using V<br>volume array using V                 |

| 0101<br>0110         | DAC0           | Not used<br>DAC0                                |

| 0111<br>1000         | DAC1<br>SQ,A   | DAC1 square table indexed by the                |

| 1010                 | WV,A           | accumulator waveform indexed by the accumulator |

| 1100                 | E0             | register E0                                     |

| 1101<br>1110<br>1111 | E1<br>E2<br>E3 | register E1<br>register E2<br>register E3       |

Fig. 4. Note generating system. Microcode in the t.t.l. processor runs eight of these systems. A pitch register is repeatedly added to an accumulator which is used to index a stored waveform. The waveform is multiplied by a volume factor using the 'quarter squares' method and then sent to the output d-to-a converter.

Fig. 3. Envelope profiles. The general a.d.s.r. (attack-decay-sustain-release) envelope is shown in (a), preset envelope profiles are shown in (b-e), and (f) is a non-a.d.s.r. profile which produces pulses. A pre-echo profile similar to the general a.d.s.r. form but with two attacks is shown in (g). Shaded portions indicate the time that a key is held.

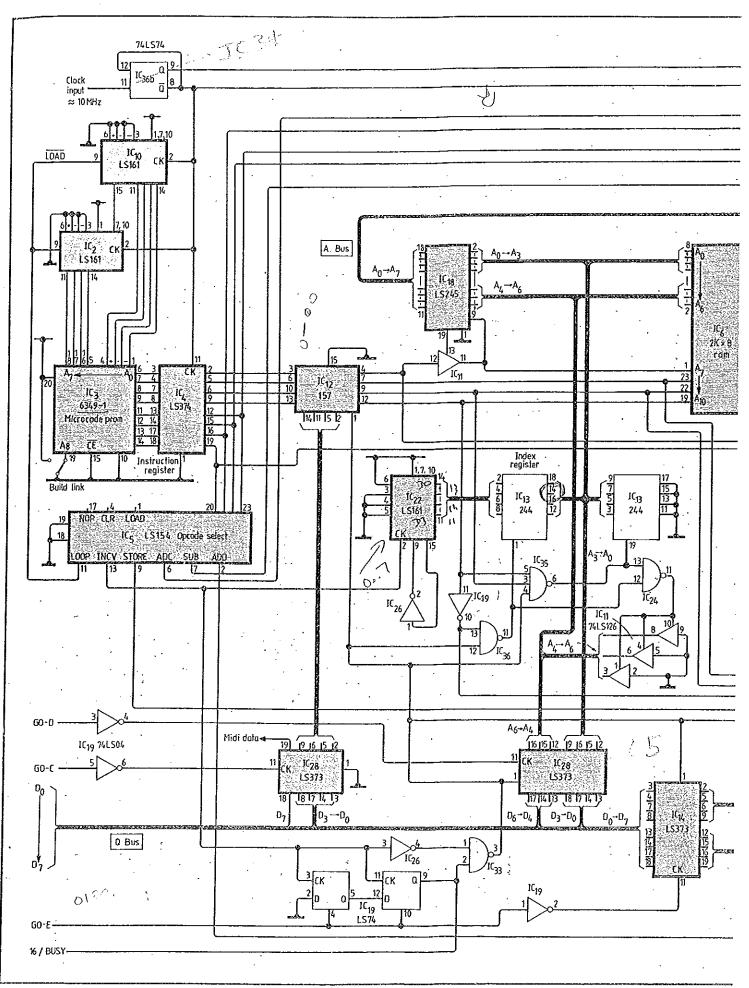

Fig. 5. Architecture of the t.t.l. processor which has ten instructions. The accumulator is used for all arithmetic results and there are four extension registers for temporary results. The main memory is partitioned in hardware and is accessed using several different addressing modes.

contains values in the range -64 to +64. Contents of the array are initially loaded by the 8088.

Each channel has a volume register holding a value between zero and 63. It is necessary to multiply values from the waveform table by the volume value to control output-signal amplitude. This multiplication is performed using the 'quartersquares' method. Use of a simple look-up table to multiply a seven-bit number by a six-bit number to produce an eight-bit result would take eight Kilobytes of memory; with the quarter-squares method, only 256 bytes are needed. The identity

A×B×4=(A+B)²-(A-B)² is used. Values from the waveform table and volume register are summed and differenced, then the difference between the squares of these values is computed. In order to keep the number of bits under control, the square table actually contains the function.

SQ(X)=X×X/128

which gives results in the range 0 to 128. When two values from the square table are differenced, a full eight-bit value is produced and this is the result of the computation.

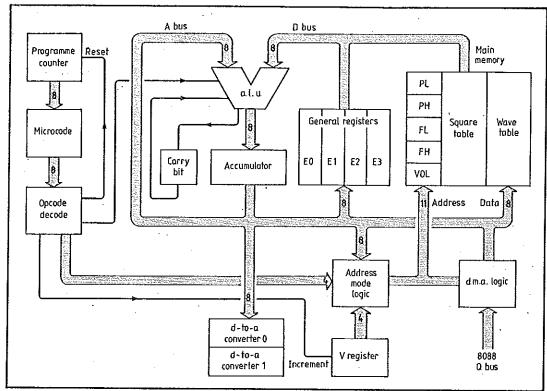

Figure five shows the t.t.l.

processor architecture. This processor was specifically designed for Digipoly but is general enough for use in many other applications. Different address spaces are used for the program and data so that the

hardware can be more easily 'pipelined'.

A prom holds the microcode program and sequential execution is controlled by the eight-bit program counter register. All data manipulation instructions use the eight-bit accumulator either as a source or destination (or both) of one of the operands. There are four general-purpose extension registers E0-E3 and an index register V which is normally used to select which synthesizer channel is being processed.

Main memory is partitioned in hardware into several regions. There are five arrays which are always indexed by the V register — PL,PH,FL,FH and VOL. These arrays contain eight-bit bytes and are 16 locations long. They are used for the low and high-order bytes of the P,F and volume registers respectively.

There are also two arrays of 256 bytes, the square table SQ and the waveform table WV, which are indexed by the accumulator. Output from the t.t.l. processor is achieved by writing to one of two locations, DAC0 and DAC1. Only DAC0 is used on the present Digipoly. Input to the processor is always performed by direct memory access (d.m.a.) to the processor memory under the control of an external device.

Descriptions of the 8088 processor section and Midi bus are included in the next article.

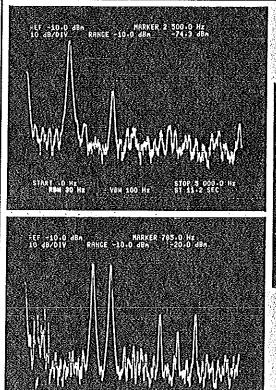

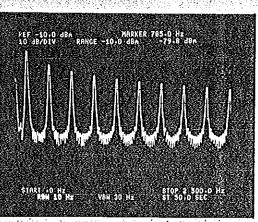

Fig. 6. Second harmonic at 36dB and sampling noise at 65dB of a 1kHz sinewave (a), two sinewaves at 750 and 1000Hz with intermodulation product —50dB at 1750Hz (b), and 120Hz squarewave with its spectrum of odd harmonics (c).

# Polyphonic keyboard

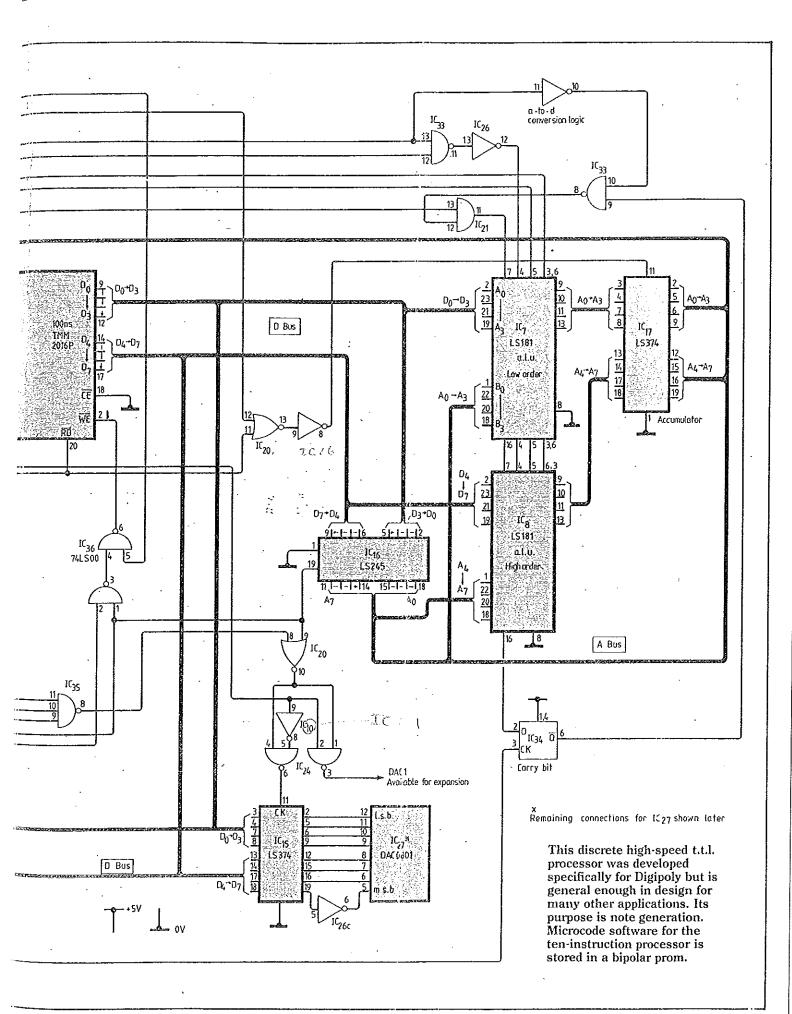

# Digipoly's t.t.l. processor circuit and microcode program.

by D.J. Greaves B.A.

The instrument has two proces- assembled using the instruction sors - an 8088 microprocessor for control functions and a t.t.l. processor for note generation. There are 18 instructions in Digipoly's microcode program, List1, which execute sequentially and then start again. The final instruction, INCV, causes the program to be run on each sound channel in turn.

Frequency of the master clock is divided by the length of the program and by the number of voices to give the sample rate at the audio output d-to-a converter. With a 5MHz master clock rate

$5\ 000\ 000/(18\times8)=35$ kHz.

An assembler written for the microcode language in BCPL produced the code in List 1, but microcode can easily be manually set described last month.

The first three instructions of the microcode increment the Pregister low-order section and the next three the high-order section. At address six, the wave from the waveform table is sampled and this is multiplied by the VOL, V register in the ramaining instructions. At address 16, the computed result is sent to the output d-to-a converter.

Each channel sends its output to the same converter and the value is latched there until the next channel sends a value.

This gives a discontinuous waveform. Summation of the eight channels into a single continuous audio wave is performed by the integrating behaviour of the analogue low-pass filter following the converter.

List 1 Microcode of t.t.l. processor is only eighteen bytes long.

### Features and software availability

Digipoly is an eight-note polyphonic digital musical instrument with a five-octave keyboard transposable over a nine-octave useful range. It includes

- Comprehensive envelope generator controls

- O Vibrato and tremolo control

- Midi interface

- O Hundreds of front-panel selectable waveforms

- Battery-maintained memory for 16 user-defined voices

- Rotary control for adjustment of many parameters

Note frequencies are not rigidly locked as in divider type organs. A detune facility introduces a variable amount of scale error.

Digipoly can be built for around £175 excluding case. Software is available iin various forms from the author at 5 Grovely Way, Crampmoor, Romsey, Hampshire SO5 9AX. A fifty-page listing of the 8088 source program is £3 and a 40track disc for the BBC microcomputer, holding source, object and related files, is £4 (single density). Programmed 2764 eproms containing the 8088 object code and a bipolar prom containing the t.t.l. processor code are £6.50 and £4.00 respectively. Please include £1 for UK postage and make cheques payable to D.J. Greaves, Brave

readers can obtain a copy of the hexadecimal listing by sending a large stamped addressed envelope and a cheque for £1.35 to our editorial offices. Please make this cheque payable to Business Press International.

\* Microcode software for the DigiPoly TTL processor. This version uses the wrap around on the V register to set the number of oscillators. The instuction after LOOP is assumed to execute. c) The HOST instruction is assumed to be performed as a side effect of the INCV instruction. The multiplication is performed using a quarter squares algorithm. The amplitude value is 0..63 and the waveform table ranges -64 to 64.  $A \times B \times A = (A + B) - (A - B)$ The square table is indexed -128 to + 127 st and gives values in the range 0 to 63 LOAD get low order part of note phase ADD FL,V STORE PL,V LOAD PH,V add on the frequency (Intergrate) 80 repeat with high order 53 81 ADC including the carry from the low order 0.5STORE PH, V 06 LOAD WY, A look up the result in the waveform table STORE E3 08 04 LOAD VOL, V get the amplitude of this oscillator. 09 6F take the difference, SUB E3 ÓΑ 08 LOAD SQ, A and square it. 8E STORE E2 Save in register 2. VOL, V LOAD OC 04 Now calculate ΟD 1 F ADD the sum of them, square the answer E3 08 LOAD SO.A 0F 4E SUB plus the square of the difference 10 86 STORE DACO giving the answer. LOOP 11 AO move to next voice and perform HOST instruction.

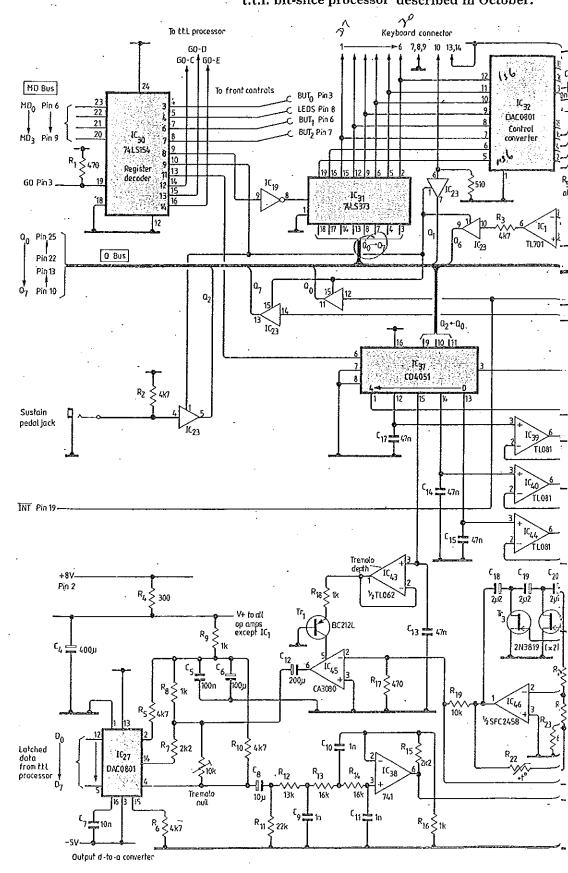

The large circuit has left little space for text in this issue. We hope to find room for more description in the next article which includes details on the Midi bus.

by D.J. Greaves B.A.

# Polyphonic Keyboard part 3

Midi interface details are included in this third article on a versatile keyboard instrument using two processors.

Software for the 8088 microprocessor was written in assembly language and programmed into a 2764 8Kbyte eprom. There are two devices in the processor memory map, this eprom with addresses between E000 and FFFF and a 2Kbyte cmos ram with battery backup using addresses from zero to 7FF.

As mentioned last month, the processor accesses the whole of the rest of the instrument in an address space of 16 parallel ports. Names and functions of used ports are given opposite.

From the user's point of view, there are two main aspects to controlling Digipoly. First is operation of the front panel controls for setting up the instument's sound and performance characteristics, and second is the response of the keys when

pressed, i.e. music.

Communication between these aspects relies on a set of global variables in the 8088 memory map known as voxcons. These voxcons are stored in a 32byte array containing all information about the current sound of the instrument. Operating the front panel controls changes some of the voxcons in specific ways and playing the instrument uses them to create sounds.

Part of the random-access memory forms a library of sixteen sets of voxcons which are retained by means of battery backup while the main power is switched off. Save and recall functions issued from the front panel copy the current voxcons to a position in the library and back respectively. Two other similar variables, for fine and coarse pitch settings, are not saved in the library. It is important that these too are saved when the main supply is switched off.

When power is applied, the 8088 is given a power-on reseet which causess it to start execution at address FFF0, which is in the eprom. First it initializes variables in its own memory map and then sends the table of squares to the t.t.l. processor. The volume registers are all zeroed and all voxcons are set to default values giving a simple reed organ type sound, i.e. a triangle wave, abrupt envelope and all other features off.

The software then enters the

main polling loop which, in outline, performs the following:

- scan keyboard, turning on or off notes that have changed since the last scan.

- send values to the d-to-a converter influence register.

- advance each envelope register phase

- inspect the Midi bus queue for commands

- scan front panel controls

- read control knob if enabled When there is no work to be done, the polling loop takes just under 1ms. Advancing of envelope phases only takes place every fifth time around the loop, i.e. once in about 4ms.

#### Midi bus

Midi, short for musical instrument digital interface, is a standard interface used on nearly all modern keyboard instruments. It can be used for controlling sound generation sections of one musical instrument from the keyboard of another. Drum computers and sequencers can also be interconnected using the bus and there are Midi adaptors which allow instruments to be controlled by computer.

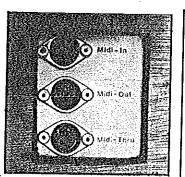

Three 180° five-pin DIN sockets are fitted to the instrument - 'Midi-in', 'Midi-out' and 'Midi-through'. Data is transmitted on pins four (positives) and five using a 10mA current loop to drive opto-isolators at the receiving end. Cables used are shielded

Midi interface back panel.

The 6-pin dil i.c. is a medium-speed opto-isolator for receiving data at 31.25 kilobaud from a 5mA current loop. A 74LS04 i.c. buffers received data driving the 'through' socket and serial data from the 8088 processor for the 'out' socket.

twisted pairs with the shield connected to pin two at both ends: this pin is only earthed at the transmitting end. The connector chasis is not connected and pins one and three are unused.

Data is transmitted serially at 31.25 kilobaud. One start bit of zero is sent then eight data bits with the least-significant bit first followed by a stop bit of one.

Midi commands are normally three bytes long. First is the command byte with its most significant bit is set on. Represented in the least-significant four bits of this byte is a channel number, n. Subsequent bytes specify parameters and have values between zero and 127.

The bus is logically divided into sixteen channels, referred to as one to sixteen, but of course the bit pattern of the n field in the command byte has values from zero to fifteen. Channel numbers that a particular instrument uses and responds to are set from the front panel of the instrument and Digipoly is no exception. Using diferent channel numbers allows

several instruments to chained together using the Midi 'through' sockets and independently controlled from a single computer or sequencer.

In some commands, the second byte is 'kk' which corresponds directly to a key on the instrument keyboard. Byte kk is zero for lowest Cand 3C for top C. If a number greater than 3C (60 denary) is received then the instrument will play that note as though the keyboard were continued to the right, provided that this is still within the instrument's pitch range. The actual highest value will depend on how the keyboard is currently transposed.

One restriction on Digipoly is that the Midi 'out' socket cannot be used at the same instant as the 'in' socket. This is because data is serialized and deserialized in software and not using a uart (universal asynchronous receiver and transmitter) i.c. The only problem that this causes is that the useful loop test involving connecting the 'out' and 'in' sockets of the same instrument will not work.

#### Midi output

If transmit-on mode is selected on the front panel (Tx on), then information from the keyboard is not interpreted by Digipoly but is transmitted on the Midi 'out' socket. The channel number must also be selected from the front panel. Commands that may be transmitted are (9n, kk 40) which notifies any device on channel n that key kk has just been pressed on the keyboard, (8n kk 40) which notifies any device on the channel that key kk has just been released, (Bn 0p vv) used to adjust sound-generating parameters of other instruments and (9104) sent as a continuous stream of double bytes on the Midi 'out' socket.

In the third command, adjust parameter, the parameter to be modified, p, is a value ranging from zero and 15 selected on the front panel. On selection of this

### Names and functions of parallel ports used on the 8088 microprocessor.

BUTTONS, port 3, contains a bit-mapped image of frontpanel control buttons.

LEDS, port 4, has various bit patterns written to it to control front-panel indicator leds.

BUT1, port 6, is a bit-mapped image of general-purpose buttons 1-8.

BUT2, port 7, is a bit-mapped image of buttons 9-16. All of these buttons are push-tomake and produce a zero bit when pressed.

CONTDAC, Port 8, when written to latches an eight-bit control word for the auxiliary d-to-a converter. This converter determines various analogue parameters. The same latch is used for scanning the clavier keyboard.

STATUS, Port 9, is a readonly port with bit flags as

Bit seven, reflecting output of the oscillator is used for arpeggio (TBASE), and is

available to clock a sequencer which could be added as a software extension.

Bit 6 is one if voltage from the rotary control potentiometer on the front panel is higher than that of the control d-to-a converter. In conjunction with

CONTDAC, this bit allows analogue-to-digital conversion under software control so that the 8080 can read the knob position. Bit 2 is zero if the sustain foot switch is pressed. Bit 1 is one if the clavier key indexed by the value last written to CONTDAC is currently held down. Bit 0 reflects the state of the Midi in serial-data line.

INFLUTE, port 11, when written to causes the voltage on the control converter output to be stored on a sample-and-hold capacitor. There are five of these capacitors. Writing numbers zero to four has the following effects. Code 000 sets the track

oscillator frequency. The track oscillator produces a sinewave for tremolo and vibrato and can be varied from about 0.2 to 10Hz. Code 001, vibrato depth, varies coupling of the track oscillator to the master clock to change the degree of vibrato in the sound by frequency modulation. Code 010, tremolo depth, varies coupling of the track oscillator to the multiply input of the main audio d-to-a converter. This changes the amount of tremolo in the sound by amplitude modulation. Code 011, fine pitch, varies

the steady frequency of the master clock to the t.t.l. processor and so pitches the whole instrument. Code 100 sets the TBASE

oscillator frequency over a range of about 0.2 to 10Hz.

HOSTREG, port 12, has its most significant bit inverted and connected directly to the Midi out socket at the back of the keyboard for communication with other

instruments and computers. Other bits in this port address regions of the t.t.f. processor main memory. Values correspond directly to values of m in the microcode instruction set.

INDEX, port 13, is similar to the previous one, except that it provides the offset address within a memory region.

DATATX, port 14, is used for writing data to the t.t.l. processor. Values are set up in HOSTREG and INDEX first, then the required data is written to this port for passing on to the t.t.l. processor when it next executes a HOST instruction. Completion of the last operation can be detected by the 8088 using a handshake on its test input. The 8088 has a WAIT instruction which causes the processor to wait until the test input goes low; it is normally advisable to execute a WAIT instruction before updating ports 12 to 14.

parameter, the main control knob is enabled and any change in its setting causes the adjust parameter command to be retransmitted with a new value of vv. Value vv ranges from zero to 127. In the final command, used as a hardware diagnostic aid, the two byte transmission is repeated about once every 400µs.

#### Midi input

Any data received on the Midi 'in' socket will be retransmitted on the 'through' socket. If the data is one of the following commands, it will also be interpreted by Digipoly. Since the keyboard has no touch-sensitivity software, the third byte of these commands need not be present for correct operation. Normally, the command will be interpreted as soon as the first two bytes are received. Commands are (9n kk 40), note on command, which plays a Digipoly note exactly as if a key had been pressed, (8n kk 40) which has the same effect as releasing key kk on the keyboard, (Cn Op 00) for selecting a present voice in the range 0-15, (Dn 7B 00) for turning all notes off and (FF) for repeating the power-on reset sequence.

While using the first command, the keyboard remains functional but pressing key kk will have no effect until the key is released, when it will silence the note. Normal polyphonic restrictions apply regarding the number of these commands that may be sent. The command for selecting a preset voice has the same effect as using the play button on Digipoly's front panel and the turn-all-notes-off command has the same effect as sending note-off commands to all current notes.

With respect to the Omni and Poly modes of the Midi standard, Digipoly always behaves as though Omni is off and Poly is on.

The t.t.l. and 8088 processor circuits are described next.

### Software availability

Digipoly can be built for around £175 excluding case. Software is available in various forms from the author at 5 Grovely Way, Crampmoor, Romsey, Hampshire S05 9AX. A 50 page listing of the 8088 source program is £3 and a 40track disc for the BBC microcomputer holding source, object and related files is £4 (single density). Programmed 2764 eproms containing the 8088 object code and a bipolar prom containing the t.t.l. processor code are £6.50 and £4 respectively. Please include £1 for UK postage and make cheques payable to D.J. Greaves. Brave readers can obtain a copy of the hexadecimal listing by sending a large stamped addressed envelope and a cheque for £1.35 to our editorial offices. Please make this cheque payable to Business Press International.

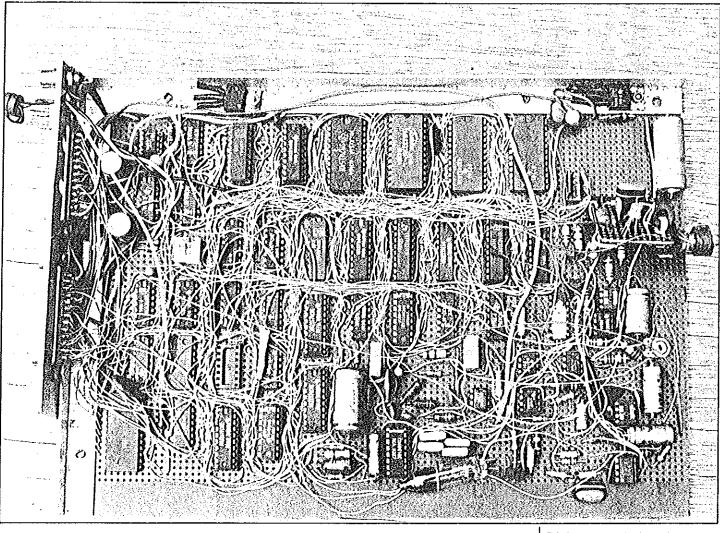

Digipoly's main board. The t.t.l. processor is in the upper left area. Microcode prom, op-code latch, op-code decoder, 100ns register memory and the two a.l.us are in the top row of i.cs. Analogue circuits to the lower right include the output low-pass filter, vibrato and tremolo (note the glassencapsulated themistor) sections and the d-to-a converter influence sample and hold circuits. To the right is a small perpendicular board holding the 10MHz master clock and at the left, a 14-pin keyboard socket and two 25-pin sockets for the 8088 board and front-panel controls.

Control-processing circuit (left) with battery-backed ram for storing user-defined voices when the power is removed. The 8088 microprocessor controls all instrument functions through 16 eight-bit parallel i/o ports.

# Polyphonic Keyboard

by D. J. Greaves B.A.

# Audio and interface circuits of David Greaves' digital musical instrument

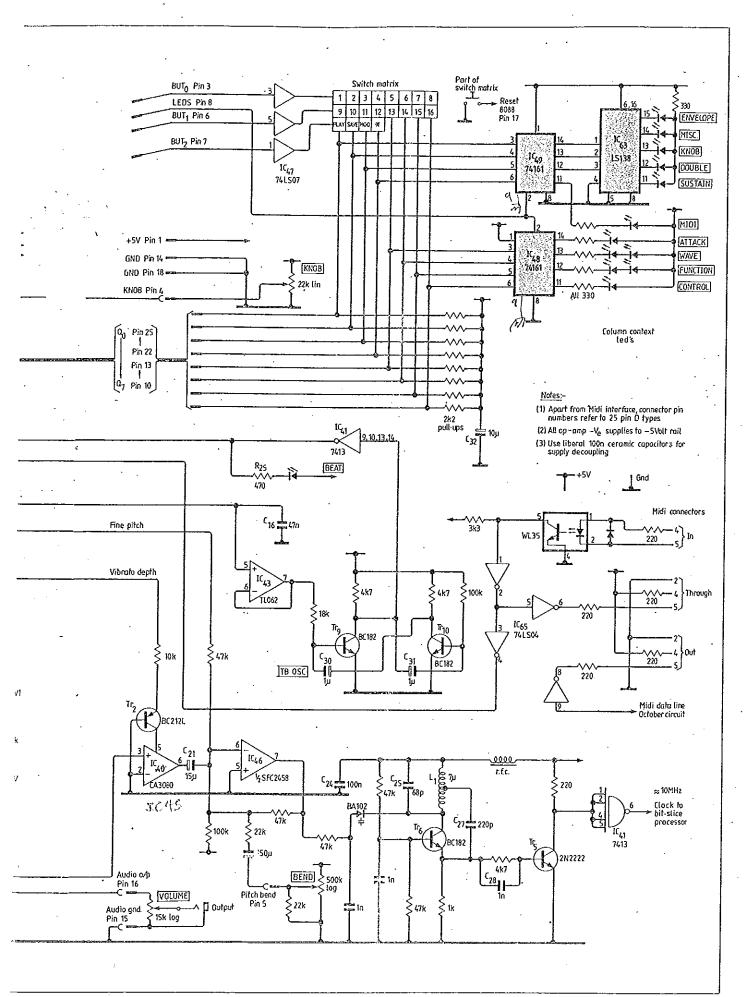

Push-to-make switches are used on the front panel. These are wired in a rectangular array of three rows by right columns. Since no two buttons in the same row need be pressed at once, multiplexing diodes are

not necessary.

The columns connect directly to the Q-bus. This bus is terminated with 2.2kΩ pull-up resistors which reduce line ringing and provide a logical one if a switch is not pressed. The rows are fed from open collector buffers which pull the row line low when the 8088 wants to read the switches. If a switch is pressed, a line in the Q-bus will be pulled low when the row line is pulled low. Debouncing of the switches is performed in software.

The front panel leds are controlled by writing to a single eight-bit latch consisting of IC<sub>48,49</sub>. For economy, a single 74LS374 could be substituted for these two integrated circuits. Ten sets of single leds or pairs of leds need to be addressed so decoder IC63 is used to extend the eight available bits.

#### Analogue electronics

Component IC<sub>32</sub> is the control digital-to-analogue converter. It is an eight bit device and produces a voltage on pin two proportional to the number that the

8088 has put into  $IC_{31}$ .

Control-converter voltage is fed to the comparator, IC1 where it is compared with the front panel knob voltage to give a single above/below bit. This bit is gated onto the Q-bus by IC<sub>23</sub> when the 8088 reads the status port. The control convertor also feeds IC<sub>37</sub>, a CD4051 eight way bilateral switch.

When the 8088 writes to its influence register, one of the switches in IC<sub>37</sub> is enabled and

this feeds the control voltage to one of five holding capacitors. These are the five sample-andhold circuits described earlier.

Holding capacitor  $C_{15}$  is buffered by  $IC_{44}$ . This capacitor

sets the tremolo and vibrato oscillator frequency. The oscillator is a standard phaseshift ring type based around half of  $IC_{46}$ . Its output feeds  $IC_{40, 45}$ , both CA3080 variable

|    |          | Polyphonic ke                | ybo             | ard i.c. list |                              |

|----|----------|------------------------------|-----------------|---------------|------------------------------|

| 1  | TL701    | KNOB comparator              | 32              | DAC0801       | Control d-to-a converter     |

| 2  | 74LS161  | Microcode address upper 4    | 33              | 74LS00        | Carry-bit logic              |

|    |          | bits                         | 34              | 74LS74        | Carry-bit reg.               |

| 3  | 6349-1   | Microcode prom               | 35              | 74LS10        | Converter address detector   |

| 4  | 74LS734  | Current op-code reg.         | 36              | 74LS00        | Converter address detector   |

| 5  | 74LS154  | Op-code decoder              | 37              | CD4051        | Converter influence reg.     |

| 6  | TMM2016P | 2K x 8 100ns ram             | 38              | 741           | Audio output filter          |

| 7  | 74LS181  | Lower four a.l.u. bits       | 39              | TL081         | Fine pitch control           |

| 8  | 74LS181  | Upper four a.l.u, bits       | 40              | TL081         | Vibrato depth control        |

| 9  | 74LS74   | Host command 2-bit shift     | $\tilde{41}$    | 74LS13        | Master clock Schmitt trigger |

|    |          | reg.                         | $\overline{42}$ | CA3080        | Tremolo depth amplifier      |

| 10 | 74LS161  | Microcode address lower      | 43              | TL062         | Tremolo-depth/timebase-      |

| l  | •        | four bits                    |                 |               | speed buffer                 |

| 11 | 74LS126  | Addressing mode steering     | 44              | TL081         | Tremolo and vibrato-speed    |

| 12 | 74LS157  | Host-command address         |                 |               | buffer                       |

| 1  |          | switch                       | 45              | CA3080        | Vibrato depth amplifier      |

| 13 | 74LS244  | V-reg. buffer                | 46              | SFC2458       | Tremolo and vibrato osc.     |

| 14 | 74LS373  | Host data reg.               | 47              | 7407          | Front panel o.c. buffer      |

| 15 | 74LS374  | Audio d-to-a converter reg.  | 48              | 74LS161       | Upper led latch              |

| 16 | 74LS245  | A-bus to D-bus buffer        | 49              | 74LS161       | Lower led latch              |

| 17 | 74LS374  | Accumulator                  | 50              | 8284          | 8088 clock generator         |

| 18 | 74LS245  | Indexed addressing buffer    | 51              | 8088          | processor                    |

| 19 | 74LS04   |                              | 52              | HMM6116LP-3   | 2K×8 c-mos memory            |

| 20 | 74LS02   |                              | 53              | 2764          | 8K×8 n·mos eprom             |

| 21 | 74LS08   |                              | 54              | 74LS10        | 8088 address decoding        |

| 22 | 74LS161  | V-reg.                       | 55              | 74LS373       | 8088 lower address bus       |

| 23 | 74LS367  | Status port buffers          |                 |               | latch                        |

| 24 | 74LS00   |                              | 56              | 74LS245       | 8088 i/o transceiver         |

| 25 | 74LS373  | Data for host index reg.     | 57              | 7805          | 8088 5V regulator            |

| 26 | 74LS04   |                              | 58              | 74LS04        | 8088 logic                   |

| 27 | DAC0801  | Audio output converter       | 59              | 74LS00        | 8088 logic                   |

| 28 | 74LS373  | Data destination reg. & Midi | 60              | 74LS10        | 8088 i/o decoder             |

|    |          | out                          | 61              | 7805          | 5V regulator                 |

| 30 | 74LS154  | Host reg. address decode     | 62              | 7905          | - 5V regulator               |

| 31 | 74LS373  | Control converter reg. & key | 63              | 74LS138       | Front-panel led controller   |

|    |          | scan address                 | 64              | 7805          | Microcode logic regulator    |

|    |          |                              | 65              | 74LS04        | Midi data buffer             |

transconductance amplifiers. Their transconductance is set by a current into pin five.

Similar circuits are used for both 3080 devices consisting of transistor constant-current generators whose current is set by one of the influence register sample and hold circuits.

Amplifier IC<sub>45</sub> modulates reference current in the audiooutput converter IC<sub>27</sub> to provide a tremolo effect. Because the converter zero output is actually half way through its range, the tremolo modulates the d.c. level of the output. This effect can be nulled by adjusting the tremolo null potentiometer to add an opposite d.c. modulation directly to the output. The potentiometer is the only preset requirement in the whole instrument.

Audio output from the converter is filtered by IC<sub>38</sub> which is wired as a Sallen and Key three-pole low-pass filter with pass-band gain of three and cut-off frequency of 5kHz. Output level is about 200mV when a single key is pressed.

Component IC<sub>40</sub> feeds IC<sub>46</sub> which controls frequency of the master clock to provide a vibrato effect. Along with the vibrato signal, IC46 sums the fine pitch setting from IC39 and voltage from the pitch-bend front-panel control. Output of IC46 biases a voltage-controlled capacitor in the tank circuit of the clock. For a swing from +5 to -10V in bias, clock frequency varies by about 1.5MHz in 10MHz. However this range is not all needed and only a positive and negative swing of about 2V is produced by IC<sub>46</sub>. A swing of 600kHz in the master clock changes the instrument pitch by one semitone.

Control-converter register IC<sub>31</sub> is also used to read the keyboard. The prototype keyboard has a built-in digital encoder provided with a 14-pin dil header connector. A five octave C-to-C keyboard has 61 notes which therefore need a six bit address.

The six least-significant bits of  $IC_{31}$  are fed to the keyboard and a single bit is returned. Numbering the lowest C as zero, if the key addressed by the six-bit number is pressed, then a logical one is returned, otherwise a zero. The bit is buffered by  $IC_{23}$  onto the Q-bus so that it appears as bit one in the 8088 status port.

Digital-to-analogue conversion, interfacing and audio processing are main functions of this final section of the digital polyphonic keyboard. Midi i/o is on the middle right. The Q data bus links to both the 8088 control processor section described in the November issue and the t.t.l. bit-slice processor described in October.

# Polyphonic Reyboard — part 5

by D. J. Greaves B.A.

Hardware details of Digipoly's two processors are presented in this final article.

he t.t.l. processor is clocked by a 10 MHz Hartley oscillator using  $Tr_6$  as the active component (December issue circuit). Output at 10 MHz is converted to a squarewave using the self-biasing stage around  $Tr_5$  and then divided by two by  $IC_{36b}$  to give the operating frequency of 5 MHz. This signal clocks the instruction address counter made from  $IC_{2,10}$ , as shown in October on the t.t.l. processor circuit.

Microcode for the processor is stored in IC<sub>3</sub>, a bipolar programmable read-only memory (prom) from the MMI or Signetics 63xx series. The 6349 is organized as 512 locations of eight-bit bytes and has an access time of about 55ns; any non-volatile memory device with an access time of less than 150ns could be substituted.

Each op-code from the prom is latched in IC<sub>4</sub> while it is being executed. The four most-significant bits drive four-to-sixteen-line decoder IC<sub>5</sub>, outputs of which select the operation.

Least-significant bits feed the data selector IC<sub>12</sub> to provide a page-select address for the processor's memory device, IC<sub>6</sub>. Being n-mos, memory IC<sub>6</sub> is the slowest element in the t.t.l. processor and limits operating speed to 5MHz. Access time of this 2K-by-8bit static memory is 100ns. As can be seen from Table 1, which shows address allocations for IC<sub>6</sub>, not all the memory locations are used.

The two 74LS181 four-bit arithmetic logic i.cs form the arithmetic unit. Accumulator output register IC<sub>17</sub> has its outputs permanently enabled in order to drive the A-bus. Together with the D-bus, the A-bus feeds into the a.l.u. where the two eight-bit

numbers are combined to produce a new value for the accumulator.

Values for the D-bus are supplied from memory. The type of combination performed by the a.l.u. depends on the control number fed into the a.l.u. on pins three to six.

Arithmetic instructions in the t.t.l.-processor instruction set are ordered so that the a.l.u. control number can be derived directly from each op-code bit pattern.

Bistable device  $IC_{34}$  is a onebit latch containing the carry bit. It is updated only as a result of an ADD instruction and its contents are fed into the a.l.u. through  $IC_{33c,21d}$  during an analogue-to-digital conversion instruction.

For store operations,  $IC_{16}$  is enabled to feed the accumulator value onto the D-bus so that the memory can be updated. Some store operations feed the output ports in an addressing mode decoded by  $IC_{35c}$ . One of two output ports is selected by  $IC_{24}$ .

Data for the output analogue converter is latched in IC<sub>15</sub> in two's complement form. Since the digital-to-analogue converter expects unsigned numbers on its inputs, IC<sub>26c</sub> adds 128 to the number which offsets the zero value to the middle of the converter's voltage range.

Addressing modes are decoded by random logic and determine what feeds the address inputs to the memory. Four-bit V-rigister  $IC_{22}$  is gated onto  $A_{0.3}$  by  $IC_{13}$  if indexed addressing is required for V instructions.

Zeros are fed onto the low address bits by IC<sub>1</sub> and IC<sub>11</sub> feeds zeros onto the high address bits if indexing is not required. If accumulator indexing is required, buffer IC<sub>18</sub> is enabled to gate the A-bus onto A<sub>0.7</sub>.

Input to the t.t.l. processor occurs during the HOST instruction under control of the 8088 processor. The 8088 processor has an i/o bus called the Q-bus which feeds three register ports in the t.t.l. processor. Latches and operations of these three ports are shown on Table 2.

Writing data to port 14 also sets two-bit shift reigster  $IC_9$  to all ones. Clocking of the shift register takes places at the end of each HOST instruction; if the output bit is one, data from  $IC_{14}$  is written into the t.t.l. processor memory.

8088 microprocessor board also contains an 8K eprom, 2Kbyte ram, an 8284 clock generator and crystal, NiCd battery for data retention, various support chips and an extra reset switch.

### Feature summary

Digipoly is an eight-note polyphonic digital musical instrument with a five-octave keyboard transposable over a nine-octave useful range. It includes

- Comprehensive envelope generator controls

- Vibrato and tremolo control

- Midi interface

- Hundreds of front-panel selectable waveforms

- Battery-maintained memory for 16 user-defined voices

- Rotary control for continuous adjustment of many parameters

Note frequencies are not rigidly locked as in divider type organs. A detune facility introduces a variable amount of scale error,

**ELECTRONICS & WIRELESS WORLD JANUARY 1986**

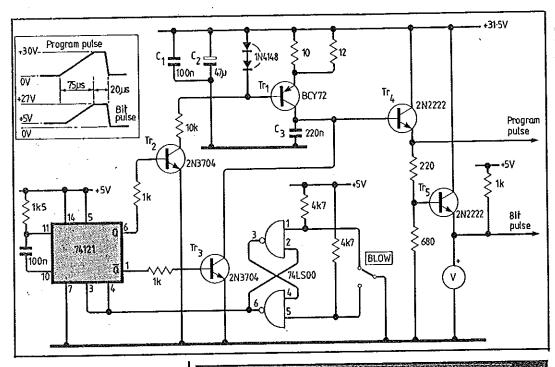

Microcode for the highspeed t.t.l. processor is contained in a 63xx-series programmable rom (Monolithic Memories, Farnborough). This circuit, published on page 39 in the April 1985 issue of Electronic Engineering is for programming such roms. There are one or two minor errors in the previously published circuit.

The 6349 prom may be programmed manually by addressing a byte then using this circuit to program all bits that must be zero. The program pulse is fed to the chip-enable input, pin 15, and the bit pulse to. the output pin.

Table 1. Memory use in the t.t.l.

| Address | Array                       |

|---------|-----------------------------|

| 000-00F | low-order osc. phases       |

| 080-08F | high-order osc. phases      |

| 100-10F | low-order frequency values  |

| 180-18F | high-order frequency values |

| 200-20F | volume values               |

| 400-4FF | table of squares            |

| 500-5FF | waveform table              |

| 600     | E <sub>n</sub> register     |

| 680     | E <sub>1</sub> register     |

| 700     | E <sub>2</sub> register     |

| 780     | E <sub>3</sub> register     |

Hote: the first five arrays are indexed using the V register; the two tables are indexed using the accumulator.

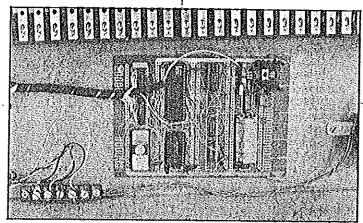

Back view of Digipoly's front panel showing the knobs leds and switches. Four interface devices  $IC_{47,48,49,63}$  are mounted on their own board, with led current-limiting resistors and the Q-bus terminating pull-up resistors.

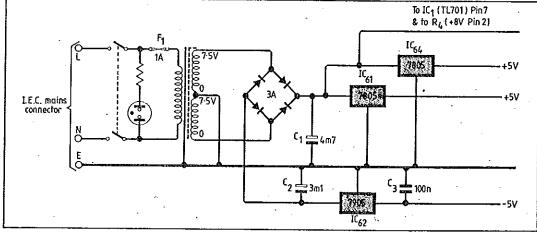

Digipoly power supply provides 8V and -8V unregulated. Up to 2.5A is required from the positive supply to drive the 5V logic. the ground pin is connected to

Presence of the shift register causes the data to be written twice on successive HOST instructions. The second writing ensures that the correct data is written to the t.t.l. processor memory when the HOST instruction is executing at the time that the 8088 writes to  $IC_{14}$ .

For speed, and since the IN-CV instruction does not need access to the memory, INVC and HOST instructions are performed together using the same op-code. This is simply a matter of wiring outputs of IC<sub>5</sub>.

The LOOP instruction causes the address counter to load a zero value on the next instruction. Since there is a one instruction delay through the prom and IC4, the instruction after LOOP is always executed before control resumes at the start of the microcode. If needed, an accumulator indexed branch could be added by simply feeding the A-bus to pins three to six of IC2.10.

#### 8088 processor hardware

The 8088 microprocessor is mounted on a separate board with ten other i.cs, forming a self-contained microcomputer module. This module is connected to the rest of Digipoly through a single 25-pin connector carrying address/data lines for the 16 ports, signals for reset, busy and interrupt and an 8V supply line. This is a general-purpose computer board: I have used the same circuit in other applications.

Clock generator IC50 is an Intel 8284 device. It divides a 14.7486MHz crystal frequency by three to obtain the two-toone duty cycle required by the 8088 processor. Power-on reset and wait-state circuits are also provided by the 8284, although wait states are not used in this design.

Component IC52 provides the 8088 processor with 2Kbyte of ram. This static ram is an HMM6116LP-3 c-mos device requiring only about 4µA of current in standby mode. It is practical to run the memory from a small NiCd battery for long periods; when Digipoly is switched on, the battery charges automatically from the 5V supply.

Supply-pin 24 of the ram is connected to the 5V supply but

ELECTRONICS & WIRELESS WORLD JANUARY 1986

ground through  $Tr_8$ . When the board is powered  $Tr_8$  is switched fully on, bringing the main and i.c. grounds to within 50mV of each other. This figure is too small to affect logic switching. When power is removed however,  $Tr_8$  turns off, causing the ram ground pin to move to -4.8V relative to the main ground.

Put another way, all ram control signals move to +4.8V, or logic one. Since the ram control pins are active when at logic zero, this disables the ram, putting it into low-power mode. When Tr<sub>8</sub> is off, its collector-base diode becomes forward biased so Tr<sub>7</sub> is needed to stop the battery being discharged through the base of Tr<sub>8</sub>.

Input and output to the 8088 is performed through the Q-bus. This bus is a set of eight lines running through the whole instrument. Associated with the Q-bus is the MD-bus consisting of four lines for selecting one of the 16 i/o ports that the 8088 can address.

Both the MD-bus and the transceiver buffering the bus, IC<sub>56</sub>, are set up before master strobe line GO is pulsed low. This gives time for written data to propagate and settle. On input cycles, the data is returned to the 8088 before the trailing edge of the GO pulse. This pulse is always about 350ns long.

On arriving at the board, the active-low interrupt-request signal is inverted and fed to the 8088 maskable-interrupt input. The non-maskable input is not used. In response to an interrupt, the 8088 strobes INTA low twice at pin 24. The first strobe is a dummy one and the second reads an interrupt vector from the processor data bus. Eight diodes provide the vector by grounding each line during the acknowledge cycle, producing a zero value. Hence only vector zero is used and this sets software to read a serial byte from the Midi-in port.

#### Performance

Figure 6a in the September issue shows the Digipoly output spectrum when synthesizing a single 1kHz sinewave. The noise floor is at -65dB relative to the single note. This is virtually all sampling noise which disappears when no notes are pressed since d-to-a converter

25-pin connectors Two connectors, both D-types, link the main t.t.l., processor to the front panel and 8088 card.

| Pin 8088-board     | Control panel        |

|--------------------|----------------------|

| 1 n.c.             | 5V                   |

| 2 8V unstab.       | n.c.                 |

| 3 strobe, atc. low | read control buttons |

| 4 ground           | knob voltage         |

| 5 n.c.             | pitch-bend voltage   |

| 6 MD <sub>o</sub>  | read buttons 1-8     |

| 7 MD <sub>1</sub>  | read buttons 9-16    |

| 8 MD <sub>2</sub>  | write to leds        |

| 9 MD <sub>3</sub>  | n.c.                 |

| 10 Q <sub>7</sub>  | 0 <sub>7</sub>       |

| 11 08              | 06                   |

| 12 Q <sub>5</sub>  | Q <sub>s</sub>       |

| 13 O <sub>4</sub>  | $0_4$                |

| 14 ground          | ground               |

| 15 ground          | audio ground         |

| 16 BUSY            | audio out            |

| 17 reset switch    | reset switch         |

| 18 ground          | ground               |

| 19 INT             | n.c.                 |

| 20 n.c.            | п.с.                 |

| 21 n.c.            | n.c.                 |

| 22 Q <sub>3</sub>  | $0_3$                |

| 23 Q <sub>2</sub>  | $\mathfrak{Q}_{Z}$   |

| 24 Q <sub>1</sub>  | a <sub>1</sub>       |

| 25 Q <sub>0</sub>  | $Q_0$                |

|                    |                      |

| Table | 2. | Port | data | latche | 15 |

|-------|----|------|------|--------|----|

| IC | Port | Operation                               |

|----|------|-----------------------------------------|

| 28 | 12   | select type of memory to be<br>modified |

| 25 | 13   | memory offset of type<br>defined above  |

| 14 | 14   | data to be stored                       |

output is constant d.c.

Sampling noise can be heard quite clearly if Digipoly is connected into a high-quality amplifier and loudspeakers. This means that a further low-pass filter, for example on a mixing desk, has to be added before the sinewave voice can be used for quiet solo work. For all other voices there is no problem with output signal-to-noise ratio.

Owing to the note-generation technique, synthesis of highfrequency complex waveforms above about 1kHz is not good. Using higher frequencies, nonconsecutive samples from the waveform table are taken with gaps of several samples. This causes small features in the waveform to become aliased, thus introducing the characteristically unmusical spurious frequencies into the sound. Remember though, that the true harmonics that these small features are supposed to add to the sound would be out of the audio spectrum and the desired sound can be achieved by using a simpler waveform.

Figure 6(b) in the September issue shows intermodulation product measured when two sinewaves are produced by

Digipoly back panel provides an illuminated on/off power switch and access to the mains fuse. A BS4491 connector is provided for 240V a.c. input and 6mm jacks connect the sustain-pedal switch and the audio output.

Midi standard calls for three connections; Midi-in receives data which is automatically echoed on Midi-through. Midi-out leads to other devices under Digipoly control.

holding down two keys at once. This product is presumably created in the 741-based active filter used in Digipoly's output circuit since the digital circuit behaves totally linearly. Figure 6c shows harmonic spectrum from a single squarewave.

Performance and versatility of Digipoly are very good. The instrument is capable of producing several well-known organ sounds, a good Fender Rhodes sound, good chime and bell sounds and a large number of rich, raunchy synthesizer sounds.

As usual with keyboard instruments, adding a few effects such as flanger and chorus can add a lot to the sound and the Midi interface puts the instrument among the best as far as interfacing goes.

General view of Digipoly interior. The power supply is at the left, 8088 processor central and t.t.l. processor right.