Technical Report

Number 934

**Computer Laboratory**

# Exploitation from malicious PCI Express peripherals

Colin L. Rothwell

February 2019

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500

https://www.cl.cam.ac.uk/

© 2019 Colin L. Rothwell

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

https://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986

### EXPLOITATION FROM MALICIOUS PCI EXPRESS PERIPHERALS

## Colin Lewis Rothwell

The thesis of this dissertation is that, despite widespread belief in the security community, systems are still vulnerable to attacks from malicious peripherals delivered over the *PCI Express* (PCIe) protocol. Malicious peripherals can be plugged directly into internal PCIe slots, or connected via an external Thunderbolt connection.

To prove this thesis, we designed and built a new PCIe attack platform. We discovered that a simple platform was insufficient to carry out complex attacks, so created the first PCIe attack platform that runs a full, conventional os. To allows us to conduct attacks against higher-level os functionality built on PCIe, we made the attack platform emulate in detail the behaviour of an Intel 82574L *Network Interface Controller* (NIC), by using a device model extracted from the QEMU emulator.

We discovered a number of vulnerabilities in the PCIe protocol itself, and with the way that the defence mechanisms it provides are used by modern oss. The principal defence mechanism provided is the *Input/Output Memory Management Unit* (IOMMU). The remaps the address space used by peripherals in 4KiB chunks, and can prevent access to areas of address space that a peripheral should not be able to access. We found that, contrary to belief in the security community, the IOMMUS in modern systems were not designed to protect against attacks from malicious peripherals, but to allow virtual machines direct access to real hardware.

We discovered that use of the IOMMU is patchy even in modern operating systems. Windows effectively does not use the IOMMU at all; macOS opens windows that are shared by all devices; Linux and FreeBSD map windows into host memory separately for each device, but only if poorly documented boot flags are used. These oss make no effort to ensure that only data that should be visible to the devices is in the mapped windows.

We created novel attacks that subverted control flow and read private data against systems running macOS, Linux and FreeBSD with the highest level of relevant protection enabled. These represent the first use of the relevant exploits in each case.

In the final part of this thesis, we evaluate the suitability of a number of proposed general purpose and specific mitigations against DMA attacks, and make a number of recommendations about future directions in IOMMU software and hardware.

#### A note on formatting

This is the *technical report* version of my thesis. As such, it is formatted differently from the submitted version. In particular, the text block of the technical report version is much wider, which saves paper at a cost in readability (possibly), and aesthetics (certainly). It also lacks the title page and colophon. My preferred version of this thesis is available at the University's Apollo repository<sup>*a*</sup>, or on my personal website<sup>*b*</sup>.

<sup>a</sup>https://www.repository.cam.ac.uk/handle/1810/274352 <sup>b</sup>http://colinrothwell.net To my parents, of course.

## DECLARATION

This dissertation is the result of my own work and includes nothing which is the outcome of work done in collaboration except as declared in the Preface and specified in the text. It is not substantially the same as any that I have submitted, or, is being concurrently submitted for a degree or diploma or other qualification at the University of Cambridge or any other University or similar institution except as declared in the Preface and specified in the text. I further state that no substantial part of my dissertation has already been submitted, or, is being concurrently submitted for any such degree, diploma or other qualification at the University of Cambridge or any other University or similar institution except as declared in the Preface and specified in the text. It does not exceed the prescribed word limit of 60,000 words.

> Colin Lewis Rothwell September 2017

## ACKNOWLEDGEMENTS

There is a slight danger that any statement that begins 'I would like to thank' takes on the histrionic tone of an Oscar winner's speech. Nevertheless, I would like to thank...

First and foremost, Simon Moore and Robert Watson, my supervisor and secondary supervisor. Despite both being extremely busy, they have always been available to provide me with both guidance and friendly conversation. The level of trust they have put in me to find and complete a difficult research project has often exceeded the level I put in myself. I am particularly grateful to Simon for supporting my interest in hardware from my undergraduate degree onwards; and to Robert for gently steering me towards an area of security that I found interesting, and providing me with the well-founded suspicions about the state of DMA security that motivated my eventual thesis.

My examiners, Andrew Moore and Herbert Bos, for their careful and considered reading of my thesis, and providing suggestions that I believe have resulted in a substantially better dissertation.

Ross Anderson for his detailed reading of my thesis and encouraging remarks.

Mbou Eyole, my supervisor at ARM, for his insightful comments about my work, for giving me the freedom to pursue my interests as they developed, and for his supervision during my placement at ARM.

Theo Markettos, my principal collaborator on this project, for suffering a lot of FPGArelated pain so that I didn't have to and for being willing to check my ideas and work through problems from across the other side of the desk at short notice.

Brett Gutstein and Allison Pearce, for their contributions to the project as a whole, and their writing and proof-reading on our papers. Allison, specifically, for her initial work to confirm the likelihood of vulnerabilities on macOS; Brett for proof-of-concept attacks on macOS.

Jon Woodruff and David Chisnall, for supervising my third year project, which was my first experience of the CTSRD research group, and for making the experience sufficiently enjoyable that I went on to continue in the same group, using the same skills, for my PhD. I also thank Jon for his support for the BERI processor, and David for the opportunity to contribute to the ASPLOS 2015 paper on CHERI and the C programming language.

John Fawcett, my former Director of Studies at Churchill, for encouraging me to consider research as an option, and for providing me with many opportunities to teach and conduct interviews, without pressuring me to do too much.

Several fellow students in the Computer Lab, including my one-time office mate Alexandre Joannu, who has shared the stresses of his PhD at the same time as me; and the various people I have eaten lunch or played table football with, for some interesting conversations in many senses of the word, including Alan Mujumdar, Robert Norton, Niall Murphy, Steven Herbert, and Michael Hull.

My friends generally, for keeping me sane. Friends from before university, for irregular meetings that have kept me grounded (I hope). Friends from my undergraduate degree, who have been here the same seven years I have, and people we have met after graduating. Friends that I used to teach, in particular those who joined me as PhD students, Sam Ainsworth and Ian Orton, for their entertainingly singular take on life in the Computer Lab. Sam and Ian also, for providing feedback on the draft.

Anybody I have met because they have been involved with a show with me. The opportunities I've had to perform theatre of various sorts have far exceeded the expectations I had when I joined Cambridge, and it's been a lovely experience of a world that is very different to computer science.

Finally, my parents. Firstly, for struggling through this technical document to provide comments on the grammar, but also for their support in many less tangible ways. They have not had an easy time while I have been doing my PhD – largely for reasons that are not my fault, of course. Despite this, they have always provided me with warmth, wisdom and encouragement, whether in food, visits to or from the dog, or simply by their companionship. Thank you for everything.

# CONTENTS

- List of Figures 13

- List of Tables 14

## 1 INTRODUCTION 15

### 2 BACKGROUND 19

- 2.1 Threat Model 20

- 2.2 Attack Scenarios 21

- 2.3 PCI Express 23

- 2.4 Thunderbolt 27

- 2.5 Network Interface Controllers 27

- 2.6 IOMMUS 28

- 2.7 Control Flow Vulnerabilities and Exploits 33

- 2.8 Vulnerability Taxonomy 35

- 2.9 Attack and Escalation Techniques 35

- 2.10 Early DMA Attacks 37

- 2.11 Existing Attacks against the IOMMU 38

## 3 KNOWN MITIGATIONS 43

- 3.1 Deployed Protection 43

- 3.2 Research 47

- 3.3 Summary 51

## 4 THE RESEARCH PLATFORM 53

- 4.1 Platform Structure 54

- 4.2 The Terasic DE5-Net and Soft SoCs 55

- 4.3 The Software Interface 57

- 4.4 QEMU 61

- 4.5 Postgres Back end 65

- 4.6 Summary 67

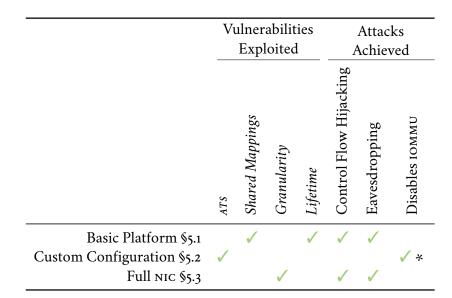

# 5 NOVEL ATTACKS 69

- 5.1 Attacks from a Basic Platform 70

- 5.2 Custom Configuration Responses 74

- 5.3 Full NIC emulation 76

- 5.4 Effective Defences 78

- 5.5 Summary 79

#### 6 FUTURE DEFENCES 81

- 6.1 Robust Drivers 81

- 6.2 Suspicious Behaviour Detection 81

- 6.3 Cryptographic Handshaking 82

- 6.4 Encrypted Memory 82

- Finer Granularity Mappings 83

- 6.6 Spatial Segregation 87

- 6.7 Bounce Buffering 87

- 6.8 Address Space Layout Randomisation 87

6.5

- 6.9 Symbol Hiding 87

- 6.10 Function Pointer Indirection 88

- 6.11 Novel Peripheral Interconnects 89

- 6.12 Summary 89

## 7 CONCLUSION 91

- 7.1 Contributions 91

- 7.2 Recommendations 92

- 7.3 Future Work 93

- GLOSSARY 95

- Bibliography 101

# LIST OF FIGURES

| 2.1 | Interconnect Protocols in a Single Processor Intel System      |

|-----|----------------------------------------------------------------|

| 2.2 | PCIe ID Bit Layout                                             |

| 2.3 | ATS Extended Capability Bit Layout                             |

| 2.4 | Descriptor Ring Diagram                                        |

| 2.5 | Intel vT-d Page Table Diagram 31                               |

| 4.1 | Photograph of macOS experimental setup                         |

| 4.2 | Photograph of Windows, Linux and FreeBSD experimental setup 54 |

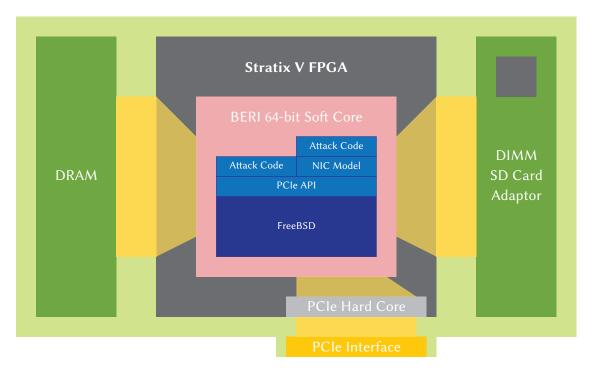

| 4.3 | Attack Platform Diagram                                        |

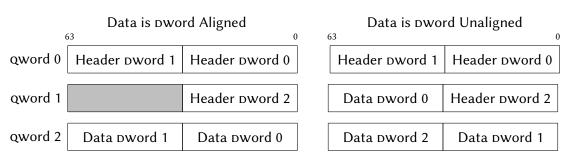

| 4.4 | Intel PCIe Hardcore Header and Data Alignment                  |

| 4.5 | RawTLP definition                                              |

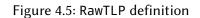

| 4.6 | Request Transaction Bit Layout and Corresponding Struct        |

| 4.7 | Postgres field access macro                                    |

| 4.8 | Code to construct TLP                                          |

| 5.1 | MacOS Mbuf Definition                                          |

| 5.2 | struct iopa_t Definition                                       |

| 5.3 | Code for Adding an ATS Capability to a NIC Model               |

| 6.1 | Page Table Mapping with Base and Bounds                        |

# LIST OF TABLES

| 2.1 | Meanings of the AT field in a PCIe header           |

|-----|-----------------------------------------------------|

| 2.2 | Taxonomy of Vulnerabilities                         |

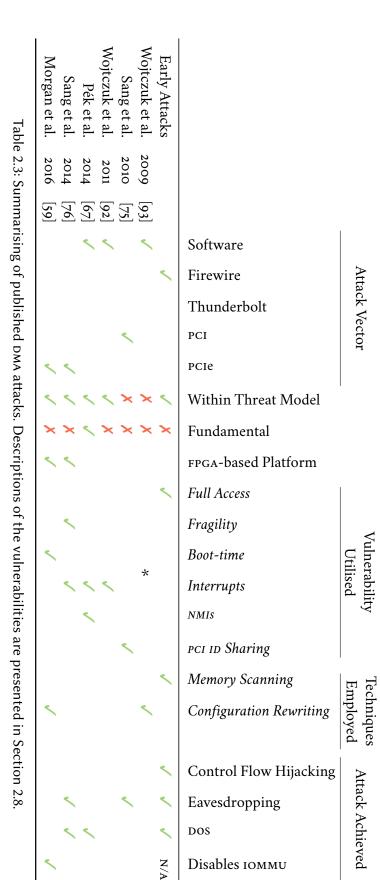

| 2.3 | Summary of published DMA attacks                    |

| 3.1 | Performance Improvement Provided by [53]            |

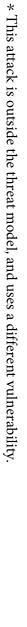

| 3.2 | юмми Usage in Current oss 52                        |

| 3.3 | юмми-based Mitigation Research                      |

| 5.1 | Fields Common to Every MacOS Mbuf                   |

| 5.2 | Header Data in MacOS Mbufs with an External Payload |

| 5.3 | Summary of our novel attacks                        |

| 6.1 | Potential Defences                                  |

# INTRODUCTION

A traditional model of a personal computer is of a *central processing unit* (CPU), some memory, and a collection of peripherals that allow the computer to interact with the outside world. This model has become increasingly inaccurate, as peripherals are becoming more and more complicated, and are performing increasing amounts of workload-specific computation that would once have been performed by the CPU. In the earliest PCs, peripherals were unable to directly access host memory: they could communicate with the host only in response to requests from the CPU. To transfer data to a device, the CPU had to read from memory into its registers, then write from its registers to the device. Transferring data from the device involved the same operation in reverse. CPUs are not particularly good at transferring data. Their registers are narrower than the width of a modern memory bus, so even though the processor may execute multiple instructions in the time between sequential memory operations completing, it is hard for the processor to saturate the bus. Processors also implement a vast number of features for control flow and arithmetic that are largely superfluous for copying data.

To allow CPUs to spend less time copying memory, and more time performing the complex calculations for which they are designed, certain peripherals were allowed *Direct Memory Access* (DMA), so they could read and write host memory without requiring copy instructions to be performed by the processor. In a familiar story, this is good for performance, but has worrying implications for security. As time has gone on, DMA has become widespread. The ubiquitous standard in internal peripheral interconnects is now *PCI Express* (PCIe), the successor to the *Peripheral Component Interconnect* (PCI) standard, described in Section 2.3. In contrast to its predecessor, PCIe potentially allows every connected peripheral DMA. This allows *confused deputy* attacks, where a device is forced to use its DMA privileges maliciously [35]. Worse, an attacker may be able to directly install a malicious peripheral into the computer itself. With DMA, an attacker can entirely rewrite the kernel in memory, so any protection mechanism that is implemented only in software can potentially be rewritten, and therefore bypassed, itself.

This perhaps does not seem like too big a security concern. After all, any attacker who is willing to use a screwdriver to open a device is clearly very determined. However, the IEEE 1394 standard, which was released in 1995 [39] and implemented by Apple as 'Firewire', provided DMA to peripherals that were outside the computer's case. This led to the development of a number of attacks that were carried out via the somewhat unexpected vector of a hacked iPod running a custom software stack [11]. No truly satisfying defences were deployed against these attacks, with only partial mitigations at best being released. Apple, for example, disabled the relevant driver when the user was not logged in [4]. However, Firewire was never really ubiquitous.

In 2011, Apple and Intel released 'Thunderbolt', another high-speed external peripheral interconnect that granted DMA, covered in more detail in Section 2.4. The same attacks that were possible over Firewire were possible over Thunderbolt, simply by using a Thunderbolt-to-Firewire adaptor [50]. Like Firewire, for several years after its release, Thunderbolt was

far from ubiquitous, being found on most Apple computers, but only a few Windows PCs. At the beginning of December 2015, Thunderbolt 3 was released. This dropped the proprietary Thunderbolt connector, and switched to using the USB Type-C (more commonly, USB-C) connector. Consequently, Thunderbolt 3 started appearing on most new mid- and high-end Windows laptops, as well as Apple products.

In the meantime, both AMD and Intel started releasing processors with *Input Output Memory Management Units* (IOMMUS), beginning around 2008. A traditional *Memory Management Unit* (MMU) maps between a virtual address used by a program and a physical DRAM address: an IOMMU does the same thing, except with virtual addresses used by a peripheral. Indeed, deployed IOMMUS greatly resemble conventional MMUS: they employ a *page based* architecture where memory can be remapped in 4KiB chunks, and have an analogue of the *Translation Lookaside Buffer* (TLB) which caches translations in order to improve performance – the IOTLB. Any area of memory that a device does not have a mapping for, it cannot access. Many early attacks operated by rewriting os code in memory. IOMMUS are covered in more detail in Section 2.6. As code and data are in distinct areas of memory, the IOMMU could protect against these attacks. This level of protection seems to have been enough for the attack community to form a loose consensus that the IOMMU was sufficient to prevent all DMA attacks.

From 2009 onwards, various groups of researchers carried out work that used gaps in IOMMU protection to disable the IOMMU and regain DMA to all of physical memory. These gaps in protection included a time period at boot when the IOMMU did not protect its own configuration structures, forming a *race condition* [59, 60], and the use of interrupts, which were initially not remapped [92]. At around the same time, some research work was done in improving the performance of the os algorithms that made use of the IOMMU [53, 68]. Some of this work posited that the lack of granularity in the IOMMU would prove to be a security vulnerability, but did not suggest exploits or attempt to carry out any attacks [55]. We describe these attacks in Section 2.10.

Beginning in 2015, we began investigating the possibility of carrying out DMA attacks on modern systems. We first conducted a survey of the IOMMU support provided across several modern operating systems, using system tracing tools to reveal the existence of some probable vulnerabilities [66].

In order to exploit these vulnerabilities in practice, we created an soc on FPGA, which used the BERI 64-bit open source processor, capable of booting the FreeBSD operating system. We describe the platform in detail in Chapter 4. We used this platform to develop several novel attacks against PCIe, thereby demonstrating that the current level of protection against DMA attacks is inadequate. More information on these attacks is given in Chapter 5. We attacked macOS with an exploit that allowed hijacking of a function pointer along with some of the arguments that function was called with inside the kernel. This attack required finding a kernel symbol that was leaked to the attack platform in order to break the *Kernel Address Space Layout Randomisation* (KASLR – see Section 2.7) which randomises the location of the kernel in virtual memory. We also exploited a feature of PCIe that allows a peripheral to cache translations on a device itself. This was achieved by creating the simplest possible behavioural model of an Intel 82574L NIC that Linux recognised as functional, and modifying the PCIe configuration of this device to report that it was capable of caching translations. This allowed the device to mark DMA accesses as having being translated by the device, allowing full access to host memory in spite of IOMMU protection.

We also exploited the same vulnerability that allowed control flow subversion on macOS on FreeBSD, despite FreeBSD's superior protection. To do this, we extracted a complete behavioural model of an Intel 82574L NIC from the QEMU emulator, and cross-compiled it for

BERI. Ordinarily 'DMA' for a QEMU device involves accessing memory running on the emulator platform. We modified the device model so that its DMA requests were sent over PCIE to the real host. We also used this fake-NIC-based platform in order to read data encrypted by IPSEC and sent over the host's real NIC in macOS can be read by an attacker.

# Contributions

In this dissertation, we make the following principal contributions:

- We characterise a new threat model for DMA-based attacks (Section 2.1). It is not acceptable to state that all peripherals must be part of the trusted computing base. Peripherals that are granted DMA to a system may have insecure upgrade channels that leave them liable to exploitation, may be sourced from an untrustworthy supplier, or may be plugged into an external Thunderbolt 3 port.

- We create, test, and debug an attack platform to enable a thorough exploration of the space of DMA attacks (Chapter 4). In particular, we simulate an existing, benign PCIe device to allow attacks that rely on higher-level protocol behaviours.

- We conduct the first thorough investigation of relevant literature, covering work in the areas of both attack and defense, fields that each seem to exist without thorough understanding of the other (Sections 2.10 and 2.11; Chapter 3).

- We demonstrate exploits based on novel mechanisms against widely-deployed, modern operating systems (Chapter 5).

- We suggest some mitigations for these vulnerabilities (Chapter 6).

Over the course of my PhD I have made contributions to the following papers:

• Under Submission – Markettos, A. T.\*, Rothwell, C.\*, Gutstein, B., Moore, S., Pearce, A., and Watson, R. A Thunderbolt from the Blue: Exploiting IOMMU Bypass Vulnerabilities in Operating Systems. (\* These authors contributed equally to the work.)

The work detailed throughout this thesis forms the majority of this paper.

• October 2016 – Watson, R., Rothwell, C. et al. Fast Protection-Domain Crossing in the CHERI Capability- System Architecture. IEEE Micro Volume 36, Issue 5 [88].

Early in my PhD, I made contributions to the CHERI capability research processor, including improvements to the memory bus, and the development of a floating point unit.

• *March 2015* – Chisnall, D., *Rothwell, C.* et al. *Beyond the PDP-11: Architectural support for a memory-safe C abstract machine*. Proceedings of the Twentieth International Conference on Architectural Support for Programming Languages and Operating Systems [18].

I undertook a partially automated investigation of a large corpus in order to determine the ways in which it used C language pointers that resulted in invalid behaviour with reference to the specification.

# Acknowledgements of Technical Contributions

With the exception of the following, the work detailed in this thesis was all carried out by myself:

- *A. Theodore Markettos* The investigation of Microsoft Windows discussed in Section 3.1. The construction of the hardware aspects of the platform covered in Chapter 4.

- *Brett Gutstein* Some investigation of macOS, discussed in Section 3.1. An initial version of a control flow subversion attack against macOS, further detailed in Section 5.1.

- Allison Pearce An initial survey of IOMMU use using sytem-tracing tools, covered earlier in the introduction. Some investigation of macOS, discussed in Section 3.1.

# A Note on Branding

Much of the work detailed in this thesis is carried out on Intel FPGAS. Formerly, these were Altera FPGAS, but over the course of the work Intel bought Altera, and have rebranded their products accordingly. We use Intel throughout, as this enables information about the products we use to be found most easily online, despite the physical objects themselves carrying an Altera logo.

# BACKGROUND

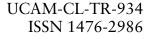

A modern PC is a collection of disparate parts produced by different manufacturers. This is in contrast to the early days of computers, where every component of a mainframe was produced by a single manufacturer, so logic for 10 could be handled by homogeneous compute units, such as channels or peripheral processors [8, 19], which we discuss further in Section 2.6. In order for the different peripherals in a PC to communicate with the processor and main memory, they use a standardised substrate, traditionally thought of as a bus. In the same way that peripherals are no longer the simple electrical interfaces that they used to be, this is no longer a particularly accurate representation of the present situation. A modern Intel system, for example, uses an array of specialised protocols for different tasks. The CPU is not connected directly to most peripherals, with this instead delegated to a chipset, which Intel call a Platform Controller Hub (PCH). The CPU is composed of multiple independent cores that communicate among themselves with a proprietary, nameless ring-based interconnect [85]. A system agent on the same chip as the processor cores connects the cores directly to DRAM, and typically includes a PCIe channel to communicate with a Graphics Processing Unit (GPU) and a separate proprietary interface to connect to a chipset. In a system with a single-processor chip, this interconnect is Direct Media Interface: on a system with multiple physical processors, it is Quick Path Interconnect, which connects to the other processors in the system, and to some number of chipsets that are shared between different cores [10]. Figure 2.1 represents a single-processor Intel system diagrammatically.

Figure 2.1: Diagram showing some of the different protocols that appear in a single-processor Intel system. If the system had multiple processors, these would be connected with Quick Path Interconnect. Intel's server class processors are beginning to move to a mesh-based internal interconnect, rather than the ring presented here [40].

There are many criteria by which peripheral interconnects can be compared. Probably the simplest is whether the interconnect is external or internal – whether the connector is easily accessible on the outside of the computer case or not. Originally, most external peripherals had simple requirements, and were designed for human-computer interaction. However, there has been an increasing desire for high-performance external peripheral interconnects. One particular impetus for this has been the growth in popularity of laptops, which frequently have very little flexibility for internal peripherals. Another is the appearance of external mass storage devices – Firewire was often used on early digital camcorders.

Another criterion for the comparison of interconnects is *Direct Memory Access* (DMA) support. The use of DMA-enabled peripherals provides higher speed data transfer while incurring a lower CPU overhead, but means the peripheral must be trusted. The general approach to this tension between performance and security in the past has been to confine DMA to internal interconnects. The assumption seems to have been that if an adversary has physical access to a machine, then they will be able to subvert it somehow, so a weakness that requires opening up the case with a screwdriver is outside the threat model.

However, as demand for higher-performance external interconnects has grown, we have seen external interconnects with DMA: first Firewire, and now Thunderbolt. When devices were created to subvert machines using the weaknesses in Firewire, only stopgap solutions were implemented (Section 2.10). MacOS prevented the use of Firewire at the login screen to prevent attacks that allowed a user to log in without a password [4]; advice from the attackers recommends uninstalling the drivers that enable DMA [50]. The consensus among the community is that attacks via Thunderbolt can be prevented with the use of an IOMMU [50, 26], but IOMMUS were designed to allow higher performance virtualisation, not to prevent attacks from a malicious adversary [41, 7].

## 2.1 THREAT MODEL

To begin to develop attacks, we must first characterise a threat model. The field has not converged on a threat model for peripherals in the same way that it has for, for example, memory safety. We have found a range of different views on the threat provided by peripherals across the literature. Much work assumes that a user who has physical access to a machine is able to fully compromise its security, a view shared by the Intel vT-d specification, as discussed in Section 2.6. This presents the IOMMU as providing better performance for virtualisation and protecting against badly programmed drivers; malicious adversaries are never explicitly mentioned. We define a threat model that we believe includes the capabilities of many plausible attackers. Some examples of plausible attackers are discussed in Section 2.2.

The threat model assumed in this thesis is an attacker that:

- Has access to a PCIe slot inside the system or a Thunderbolt port outside it. Access to a PCIe slot may be through firmware override of a device that is already inside the system.

- May make arbitrary valid PCIe transactions.

- Does not have the ability to run any software on the victim computer, although we do mention cases where we hypothesise that lifting this restriction would allow more attacks in the face of more stringent defences.

- When using a PCIe slot, may power-cycle the machine. This is because systems do not generally support PCIe hotplugging, and represents the device being rebooted over its normal course of use.

- Is not able to induce behaviour outside the specification of the computer hardware. In particu-

lar, we consider the use of DRAM disturbance, or *rowhammer* attacks (for example, [45, 70, 86]) to be outside the scope of this thesis.

In order to be perfectly secure in the face of such an attacker:

- <sup>1</sup> The system must not unduly trust unverified peripherals. Verification must be the responsibility of the user, who must ensure that each peripheral in the system is identified according to its purpose.

- 2 Each peripheral in the system must be granted access to only the areas of address space required to carry out its specified functionality.

- 3 Any areas of address space that a device has read-access to must not contain data other than that intended for the device while that device has access. Correspondingly, any areas of address space that a device has write-access must not effect the semantics of the running system in any way other than that specified.

- 4 It must be impossible for a peripheral to impersonate any other device in the system, to ensure that the victim does not attempt to allow that peripheral access to data that is meant for the impersonated peripheral.

A mechanism that provides all of these benefits with an acceptable performance cost may not be possible within the confines of PCIe, or the expectations that users have of their system.

Even with a protection mechanism that provides these guarantees, there are still some plausible peripheral-based attacks. Out-of-scope attacks include those that use legitimate, specified behaviour of the system to induce faults. They also include certain sorts of Trojan attacks. For example, where a peripheral is provided by a manufacturer that carries out its specified behaviour, but also performs some sort of malicious activity. Examples might include NICs that record the data that they transmit, or a webcam that works in tandem with other parts of the system to record the user unexpectedly. Defences against even these attacks may be possible, for example by cryptographic verification of device firmware by a trusted system component; a full analysis is complex, which is why we define it as explicitly out-of-scope. We also exclude attacks where the user, for example, picks up a malicious usB pendrive they find on the ground, and runs a binary they find installed [83].

# 2.2 ATTACK SCENARIOS

We identify several plausible scenarios in which an attacker could attain the capabilities assumed by our model:

- 1 Deliberate production of malicious peripherals for sale to the consumer. This could be carried out by a particularly unscrupulous manufacturer, either for explicitly malicious purposes, or to enforce a notion of rights control. Large multinutational companies have demonstrated that they are not above this behaviour in the past, as in the case of the Sony BMG rootkit scandal [77]. It may also be that a state actor coerces a manufacturer into the inclusion of backdoors that operate in this fashion.

- 2 Accidental production of malicious peripherals for sale to the consumer. There are many ways in which a manufacturer could produce a device with good intentions that later acted as a vector for an attack. For example, a rogue employee could potentially modify the firmware; the mechanism for firmware updates could be externally subverted; and for sufficiently programmable devices, it is plausible that an attack can be written to run on the device [24, 96].

- 3 *Distribution of 'trojan' devices by individuals.* A device does not necessarily only carry out its expected functionality. People are willing to plug peripherals into their laptops with minimal

assurances of trustworthiness.

A Thunderbolt dongle for video output at a conference is an obvious example, as one provided by a conference hotel could be easily and discreetly swapped by a guest or employee without difficulty. As conference speakers do not consider the video-output port on their laptop to be a source of vulnerabilities, a single malicious dongle could lead to the compromise of significant numbers of laptops.

The ability of the new USB-C connector to provide power delivery, and data protocols other than USB make even more attacks of this type possible: what appears to a user to be a simple USB device could opportunistically attempt to operate as a Thunderbolt device in order to carry out an attack. We are already seeing socket outlets that provide USB for charging mobile devices. At the same time, laptops that charge over USB are appearing. A malicious state actor could easily provide USB-C charging points in communal locations, such as airports, that install a rootkit before charging an attached device. Any peripheral that uses a USB-C connector could equally carry out the same attacks.

Another attack of this nature, as suggested in [75] is in a workplace where users share computers. A user could install a PCIe card to install a rootkit in a machine that they are currently using.

One impediment to the mass production of attack devices that employ Thunderbolt is its cost. Intel maintains a tight grip on the market, and is the only company manufacturing Thunderbolt controllers. To gain access to developer information, a form must be submitted detailing the proposed Thunderbolt device. Our attack platform, described in detail in Chapter 4, uses an expensive FPGA and development board, and a 'MaxExpansion.com<sup>™</sup> PCIe to Thunderbolt dock, which retails at \$850. As well as being expensive, the attack platform is bulky and conspicuous.

However, with some ingenuity, it would be possible to create an attack device at a lower cost that was much more discreet. Even Intel's relatively low end FPGAs now include PCIe support. The Cyclone V SX chip, which includes a dual-core ARM Cortex-A9, would probably be able to carry out any of the attacks we present if equipped with appropriate memory and mounted on a PCB. These are available for around \$80. A PCIe-to-Thunderbolt bridge can be extracted from an Apple Ethernet to Thunderbolt 2 adaptor, which retail for \$29. Apple's Ethernet to Thunderbolt adaptors are principally built around two chips: a Thunderbolt controller and an Ethernet to PCIe chip [78]. These are joined by a short length of cable carrying the PCIe signal. An attack platform could be constructed by cutting this cable in two and connecting it to another device capable of generating PCIe signals. This means that the minimal cost of an attack, excluding man-power and development tools is around \$150. With the construction of a custom PCB for mounting the FPGA, it would probably be possible to create a convincing Trojan device in the same space as a Thunderbolt to vGA adaptor. This places attacks on specific targets well within the price range of a determined individual or organisation.

Additional engineering work could lead to a further large decrease in the cost of exploits. Although the operation of Thunderbolt controller chips is secret, the chips themselves are widely available at a cost of around \$10. A determined adversary would be able to reverse-engineer the operation of these chips and drive them from a cheap microcontroller. Previous large-scale attacks have shown that criminal gangs are capable of creating hardware-based exploits [73, 31]. It is plausible that special shims and adaptors could be distributed to many vulnerable locations.

Another possibility is an attack that exploits the firmware of a device that is already in the system. This approach was demonstrated in [24]. This could lead to a worm, where a

device is uploaded with malicious firmware that uploads itself to other vulnerable devices that it comes into contact with. Firmware-based attacks seem like they will continue to be a concern in the future. The GPUs present in all modern system, whether embedded or discrete are powerful, Turing-complete processors, which are already starting to be used as vectors for malware [96]. This is part of a general trend towards more flexibility in peripherals, also seen in the programmable NICs being introduced to cope with increasing network bandwidth demands. These typically include an FPGA fabric or other specialised architecture to allow packet processing at very high performance. These devices are primarily targeted at high frequency trading but may have applications in other areas. These users are potentially high value targets, so this may already be a serious risk. It seems unlikely that devices of this nature will spread to home users, as they do not require very high bandwidth network access. This may, however, be due to the limitations of bandwidth available. Nvidia are currently trialling a game-streaming server that has a recommended bandwidth requirement of 50Mbps [27], beyond the capacity of most home internet connections.

### 2.3 PCI EXPRESS

*PCI Express* (PCIe) is the ubiquitous standard internal peripheral interconnect. It was primarily designed to replace the PCI bus, and deliberately uses a compatible-but-expanded software interface, although its physical layer is very different.

PCIe is designed rather like a network protocol, as a stack of encapsulated layers. Only the *Transaction Layer* of PCIe, which broadly corresponds to the network and transport layers in the OSI model is directly relevant to our work.

At the physical layer, PCIe is a *differential signalling* protocol. This means that data is encoded as the difference in signal between a pair of conductors, rather than the difference between a single conductor and ground. Inside a computer, the conductors are tracks on a PCB. Data on the conductors is encoded with a *line code*. For PCIe versions one and two, this is an *8b/10b* encoding, where 8-bit data words are transmitted as 10-bit signals. For PCIe versions, three and up, a *128b/130b* encoding is used, which has a lower overhead. The use of line encodings brings more favourable electrical properties than just transmitting the data raw.

The basic conceptual unit of the PCIe interconnect is the *link*. A link consists of two single-way channels, each running in a different direction between a pair of components. Links may operate at one of a number of different signaling rates. Each link supports at least one *lane*, which consists of a pair of differential signalling pairs (so four conductors in total) – again, one in each direction. Having multiple lanes per channel enables PCIe to provide different bandwidth at different locations.

These links connect a number of components of different types together. The interconnect can be thought of as a hierarchy: at the top is the *root complex*, which connects the rest of the interconnect to the CPU and memory. The root complex has some number of ports, each defining a separate *hierarchy domain*. Each of these hierarchy domains consists either of a single *endpoint* or a number of endpoints connected together through one or more *switches*.

Endpoints represent what we typically think of as PCIe peripherals – for example, NICs and GPUs – as well as peripherals that are integrated into the root complex, or peripherals that are chips soldered onto the motherboard elsewhere.

In order to maintain backwards compatibility, PCIe switches are represented conceptually as a collection of PCI-PCI bridges, one for each port of the switch. A switch has one

#### 2 BACKGROUND

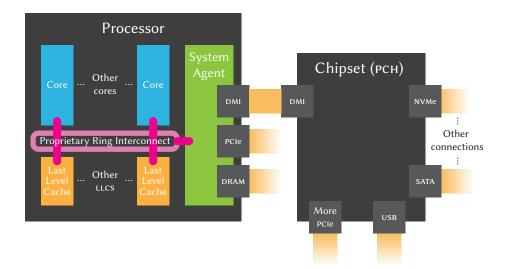

Figure 2.2: PCIE ID Layout. PCIE now supports an 'Alternative Routing ID' format, but we have not seen this used it in practice.

upstream port, which connects towards the root hub, and several downstream ports, which connect away from it. Often, upstream ports connect directly to the root hub, and downstream ports directly to peripherals, but they may connect to other PCIe switches or bridges of various types. The ports connect to an internal logical bus that represents the routing logic of the switch in terms of the PCI protocol.

The unit of communication at the transaction layer is the *Transaction Layer Packet*, or TLP. At the top level, TLPs are categorised into *requests* and *completions*. Requests are further categorised based on the address space they target, which is one of memory, 10, or configuration; and whether they are a request to read from or write to the space. Requests may also be of a special type, *message*, which are largely concerned with protocol bookkeeping. Completions may carry data with them, but don't necessarily. A completion is only generated in response to some sort of request. If a request is made to an endpoint that it cannot fulfil in accordance with the specification, then a special completion is returned – an *unsupported request response*.

The behaviour of the configuration space is defined by the PCIe specification, and as such covers behaviour that is common to many different peripherals. The memory space is used for interaction in a device-specific way. Peripherals can access system memory – that is, perform DMA – by making memory requests to the root complex. The IO space is included for backwards compatibility, so while it is not technically deprecated the PCIe specification states that it may be at some point.

TLPS are divided into header and data sections. The header section of a TLP is structured according to the PCIe protocol. It is interpreted both by the component that is the target of the TLP, and also by the switches on the interconnect to make routing decisions. The data section is opaque to the protocol, and is only given semantic meaning by the endpoints. Not every TLP has a data section. Of those that do, the TLPs that interact with configuration or 10 space have a fixed-length data section; the TLPs that interact with memory, a variable-length data section.

Configuration requests are addressed with PCIE IDS. These are sixteen bit values consisting of an eight bit bus number, a five bit device number, and a three bit function number, as illustrated in Figure 2.2. This format is inherited from PCI. PCIE IDS correspond to a physical slot for a device. Each switch 'knows' the IDS of the peripherals attached to it, and only forwards configuration TLPS with the appropriate IDS. Peripherals are expected to derive their IDS by reading the destination field of the TLPS they receive.

The configuration space defines several fields that are common to every endpoint. These include, for example, information about the model number of the device. It also includes two linked-lists of *capabilities*. These are not capabilities in the unforgeable-token-of-authority sense, but rather features that a device has. There are two linked-lists as one is inherited from PCI, while the other is PCIE specific. The inherited linked-list is simply known as the *capability list*; the new one is the *extended capability linked-list*. The configuration address of the start of the capability list is presented by the device in a register in configuration space. The address of the start of the extended capability list is fixed by the PCIE specification.

IO and memory requests are routed by address. Each PCIe peripheral defines a number of *Base Address Registers* (BARS) in its configuration space header. These are used to designate areas

of address space that the card inhabits. Somewhat confusingly, the on-device memory that is mapped into host address space starting at the address written into a BAR is commonly referred to simply as a BAR. It is worth noting that on-device 'memory' is something of a misnomer. Devices typically assign complex semantics to *registers* within their memory space. For example, repeatedly reading the same register may result in an internal FIFO being dequeued. When allocating address space for a device, the system probes each BAR in turn. First, it writes the current BAR to all ones. It then reads it back. As the address of a BAR has to be aligned to its size, some number of low bits of the BAR will have been forced to zero. From this, the system can determine the size of the BAR.

In general, a device that is able to make requests of other devices is known as a *master*. In true buses, mastering is a special feature, granted to the CPU and perhaps certain privileged peripherals. This helps to keep down complexity: as soon as multiple devices can make requests, there must be an arbitration scheme to decide which device is permitted to make a request at any given time, and this scheme will typically scale in complexity along with the number of masters in the system. In PCIE, memory requests are just another type of TLP, and can be generated by any device on the system. Decisions about arbitration are made using a flow control system to throttle devices that are unfairly using system resources.

Each PCIe device has a *bus master enable* bit as part of the command register in its configuration space. The PCIe specification states that if the bit is zero, the device is not allowed to issue memory or 10 requests. However, it is unclear whether this behaviour is enforced. Root and switch ports also have the bit, and will not forward upstream requests if it is zero, but again, it is unclear if the host makes use of this as an policy enforcement mechanism in practice. While the bit is zero by default at power on, we have found that hosts quickly enable it.

To prevent the processor from having to repeatedly read from a device register to determine if an event of interest has occurred, internal interconnects implement *interrupts*. An interrupt is a signal that a device can trigger in order to disrupt processor control flow so that an event can be handled soon after it has occurred. PCIe has three separate interrupt implementations. The first is a legacy mode, designed for backwards compatibility with PCI, that sends a special message request TLP which is a simulation of a physical interrupt wire on PCI. The other two are both considered current, and are variants of *Message Signalled Interrupts* (MSI and MSI-X). Both operate via generic memory write TLPs to special memory addresses. Information about the level of MSI or MSI-X support that a device has is encoded in capabilities in its configuration space. The use of a memory write packet allows metadata to be carried with an interrupt. This usually encodes the cause of the interrupt as an ID, so writes of different values to the same memory location can signify 'different interrupts'. For example, a NIC might have separate interrupts to signify that a packet has arrived and that it has transmitted the packets assigned to it by the host.

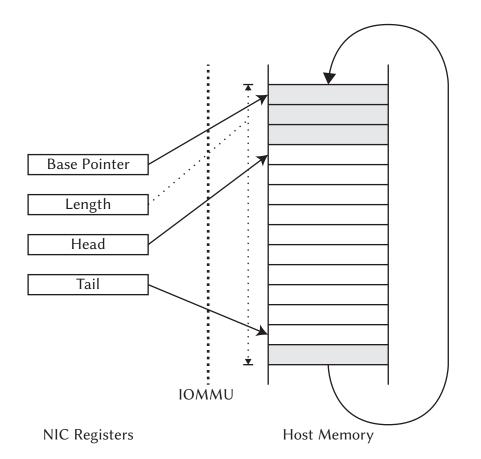

## Address Translation Services

The addresses associated with memory requests made to the root complex do not necessarily refer directly to physical locations in memory. They may be translated by an IOMMU, as described in Section 2.1, but this carries with it a performance overhead. To ameliorate this performance overhead, PCIe allows a peripheral to cache its translations on the device itself. This feature is known as *Address Translation Services* (ATS). It is not entirely straightforward. To be able to store translations, a device must be able to request mappings from the host, and the host must be able to communicate to the device when this mapping is no longer valid. A device

## 2 BACKGROUND

| 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 | 1 0 |

|-------------------------------------------------------------------------------------|-----|

|-------------------------------------------------------------------------------------|-----|

|                      | Next Capability Offset | CV | атs Extended Capability ір |  |

|----------------------|------------------------|----|----------------------------|--|

| ATS Control Register |                        | r  | атs Capability Register    |  |

Figure 2.3: ATS Extended Capability. CV is the capability version. The control and capability registers are further divided into subfields. Only relevant here is bit 15 of the control register, the enable bit.

| Value | Meaning                 | Description                                                                                                                                             |

|-------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00    | Untranslated.           | For backwards compatibility with the reserved bits, which have a value of zero.                                                                         |

| 01    | Translation<br>Request. | The host returns the translated value of the address as a read completion.                                                                              |

| 10    | Translated.             | The address of the transaction has been translated on the device.<br>The host will not pass the memory address of the transaction<br>through the IOMMU. |

| 11    | Reserved                | Host will return an unrecognised request.                                                                                                               |

Table 2.1: Meanings of the AT field in a PCIe header.

that supports ATS must present the ATS Extended Capability structure, shown in Figure 2.3.

In order to specify that a request has been translated, the ATS specification repurposes two previously reserved bits of the PCIe header to become an *Address Type* (AT) field. The meanings of each possible value of the AT field are given in Table 2.1.

# Access Control Services

It was recognised relatively early on that the ability of every component in the system to communicate independently with each other had problematic security implications. In 2005, the 'PCI Express Access Control Services' (ACS) specification was released [65]. This is a set of optional features – in practice, even in 2017 we found implementations only on high-end server machines. The features are:

- *Source Validation* Ports, which either connect directly to a peripheral, or to a bridge, must test that requests they forward have a source ID that is within the range of IDs attached to the port. This is necessary as PCIe makes it the responsibility of the endpoint to set the source ID to a valid value. This mechanism can prevent certain attacks where a malicious device sends TLPs that appear to come from another device on the system [76].

- *Translation Blocking* Makes switches block requests that have a 'non-default' AT field. As the default value is 0, this blocks all requests for translations, and all requests that are marked as having been translated on-device.

- *P2P Redirect Features* The remaining features combine to force all requests and their respective completions to go through the root complex, even when a more direct peer-to-peer path is available. This prevents devices from illegally accessing peers they are forbidden access to by bypassing the IOMMU, which is found in the root complex.

## 2.4 THUNDERBOLT

Thunderbolt is a proprietary high performance external peripheral interconnect. It first appeared as part of a consumer product in February 2011. Despite being proprietary, it is known to carry the PCIe protocol, and there are a number of chassis allowing a generic PCIe card to be plugged into a Thunderbolt port.

Thunderbolt versions 1 and 2 saw limited uptake, with ports included in large numbers only on Apple laptops. This may be due Thunderbolt's lack of backwards compatibility with other interconnects, and a lack of a pressing use case. However, Thunderbolt 3 has seen more uptake, appearing in the high-end laptops from a number of manufacturers. Thunderbolt 3 uses the USB-C connector, rather than the Mini DisplayPort connector of previous generations.

Thunderbolt 3 provides a data rate of 40Gbit/s, in comparison to USB 3.1's 10Gbit/s. The use of Thunderbolt and USB on the same port may lead to confusion for the consumer. For example, USB-C ports on a computer are not guaranteed to support Thunderbolt, and cables with USB-C connectors are also not guaranteed to be able to carry Thunderbolt signals.

USB-C ports may also implement *USB power delivery*, allowing up to 100W to be supplied to or from the port. This means that the same port that is used to charge a laptop may also grant DMA.

## 2.5 NETWORK INTERFACE CONTROLLERS

Some of the exploits we cover rely on an implementation of a Network Interface Controller (NIC) so a basic grounding in what NICs are, and how they communicate with their host is pertinent. NICS are an extremely common form of peripheral that allow a computer to connect to a Local Area Network (LAN), often with the purpose of then connecting through a gateway to the internet. It would be astonishing to find a personal computer of any type without some form of NIC, and increasing numbers of non-personal computers have one to enable them to take part in the 'Internet of Things'. NICs have been around for a long time in the context of computer science, predating the PC. The development of Ethernet, the earliest LAN standard, and predecessor to the most-widely-used current wired LAN, began in 1973; the Cambridge Ring in 1974 [57, 61]. NICs are created by many different manufacturers, and come in many forms, from components in systems-on-chip to discrete integrated circuits on motherboards and pluggable expansions cards operating over PCIe, USB and Thunderbolt. They are built with a wide range of differing requirements. They may implement an old and well-understood technology, needing to make no particular guarantees about performance, or may be an implementation of a bleeding-edge protocol where nanoseconds are important. They can exhibit complex behaviour. Applications on the host and in the network can generate data in totally unpredictable patterns, and the host needs to react to network data, potentially at the same time as having to saturate the NIC with traffic at a rate that may require the transfer of multiple bytes per processor clock cycle.

These factors make a NIC a likely choice for a model peripheral to use to carry out an attack. In order to attempt to handle such a broad spectrum of requirements in a uniform way, the kernel code for interacting with NICs is complex, and therefore liable to suffer from bugs. Before starting implementation, we had a good idea that a feature of the network stack shared across macOS and FreeBSD was likely to lead to vulnerabilities. This is detailed in Section 5.1. On top of this, we knew the QEMU full system emulator had a software model of a NIC that we could potentially transplant. We describe this process in Section 4.4.

Perhaps surprisingly, given the range of different requirements, most NICs use the same

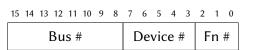

basic interface to communicate with the host, although each device has individual differences. The basic mechanism is that of descriptor rings. These come in two broad types: transmit and receive rings. Both work in broadly similar ways. Rings are contiguous areas of host memory that consist of a circular list of *descriptor records*, which contain a small amount of metadata about a fragment of packet to send, consisting of at least an 10 base address and a length. The card is told about the locations of the rings by writes to registers in memory space. When the host has a set of packets to send, it populates the transmit ring with pointers to packet data in memory. It then notifies the card that it has data to send by updating the register specifying the end of the ring as appropriate. Depending on the card's configuration, it will trigger an interrupt to the host when it is done. Receive rings behave in a similar way, except the host populates the rings with buffer addresses that it expects the card to write received data into. This is shown diagrammatically in Figure 2.4: figures similar to this are almost mandatory wherever descriptor rings are explained.

Variants of this simple scheme are possible, and are particularly prevalent in higher performance devices. For example, while packets at the IP layer are not connection-orientated, many IP packets will form part of TCP flows, which are. An advanced NIC may have separate descriptor rings for separate TCP flows and disambiguate between them on the card, rather than the host.

### 2.6 IOMMUS

A regular MMU maps from virtual addresses to physical addresses: an IOMMU maps from *IO Virtual Addresses* (IOVAS) to physical addresses. Similarly to regular MMUS, IOMMUS have a variety of purposes, including virtualisation and security. The protection offered by a particular usage mode of an IOMMU may be said to be either inter-os, or intra-os. Inter-os protection stops a malicious os or peripheral running within a hypervisor from attacking other oss within the same hypervisor; intra-os protection stops a malicious peripheral from attacking its host.

The idea of a specialised piece of hardware for rewriting 10 is not new. The IBM System/360, which was introduced in 1964, used *channels* for 10, highly specialised cores with an instruction set designed to facilitate memory copying [8]. This idea was also seen in the CDC 6600, introduced in 1965, which had a collection of ten *peripheral processors*. These shared execution units, and executed in a *barrel* configuration [19]. In this configuration, each execution unit in the pipeline executes part of an instruction from a successive processor each cycle. This idea is similar to some variants of *multithreading* in modern processors.

There are many differences between the situation then and now. Now, different components of the computer are made by different companies, rather than the computer being built from the ground up by one company. This has led to the replacement of concepts like peripheral processors with logic on the chip that accesses host memory by DMA. Nonetheless, viewing the IOMMU as a device that rewrites IO data arguably makes it a distant descendant of these processors.

One of the earliest actual IOMMUS appeared in Sun's 'sun4m' platform, which was the basis for a series of workstation PCs sold from 1992-1999. Linux has support for this IOMMU, but it is unclear what Sun's rationale was for using it at this time. Early bus protocols supported a narrower address format than some of the PCs that they appeared in. This meant that peripherals could only access a restricted area of the address space. If the kernel allocated buffers in an area the device did not have access to, then the data in the buffers had to be

Figure 2.4: Diagram of Descriptor Ring, based on those of an Intel 82574L NIC. The registers contain addresses in host memory as IOVAS. The following descriptions describe the case for a receive ring. Each receive descriptor also contains an address in host memory as an IOVA, a length and some metadata. When the NIC receives data it places it into the buffer described by the head pointer. If this fills that buffer, the NIC advances the head pointer. When the NIC needs more buffer space, the host allocates buffers, places their IOVAS and lengths in the descriptors after the tail pointer, and increments the tail pointer. The buffer is circular: if the tail pointer has a smaller address than the head pointer, the buffer wraps around.

copied to an area the device did have access to. This process, which reduced performance, was called *bounce buffering* [12]. Early IOMMUS are frequently described as a higher-performance alternative to bounce buffering, and improving IO performance may have been the reason behind Sun's IOMMU implementation. Linux uses the Sun IOMMU by tying it to the API for allocating device memory buffers, so it provides some per-device isolation.

Another early IOMMU was part of the *Accelerated Graphics Port* (AGP) specification, which was released in 1996 and gradually phased out with the introduction of PCIe in 2004. The AGP IOMMU was called the *Graphics Address Remapping Table* (GART). Its purpose was to allow the graphics card to have a contiguous view of large sections of host memory. This simplified access to, for example, texture data, which might have been in physical memory across several non-contiguous pages.

A later юмми implementation appears on вм's xSeries x366 and x460 servers, which appeared in 2005. Again, Linux has support for this юмми. The ксопfig documentation,

which describes the features that can be compiled into the Linux kernel, states that the IBM IOMMU exists to allow 32-bit PCI devices to work on systems with more than 3GiB of RAM, and also that it provides isolation benefits in order to catch bugs and find misbehaving drivers [82]. The IBM servers implementing the IOMMU use commodity x86 processors: the IOMMU is implemented in PCI-x bridges on the chipset. PCI-x is an early successor protocol to PCI. It is a direct extension of PCI, rather than the ground-up rebuild of PCIe. Its precise details are not relevant. Based on the marketing documents available online, the IOMMU was not a marquee feature of these servers.

ARM also have a specification for an IOMMU, called the *System Memory Management Unit* (SMMU). As there are no currently-widely-used ARM systems with external peripheral interconnects that support DMA, we have not thoroughly investigated the SMMU. However, we are beginning to see phones that have a USB-C port into which can be plugged a keyboard, monitor, and mouse to provide a PC-like experience. If this form factor catches on, it seems plausible that Thunderbolt support will be added, and the protection offered by the SMMU will be important.

#### vт-d

The IOMMU that we focus on attacking is part of 'Intel Virtualization Technology for Directed I/O' (VT-d) [41]. The VT-d specification includes several distinct features: IO device assignment, to give VMs direct access to peripherals; DMA Remapping (DMAR), which includes the IOMMU; interrupt remapping; and 'reliability features'. Based on our analysis of recent processor IOMMU support, detailed in Section 3.1, we believe this to be the most widely deployed implementation of a PC IOMMU.

Intel suggest a variety of uses for their IOMMU. A number of these are os use patterns: protecting vital os internals from all IO devices; the use of 32-bit devices in a 64-bit host; isolating each device, so that it has the minimal necessary access to host memory; and allowing devices to share a virtual address space with user level programs. They also suggest that the IOMMU can be used for mapping a peripheral directly into a *Virtual Machine* (VM) from its *Virtual Machine Manager* (VMM).

To perform remapping, platforms with vT-d provide one or more *DMA Remapping Hard-ware Units* (DRHUS). Each DRHU is responsible for remapping requests from different devices. DRHUS interpose between peripherals and main memory, performing look-ups of the virtual address provided by the peripheral, and re-writing the transaction with the corresponding physical address if a mapping is provided, or returning an unsupported request response if none is found.

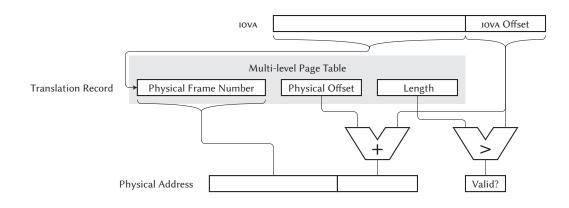

A page-based system, like the vT-d IOMMU, only translates the top bits of the address, translating a *frame number* to a *page number*. The bottom bits, which specify an offset within a page, are the same in the translated and untranslated address.

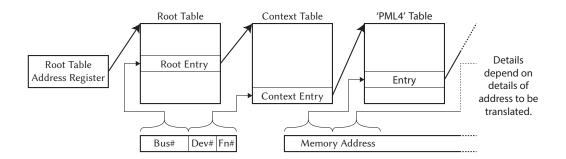

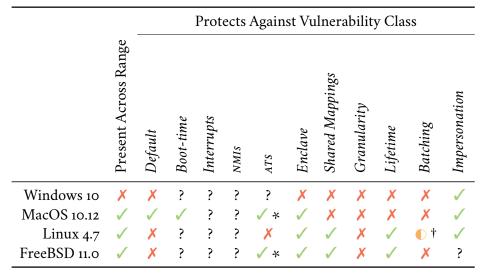

The DRHUS are configured by a multi-level page table, as shown in Figure 2.5. As these tables configure *DMA Remapping*, they are frequently referred to as the DMAR tables. The top level structure is the *root table*, which is populated with *root entries*. The root table occupies one 4KiB page, and contains 256 128-bit entries. The first step in translating a request from a given peripheral is to index the root table with the request's PCIe bus number, giving a root entry. Each root entry table contains a present flag, indicating that the translations are present for the device, and a pointer to the next table in the hierarchy, the *context table*.

Like the root table, context tables each fill one 4KiB page, and contain 256 128-bit entries. They are indexed by the device and function numbers of the relevant PCIE requester ID. Each

Figure 2.5: Diagram showing the page tables for Intel  $v\tau$ -d. The AMD table layout is similar, but the entirety of the PCIe requester ID indexes one much larger table – the first root table and context table are combined.

entry contains a pointer to a further *hierarchical translation structure*, and various metadata bits. vT-d makes use of the concept of *domains*, non-intersecting areas of address space that a given hardware device may be assigned to – that is, be able to read or write. The context entry metadata includes a *domain identifier*, such that devices assigned to the same domain must have equal domain identifiers, and it is recommended that devices that make use of the same page tables explicitly have identical domain identifiers, 'for best hardware efficiency'.

The root and context tables both support an *extended mode*. These modes use 256-bit entries in order to translate PCIe requests that specify a targeted *Process Address Space Identifier* (PASID), and to hold some additional attributes. In practice, we have not seen these features used.

The layouts of the hierarchical translation structures vary. Firstly, systems can have different address widths, and smaller addresses require fewer levels of table to translate. Additionally, vT-d has support for *large pages*, which are 2MiB or 1GiB in size. Each step of larger page size reduces the number of tables that need to be indexed by one, with the possible sizes of large page deliberately chosen for this to be the case. The largest – and indeed, standard – number of tables that need to be walked to carry out the translation is six, including the two tables to find the per-device hierarchical translation structure. This corresponds to two translations to find the address of the hierarchical translation structure from the PCIE ID, then the use of four successive 9-bit chunks of IOVA to index successive levels of the hierarchical translation structure, which results in a 36-bit physical page number, which is in turn spliced with the bottom 12-bits of the IOVA, resulting in a 48-bit physical address.

Performing a six-level page lookup for each request would carry a large performance penalty, so VT-d specifies several varieties of cache in order to improve performance. The two most relevant are the *context cache* and the IOTLB. The context cache caches context entries, which are used to specify the hierarchical translation structures for a device based on its source ID. The IOTLB caches translations from IO virtual frame number to physical page number. IOTLB cache entries are tagged by source ID to allow translation requests from different devices to be disambiguated, and by the upper bits of the requested address. They may also be tagged by domain ID to allow batch invalidation of entries associated with a given domain.

If a device attempts to carry out a translation for which no mapping exists – a *translation fault* – the IOMMU returns with an unsupported request response. It also records some data about the fault in a *fault recording register*: the IOMMU can have an implementation specific number of these, from one per DRHU up to 256. An implementation may also support *advanced*

*fault logging*, which writes to a log in host memory. On a fault, the IOMMU also raises an interrupt to the host. The IOTLB can cache translation faults, meaning that it explicitly remembers that requests with specific tag bits are invalid.

There are two mechanisms for invalidating cached translation entries: a legacy registerbased interface, and the current *queued invalidation interface*. These cannot both be active at the same time. Both mechanisms allow all entries to be revoked simultaneously, all entries in a given domain to be revoked simultaneously, and for individual pages to be revoked sequentially. The register-based interface operates synchronously, while the queued invalidation interface is asynchronous and uses a circular buffer of *invalidation descriptors* in host memory.

The specification does not suggest specific designs for the IOTLB. Instead, this is left up to the implementer and hidden from software.

VT-d specifies support for 'Device TLBS', in accordance with the PCIE ATS specification, described in Section 2.3.

#### AMD-V

AMD also have have an IOMMU specification, and a number of partial solutions to the same problems solved by an IOMMU, which predate their system-wide IOMMU. These include the AGP GART, as described in Section 2.6, and also a feature called the *Device Exclusion Vector* (DEV) [7], which first appeared in 2005. The DEV added a mechanism whereby the host bridge, which connects the CPU to high performance peripherals and RAM, can mark areas of memory as being accessible to either all devices or no devices. The DEV is implemented as a bit field, where each bit corresponds to a 4KiB page of physical memory. When a request comes in, the appropriate bit is looked up and checked: if the bit is unset, the request is dropped. A register specifies the location of the bit field in memory.

This mechanism has some appealing features: it is simple and easy to understand, and the metadata corresponding to a given page is located in only one location and can be found quickly. It does have several disadvantages when compared to a fully fledged IOMMU, however. The two principal downsides are that it does not allow address remapping or per-device exclusion. These limitations will be explored in more detail in Section 3.1, as they are reflected in the way that certain oss use the IOMMU.

Both DEV and AMD's full IOMMU fall under the umbrella of virtualisation technology, which AMD shorthand as 'AMD-V'. AMD's rationale for their IOMMU includes the use of 32-bit devices on 64-bit systems. They also claim that it provides 'more secure' use of peripherals in systems running VMs, and allows use of a peripheral to be granted directly to a user-level application. They specify that the IOMMU may have support for Device TLBS.

The AMD IOMMU is almost identical to Intel's. The principal difference is that they have only one table mapping from PCIE device IDS, rather than two levels of table. It uses 256-bit entries, and may be up to 2MIB in size in order to cover the whole PCIE space. This sacrifices memory space efficiency for eliding one memory read in the IO page table lookup. Given that most modern PCs have many gigabytes of memory and memory accesses are comparatively slow, this seems a reasonable trade off. Other than this, the two designs are essentially the same, at least to the level of detail that we have covered vT-d. The AMD IOMMU is also controlled via a circular buffer, which is primarily used to invalidate entries. *Events*, including translation faults, are reported in an *event log* in system memory. The IOMMU can be configured to trigger an interrupt in response to the occurrence of an event.

Again, there is support for the implementation of an IOTLB. AMD explicitly say that they expect most will use a set-associative structure, but they are not prescriptive. They recommend

a two-stage organisation: the first stage mapping a device ID to a domain and IO page table base address, the second mapping a domain ID and device virtual address to a system physical address and protection. They recommend that the former can be small, but should have high associativity or a very good hash to spread the clustered nature of device IDs, and the latter should be large. They also recommend the use of the domain ID in hashing so that multiple domains with similar layouts don't compete.

## 2.7 CONTROL FLOW VULNERABILITIES AND EXPLOITS

In our work, we use a malicious peripheral to modify the control flow on the processor. At first glance, being able to force one return statement or function pointer to branch to a different location is not necessarily a severe vulnerability. However, there is a long-running and on-going strand of research concerned with escalating minimal control of a processor into the ability to execute arbitrary code. Defences designed to prevent these attacks are also effective against some of our exploits, and the approaches to privilege escalation they use are also relevant to our work.

A widespread class of early control-flow-hijack attacks are *buffer overflow* attacks [21]. These operate by finding a string input to a program that is not properly length checked. A malicious user can input a string longer than its allocated buffer, which overflows and overwrites the return address on the stack. When the CPU returns from the currently executing function, it branches to an address of the user's choice. As part of their payload, the user could include code that they wanted to run, and set the return address to point to this code.

Various mitigations have been implemented to thwart these attacks. One of the simplest is *Write xor Execute* ( $W \oplus X$ ). This uses the conventional MMU to ensure that either a page can be written to by user-mode code, or code located on the page can be executed, but not both. This prevents an attacker from being able to execute any code path that isn't already included in the running binary.

It turns out that this is not a sufficient protection measure. In the late 90s, a patch was made available for Linux that introduced the concept of a *non-executable stack*, with similar protection being implemented on Sun's Solaris. Attacks against these measures appeared on mailing lists, bug-trackers, and 'underground' hacking magazines [23, 91, 56, 62]. These attacks revolved around the idea of subverting a return instruction in order to carry out an unexpected function call, rather than to branch to user-provided code. As the usual targets were functions in libc, these attacks are often known as *return-into-libc* attacks. An example attack sequence writes some code to be executed into an area of address space, then uses the mprotect system call in order to switch the area's permissions from 'write' to 'execute', then branch to this area.

This work did not see much interest from the academic community until 2007, possibly because it was not published in a traditional venue. In 2007, the approaches taken by returninto-libc attacks were generalised into *Return-Oriented Programming* (ROP) attacks. [79, 72]. These assume an attacker with the ability to add several addresses to the return address stack, which is possible by exploiting a buffer overflow, and a target system running a known binary. In a ROP attack, the attacker scans the target binary for *gadgets*. These are short sequences of code followed by a return statement. The program that the attacker wants to run is broken down into a sequence of gadgets, then the addresses of those gadgets are pushed to the stack in reverse order, so that the address of the piece of code that should be executed first appears at the top. Then, the attacked function is allowed to return. Instead of returning to the caller, the CPU reads the gadget's address from the top of the stack, and branches to and executes that code. When that has executed, it calls return, and so the next address executed is that of the next gadget, and so on. It turns out that in practice even quite modestly sized binaries contain enough gadgets for arbitrary code execution – a set of gadgets that provide Turing completeness. A standard approach is to carry out a ROP attack against the Standard C Library, which is included in almost all C language applications. Gadget search is helped by the x86 architecture's variable length instructions, which means that the processor can be made to branch to the middle of another instruction, and interpret it to be an entirely different instruction.

Some early defences against ROP attacks operated by either detecting return instructions that occurred more frequently than would be expected in legitimate code, or by detecting return instructions that were executed without a corresponding call instruction having been issued. However, in 2010, Checkoway et al. observed that an actual 'return' instruction is not actually necessary to carry out a ROP-style attack [17]. They observe that the properties of the return instruction that enable ROP attacks are that they transfer control of execution by an indirect jump, and that they update processor state so that a subsequent return will not transfer execution back the expected path of the program. Sequences of instructions that have these properties and are not return instructions occur far less frequently than returns, so it is not possible to find a set of gadgets that end in an appropriate sequence of instructions, as it is with returns. Instead, they use a *trampoline* to update state and redirect control flow, where each sequence of instructions that they use as a gadget ends in an indirect jump that can be redirected to this trampoline. Their attack does not work simply with libc, but does work with Mozilla's libxul, which is distributed with Firefox and Thunderbird, and with PHP's libphp.