Technical Report

Number 832

**Computer Laboratory**

# Communication centric, multi-core, fine-grained processor architecture

Gregory A. Chadwick

April 2013

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500

http://www.cl.cam.ac.uk/

© 2013 Gregory A. Chadwick

This technical report is based on a dissertation submitted September 2012 by the author for the degree of Doctor of Philosophy to the University of Cambridge, Fitzwilliam College.

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

http://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986

# Abstract

With multi-core architectures now firmly entrenched in many application areas both computer architects and programmers now face new challenges. Computer architects must increase core count to increase explicit parallelism available to the programmer in order to provide better performance whilst leaving the programming model presented tractable. The programmer must find ways to exploit this explicit parallelism provided that scale well with increasing core and thread availability.

A fine-grained computation model allows the programmer to expose a large amount of explicit parallelism and the greater the level of parallelism exposed the better increasing core counts can be utilised. However a fine-grained approach implies many interworking threads and the overhead of synchronising and scheduling these threads can eradicate any scalability advantages a fine-grained program may have.

Communication is also a key issue in multi-core architecture. Wires do not scale as well as gates, making communication relatively more expensive compared to computation so optimising communication between cores on chip becomes important.

This dissertation presents an architecture designed to enable scalable fine-grained computation that is communication aware (allowing a programmer to optimise for communication). By combining a tagged memory, where each word is augmented with a presence bit signifying whether or not data is present in that word, with a hardware based scheduler, which allows a thread to wait upon a word becoming present with low overhead. A flexible and scalable architecture well suited to fine-grained computation can be created, one which enables this without needing the introduction of many new architectural features or instructions. Communication is made explicit by enforcing that accesses to a given area of memory will always go to the same cache, removing the need for a cache coherency protocol.

The dissertation begins by reviewing the need for multi-core architecture and discusses the major issues faced in their construction. It moves on to look at fine-grained computation in particular. The proposed architecture, known as Mamba, is then presented in detail with several software techniques suitable for use with it introduced. An FPGA implementation of Mamba is then evaluated against a similar architecture that lacks the extensions Mamba has for assisting in fine-grained computation (namely a memory tagged with presence bits and a hardware scheduler). Microbenchmarks examining the performance of FIFO based communication, MCS locks (an efficient spin-lock implementation based around queues) and barriers demonstrate Mamba's scalability and insensitivity to thread count. A SAT solver implementation demonstrates that these benefits have a real impact on an actual application.

# Acknowledgments

Firstly, I would like to thank my Supervisor Simon Moore. Not only for his valuable guidance and advice during my PhD but for his support and teaching from when I first came to know him as an undergraduate. From the time I timidly requested to borrow an DE2 board in the Part 1B ECAD labs for my own self study he always given me the freedom to follow my ideas.

No work is ever done in isolation and my friends and colleagues in the computer architecture group have provided many useful hours of discussion and advice. I must give particular thanks to Arnab Banerjee for his Bluespec implementation of the network I used as well as Theo Markettos for his proof reading of this dissertation.

Finally I would like to thank my family for their support and my friends, for making my time at Cambridge so enjoyable.

# Contents

| 1        | Intr | oducti  | on                                                                                                          | 17 |

|----------|------|---------|-------------------------------------------------------------------------------------------------------------|----|

|          | 1.1  | Overv   | iew                                                                                                         | 17 |

|          | 1.2  | Thesis  |                                                                                                             | 18 |

|          | 1.3  | Outlin  | e                                                                                                           | 19 |

|          | 1.4  | Publis  | hed work                                                                                                    | 19 |

|          | 1.5  | Contri  | butions                                                                                                     | 20 |

| <b>2</b> | Bac  | kgrour  | ad                                                                                                          | 21 |

| -        | 2.1  | 0       | al connections                                                                                              |    |

|          | 2.1  | 2.1.1   | Off chip connections                                                                                        |    |

|          |      |         | -                                                                                                           |    |

|          | 0.0  | 2.1.2   | Going beyond wires                                                                                          |    |

|          | 2.2  |         | onnect architecture                                                                                         |    |

|          | 2.3  |         | ectural communication                                                                                       |    |

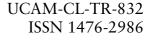

|          |      | 2.3.1   | Cache coherency                                                                                             |    |

|          |      | 2.3.2   | Message passing                                                                                             | 28 |

|          |      | 2.3.3   | Consistency                                                                                                 | 29 |

|          | 2.4  | Softwa  | are communication $\ldots$ | 31 |

|          |      | 2.4.1   | Locks, barriers and notification $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                  | 32 |

|          |      | 2.4.2   | Partitioned global address space                                                                            | 33 |

|          | 2.5  | Existin | ng architectures                                                                                            | 33 |

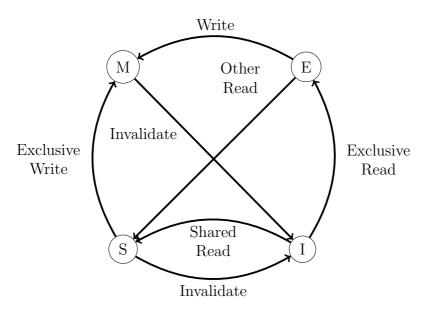

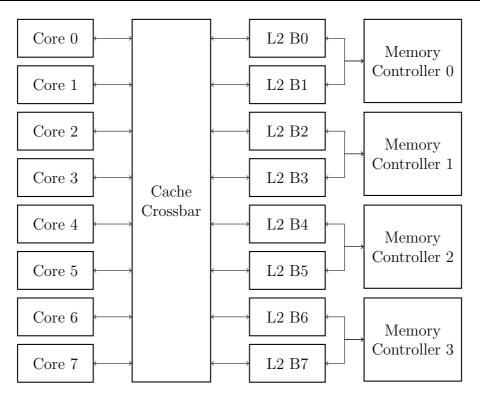

|          |      | 2.5.1   | Sandy Bridge                                                                                                | 34 |

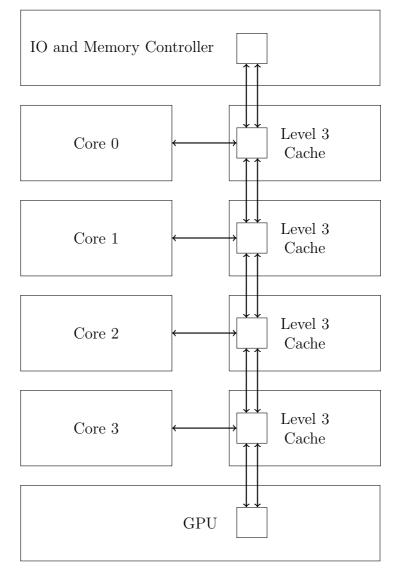

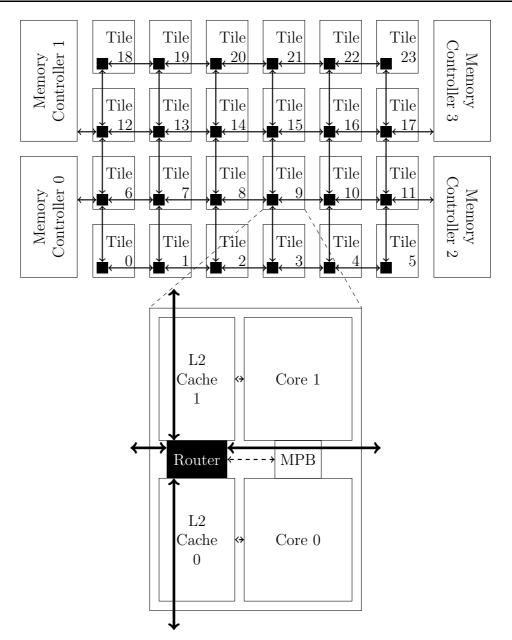

|          |      | 2.5.2   | Tile Architecture                                                                                           | 35 |

|          |      | 2.5.3   | Single-chip Cloud Computer                                                                                  | 38 |

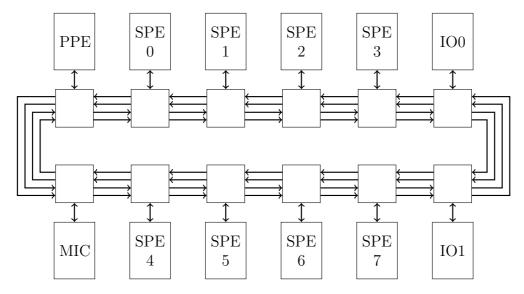

|          |      | 2.5.4   | Cell Broadband Engine                                                                                       | 40 |

|          |      | 2.5.5   | Niagara Architecture                                                                                        | 42 |

|          |      | 2.5.6   | Tile based, application dedicated architecture                                                              | 43 |

|          | 2.6  | Summ    | ary                                                                                                         | 44 |

| 3 | Fin | e-grain | ed computation                                                                                            | 45 |

|---|-----|---------|-----------------------------------------------------------------------------------------------------------|----|

|   | 3.1 | Amdal   | nl's Law                                                                                                  | 45 |

|   | 3.2 | Fine-g  | rained software $\ldots$ | 46 |

|   |     | 3.2.1   | Message passing                                                                                           | 47 |

|   |     | 3.2.2   | Lightweight threads                                                                                       | 47 |

|   |     | 3.2.3   | Software transactional memory                                                                             | 48 |

|   | 3.3 | Fine-g  | rained hardware                                                                                           | 48 |

|   |     | 3.3.1   | SIMD                                                                                                      | 48 |

|   |     | 3.3.2   | Hardware threading                                                                                        | 50 |

|   |     | 3.3.3   | Hardware transactional memory                                                                             | 51 |

|   |     | 3.3.4   | Hardware synchronization                                                                                  | 51 |

|   |     | 3.3.5   | Full / empty bits                                                                                         | 54 |

|   | 3.4 | Summa   | ary                                                                                                       | 55 |

| 4 | Ma  | mba ar  | chitecture                                                                                                | 57 |

|   | 4.1 | Overvi  | ew                                                                                                        | 57 |

|   |     | 4.1.1   | Interconnect                                                                                              | 58 |

|   |     | 4.1.2   | Architectural communication                                                                               | 58 |

|   |     | 4.1.3   | Software                                                                                                  | 59 |

|   | 4.2 | The pr  | rogramming model                                                                                          | 59 |

|   |     | 4.2.1   | Activation frames                                                                                         | 60 |

|   |     | 4.2.2   | Presence bits                                                                                             | 61 |

|   |     | 4.2.3   | Initialisation, exception handling and cleaning up                                                        | 65 |

|   | 4.3 | The M   | amba system                                                                                               | 66 |

|   | 4.4 | The pr  | cocessor core                                                                                             | 68 |

|   |     | 4.4.1   | The pipeline                                                                                              | 70 |

|   |     | 4.4.2   | Memory actions                                                                                            | 74 |

|   |     | 4.4.3   | Scheduling                                                                                                | 83 |

|   |     | 4.4.4   | The caches                                                                                                | 84 |

|   |     | 4.4.5   | The network                                                                                               | 85 |

|   |     | 4.4.6   | Profiling                                                                                                 | 86 |

|   | 4.5 | FPGA    | Implementation                                                                                            | 87 |

|   | 4.6 | Summa   | ary                                                                                                       | 89 |

| <b>5</b> | Soft | ware t  | echniques                   | 91  |

|----------|------|---------|-----------------------------|-----|

|          | 5.1  | Primit  | ives                        | 91  |

|          |      | 5.1.1   | Basic spin lock             | 91  |

|          |      | 5.1.2   | Acquiring locations         | 91  |

|          |      | 5.1.3   | Notify nodes and chains     | 92  |

|          |      | 5.1.4   | FIFO communication          | 100 |

|          | 5.2  | A SAT   | Solver implementation       | 104 |

|          |      | 5.2.1   | SAT problem                 | 104 |

|          |      | 5.2.2   | SAT solver algorithm        | 105 |

|          |      | 5.2.3   | Parallelizing the algorithm | 106 |

|          | 5.3  | Summ    | ary                         | 106 |

| 6        | Eva  | luatior | 1                           | 109 |

|          | 6.1  | Metho   | dology                      | 109 |

|          | 6.2  |         | 54 comparison system        |     |

|          |      | 6.2.1   | The software scheduler      | 110 |

|          | 6.3  | Softwa  | are tool chain              | 111 |

|          | 6.4  | Netwo   | rk and Memory performance   | 113 |

|          |      | 6.4.1   | Network Message Size        | 114 |

|          | 6.5  | Area a  | and memory utilisation      | 114 |

|          |      | 6.5.1   | Timing Overheads            | 116 |

|          | 6.6  | The b   | enchmarks                   | 116 |

|          |      | 6.6.1   | The lock benchmark          | 116 |

|          |      | 6.6.2   | The barrier benchmark       | 117 |

|          |      | 6.6.3   | The FIFO benchmark          | 118 |

|          | 6.7  | Result  | s                           | 120 |

|          |      | 6.7.1   | The lock benchmark          | 120 |

|          |      | 6.7.2   | The barrier benchmark       | 122 |

|          |      | 6.7.3   | The FIFO benchmark          | 123 |

|          |      | 6.7.4   | Microbenchmark summary      | 130 |

|          |      | 6.7.5   | The SAT solver              | 131 |

|          | 6.8  | Summ    | ary                         | 134 |

| 7 | Con | clusion                                                                                         | 137 |

|---|-----|-------------------------------------------------------------------------------------------------|-----|

|   | 7.1 | Comparison with related architectures $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 138 |

|   | 7.2 | Future work                                                                                     | 138 |

|   | 7.3 | Summary                                                                                         | 139 |

| A |     | mba: A Scalable Communication Centric Multi-Threaded Processor<br>hitecture                     | 141 |

|   | A.1 | Introduction                                                                                    | 143 |

|   | A.2 | Mamba Architecture                                                                              | 143 |

|   |     | A.2.1 FPGA Implementation                                                                       | 146 |

|   | A.3 | Software Techniques                                                                             | 147 |

|   | A.4 | Evaluation                                                                                      | 149 |

|   |     | A.4.1 MCS Lock Benchmark                                                                        | 149 |

|   |     | A.4.2 FIFO Queue Benchmark                                                                      | 151 |

|   | A.5 | Related Work                                                                                    | 152 |

|   | A.6 | Conclusion                                                                                      | 154 |

|   | A.7 | Future Work                                                                                     | 154 |

# List of Figures

| · ·              | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| • •              | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                  | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                  | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| m).              | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

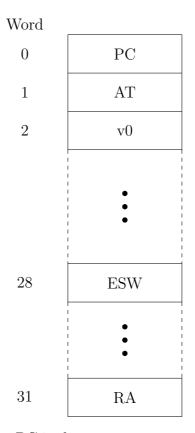

|                  | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ad<br>nt         | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ng               | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Rng              | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

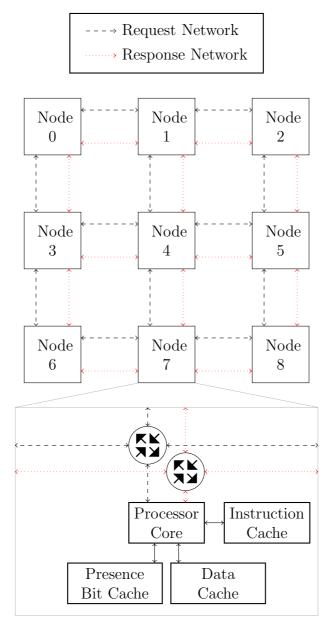

|                  | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

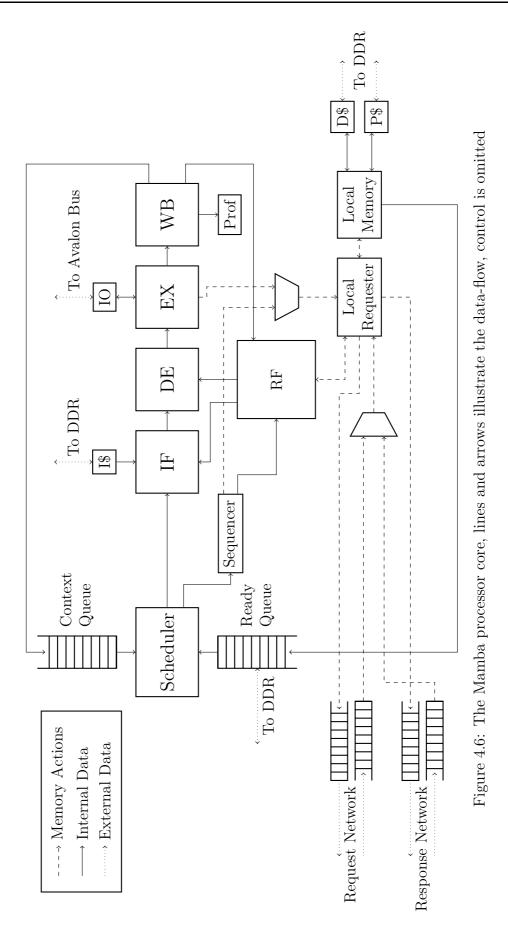

| n-<br>           | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| d-<br>a <i>n</i> | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

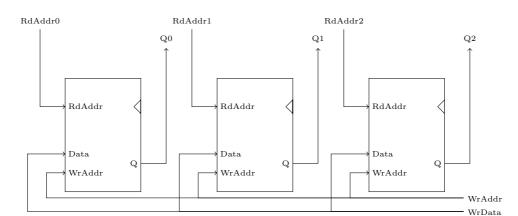

|                  | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                  | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                  | rn).<br>rn).<br>rn).<br>rn).<br>rn).<br>rnd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd<br>rd |

| 4.8  | The parts of a memory action's target address, L refers to the number<br>of bits in the local part of the address so $2^L$ is the size of a node's local<br>memory area $\ldots \ldots \ldots$                                                                      | 4 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

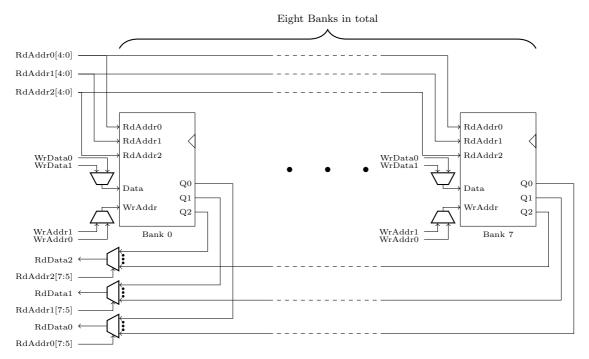

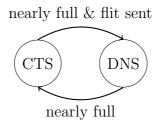

| 4.9  | On/Off flow control state machine, CTS is the clear to send state, DNS is<br>the do not send state                                                                                                                                                                                                                                                                                  | 6 |

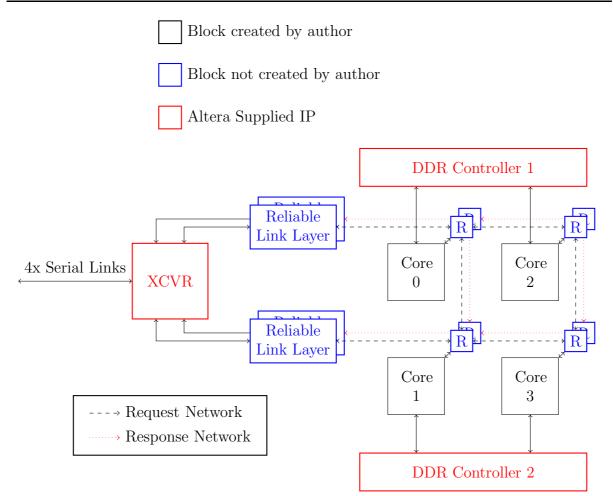

| 4.10 | The FPGA implementation of Mamba. R signifies a network router, XCVR is the Altera component responsible for driving the serial links. There are also 4 serial controllers that communicate via JTAG over USB utilised to output messages to a host PC and a block that can read and write DDR memory controlled by the host PC which is used for programming and results gathering | 8 |

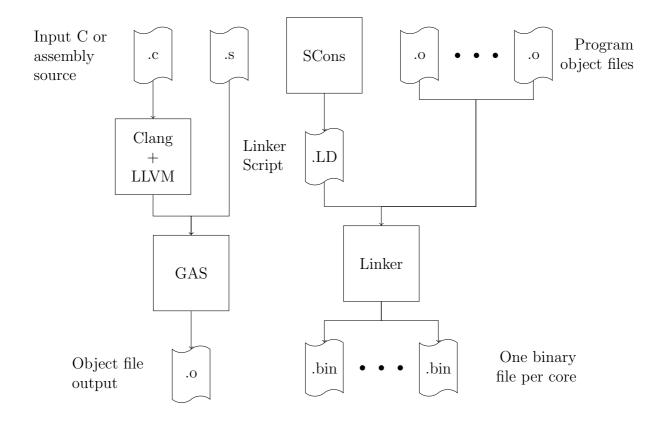

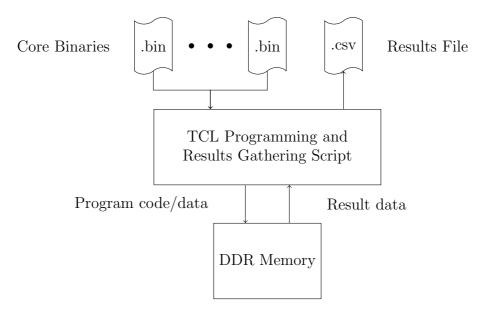

| 6.1  | The Software Tool Chain. SCons orchestrates the entire process as well as generating linker scripts                                                                                                                                                                                                                                                                                 | 2 |

| 6.2  | The program loading and running process                                                                                                                                                                                                                                                                                                                                             | 2 |

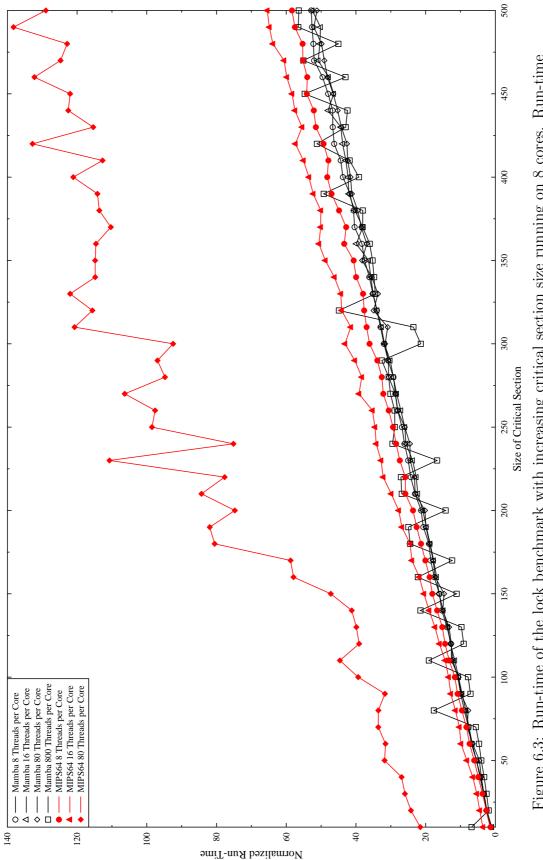

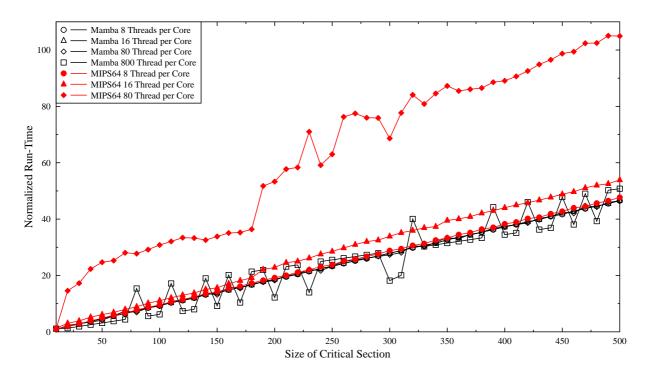

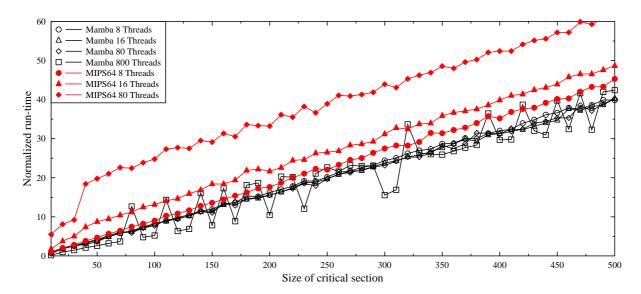

| 6.3  | Run-time of the lock benchmark with increasing critical section size running<br>on 8 cores. Run-time is normalised to MIPS64 run-time on 1 core with<br>smallest critical section size with 8 threads                                                                                                                                                                               | 9 |

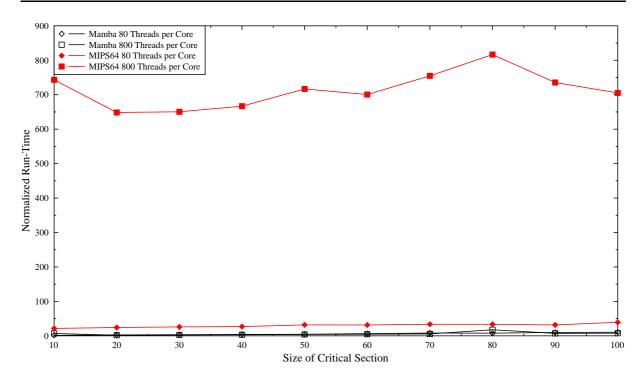

| 6.4  | Run-time of the lock benchmark with increasing critical section size running<br>on 8 cores for 80 and 800 threads. Run-time is normalised to MIPS64 run-<br>time on 1 core with smallest critical section size with 8 threads 120                                                                                                                                                   | 0 |

| 6.5  | Run-time of the lock benchmark with increasing critical section size running<br>on 1 core. Run-time is normalised to MIPS64 run-time on 1 core with<br>smallest critical section size with 8 threads                                                                                                                                                                                | 1 |

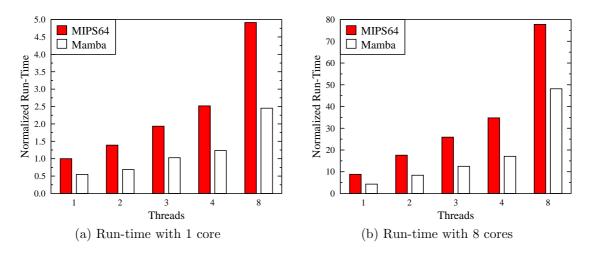

| 6.6  | Barrier benchmark normalised run-time for up to 8 threads for 1 and 8 cores. Run-time normalised to MIPS64 1 thread run-time                                                                                                                                                                                                                                                        | 2 |

|      | (a) Run-time with 1 core                                                                                                                                                                                                                                                                                                                                                            | 2 |

|      | (b) Run-time with 8 cores $\ldots \ldots \ldots$                                                                                                                                                                                                                    | 2 |

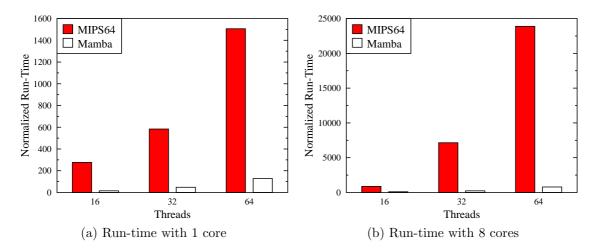

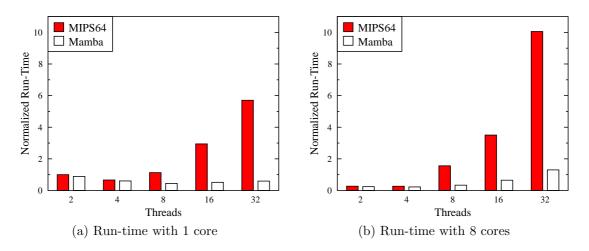

| 6.7  | Barrier benchmark normalised run-time for 16, 32 and 64 threads for 1 and 8 cores. Run-time normalised to MIPS64 1 thread run-time                                                                                                                                                                                                                                                  | 3 |

|      | (a) Run-time with 1 core                                                                                                                                                                                                                                                                                                                                                            | 3 |

|      | (b) Run-time with 8 cores                                                                                                                                                                                                                                                                                                                                                           | 3 |

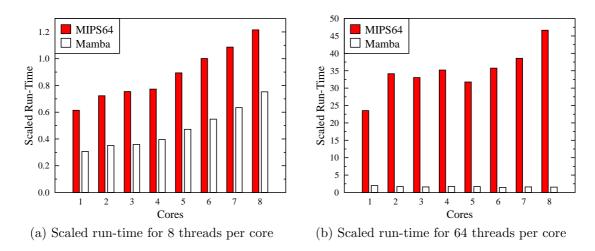

| 6.8  | Barrier benchmark scaled run-time for 1 - 8 cores with 8 and 64 threads.<br>Normalised run-time is divided by the total number of threads to get scaled<br>run-time                                                                                                                                                                                                                 | 4 |

|      | (a) Scaled run-time for 8 threads per core                                                                                                                                                                                                                                                                                                                                          |   |

|      | <ul> <li>(a) Scaled run-time for 64 threads per core</li></ul>                                                                                                                                                                                                                                                                                                                      |   |

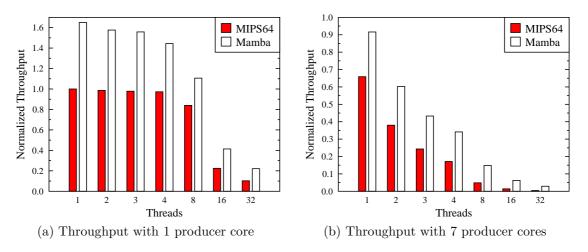

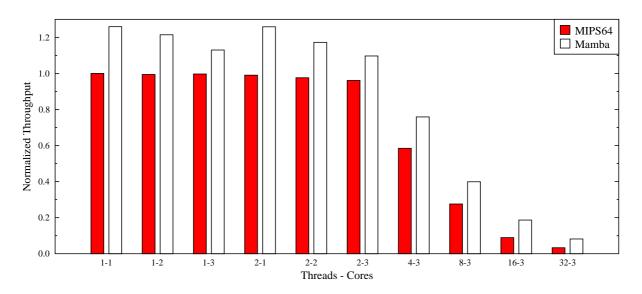

| 6.9  | Throughput of FIFO benchmark for 1 and 7 producer cores for 1, 2, 3, 4, 8, 16 and 32 threads per producer core. Throughput is normalised to MIPS64 run with 1 producer core with 1 thread per producer core                                                                                                                                                                         |   |

|      | (a)                                                                                                                                                                                                                                                   | Throughput with 1 producer core                                                                                                                                                                                                                                  |  |  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|      | (b)                                                                                                                                                                                                                                                   | Throughput with 7 producer cores $\ldots \ldots 124$                                                                                                                                       |  |  |

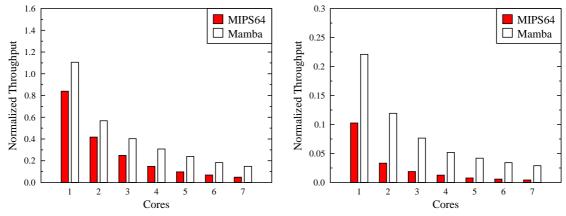

| 6.10 | 1 - 7                                                                                                                                                                                                                                                 | ughput of FIFO benchmark 8 and 32 threads per producer core for<br>7 producer cores. Throughput is normalised to MIPS64 run with 1<br>1 ucer core with 1 thread per producer core                                                                                |  |  |

|      | (a)                                                                                                                                                                                                                                                   | Throughput with 8 threads per producer core                                                                                                                                                                                                                      |  |  |

|      | (b)                                                                                                                                                                                                                                                   | Throughput with 32 threads per producer core                                                                                                                                                                                                                     |  |  |

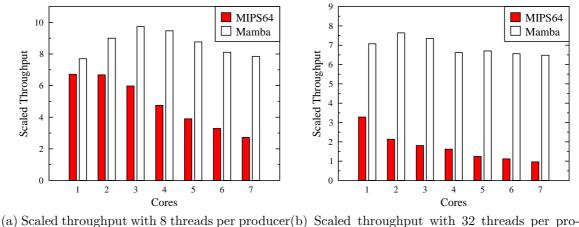

| 6.11 | Throughput of FIFO benchmark scaled by the total number of producer threads with 8 and 32 threads per producer core for 1 - 7 producer cores. Throughput is normalised to MIPS64 run with 1 producer core with 1 thread per producer core             |                                                                                                                                                                                                                                                                  |  |  |

|      | (a)                                                                                                                                                                                                                                                   | Scaled throughput with 8 threads per producer core                                                                                                                                                                                                               |  |  |

|      | (b)                                                                                                                                                                                                                                                   | Scaled throughput with 32 threads per producer core                                                                                                                                                                                                              |  |  |

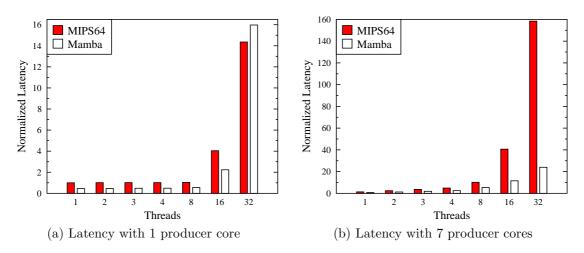

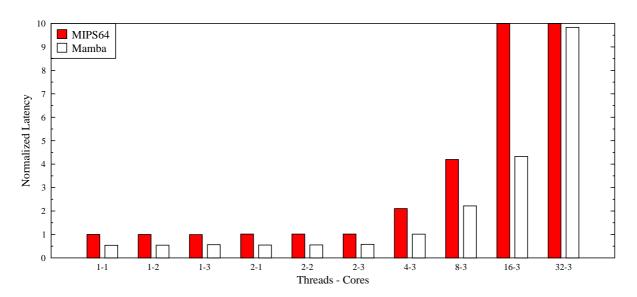

| 6.12 | and a                                                                                                                                                                                                                                                 | ncy of FIFO benchmark for 1 and 7 producer cores for 1, 2, 3, 4, 8, 16<br>32 threads per producer core. Latency is normalised to MIPS64 run<br>1 producer core with 1 thread per producer core                                                                   |  |  |

|      | (a)                                                                                                                                                                                                                                                   | Latency with 1 producer core                                                                                                                                                                                                                                     |  |  |

|      | (b)                                                                                                                                                                                                                                                   | Latency with 7 producer cores                                                                                                                                                                                                                                    |  |  |

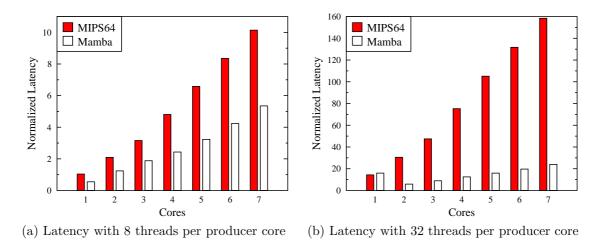

| 6.13 | prod                                                                                                                                                                                                                                                  | ncy of FIFO benchmark 8 and 32 threads per producer core for 1 - 7<br>ucer cores. Latency is normalised to MIPS64 run with 1 producer core<br>1 thread per producer core                                                                                         |  |  |

|      | (a)                                                                                                                                                                                                                                                   | Latency with 8 threads per producer core                                                                                                                                                                                                                         |  |  |

|      | (b)                                                                                                                                                                                                                                                   | Latency with 32 threads per producer core                                                                                                                                                                                                                        |  |  |

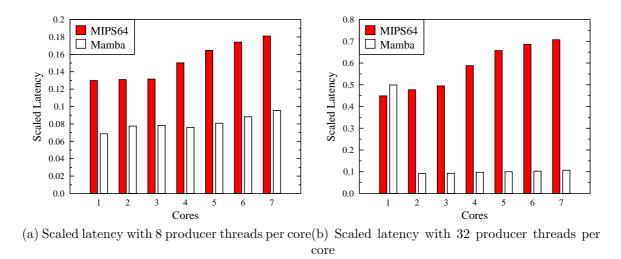

| 6.14 | Latency of FIFO benchmark scaled by dividing by the total number of producer threads with 8 and 32 threads per producer core for 1 - 7 producer cores. Latency is normalised to MIPS64 run with 1 producer core with 1 thread per producer core       |                                                                                                                                                                                                                                                                  |  |  |

|      | (a)                                                                                                                                                                                                                                                   | Scaled latency with 8 producer threads per core                                                                                                                                                                                                                  |  |  |

|      | (b)                                                                                                                                                                                                                                                   | Scaled latency with 32 producer threads per core                                                                                                                                                                                                                 |  |  |

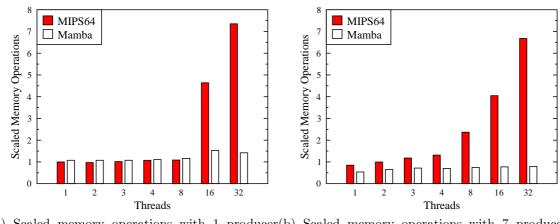

| 6.15 | Memory operations in the data cache of the consumer core divided by the total number of producer threads (total number of FIFOs) in the throughput benchmark. Normalized to the MIPS64 consumer core on the 1 producer core and 1 producer thread run |                                                                                                                                                                                                                                                                  |  |  |

|      | (a)                                                                                                                                                                                                                                                   | Scaled memory operations with 1 producer core                                                                                                                                                                                                                    |  |  |

|      | (b)                                                                                                                                                                                                                                                   | Scaled memory operations with 7 producer cores                                                                                                                                                                                                                   |  |  |

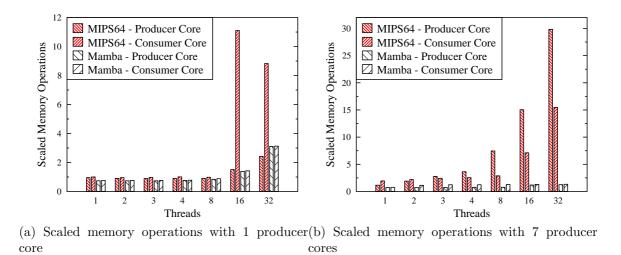

| 6.16 | prod<br>space                                                                                                                                                                                                                                         | ory operations in the data cache of the consumer core and average<br>ucer core divided by the total number of FIFOs in the core's address<br>e in the latency benchmark. Normalized to the MIPS64 consumer core<br>are 1 producer core and 1 producer thread run |  |  |

|      | (a)                                                                                                                                                     | Scaled memory operations with 1 producer core $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 129$                                                                                                                                                       |  |  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|      | (b)                                                                                                                                                     | Scaled memory operations with 7 producer cores                                                                                                                                                                                                                    |  |  |

| 6.17 | 7 Normalised run-time of the SAT solver for 1 and 8 cores solving the 'huge' instance. Run-time normalised to the MIPS64 run with 2 threads and 1 core1 |                                                                                                                                                                                                                                                                   |  |  |

|      | (a)                                                                                                                                                     | Run-time with 1 core                                                                                                                                                                                                                                              |  |  |

|      | (b)                                                                                                                                                     | Run-time with 8 cores $\ldots \ldots 131$                                                                                                                                            |  |  |

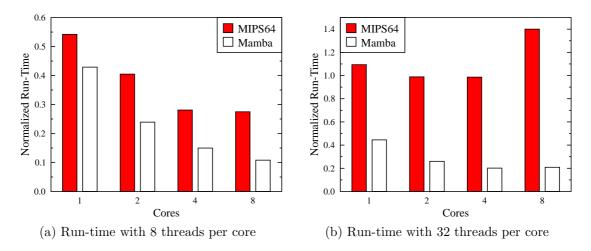

| 6.18 | the 'h                                                                                                                                                  | halised run-time of the SAT solver for 8 and 32 threads per core solving<br>nuge' instance. Run-time normalised to the MIPS64 run with 2 threads<br>1 core                                                                                                        |  |  |

|      | (a)                                                                                                                                                     | Run-time with 8 threads per core    132                                                                                                                                                                                                                           |  |  |

|      | (a)<br>(b)                                                                                                                                              | Run-time with 32 threads per core                                                                                                                                                                                                                                 |  |  |

| 6 10 |                                                                                                                                                         | -                                                                                                                                                                                                                                                                 |  |  |

| 0.19 |                                                                                                                                                         | nalised run-time of the SAT solver for 1 and 8 cores solving the 'medium' nce. Run-time normalised to the MIPS64 run with 2 threads and 1 core133                                                                                                                 |  |  |

|      | (a)                                                                                                                                                     | Run-time with 1 core                                                                                                                                                                                                                                              |  |  |

|      | (b)                                                                                                                                                     | Run-time with 8 cores                                                                                                                                                                                                                                             |  |  |

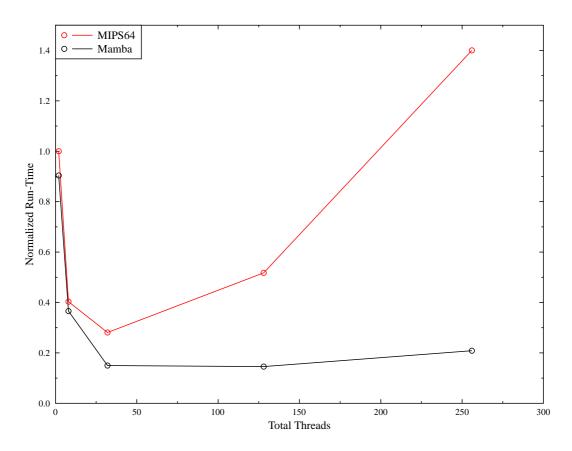

| 6.20 | (thre                                                                                                                                                   | halised run-time of the SAT solver for a range of total thread counts<br>ads per core cores) solving the 'huge' instance. Run-time normalised<br>e MIPS64 run with 2 threads and 1 core                                                                           |  |  |

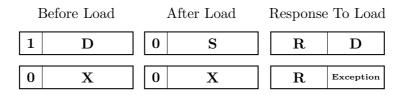

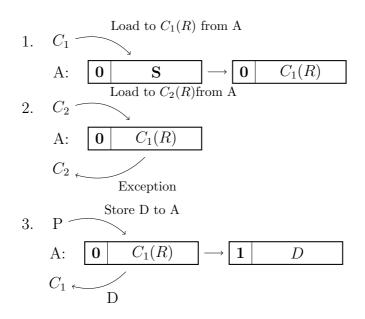

| A.1  | store<br>load                                                                                                                                           | possible actions on a load request at a particular word. D is the data<br>d in the word, S is the sentinel value, R is the return address of the<br>and F is an already existing return address. <b>0</b> refers to a non-present<br>, <b>1</b> to a present word |  |  |

| A.2  | existi<br>writi                                                                                                                                         | possible actions on a store request at a particular word. D is the ing data stored at the word, D' is the new data the store request is ng, S is the sentinel value and R is a return address. $0$ refers to a present word, $1$ to a present word                |  |  |

| A.3  |                                                                                                                                                         | ucer Consumer. $C_n(R)$ represents the address of register R in the $C_n$ . In a single consumer situation only steps 1. and 3. will occur. In ltiple consumer situation all 3 steps will occur                                                                   |  |  |

| A.4  | critic                                                                                                                                                  | time for the MCS Lock Benchmark with increasing work size in the<br>cal section, run-time normalized to MIPS64 run-time with smallest<br>cal section size. Benchmark run over 4 cores in all cases                                                                |  |  |

| A.5  | and                                                                                                                                                     | halized latency for the FIFO Queue Benchmark, for differing thread<br>core numbers, where t-c on the axis labels refers to t threads per<br>ucer core and c cores producing                                                                                       |  |  |

| A.6  | and o                                                                                                                                                   | nalized throughput for the FIFO Queue Benchmark, for differing thread core numbers, where t-c on the axis labels refers to t threads per pro-<br>r core and c cores producing                                                                                     |  |  |

# List of Tables