Number 830

# Massively parallel neural computation

Paul J. Fox

March 2013

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500 http://www.cl.cam.ac.uk/

# © 2013 Paul J. Fox

This technical report is based on a dissertation submitted October 2012 by the author for the degree of Doctor of Philosophy to the University of Cambridge, Jesus College.

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

http://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986

#### **Abstract**

Reverse-engineering the brain is one of the US National Academy of Engineering's "Grand Challenges." The structure of the brain can be examined at many different levels, spanning many disciplines from low-level biology through psychology and computer science. This thesis focusses on real-time computation of large neural networks using the Izhikevich spiking neuron model.

Neural computation has been described as "embarrassingly parallel" as each neuron can be thought of as an independent system, with behaviour described by a mathematical model. However, the real challenge lies in modelling neural communication. While the connectivity of neurons has some parallels with that of electrical systems, its high fan-out results in massive data processing and communication requirements when modelling neural communication, particularly for real-time computations.

It is shown that memory bandwidth is the most significant constraint to the scale of real-time neural computation, followed by communication bandwidth, which leads to a decision to implement a neural computation system on a platform based on a network of Field Programmable Gate Arrays (FPGAs), using commercial off-the-shelf components with some custom supporting infrastructure. This brings implementation challenges, particularly lack of on-chip memory, but also many advantages, particularly high-speed transceivers. An algorithm to model neural communication that makes efficient use of memory and communication resources is developed and then used to implement a neural computation system on the multi-FPGA platform.

Finding suitable benchmark neural networks for a massively parallel neural computation system proves to be a challenge. A synthetic benchmark that has biologically-plausible fan-out, spike frequency and spike volume is proposed and used to evaluate the system. It is shown to be capable of computing the activity of a network of 256k Izhikevich spiking neurons with a fan-out of 1k in real-time using a network of 4 FPGA boards. This compares favourably with previous work, with the added advantage of scalability to larger neural networks using more FPGAs.

It is concluded that communication must be considered as a first-class design constraint when implementing massively parallel neural computation systems.

# Acknowledegments

Simon Moore gave many hours of supervision and advice. Theo Markettos proof-read this entire thesis and corrected many typos and other errors. Andrew Moore provided the coffee machine that allowed sufficient work to be put in to get this finished.

None of this would have been possible without the support of my friends and family. Particular thanks go to Cambridge University Yacht Club for providing many opportunities to escape from the pressures of writing this thesis. Hopefully future Commodores will not need to spend a whole week on the phone trying to fix an engine failure half-way across the world.

I would also like to thank Peter Wilson and Pietro Lio for taking the time to examine my thesis, which forms the basis of this technical report.

# **Contents**

| 1 | Intro | oduction                                                |       |       | 8    |

|---|-------|---------------------------------------------------------|-------|-------|------|

|   | 1.1   | Motivation for neural computation                       |       |       | . 8  |

|   | 1.2   | Fundamental processes of neural computation             |       |       |      |

|   | 1.3   | Goals and hypotheses                                    |       |       |      |

|   |       |                                                         |       |       |      |

|   | 1.4   | Overview                                                |       |       |      |

|   | 1.5   | Publications                                            | <br>• | <br>• | . 11 |

| _ | D 1   | 1                                                       |       |       | 10   |

| 2 |       | kground                                                 |       |       | 12   |

|   | 2.1   | Introduction                                            |       |       |      |

|   | 2.2   | Fundamentals of neural computation                      |       |       |      |

|   | 2.3   | Neural computation methods                              |       |       | . 13 |

|   |       | 2.3.1 Mapping neural networks on to computation systems |       |       |      |

|   |       | 2.3.2 Neuron models                                     |       |       |      |

|   |       | 2.3.3 Communication models                              |       |       |      |

|   |       | 2.3.4 Implementation methods                            |       |       |      |

|   | 2.4   | T                                                       |       |       |      |

|   | 2.4   | Software-based neural computation                       |       |       |      |

|   |       | 2.4.1 Supercomputer-based systems                       |       |       |      |

|   |       | 2.4.2 PC-based systems                                  |       |       |      |

|   |       | 2.4.3 GPU-based systems                                 |       |       |      |

|   | 2.5   | Hardware-based neural computation                       |       |       |      |

|   |       | 2.5.1 Modelling neurons                                 |       |       | . 18 |

|   |       | 2.5.2 Modelling neural network topology                 |       |       |      |

|   |       | 2.5.3 Modelling synaptic connections                    |       |       |      |

|   | 2.6   | Design decisions                                        |       |       |      |

|   | 2.7   | Conclusion                                              |       |       |      |

|   | ۷.7   | Conclusion                                              | <br>• | <br>• | . 23 |

| 3 | Hiol  | h-level requirements                                    |       |       | 24   |

| 3 | 3.1   | Introduction                                            |       |       |      |

|   |       |                                                         |       |       |      |

|   | 3.2   | The Izhikevich spiking neuron model                     |       |       |      |

|   |       | 3.2.1 Conversion to discrete-time                       |       |       |      |

|   |       | 3.2.2 Conversion to fixed-point                         |       |       |      |

|   |       | 3.2.3 Sampling interval size                            |       |       |      |

|   |       | 3.2.4 Final simplification                              |       |       | . 29 |

|   |       | 3.2.5 Numerical precision                               |       |       | . 29 |

|   | 3.3   | Communication properties of neural networks             |       |       | . 30 |

|   |       | 3.3.1 Fan-out                                           |       |       |      |

|   |       | 3.3.2 Locality                                          |       |       |      |

|   |       | 3.3.3 Spike frequency                                   |       |       |      |

|   |       |                                                         |       |       |      |

|   | 0.4   | J 1 J                                                   |       |       |      |

|   | 3.4   | Conclusion                                              | <br>• | <br>• | . 31 |

| 1 | Dag   | winom on to                                             |       |       | 32   |

| 4 | _     | uirements                                               |       |       |      |

|   | 4.1   | Introduction                                            |       |       |      |

|   | 4.2   | Neural computation tasks                                |       |       |      |

|   | 4.3   | Volume of activity                                      |       |       |      |

|   |       | 4.3.1 Evaluating neuron modelling equations             |       |       | . 33 |

|   |       | 4.3.2 Synaptic updates                                  |       |       |      |

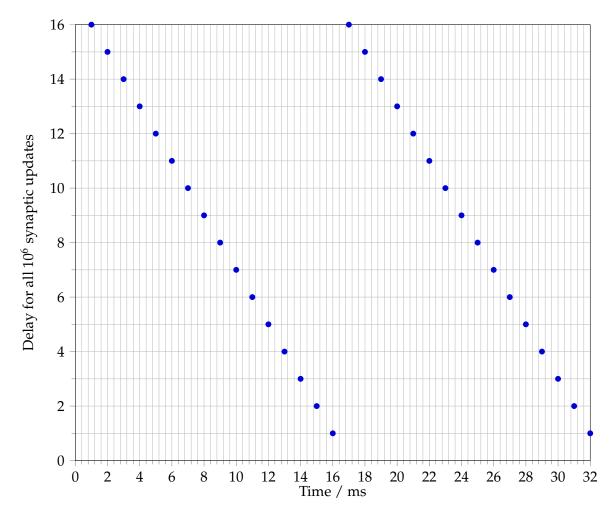

|   |       | 4.3.3 Delaying synaptic updates                         |       |       |      |

|   |      | 4.3.4                | Applying synaptic updates             | 36       |

|---|------|----------------------|---------------------------------------|----------|

|   |      | 4.3.5                | Summary                               | 36       |

|   | 4.4  | Memo                 |                                       | 37       |

|   |      | 4.4.1                | Evaluating equations                  | 37       |

|   |      | 4.4.2                | Synaptic updates                      | 38       |

|   |      | 4.4.3                | Delaying synaptic updates             | 38       |

|   |      | 4.4.4                | Applying synaptic updates             | 39       |

|   |      | 4.4.5                | Summary                               | 39       |

|   | 4.5  | Comm                 |                                       | 40       |

|   |      | 4.5.1                | Type of communication infrastructure  | 40       |

|   |      | 4.5.2                | 7.1                                   | 40       |

|   |      | 4.5.3                | • • •                                 | 41       |

|   | 4.6  | Imple                |                                       | 41       |

|   |      | 4.6.1                | 0;                                    | 41       |

|   |      | 4.6.2                | •                                     | 41       |

|   |      | 4.6.3                |                                       | <br>41   |

|   |      | 4.6.4                | 1 0                                   | 42       |

|   |      | 4.6.5                |                                       | 12       |

|   |      | 4.6.6                | 1                                     | 12<br>12 |

|   |      | 4.6.7                |                                       | 43       |

|   | 4.7  |                      |                                       | 10<br>44 |

|   | 1.7  | Corici               |                                       |          |

| 5 | Plat | form                 | 4                                     | 45       |

|   | 5.1  | Introd               | uction                                | 45       |

|   | 5.2  | Choice               | e of FPGA board                       | 45       |

|   |      | 5.2.1                | Number of FPGAs per PCB               | 45       |

|   |      | 5.2.2                |                                       | 45       |

|   |      | 5.2.3                |                                       | 46       |

|   |      | 5.2.4                |                                       | 46       |

|   |      | 5.2.5                |                                       | 46       |

|   |      | 5.2.6                | Summary                               | 47       |

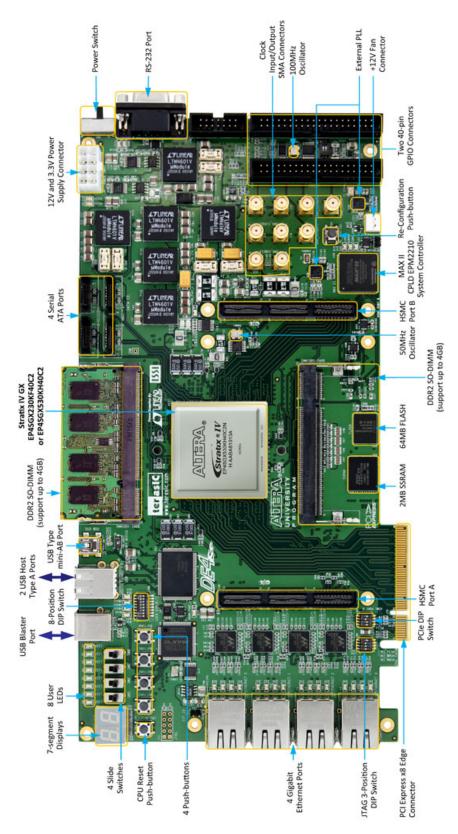

|   | 5.3  | Terasio              | c DE4 evaluation board                | 47       |

|   |      | 5.3.1                | Memory hierarchy                      | 47       |

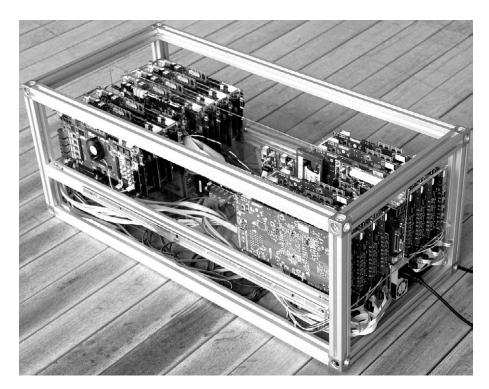

|   | 5.4  | Creati               |                                       | 48       |

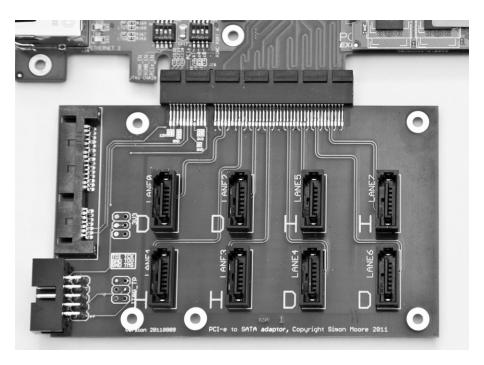

|   |      | 5.4.1                |                                       | 48       |

|   |      | 5.4.2                | Programming and diagnostics           | 49       |

|   |      | 5.4.3                |                                       | 49       |

|   | 5.5  | Concl                | 8                                     | 50       |

|   |      |                      |                                       |          |

| 6 | Syn  | aptic u <sub>l</sub> | L                                     | 53       |

|   | 6.1  |                      |                                       | 53       |

|   | 6.2  | Design               | 0                                     | 53       |

|   |      | 6.2.1                | Fetching synaptic updates efficiently | 54       |

|   |      | 6.2.2                | On-chip memory usage                  | 54       |

|   |      | 6.2.3                | Inter-FPGA communication              | 54       |

|   | 6.3  | Design               | n decisions                           | 54       |

|   |      | 6.3.1                | Starting the update process           | 55       |

|   |      | 6.3.2                |                                       | 55       |

|   |      | 6.3.3                | Delaying synaptic updates             | 56       |

|   |      | 6.3.4                |                                       | 57       |

|   | 6.4  | Passin               |                                       | 57       |

|   |      | 6.4.1                | 01                                    | 58       |

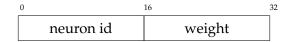

|   | 6.5  | Synap                |                                       | 58       |

|   |      | , ,                  | 1 0                                   | 59       |

|     | 6.6   | Evaluation of the algorithm             |

|-----|-------|-----------------------------------------|

|     |       | 6.6.1 Mathematical models 60            |

|     |       | 6.6.2 Results                           |

|     |       | 6.6.3 Memory size                       |

|     | 6.7   | Conclusion                              |

| _   | T     | lementation 69                          |

| 7   | 7.1   | <b>lementation 69</b> Introduction      |

|     | 7.1   |                                         |

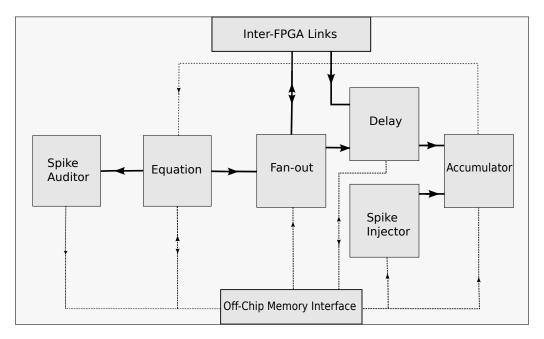

|     | 7.2   | 1 0 0                                   |

|     |       | 7.2.1 Equation processor                |

|     |       | 7.2.3 Delay unit                        |

|     |       | 7.2.4 Accumulator                       |

|     |       | 7.2.5 Memory spike source               |

|     |       | 7.2.6 Spike injector                    |

|     |       | 7.2.7 Spike auditor                     |

|     |       | 7.2.8 Control state machine             |

|     |       | 7.2.9 Control logic                     |

|     | 7.3   | Input data                              |

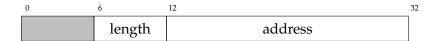

|     | 7.0   | 7.3.1 Neural network description format |

|     |       | 7.3.2 Memory image file format          |

|     |       | 7.3.3 Memory image file generation      |

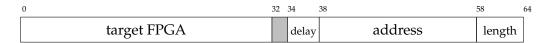

|     | 7.4   | Inter-FPGA communication                |

|     | ,.1   | 7.4.1 Physical layer                    |

|     |       | 7.4.2 Link layer                        |

|     |       | 7.4.3 Routing                           |

|     |       | 7.4.4 Message filtering and delivery    |

|     |       | 7.4.5 Application usage                 |

|     | 7.5   | Implementation languages                |

|     | 7.6   | Conclusion                              |

|     |       |                                         |

| 8   | Eval  | uation 90                               |

|     | 8.1   | Introduction                            |

|     |       | Benchmark neural network                |

|     | 8.3   | Scale                                   |

|     | 8.4   | Communication overhead                  |

|     | 8.5   | Validation                              |

|     | 8.6   | Conclusion                              |

| 9   | Con   | clusions 97                             |

| ,   | 9.1   | Evaluation of hypotheses                |

|     | ···   | 9.1.1 Scalability Hypothesis            |

|     |       | 9.1.2 Communication-Centric Hypothesis  |

|     |       | 9.1.3 Bandwidth Hypothesis              |

|     | 9.2   | Comparison to other systems             |

|     | ·-    | 9.2.1 Supercomputer-based systems       |

|     |       | 9.2.2 PC-based systems                  |

|     |       | 9.2.3 GPU-based systems                 |

|     |       | 9.2.4 Bespoke hardware-based systems    |

|     | 9.3   | Future work                             |

|     |       | 9.3.1 Increase in scale                 |

|     |       | 9.3.2 Increase in flexibility           |

|     |       |                                         |

| Bil | bliog | raphy 105                               |

## 1 Introduction

Reverse-engineering the brain is one of the US National Academy of Engineering's "Grand Challenges." While there are many ways to go about this, one method is to study the behaviour of real brains and attempt to emulate their behaviour using computer-based computation of an inferred neural network. This process will be referred to as "neural computation" throughout this work.

# 1.1 Motivation for neural computation

The structure and behaviour of individual neurons is well known, particularly as a result of experiments by Hodgkin and Huxley (1952), who studied the behaviour of giant squid neurons. We also have a good understanding of the high-level functional structure of the human brain based on studies using brain imaging technologies such as MRI scans. However, we currently know very little about how neurons in the human brain are connected to form neural systems capable of exhibiting the functions that we observe.

One way to explore the connectivity of neurons in the brain is to infer candidate neural networks based on observed functionality and then compute their behaviour. The results of these computations can be used to evaluate and refine the inferred neural networks and hence to gain a greater understanding of the low-level structure of the human brain.

Another application of neural computation is creating "brain-like" systems, particularly in the fields of computer vision (Rowley *et al.*, 1998) and pattern recognition (Rice *et al.*, 2009). By emulating the methods used by the human brain to perform visual processing, there is potential to create systems that have higher performance and lower power consumption than those created using conventional computer architectures. Such systems will need to be developed with the support of neural computation.

# 1.2 Fundamental processes of neural computation

All neural computation systems need to emulate the behaviour of biological neural networks. While they vary in the level of detail and accuracy that they provide (principally as a result of the algorithms used to model the behaviour of neurons and their synaptic connections), they all need to provide:

Algorithms to model the behaviour of neurons and their interaction via synaptic connections

**Data structures** to store the parameters of neurons and synaptic connections

Communication infrastructure to support modelling of the interaction between neurons

The majority of existing neural computation systems, including PC-based systems such as NEST (Gewaltig and Diesmann, 2007) and many hardware-based systems such as those by Thomas and Luk (2009) and Fidjeland and Shanahan (2010) have been designed with little focus on either data structures or communication. As a result, the size of neural network that these systems can perform neural computation with is limited to whatever can be handled by a single device (such as a single PC or single custom hardware device) as they lack the ability to

scale to handle larger neural networks using additional devices operating in parallel. The state-of-the-art is around 50k neurons and 50M synaptic connections on a single device as exhibited by Fidjeland and Shanahan.

The main exceptions to this are supercomputer-based neural computation systems such as that by Ananthanarayanan *et al.* (2009), which are able to take advantage of the custom communications infrastructure provided by supercomputers. This allows them to perform neural computation with neural networks which are orders of magnitude larger than those that can be handled by other systems (around  $10^9$  neurons and  $10^{13}$  synaptic connections), but at a financial cost that puts these systems out of reach of the majority of researchers.

# 1.3 Goals and hypotheses

This work aims to design a neural computation architecture with communication and data structures as first-class design constraints alongside the algorithms used to model neurons and synaptic connections. This will lead to an architecture that can scale to use many devices operating in parallel and hence perform neural computation with neural networks consisting of millions of neurons and billions of synaptic connections in real-time.

Since I aim to perform neural computation at a scale that greatly exceeds the capacity of any single device, I propose the Scalability Hypothesis.

### **Scalability Hypothesis**

The scale of neural network that can be handled by a neural computation system in real-time must be able to be increased by scaling the system to multiple devices

The Scalability Hypothesis indicates that a neural computation system must be a parallel processing system. There are two major types of resources in a parallel processing system:

#### Compute resources

Perform a portion of the computation involved in a parallel processing task

#### **Communication resources**

Pass data between compute resources and provide coordination between them so that the complete system produces the correct result for a parallel processing task

If a neural network (as well as the system used to perform neural computation of this network) is considered to be a parallel processing system, then neurons can be considered to be compute resources, while synaptic connections (see Section 2.2) can be considered to be communication resources. This leads to the Communication-Centric Hypothesis.

#### **Communication-Centric Hypothesis**

The scalability of a neural computation system is communication-bound, not compute-bound

The Communication-Centric Hypothesis means that the work involved in modelling communication in a neural computation system dominates the work involved in modelling the behaviour of neurons. It also means that the scale of neural network that can be handled by a neural computation system in real-time is bounded by the availability of communication resources in this system rather than the availability of compute resources.

10 1.4. OVERVIEW

Communication resources in a parallel processing system can be divided into those that provide inter-device communication and those that provide access to memory. This leads to the Bandwidth Hypothesis.

### **Bandwidth Hypothesis**

The scale of neural network that can be handled by a neural computation system in real-time is bounded by inter-device communication bandwidth and memory bandwidth

The Bandwidth Hypothesis provides two important considerations when designing a massively parallel neural computation system:

- 1. Using an implementation platform that provides sufficient inter-device communication bandwidth and memory bandwidth

- 2. Using this bandwidth efficiently to maximise the scale of neural network that can be handled by the neural computation system in real-time

This thesis will provide justification for these hypotheses.

#### 1.4 Overview

I begin by reviewing related work on neural computation systems in Chapter 2 to discover what methods have been used to model the behaviour of neurons and their communication, and how the scale of neural computation that can be handled by these systems has been increased, both on a single chip and by scaling to multiple chips. This provides justification for the Scalability Hypothesis and begins to provide justification for the Communication-Centric Hypothesis and Bandwidth Hypothesis.

Chapter 3 analyses the Izhikevich spiking neuron model to determine how its neuron modelling equations can be adapted from floating-point and continuous-time to create a fixed-point, discrete-time neuron model that is better suited to massively parallel neural computation. The communication properties of biological neural networks are also analysed, as they affect the design of both neural computation systems and the benchmark neural networks that are used to evaluate them.

Chapter 4 divides neural computation into separate tasks and analyses the volume of work involved in each task and their memory and communication bandwidth requirements. This justifies the Bandwidth Hypothesis and leads to discussion of appropriate implementation platforms for a massively parallel neural computation system, after which a platform based on a network of Field Programmable Gate Arrays (FPGAs) is selected. This platform is presented in Chapter 5, with discussion of how its features influence the design of a neural computation system implemented on it.

Chapter 6 develops and evaluates an algorithm for modelling communication between neurons that takes account of the Bandwidth Hypothesis and is optimised for a FPGA-based neural computation platform. This platform is implemented in Chapter 7 and evaluated in Chapter 8. Chapter 9 evaluates the three hypotheses proposed in this chapter, draws conclusions and considers future work.

### 1.5 Publications

The following publications were produced in the course of this work:

Simon W Moore, Paul J Fox, Steven JT Marsh, A Theodore Markettos and Alan Mujumdar; "Bluehive - A Field-Programable Custom Computing Machine for Extreme-Scale Real-Time Neural Network Simulation"; 20th Annual International Symposium on Field-Programmable Custom Computing Machines pp 133-140; April 29 - May 1 2012

Paul J Fox and Simon W Moore; "Efficient Handling of Synaptic Updates in FPGA-based Large-Scale Neural Network Simulations"; 2012 Workshop on Neural Engineering using Reconfigurable Hardware; September 1 2012; Held in Conjunction with FPL 2012

Paul J Fox and Simon W Moore; "Communication-focussed Approach for Real-time Neural Simulation"; 3rd International Workshop on Parallel Architectures and Bioinspired Algorithms pp 9-16; September 11 2010; Held in conjunction with PACT 2010

# 2 Background

#### 2.1 Introduction

To create a massively parallel neural computation system that can scale to computations of large neural networks in real-time, we must understand the tasks involved in neural computation, how they have been approached by other researchers and what limits the scale and speed of a neural computation system.

We begin with an overview of the fundamentals of neural computation, finding that there are two fundamental requirements – modelling neurons and modelling their communication. Modelling neural communication can be further divided into modelling the topology of a neural network and modelling the effect that neurons have on other neurons via synaptic connections. Having identified these fundamental tasks of neural computation, we review how other work has approached them, ranging from methods that closely mirror the processes and structure of biological neural networks to those that aim to emulate only their externally observable behaviour.

# 2.2 Fundamentals of neural computation

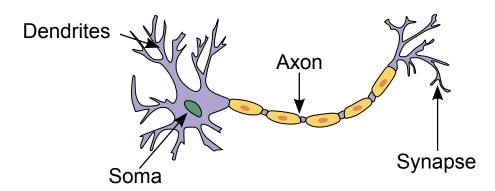

Neural computation is the process of replicating the behaviour of a biological neural network using a computer system. A diagram of a biological neuron is shown in Figure 2.1 on the facing page. It has four major components that are pertinent to neural computation:

#### **Dendrites**

Receive input from other neurons via synaptic connections.

#### Soma

The main body of a neuron. It receives input from the dendrites. The aggregated input has an effect on its membrane potential. If the membrane potential passes a threshold then the soma will emit an action potential or "spike," and then reset its membrane potential and become less responsive to input for a period.

#### Axon

Carries spikes over some distance. Wrapped in a myelin sheath to provide electrical insulation. Its end is fanned-out to connect to multiple target neurons.

#### Synapse

A gap between the axon endings of a source neuron and the dendrites of a target neuron. Introduces a delay to the communication of spikes between neurons and also provides a varying degree of effect of each spike on the target neuron, which results in each target neuron receiving a varying "synaptic update."

Figure 2.1: Diagram of a neuron showing components that are pertinent to neural computation

# 2.3 Neural computation methods

All methods of neural computation will need to model each of the four major components of a neuron to some degree. Computation methods can be categorised based on how closely they aim to replicate biological processes, both at a chemical and an electrical level.

The soma can be thought of as computing the state of a neuron, while the dendrites, axon and synaptic connections collectively communicate synaptic updates between neurons. While each neuron has a single soma and axon, there can be many dendrites and synaptic connections (around 10<sup>3</sup> per neuron in the human brain). As will be shown in Chapter 3, this means that the work involved in modelling neural communication greatly exceeds that involved in modelling the behaviour of the soma, particularly if the behaviour of each dendrite and synapse is modelled separately.

Since the axon, dendrites and synapses are all involved in neural communication rather than computing a neuron's state, the remainder of this work refers to modelling the behaviour of the soma as modelling the behaviour of a neuron.

### 2.3.1 Mapping neural networks on to computation systems

Before neural computation can be performed with a neural network, it needs to be mapped on to a neural computation system. The first stage of this process involves selecting a neuron model and a communication model. The neural network can then be though of as a number of neuron processes communicating with each other via communication channels which represent axons, synapses and dendrites.

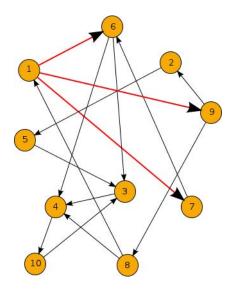

Figure 2.2 on the next page shows a neural network modelled as a number of communicating processes. The circles represent neuron processes and the lines communication channels between these processes. The red lines show the communication channels between neuron process 1 and neuron processes 6, 7 and 9. This communicating process model provides a layer of abstraction between neural networks (and in particular biological neural networks) and neural computation systems. Given a suitable model for each neuron process and communication channel, it will be possible to model the behaviour of a neural network with the desired level of biological plausibility and accuracy.

If a neural computation system conceptually consists of a number of connected devices, then each neuron process will need to be mapped on to one of these devices. The communication channels between the neuron processes will then need to be mapped on to the physical communication links between the devices. Since biological neural networks frequently have

Figure 2.2: A neural network as a number of communicating processes

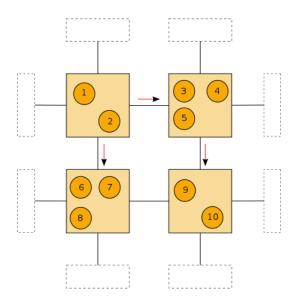

Figure 2.3: Communicating process network from Figure 2.2 mapped on to a neural computation system

communication channels that form "non-uniform" patterns, with it being possible for arbitrary neurons in a network to be connected, this means that multiplexing and routing will be needed to overlay these communication channels on to physical communication links.

For example, the communicating process network in Figure 2.2 could be mapped on to a neural computation system with a number of devices connected in a two-dimensional grid as shown in Figure 2.3. The channels between neuron process 1 and neuron processes 6 and 7 each use one physical link between two adjacent devices, while the channel between neuron process 1 and neuron process 9 uses two physical links and some form of routing on the intermediate device.

#### 2.3.2 Neuron models

Neuron models range in complexity from detailed models that are claimed to be biologically accurate, to much simpler models that aim to model only the externally-observable spiking behaviour of a neuron, known as spiking neuron models. Which type of model is used in a neural computation system depends on the goals of individual researchers and the resources

Increasing computational complexity —

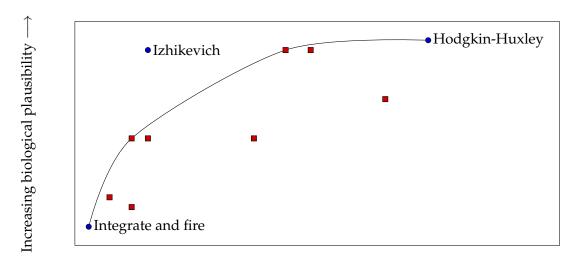

Figure 2.4: Biological plausibility and computational complexity of spiking neuron models. Redrawn from (Izhikevich, 2004). Unlabelled points are other neuron models considered by Izhikevich

available to them, as many researchers are happy to accept the reduced accuracy of spiking neuron models or believe that the extra detail provided by more biologically accurate models is irrelevant. Using a simpler neuron model also allows neural computation to be performed for larger neural networks than more complex models using the same resources.

One of the most commonly used biologically accurate neuron models is the Hodgkin-Huxley model (1952) which aims to model the behaviour of a neuron based on observed chemical and electrical processes, so that both the internal and external behaviour of a modelled neuron follow biology. The model uses ten differential equations per neuron.

There are many spiking neuron models, with varying levels of complexity and biological accuracy of the spike patterns that they produce. Some of the simplest spiking neuron models are the integrate and fire (Abbott, 1999) and leaky integrate and fire (Stein, 1965) models, which both model the behaviour of a neuron using a single differential equation. Another, more complex, spiking neuron model is the Izhikevich model (2003), which aims to be able to reproduce many observed types of neuron spike patterns using two differential equations per neuron.

Izhikevich (2004) surveys a number of spiking neuron models, and classifies them based on their biological plausibility and implementation cost (analogous to computational complexity). The results of this analysis are shown in Figure 2.4, and show that (based on the metrics used by Izhikevich) the Izhikevich model has an attractive combination of biological plausibility and computational complexity.

Neurons can also be modelled using electrical circuits that replicate their behaviour, typically using analogue components such as capacitors to model features such as membrane potential. For example the Hodgkin-Huxley model can be specified in terms of an electrical circuit as well as a set of differential equations (Toumazou *et al.*, 1998).

#### 2.3.3 Communication models

Spiking neuron models assume that axons and dendrites are essentially equivalent to electrical wiring, and hence their communication models are restricted to communicating neural spikes and modelling the effect of synapses on the transmission of these neural spikes from source to target neurons. Synapses are normally modelled using a simple model with each synaptic

connection having a delay and a multiplicative weight, which can be either positive or negative, to model varying effect of a spike on a target neuron, and hence a varying synaptic update. The weights of each synaptic update targeted at a neuron are summed to produce a single value that is input to the neuron model.

More complex neuron models are often accompanied by complex communication models, with detailed models of the effect of axons, dendrites and synapses on the transmission of neural spikes. Axons and dendrites can be modelled using cable theory (Rall, 1959), while synapse models can have a range of complexities, which can model the effect of both electrical and chemical processes on the transmission of neural spikes.

This results in complex models of the behaviour of the soma, axon, dendrites and synapses such as that used by Traub *et al.* (2005). These models are often designed to model specific regions of the brain (particularly cortical regions), for example the model used by Ananthanarayanan *et al.* (2009) is specific to the cat cortex.

These detailed communication models add orders of magnitude of complexity to a neural computation as the number of dendrites and synaptic connections that need to be modelled is orders of magnitude greater (between  $10^3 \times$  and  $10^4 \times$ ) than the number of neurons that need to be modelled. Therefore such models result in neural computation systems that operate many times slower than real-time (Ananthanarayanan *et al.*, 2009).

Communication models may also implement some form of learning mechanism, such as Hebbian learning (Hebb, 1949). This is often based on altering the connectivity or parameters of synaptic connections (synaptic plasticity) in response to spike activity (Song *et al.*, 2000), which will add computational complexity to a neural computation but will not affect communication complexity.

### 2.3.4 Implementation methods

There is a major division in neural computation between software-based and hardware-based systems. Software-based neural computation systems support larger neural networks by using more compute resources, with communication between these resources provided by some form of shared memory. Hardware-based neural computation systems show more variation, with different methods used to model neurons and to model their communication, with work by other researchers often combining different neural modelling methods with different communication modelling methods. Therefore we will survey methods of modelling neurons and of modelling their communication in hardware-based neural computation systems separately.

# 2.4 Software-based neural computation

In a software-based neural computation system, neurons and neural communication are both modelled in software. Communication resources typically use some form of shared memory. Scaling to larger neural networks is achieved primarily by increasing compute and communication resources (as suggested by the Scalability Hypothesis), but shared memory communication scales poorly without specialised interconnect, so neural computation of large neural networks either requires a supercomputer with a custom memory hierarchy (Migliore *et al.*, 2006) or many multiples of real-time on commodity PC-based systems with finite resources.

### 2.4.1 Supercomputer-based systems

A notable supercomputer-based neural computation system has been produced by the Blue Brain project (Markram, 2006), using an IBM BlueGene/L supercomputer. A similar system by Ananthanarayanan et~al.~(2009) can perform neural computation with a neural network based on the cat cortex with  $0.9\times10^9$  neurons and  $0.9\times10^{13}$  synaptic connections around  $83\times$  slower than real-time per Hertz of mean spike frequency (which would be  $830\times$  slower than real-time for a mean spike frequency of  $10\,\mathrm{Hz}$ ) with a sampling interval of 1 ms. This saturates the memory bandwidth in an IBM BlueGene/P supercomputer with 147456 CPUs and 144 TB of RAM. The number of CPUs in this system provides evidence for the Scalability Hypothesis.

Ananthanarayanan *et al.* demonstrate that doubling the available RAM in this system almost doubles the size of neural network that can be handled by this system in a given time-scale, which agrees with the Bandwidth Hypothesis. These results are impressive (a neural network around  $25 \times$  the size of this network would match the scale of the human brain), but the cost, size and power requirements of the supercomputer required by this system puts it out of reach of the vast majority of researchers.

### 2.4.2 PC-based systems

PC-based systems are more readily available to researchers than supercomputer-based systems, and can be used for smaller-scale neural computations. For example NEURON (Hines and Carnevale, 1997), Brian (Goodman and Brette, 2008) and Nest (Gewaltig and Diesmann, 2007) all use commodity PC hardware. While there is support for using multiple processors in these PC-based systems, they are ultimately limited to running on a single PC as the hardware is not designed to support shared memory between separate systems. For example, Steven Marsh found that a single-threaded neural computation system written in C required  $48.8 \, \mathrm{s}$  to perform a neural computation of 300 ms of activity for 256k Izhikevich neurons, using the benchmark neural network presented in Section 8.2, which is  $163 \times \mathrm{slower}$  than real-time (Moore *et al.*, 2012). This is broadly comparable to the time-scale of supercomputer-based systems, but for a massively smaller neural network scale.

It would be relatively trivial to perform neural computations of many unconnected neural networks using many PCs to create computations with the same total number of neurons as the neural networks used with supercomputer-based neural computation systems, but this is not comparable as the separate, small computations would not model the full set of synaptic connections in the larger neural network. This provides support for the Communication-Centric Hypothesis.

#### 2.4.3 **GPU-based systems**

Between supercomputer-based and PC-based systems sit a more recent class of neural computation systems based on Graphics Processing Units (GPUs). These can provide real-time performance for reasonably large neural networks (for example Fidjeland and Shanahan (2010) report computations of up to  $3 \times 10^4$  Izhikevich spiking neurons in real-time), but they struggle to scale to larger neural networks using additional GPUs as communication between GPUs is only available via the CPU in the host PC, a limit which supports the Bandwidth Hypothesis.

# 2.5 Hardware-based neural computation

Hardware-based neural computation systems typically separate modelling neurons, modelling the topology of a neural network and modelling synaptic connections into separate, interconnected tasks that operate in parallel, using separate circuits. We will survey methods for performing each of these tasks separately as different methods are often combined in systems by other researchers.

### 2.5.1 Modelling neurons

Hardware-based neural computation systems can model neurons using both analogue circuits and mathematical models. Between these two modelling methods are models that directly map each neuron into hardware using a dedicated digital circuit with similar behaviour to an analogue neuron model.

#### Analogue models

Analogue neuron models use an analogue circuit with components that mimic the behaviour of biological neurons. These range from neuron models that closely replicate the structure of biological neurons such as those implemented by Mahowald and Douglas (1991), Saighi *et al.* (2005) and Alvado *et al.* (2004), which all implement the Hodgkin-Huxley model (1952), to those that replicate only the spiking behaviour of biological neurons, such as the array of leaky integrate and fire neurons implemented by Indiveri *et al.* (2006). Basu *et al.* (2010) use a combination of hardware blocks that allows computation with both integrate and fire neurons and more complex multichannel neuron models such as Hodgkin-Huxley.

In some cases the parameters of the neuron model can be altered, using an analogue memory (Saighi *et al.*, 2005) or a more conventional digital memory (Alvado *et al.*, 2004), while in others the ability to alter parameters is more limited, for example only allowing spike threshold voltages to be altered (Mahowald and Douglas, 1991). Basu *et al.* allow the behaviour of their configurable blocks to be altered using programmable floating gate transistors.

The biggest weakness of analogue neuron models is their lack of scalability, for example Indiveri *et al.* (2006) implement 32 neurons on a chip, while Saighi *et al.* (2005) implement 5 and Basu *et al.* up to 84 integrate and fire neurons or a smaller number of Hodgkin-Huxley neurons.

Analogue components have large physical size compared to the transistors used in digital systems, and hence the number of neurons that can be modelled on a single device using analogue neuron models is limited.

#### Direct mapping into hardware

An evolution of analogue neuron models are digital models which replace each analogue neuron with a digital neuron implemented in a hardware description language (HDL) such as Verilog or VHDL (Bailey, 2010; Upegui *et al.*, 2005). The number of neurons that can be modelled using a single chip is broadly comparable with analogue models. Bailey (2010) implements 100 neurons and 200 synaptic connections on a Xilinx Virtex 5 100T FPGA, while Upegui *et al.* (2005) implement 30 neurons with up to 900 synaptic connections with a more constrained topology on a Xilinx Spartan II xc2s200 FPGA.

The scale of a neural computation system using direct mapping is limited by needing a separate HDL block to represent each neuron, although it is possible to time-multiplex HDL blocks in

some cases, such as if the topology of a neural network forms a regular grid (Yang *et al.*, 2011). Maguire *et al.* (2007) take another approach, with neuron state being stored in memory and HDL blocks being allocated to neurons by a coordinating processor, allowing these blocks to be time-multiplexed. This allows significantly more neurons to be modelled per chip, around  $2 \times 10^3$  on an unspecified Xilinx FPGA.

#### Mathematical models

Hardware-based neural computation systems can use the same mathematical neuron models as software-based neural computation systems, particularly simple spiking neuron models. Using discrete-time mathematical neuron models allows compute resources to be shared between neurons using time-multiplexing, allowing the number of neurons that can be modelled by each resource to be increased significantly. The proportion of total resources required by each neuron depends on the sampling interval of the neuron model.

One method of evaluating neuron modelling equations in a hardware-based system is using many small processor cores running simple embedded software. This approach is taken by Jin *et al.* (2008), who use a network of custom ASICs with up to 20 small ARM processor cores per chip, with around 10<sup>3</sup> neurons per core.

Another method of evaluating neuron modelling equations in a hardware-based system is converting them into a data-flow pipeline (Thomas and Luk, 2009; Cassidy *et al.*, 2011; Martinez-Alvarez *et al.*, 2007; Rice *et al.*, 2009). Mathematical neuron models are amenable to being converted to pipelines with many stages (Rice *et al.* use 23 stages for an Izhikevich neuron model), as the neuron modelling equations must be evaluated for every neuron in a neural network once per sampling interval, resulting in simple control flow with no branches that would require a pipeline to be flushed.

Since each neuron is represented by a flow of data rather than by physical resources, the throughput of both the embedded software and data flow approaches and hence the number of neurons in a real-time neural computation is limited by the ability of the neural computation system to fetch this data from memory. This agrees with the Bandwidth Hypothesis.

### 2.5.2 Modelling neural network topology

Modelling the topology of a neural network requires some form of interconnect in a neural computation system. Within an individual device (either custom ASIC, FPGA or CPU) this interconnect can be provided by internal wiring (either fixed, reconfigurable or an on-chip network), but if a neural computation system is to scale to multiple devices (as suggested by the Scalability Hypothesis), some kind of inter-device interconnect will be needed.

#### **Analogue wiring**

Pure analogue neuron models use voltages on wires between neuron blocks to model the topology of a neural network. For example, Saighi *et al.* (2005) connect their analogue neuron modelling blocks together using reconfigurable wiring controlled by data in a SRAM, similar to the method used to control routing in FPGAs.

### Digital wiring

Digital wiring can be used to model the topology of a neural network, particularly when neuron models are directly mapped into hardware using Field Programmable Gate Arrays (FPGAs), and also in some custom neural computation systems, such as those by Alvado *et al.* (2004) and Basu *et al.* (2010). While FPGA-based neural computation systems using this approach are much easier to implement than custom systems as FPGAs are readily available to researchers, the topology of a neural network can only be altered by resynthesising a FPGA bitstream, which is time-consuming. Altering a neural network topology at run-time is possible using dynamic partial reconfiguration, as done by Upegui *et al.* (2005), but this requires that a portion of the FPGA bitstream is resynthesised for every topology change, which rules out frequent changes.

Modelling the topology of a neural network using wiring that directly mirrors this topology is often limited to single-chip systems as extending this type of topology modelling to multiple chips requires more pins than can be implemented on a chip package, which suggests that this method of neural network topology modelling is not suited to creating neural computation systems for large neural networks.

The number of neurons and connections that can be modelled per chip is also limited by routing resources, as connections between neurons tend not to form regular grid pattens, unless the arrangement of these connections is artificially limited by the architecture (Upegui *et al.*, 2005). This provides support for the Communication-Centric Hypothesis.

#### Packet-based signalling

The topology of a neural network can be modelled more abstractly by modelling neuron spikes (or other types of communication) using packets that indicates the identity of the source neuron (and possibly other information), commonly called AER packets (Boahen, 2000). These packets must be transmitted to target neurons using some form of network.

The topology of a neural network is then modelled using a routing system that identifies which source neurons are connected to which target neurons. This requires a routing table, which is typically stored in off-chip memory in larger neural computation systems (Jin *et al.*, 2008; Cassidy *et al.*, 2011). The memory needed to store this routing table is typically orders of magnitude larger than that needed to store neuron modelling equation parameters when the number of target neurons per source neuron is high (high fan-out), and hence the scale of neural network that can be handled by these neural computation systems in real-time is bounded by memory bandwidth, supporting the Bandwidth Hypothesis.

Packet-based signalling is particularly suited to modelling the topology of a neural network in neural computation systems that span multiple chips, for example Indiveri *et al.* (2006) use analogue neuron and synapse models with packet-based signalling for inter-chip communication. It can also be used to model the topology of a neural network within a chip using an on-chip network (Dally and Towles, 2001). Packet-based signalling could be used just for long-distance connections, such as in the system implemented by Emery *et al.* (2009), which arranges neurons into tiles and uses programmable logic for connections within a tile and packet-based signalling for long-distance and inter-chip connections. Other systems such those implemented by Jin *et al.* (2008), Thomas and Luk (2009) and Cassidy *et al.* (2011) use an on- and inter-chip network to model the entire neural network topology.

### 2.5.3 Modelling synaptic connections

Synaptic connections can be modelled using either analogue models or arithmetic models, both with varying levels of complexity.

### Analogue models

The behaviour of synaptic connections can be modelled using analogue hardware, with a separate hardware block for each synaptic connection. This allows for a more complex range of synaptic behaviour (particular plasticity) than delay-weight models. For example Rachmuth *et al.* (2011) implement a detailed model of a single synaptic connection on a single chip using a complex model involving ion channels and supporting synaptic plasticity. Even with less complex analogue synaptic connection models, the number of neurons and synapses that can be implemented on a single chip is limited as analogue synaptic connection models take significant chip area, for example Indiveri *et al.* (2006) report 32 neurons and 256 synapses per chip. This is a mean fan-out of only 8, compared to  $10^3$  in the human brain. Given the resource requirements of each synapse, it would appear that implementing neural computation with biologically-plausible fan-out using an analogue synapse model is not possible.

#### Arithmetic models

If a simple delay-weight synapse model is used then modelling synaptic connections requires determining what the delay and weight of each connection should be, applying the delay and then summing the weights of each synaptic update for each neuron. Jin *et al.* (2008), Maguire *et al.* (2007), Cassidy *et al.* (2011) and Rice *et al.* (2009) all store the delay and weight of each synaptic connection in memory and then fetch it when a spike is received from a source neuron. Basu *et al.* (2010) encode synaptic weights in the interconnect between neuron blocks using floating gate transistors.

Jin *et al.* apply the delay and sum the weights using embedded software and temporary memory while Maguire *et al.*, Cassidy *et al.* and Rice *et al.* use dedicated hardware. Maguire *et al.* provide a dedicated hardware block for each synapse while Cassidy *et al.* use a data-flow processing pipeline and store the resulting summed value in memory before it is input to the neuron model.

With the parameters of each synaptic connection stored in memory, memory bandwidth limits the number of synaptic connections that can be modelled by a neural computation system in a given time period, as suggested by the Bandwidth Hypothesis.

# 2.6 Design decisions

The evaluation of neural computation systems reveals several major decisions that need to be made when designing a massively parallel neural computation system:

#### Software or hardware implementation

Software-based neural computation systems allow a wide variety of neuron models to be used, but they are not capable of performing massively parallel neural computation in real-time on platforms available to the majority of researchers. Hardware-based systems add many constraints but show significantly more potential for massively parallel computation.

#### Neuron modelling

While neuron modelling using analogue hardware has the potential to be significantly more accurate than digital modelling (since analogue hardware operates in continuous-time and digital in discrete-time), analogue hardware implementations are restricted to custom ASICs and show limited potential to scale to massively parallel computations, particularly as analogue components use a large amount of chip area. Hence a discrete-time, digital neuron model is most appropriate for massively parallel neural computation. The Izhikevich model will be used as it has an attractive combination of biological plausibility and computational complexity compared to other models such as integrate and fire.

#### Synaptic connection modelling

Similarly synaptic connections can be modelled using either analogue or digital hardware. While analogue again gives potential for greater accuracy and complex modelling of synapse behaviour, each synaptic connection will need dedicated hardware, which is unfeasible in a system with millions of neurons and billions of synaptic connections. In the digital domain it is possible to model the behaviour of synaptic connections using a range of models, but a simple model of discrete delay and weight shows the most potential for scaling to massively parallel neural computation.

### Neural network topology modelling

A variety of methods have been used to model the topology of neural networks in neural computation systems. Many are based on providing dedicated wiring that mimics each connection between source and target neurons, often using the reconfigurable routing resources in a FPGA, but these methods exhibit poor scaling. Modelling neural network topology using AER packets shows significantly more scaling potential, particularly when combined with an on- and inter-chip network. This means that the neural network topology will need to be stored in a routing table. The routing table can held in on-chip memory, but this cannot scale to massively parallel neural computations, particularly computations of neural networks with high fan-out as this results in large routing tables that will not fit in on-chip memory. Hence at least some of the data describing the topology of a neural network will need to be held in off-chip memory.

#### Resource sharing

A system using a discrete-time neuron model allows for the hardware used to model neurons and their communication to be time-multiplexed. Given that the equations used in the neuron model will need to be evaluated at around 1 ms intervals (see Section 3.2.3) and that the pipelines used to evaluate these equations can operate at 100s of MHz, the potential scale of a neural computation is significantly increased by time-multiplexing resources.

#### **Numerical precision**

Researchers who aim to create large-scale neural computation systems often use fixed-point arithmetic for their neuron models, as it is less complex than floating-point and hence has greater scaling potential. There will be a loss of accuracy as a result, manifested largely in differing spike times, but this is not particularly concerning as the overall spike pattern resulting from a neural computation (and in particular the probability density of the distribution of these spikes (Berger and Levy, 2010)) is of more interest than the exact timing of individual spikes.

#### Time-scale

Neural computation systems created by other researchers range from being orders of magnitude slower than real-time to orders of magnitude faster than real-time. The time-scale used by each system depends on the goals of the researchers who created it, and on limitations imposed by the system itself, such as maximum clock frequency or memory and communication bandwidth.

Selection of a time-scale is hence somewhat arbitrary, particularly if a neural computation system is implemented using data-flow pipelines where the volume of data that can be processed in a given time period is effectively fixed by available memory bandwidth, and hence the size of neural network that can be handled by the neural computation system is proportional to the time-scale used and the number of memory channels in the system.

This work uses a time-scale of real-time (that is that the computation of 1 ms of neural network activity takes 1 ms) as this will ease comparison with other large neural computation systems such as that by Jin *et al.* (2008), and also allow for interfacing to real-time systems such as external sensors in the future.

### 2.7 Conclusion

When creating a massively parallel neural computation system that operates in real-time and that can scale to computations of large neural networks with high fan-out, we have much to learn from other neural computation systems. It is clear that a massively parallel neural computation system must model neurons using a digital, discrete-time neuron model (such as the Izhikevich spiking neuron model) as neural computation with analogue neuron models has only been demonstrated for very small scale neural networks.

It is also clear that neural network topology should be modelled using packet-based signalling over an on- and inter-chip network, as other neural network topology modelling methods do not allow a neural computation system to scale beyond a single chip, which is essential for large-scale neural computation systems. Packet-based signalling also allows time-multiplexing of resources, which allows a massive increase in the scale of a neural computation. Further resource saving and hence increased scale can be achieved using fixed-point arithmetic in place of floating-point in neuron models.

The biggest unsolved challenge is how to efficiently model neural network topology and synaptic connections, which can be referred to as communicating and applying synaptic updates. It is clear that an on- and inter-chip network should be used to do this. The amount of data and bandwidth that will be needed to model the topology of a large-scale neural network and to communicate and apply synaptic updates in real-time must be analysed, as the Bandwidth Hypothesis suggests that the scale of neural network that can be handled by a neural computation system in real-time is bounded by inter-device communication bandwidth and memory bandwidth. We begin by analysing the high-level requirements of massively parallel neural computation in the next chapter and then develop these requirements into system resource requirements in Chapter 4.

#### **High-level requirements** 3

#### Introduction 3.1

We have chosen to use the Izhikevich spiking neuron model (2003) to perform massively parallel neural computation. While it is a "black-box" model and its equations bear little direct relation to the internal processes of biological neurons, the model is capable of reproducing the spiking patterns of a wide variety of types of biological neuron (Izhikevich, 2004). Also it has an attractive combination of biological plausibility and computational complexity compared to other models such as integrate and fire, as discussed in Section 2.3.2.

In its original form the model is unsuitable for implementation in a time-multiplexed, digital system as its equations are designed to operate in continuous-time, and so they must be converted into discrete-time alternatives. Further conversion can be applied to replace floating-point arithmetic with fixed-point, to precompute constants and to eliminate terms relating to the length of the sampling interval. This yields much simpler versions of the model's equations which are suited to massively parallel neural computation.

The communication properties of biological neural networks are examined to form some initial bounds on the character and number of synaptic updates that a massively parallel neural computation system will need to handle, which will allow the resource requirements of massively parallel neural computation to be analysed in Chapter 4 and help to evaluate the hypotheses proposed in Chapter 1.

#### 3.2 The Izhikevich spiking neuron model

Izhikevich's spiking neuron model (2003) uses a pair of differential equations to model the behaviour of a single neuron. Equation 3.1a calculates the membrane potential of the neuron and Equation 3.1b the refractory voltage. These equations have two variables (v and u) and two constants (a and b). An additional variable (I) represents the sum of all the synaptic updates targeted at the neuron.

An action potential ('spike') is produced if  $v \ge 30 \,\mathrm{mV}$ , in which case v and u are reset by Equation 3.1c and Equation 3.1d respectively. This requires two more equations with two constants (*c* and *d*).

$$\frac{dv}{dt} = 0.04v^2 + 5v + 140 - u + I \tag{3.1a}$$

$$\frac{dv}{dt} = 0.04v^2 + 5v + 140 - u + I$$

$$\frac{du}{dt} = a(bv - u)$$

(3.1a)

If  $v \ge 30$ mV after  $\frac{dv}{dt}$  and  $\frac{du}{dt}$  are evaluated then

$$v = c (3.1c)$$

$$u = u + d \tag{3.1d}$$

The model appears to be capable of reproducing the behaviour of a range of types of biological neuron by altering parameters a to d. Izhikevich provides several examples (2003).

#### 3.2.1 Conversion to discrete-time

Equation 3.1 operates in continuous-time, which makes it unsuitable for evaluation using a digital system, particular if we wish to increase the scale of a neural computation by time-multiplexing resources.

Thankfully it is straightforward to convert Equation 3.1 to operate in discrete-time. The simplest method is to use Euler integration. Given equations of the form in Equation 3.2 they can be converted to discrete-time equations, sampled at intervals of length  $\delta t$  by using Equation 3.3.

$$\frac{dy}{dt} = f(x,y)$$

$$y(x_0) = y_0 \tag{3.2}$$

$$x_{n+1} = x_n + \delta t$$

$$y_{n+1} = y_n + \delta t \cdot f(x_n, y_n)$$

(3.3)

Applying this method to Equation 3.1 yields the discrete-time version of the Izhikevich neuron model in Equation 3.4.

$$v_{n+1} = v_n + \delta t (0.04(v_n)^2 + 5v_n + 140 - u_n + I)$$

$$u_{n+1} = u_n + \delta t a (bv_n - u_n)$$

If  $v_{n+1} \ge 30$ mV after  $v_{n+1}$  and  $u_{n+1}$  are evaluated then

$$v_{n+1} = c$$

$$u_{n+1} = u_{n+1} + d (3.4)$$

### 3.2.2 Conversion to fixed-point

Equation 3.4 operates in discrete-time, but still relies on floating-point arithmetic, which is computationally expensive, particularly when aiming for a massively parallel system. By adapting the work of Jin *et al.* (2008), we can convert Equation 3.4 to use fixed-point arithmetic, which can be evaluated using comparatively simple hardware, particularly if multiplication or division can be approximated to a power of 2, allowing simple bit shifts to be used in their place.

I will extend the work of Jin *et al.* by providing additional intermediate steps to preserve  $\delta t$  (they used the simplifying assumption  $\delta t=1$ ), and to assist in understanding the process involved in transforming the equations.

The first step is to transform Equation 3.4 into Equation 3.5 by factoring out  $v_n$  and multiplying by a. The components of the equation that are applied if  $v \ge 30$ mV will be omitted for now as they do not require transformation.

$$v_{n+1} = v_n + \delta t [v_n(0.04v_n + 5) + 140 - u_n + I]$$

$$u_{n+1} = u_n + \delta t (abv_n - au_n)$$

(3.5)

| Variable / Parameter | Scaling Factor |

|----------------------|----------------|

| v                    | $p_1$          |

| и                    | $p_1$          |

| а                    | $p_2$          |

| b                    | $p_2$          |

| С                    | $p_1$          |

| d                    | $p_1$          |

Table 3.1: Mapping of variables / parameters to scaling factors (Jin et al., 2008)

| Original Value   | Replacement |

|------------------|-------------|

| $vp_1$           | V           |

| $up_1$           | U           |

| abp <sub>2</sub> | A           |

| $-ap_2$          | В           |

| $cp_1$           | C           |

| $dp_1$           | D           |

Table 3.2: Mapping used to simplify Equation 3.6 (Jin et al., 2008)

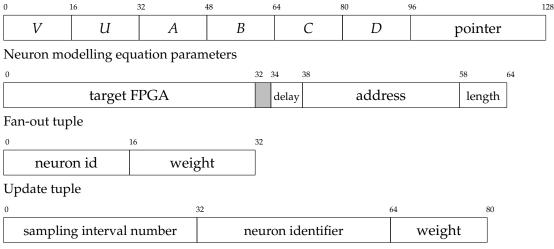

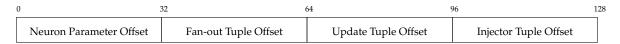

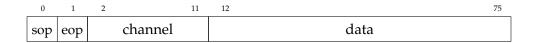

The floating-point variables and parameters can now be converted to fixed point by applying scaling factors according to the mapping in Table 3.1. Additional multiplication / division by these scaling factors is used to keep the equations balanced. The result is Equation 3.6.

$$v_{n+1}p_1 = v_np_1 + \delta t[v_np_1((0.04p_2v_np_1)/p_2 + 5p_1)/p_1 + 140p_1 - u_np_1 + Ip_1]$$

$$u_{n+1}p_1 = u_np_1 + \delta t([(abp_2)v_np_1]/p_2 + [(-ap_2)u_np_1]/p_2)$$

If  $v_{n+1} \ge 30$ mV after  $v_{n+1}p_1$  and  $u_{n+1}p_1$  are evaluated then

$$v_{n+1}p_1 = cp_1$$

$$u_{n+1}p_1 = u_{n+1}p_1 + dp_1$$

(3.6)

Notice that the majority of the scaling factors are applied directly to variables or parameters, with just a few additional scaling factors needed to keep the equations balanced. Equation 3.6 can be simplified by storing parameters in memory with the relevant scaling factors already applied. Using the mapping in Table 3.2, this results in the simplified Equation 3.7.

$$V_{n+1} = V_n + \delta t [V_n((0.04p_2V_n)/p_2 + 5p_1)/p_1 + 140p_1 - U_n + Ip_1]$$

$$U_{n+1} = U_n + \delta t (AV_n + BU_n)/p_2$$

If  $V_{n+1} \ge 30$ mV after  $V_{n+1}$  and  $U_{n+1}$  are evaluated then

$$V_{n+1} = C$$

$$U_{n+1} = U_{n+1} + D$$

(3.7)

The accuracy and ease of evaluation of Equation 3.7 depends on the values of the scaling factors  $p_1$  and  $p_2$ . After experimentation, Jin *et al.* selected the values in Table 3.3 on the facing page.

| Scaling Factor | Value |

|----------------|-------|

| $p_1$          | 256   |

| $p_2$          | 65536 |

Table 3.3: Scaling factors selected by (Jin et al., 2008)

| Operation      | Equivalent Shift |

|----------------|------------------|

| Multiply $p_1$ | << 8             |

| Multiply $p_2$ | << 16            |

| Divide $p_1$   | >> 8             |

| Divide $p_2$   | >> 16            |

Table 3.4: Mapping of scaling factors to bit shifts (Jin et al., 2008)

Since these are powers of 2, simple bit shifts can be used in place of comparatively expensive multiplication and division to apply these scaling factors, resulting in the equivalent bit shifts in Table 3.4. After applying these transformations (and with the values of  $p_1$  and  $p_2$  fixed as in Table 3.3), Equation 3.7 becomes Equation 3.8.

$$V_{n+1} = V_n + \delta t [$$

$$V_n(((0.04 << 16)V_n) >> 16 + 5p_1) >> 8$$

$$+ (140 << 8) - U_n + (I << 8)$$

$$]$$

$$U_{n+1} = U_n + \delta t (AV_n + BU_n) >> 16$$

(3.8)

Finally the shifted constants in Equation 3.8 can be simplified, resulting in Equation 3.9.

$$V_{n+1} = V_n + \delta t [$$

$$(V_n((2621V_n) >> 16 + 1280)) >> 8$$

$$+ 35840 - U_n + (I << 8)$$

$$]$$

$$U_{n+1} = U_n + \delta t (AV_n + BU_n) >> 16$$

If  $V_{n+1} \ge 30$ mV after  $V_{n+1}$  and  $U_{n+1}$  are evaluated then

$$V_{n+1} = C$$

$U_{n+1} = U_{n+1} + D$  (3.9)

Note that while it might appear that the calculation of  $U_{n+1}$  in Equation 3.9 can be simplified by removing the shift operation and reverting to using parameters ab and -a rather than A and B, both of the original groups of parameters need to be shifted to allow them to be stored using a fixed-point representation.

#### 3.2.3 Sampling interval size

In order to use Equation 3.9 to perform neural computation, a value must be chosen for the sampling interval size ( $\delta t$ ). If a neural computation system uses time-multiplexed resources then the sampling interval size has a direct effect on the number of neurons in a real-time

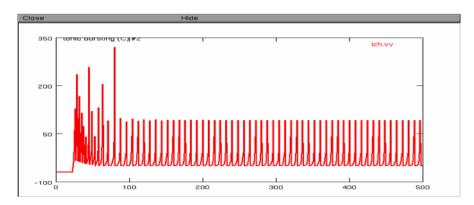

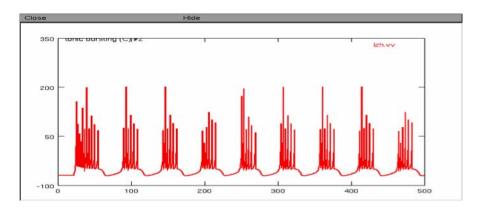

Figure 3.1: Result of evaluating Equation 3.4 with the parameters in Table 3.5 and  $\delta t = 1.0$ ms.

Figure 3.2: Result of evaluating Equation 3.4 with the parameters in Table 3.5 and  $\delta t = 0.5$ ms.

computation. Given the same resources, using a smaller sampling interval size will result in a more accurate computation of fewer neurons, while a larger sampling interval size will result in a potentially less accurate computation of more neurons.

In addition, there is potential for the Euler integration method to become unstable and produce totally inaccurate results if the sampling interval size is too large. Particularly when used with coupled differential equations such as those in the Izhikevich neuron model, it is possible for the results given by Equation 3.4 to be radically different from those that would be given if Equation 3.1 were evaluated in continuous-time. The fixed-point arithmetic used in Equation 3.6 introduces further inaccuracies.

As an example, consider the effects of evaluating Equation 3.4 with the parameters in Table 3.5. Figure 3.1 shows the results with  $\delta t=1.0$ ms while Figure 3.2 shows the result of evaluating the same equation with  $\delta t=0.5$ ms. These graphs were produced using NEURON (Hines and

| Parameter | Value            |

|-----------|------------------|

| $v_0$     | -70              |

| $u_0$     | -14              |

| а         | 0.02             |

| b         | 0.2              |

| С         | -50              |

| d         | 2                |

| $I_n$     | 15 for $n >= 22$ |

Table 3.5: Parameters used to illustrate instability produced by an overly-large sampling interval size. Note that these parameters correspond to those in Equation 3.1, and so must be transformed as described in Table 3.2 before being used in Equation 3.4

Carnevale, 1997). Figure 3.1 is clearly radically different from Figure 3.2, in particular there are several peaks in Figure 3.1 which correspond to extended flat areas in Figure 3.2.

This simple experiment illustrates that caution is needed when selecting a suitable value for  $\delta t$ . Further experiments with Equation 3.6 using both NEURON (using Equation 3.4) and a simple spreadsheet model in Microsoft Excel (using Equation 3.10) appear to indicate that increasing  $\delta t$  leads to a sudden, sharp transition from results similar (at least in the timing of peaks) to Figure 3.2 to results similar to Figure 3.1. It is likely that the exact value of  $\delta t$  when this transition occurs is dependent on the parameters of Equation 3.4.

Therefore there is a tradeoff between the number of neurons in a real-time computation and the accuracy of Equation 3.4 for a given value of  $\delta t$ . It is possible that there might be a value of  $\delta t$  that is safe regardless of the parameters used. This will not be investigated further – instead the value of  $\delta t$  will be fixed and the operation of the neural computation system will be validated using benchmark neural networks.

### 3.2.4 Final simplification

If, as suggested by Jin *et al.*,  $\delta t = 1$  ms, then a final simplification of Equation 3.9 can be made to produce Equation 3.10.

$$V_{n+1} = (V_n((2621V_n) >> 16 + 1536)) >> 8 + 35840 - U_n + (I << 8)$$

$U_{n+1} = U_n + (AV_n + BU_n) >> 16$

If  $V_{n+1} \ge 30$ mV after  $V_{n+1}$  and  $U_{n+1}$  are evaluated then

$$V_{n+1} = C$$

$$U_{n+1} = U_{n+1} + D$$

(3.10)

### 3.2.5 Numerical precision

The variables and parameters of Equation 3.10 could be stored using either floating-point or fixed-point precision. Using fixed-point precision reduces hardware complexity compared to floating-point and can also reduce the data storage (and hence memory bandwidth) requirements of processing the equation parameters. IEEE single precision floating-point requires 32 bits per value while IEEE double precision requires 64 bits. In comparison fixed-point precision can use any number of bits, though there will be a loss of accuracy compared to floating-point if fewer bits are used, manifesting itself as rounding errors.

Since reducing the memory size and bandwidth requirements of modelling each neuron increases the number of neurons that can be modelled per memory channel, 16 bit fixed-point precision will be used for the variables and parameters of Equation 3.10 (in common with Jin *et al.*), with 32 bit precision used during calculations to prevent significant loss of accuracy. With 2 variables and 4 parameters this means that  $6 \times 16 = 96$  bits are needed for each neuron. The loss of accuracy relative to floating-point will manifest itself largely in slightly differing spike times owing to accumulation of rounding errors. In practice it is likely that this can be mitigated by altering the parameters of Equation 3.10 to bring the behaviour of each neuron in line with what would be expected if floating-point precision were used.

# 3.3 Communication properties of neural networks

Along with analysing the neuron model, the communication properties of biological neural networks must be analysed. Analysing neural communication properties will facilitate design and evaluation of an algorithm to communicate and apply synaptic updates, as some algorithms have varying workload depending on the volume of synaptic updates. Other algorithms dedicate resources to all possible synaptic connections regardless of whether they are active or not, and hence do not experience additional workload in proportion to the volume of synaptic updates, but these algorithms do not scale well as network size and fan-out increase.

The volume of communication between neurons depends on their:

- Fan-out

- Locality

- Spike frequency

- Synaptic delays

Each of these properties of biological neural networks will be analysed to consider their effect on the volume of synaptic updates that must be communicated and applied and hence methods used to achieve this in a massively parallel neural computation system.

#### 3.3.1 Fan-out

As a rough guide, we will assume that each neuron will send synaptic updates to (have a fan-out of) about  $10^3$  other neurons. This assumption is based on the human brain containing approximately  $10^9$  neurons, with  $10^{12}$  synaptic connections. Likewise each neuron will be able to receive synaptic updates from about  $10^3$  other neurons. However, this is only an assumption regarding the average case, and in principle individual neurons can exhibit significantly greater fan-out.

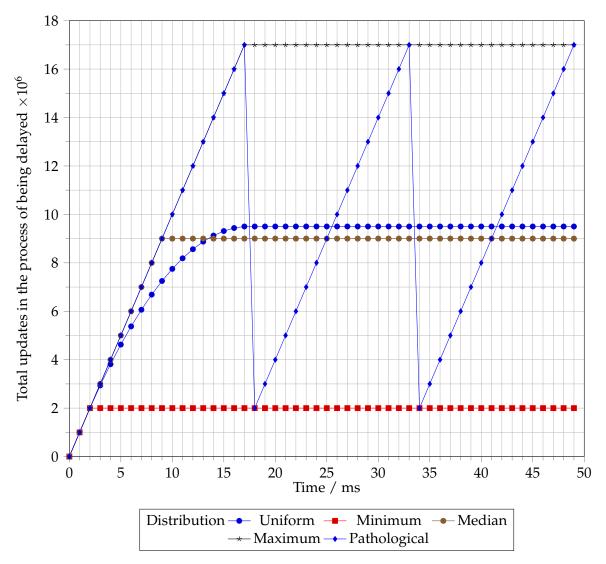

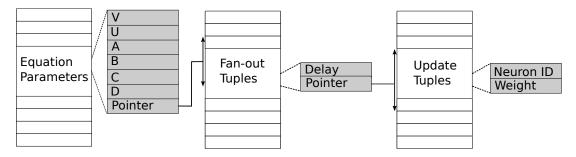

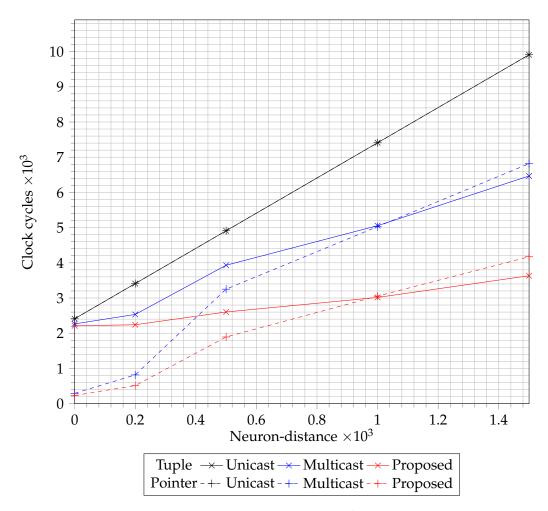

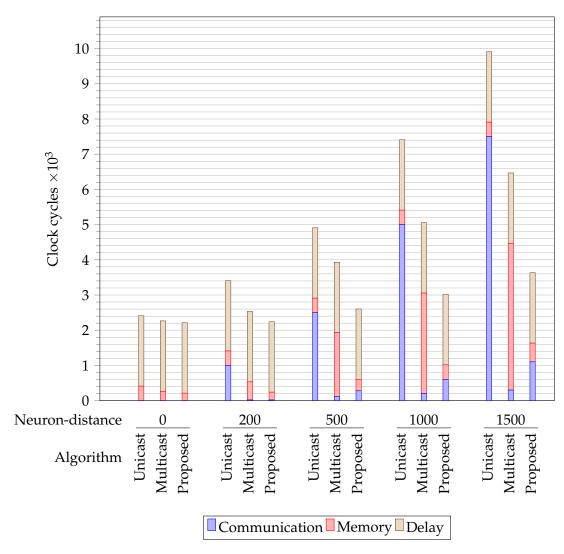

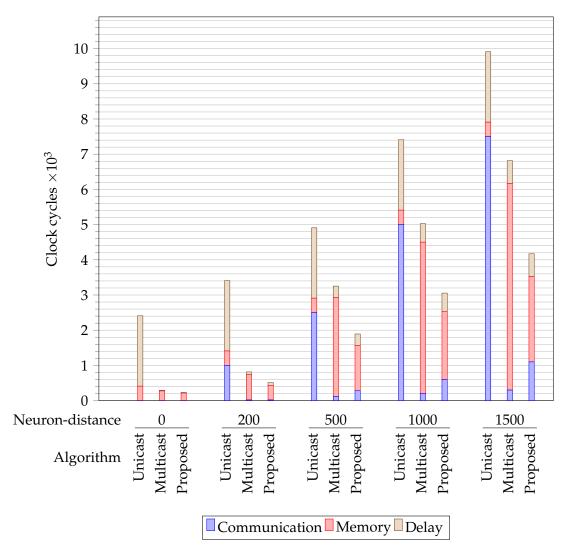

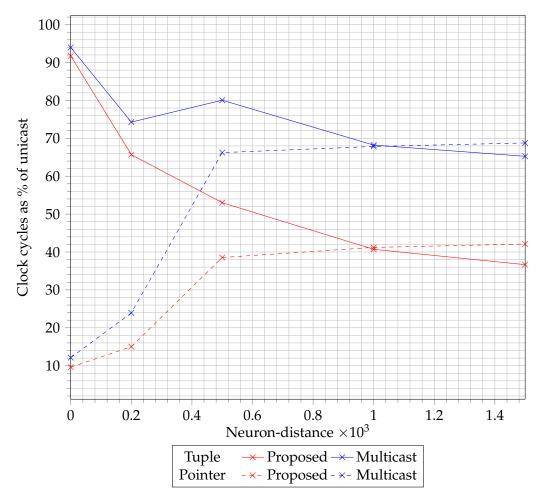

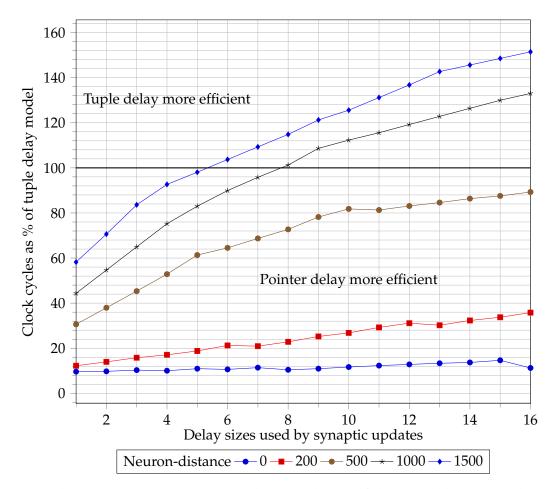

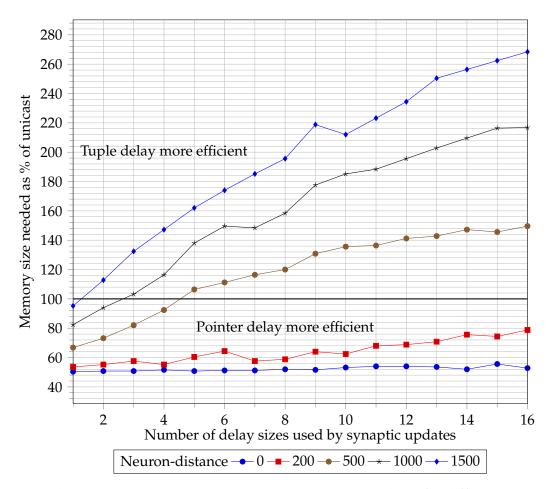

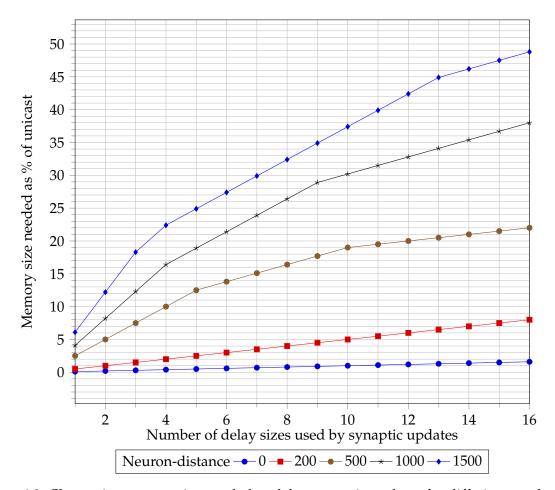

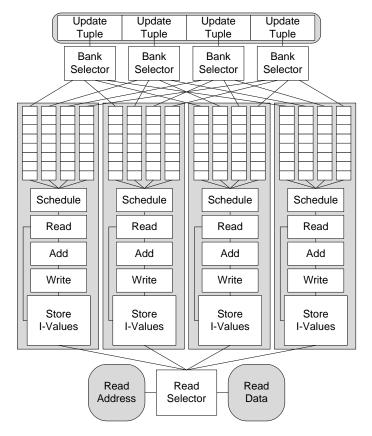

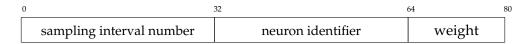

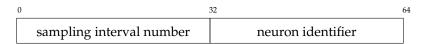

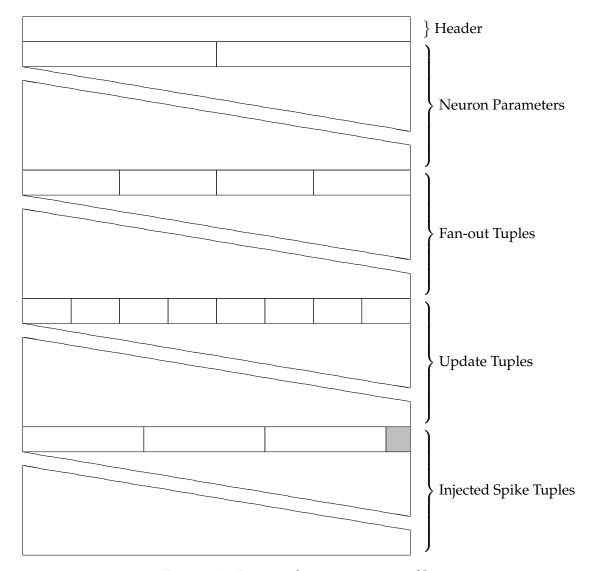

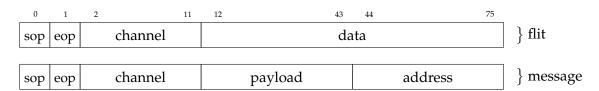

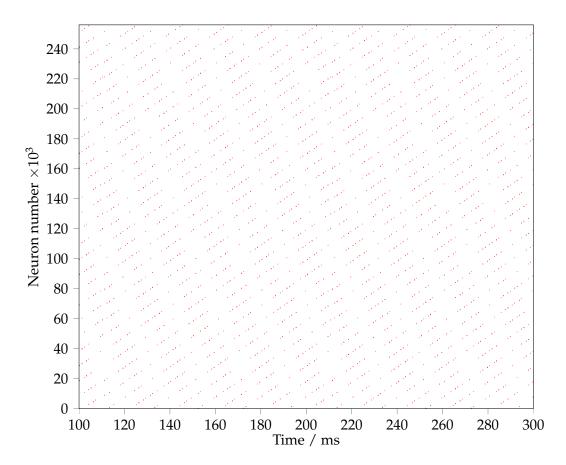

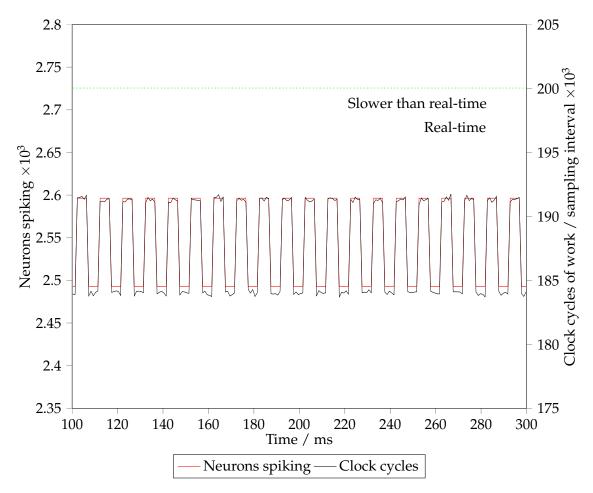

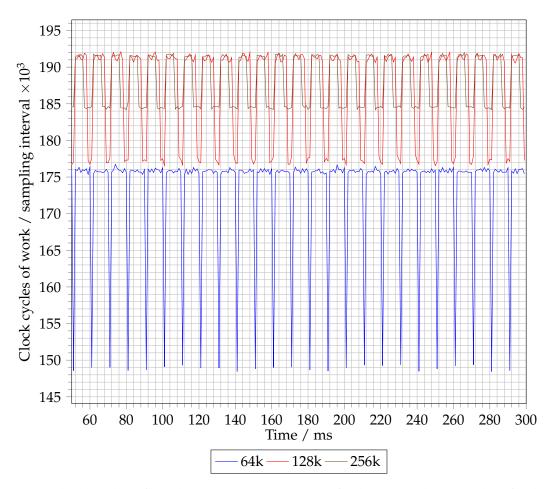

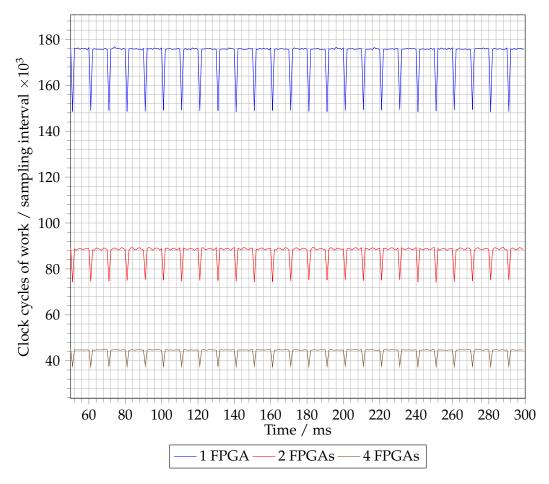

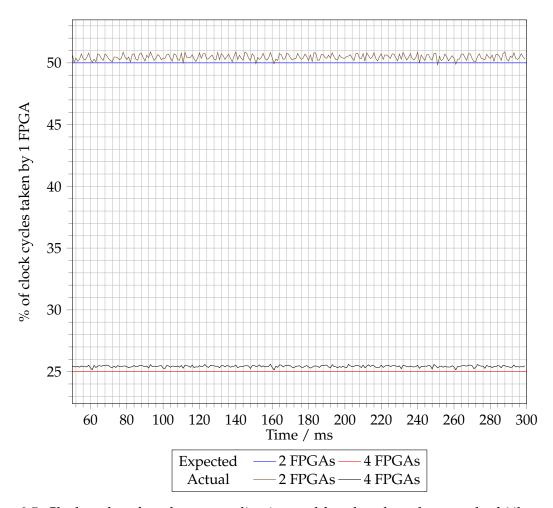

#### 3.3.2 Locality