Number 219

# Fairisle project working documents Snapshot 1

Ian M. Leslie, Derek M. McAuley, Mark Hayter, Richard Black, Reto Beller, Peter Newman, Matthew Doar

March 1991

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500 https://www.cl.cam.ac.uk/

© 1991 Ian M. Leslie, Derek M. McAuley, Mark Hayter, Richard Black, Reto Beller, Peter Newman, Matthew Doar

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

https://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986

# FAIRISLE PROJECT WORKING DOCUMENTS

# Snapshot 1 March 27, 1991

This report contains the current versions of the documents associated with the Fairisle project. These include both papers and draft documents. This collection of documents was made on March 27, 1991. Updated versions will be issued with later snapshot numbers, these will replace earlier versions.

# Contents

Fairisle: Network Architecture and Components

Ian Leslie and Derek McAuley

Fairisle Port Controller: Design and Ideas

Mark Hayter and Richard Black

Fairisle VME Interface (Draft)

Reto Beeler

A Slotted Ring Copy Fabric for a Multicast Fast

Packet Switch

Peter Newman and Matthew Doar

Universal Fairisle Connector (proposed)

Fairisle: A General Topology ATM LAN

# DRAFT

Ian Leslie and Derek McAuley

University of Cambridge Computer Laboratory

An experimental general topology local area network based on Asynchronous Transfer Mode (ATM) is described. This network is intended to be used to support multiservice traffic. Thus provision of guarantees of quality of service to various traffic types is an important feature of the network. In order to carry on quality of service experiments, one must have both a network which is inherently manageable, and the flexiblity to provide different management strategies.

Fairisle is supported by the SERC under Grant GR/F 6090.8 and by HP Laboratories Bristol.

# 1 Introduction

Fairisle is a research project investigating the architecture and management algorithms for a general topology ATM network which is to be used as a private or local area network.

Fairisle was begun in October 1989. It arose from work in the Computer Laboratory in ATM networks, multimedia communications, protocol architectures, host interface design and fast packet switching. The overall purpose of Fairisle is to investigate networks as well as switches. Such an investigation is as much concerned with how components fit together as it is with network components themselves.

In the tradition of the Computer Laboratory this investigation is based on experience of a real network moving real user data. Thus an early problem that Fairisle has faced is in designing and constructing components. These components will form the basis, or rather the experimental apparatus, on which the real experiments will take place.

A major goal of the Fairisle network is to support multiservice traffic, supplying guaran-

tees when required (e.g. on bandwidth, delay, cell loss). Decisions about what sort of guarantees are made and how many types of guarantee there are, have been left open for experimentation. It is the management of network resources which will be the most novel aspect of Fairisle.

In developing an network architecture which is to be used as a basis for experimentation in network resource management, one must produce an architecture that gives rise to a manageable network. By a manageable network we mean one in which both network resources and resource demands made by traffic are identifiable and quantifiable. The precision of guarantees given to different types of traffic will necessarily be related to the precision with which traffic demand is specified when communication is initiated.

As well as an architecture, we have developed an implementation of the network. This implementation will eventually include specific management algorithms, but in the first instance it must be sufficiently flexible to allow a variety of algorithms to be used and monitored.

The Fairisle Network Architecture is presented in the next section. Following this, section three describes the network implementation in terms of the network components. Section four outlines how devices will be attached to the network. Finally the current status of the implementation and some concluding remarks are made in section five.

# 2 Network Architecture

The most obvious features of the network architecture used on Fairisle is that is it ATM based and that it uses virtual circuits.

# ATM Motivation

Fairisle is an Asynchronous Transfer Mode<sup>1</sup> network. We are using ATM for a number of reasons. Briefly these are:

<sup>&</sup>lt;sup>1</sup>We consider ATM to be a generic term, that is, meaning the use of fixed sized cells in order to simplify switching, and make the performance of switches and the multiplexing more predictable.

- 1. ability to carry a variety of traffic

- 2. that a B-ISDN based on ATM will one day be the preferred wide area interconnect

- 3. our experience with ATM

- 4. that future network traffic demands are, and will continue to be, unpredicatble

The arguments for using ATM to provide network integration are well known (as are many of the counter arguments). However, we also believe that providing a continuim of services from delay insensitive traffic (such as traditional data) through to constant rate delay sensitive traffic (such as traditional voice) will be important for future networks. A time critical remote procedure call is an example of a communication which lies somewhere in this continuim rather than at one of the endpoints.

The expectation that B-ISDN will be the ubquitous high speed long haul interconnect, leads us not only to believe that the local distribution of B-ISDN traffic is important, but also that ATM provides an opportunity to integrate not just traffic types, but local and wide area communication. This has implications for network architecture — we are interested in ATM internetworking.

Finally, whatever the problems to be solved, and the penalties to be paid in running an ATM network we believe that the unpredictability of traffic demands, both in quality and quantity make ATM an attractive strategy. ATM provides a flexible network interface.

# Virtual Circuit Motivation

Fairisle is a virtual circuit (or perhaps more accurately a lightweight virtual circuit) network. Each ATM cell carries with it a virtual circuit identifier. Our reasons for choosing a virtual circuit approach are as follows:

- 1. VCIs in cells can be processed via very simple and fast hardware lookups in the switches

- 2. VCIs can be used to associate a cell with an arbitrary quality of service description (held at each switch)

- 3. VCIs (when allocated by the end system) can be used to simplfy the implementation of the end system interface

- 4. a virtual circuit is an obvious unit to which to attach a guarantee and which to police.

Broadband ISDN has come to a similar conclusion for similar reasons, although one could argue that virtual circuits are part of the ISDN culture.

We have considered approaches which do not use virtual circuits. One can imagine globally addressing each ATM cell and using fields in the cell header to indicate traffic type which could be used to facilitate the management of guarantees. However, using fields in the cell header restricts the number of different qualities of service that can be provided. Moreover, the virtual circuit approach is more natural, particularly when it comes to measure resource usage against resource guarantees.

#### 2.1 The Multi Service Network Architecture

The protocol architecture used in Fairisle, the Multi Service Network Architecture (MSNA) is more fully described in [McAuley 89].

MSNA is designed to support multiservice communication all the way up to the multimedia application. It achieves this in two ways:

- 1. by providing, where desired, application to application ATM cell communication, and

- 2. by streamlining (that is avoiding) multiplexing in end systems.

Providing application to application ATM cell communication means that applications are not constrained to use an adaptation layer which takes a view as to how communication should be handled. For example, if segmentation and reassembly are not required they are not used. An immediate consequence of wishing to provide application to application ATM cell communication is that MSNA must provide an internetworking layer which works on the basis of cell forwarding.

There are costs associated with multiplexing — these are often listed as bandwidth, processing and complexity [Tennenhouse 89], but in a multiservice environment multiplexing also introduces contention among traffic streams. The streamlining of multiplexing minimises these points of contention (although some may always exist) in end systems. This minimisation is important as each contention point places constraints on the scheduler within the end system; for example, in a real time system these constraints may require the scheduler to work much harder to find feasible schedules, or worse, cause missed deadlines. In MSNA, the virtual circuit identifier (VCI) can be used to identify the end application entity or indeed a single thread within the application entity. Thus it is possible to have a single contention point within the end system and reduce the constraints on the scheduler.

Virtual circuits are the units to which quality of service guarantees and priorities are given. Thus cells do not have an explicit priority field in them. MSNA does not dictate what qualities of service should be provided.

The lower layers of MSNA are concerned with cell transfer. MSNA uses an internetworking layer (analogous to IP) to provide end to end transfer of cells. The data link layer of MSNA is concerned with cell transfer on a link (where a link includes a simple topology LAN such as an Ethernet or Cambridge Fast Ring (CFR)<sup>2</sup>).

## 2.2 MSDL on Fairisle

The Multi Serivce Data Link layer (MSDL) is the network specific part of MSNA. In Fairisle, MSDL is concerned with how cells are transferred down a single link, either between a host and a switch or between two switches. Two MSDL entities transfer cells over an MSDL association which is identified by two virtual circuit identifiers, one for each direction. MSDL is also concerned with how associations are set up and how VCIs are allocated.

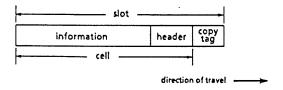

The format of a cell for the Fairisle network is shown in figure 1. As can be seen, there are four bytes of virtual circuit identifier (VCI), two bytes of framing and sequencing

<sup>&</sup>lt;sup>2</sup>The CFR is a 50Mbit/s slotted ring

information and 48 bytes of data.

| VCI       | FAS | DATA       |

|-----------|-----|------------|

| (4 bytes) | (2) | (48 bytes) |

Figure 1: Fairisle Cell Format

As part of association setup, an MSDL entity allocates the VCI for cells it is going to receive. The VCI has no structure visible outside the allocating entity. The allocating entity (which is the only entity which will have to process cells with that VCI) may of course place any internal structure it wishes on the VCI in order to make the processing task simpler<sup>3</sup>.

Per cell error detection and/or correction mechanisms are not defined by MSDL or higher layers. MSDL is designed to operate over a range of networks, and even within Fairisle it is required to operate over at least two significantly different transmission systems. Rather than define a generic mechanism within MSDL, each underlying transmission system implements a technique which is designed to deal with their individual error properties.

MSDL definitions and implementations also exist for the CFR, Ethernet, and the Cambridge Backbone Ring (CBR)<sup>4</sup> [Greaves 88].

# 2.3 MSNL

The Multi Service Network Layer (MSNL) concatenates a number of MSDL virtual circuits at MSNL routers. A series of concatenated associations which forms an end to end channel is an MSNL liaison.

A router maps an incoming VCI to an outgoing VCI and performs simple cell forwarding. This takes place at every Fairisle switch and at a MSNL router joining Fairisle to another MSDL based network – a CFR for example. This mapping is established at liaison set up

<sup>&</sup>lt;sup>3</sup>For example by only using some of the bits to perform direct lookups, by using some bits to indicate priority, etc.

<sup>&</sup>lt;sup>4</sup>The CBR is a 500Mbit/s slotted ring

time when the MSNL layer performs routing and establishes a series of associations based on the MSNL addresses of the correspondents, the state of the network and the requested quality of service. This connection set up mechanism is performed out of band.

MSNL only defines the purpose of a single bit in the in band information. When used, the frame bit delineates end to end frames, and is set in the last cell of a frame. No maximum size is defined for a frame, and it is conceivable that for some traffic classes the frame size will be a single cell (e.g. voice traffic).

The frame bit is set by the sender and will usually represent the unit of end to end recovery. The information is available at the receiver, but most importantly it can be used by the switch as part of the cell discard algorithm. During times of overload, when a switch discards a cell, it will preferentially discard cells arriving on the same virtual circuit up to and including the next cell with the frame bit set.

We envisage interworking with B-ISDN at the MSNL level by defining an appropriate MSDL instance over B-ISDN's null adaptation layer.

#### 2.4 MSSAR

Two bytes of the cell are shown as allocated for sequencing and framing information. MSNL defines the purpose of the framing bit only, the remaining (15) bits are available on an end to end basis. However, we have defined a generic sequencing mechanism which uses this field to identify lost cells, and although not a requirement, we envisage all traffic classes using this service. While the use of different sequencing mechanisms for each traffic class could provide a small saving in bandwidth, a generic solution allows the sharing of both software and hardware components.

The Multi Service Segmentation and Reassembly (MSSAR) is one user of this framing and sequencing service, providing the further services of end to end error detection / correction (and encryption if required) on blocks of data.

# 3 Network Components

The Fairisle network is an experimental network. It purpose is to provide insight into the management of ATM networks. Thus the most important consideration is flexibility rather than speed or cost.

## 3.1 The Fairisle Switch

The Fairisle switch is a space division ATM fast packet switch. It is input buffered and blocking<sup>5</sup>. The current switch size is 16 ports. The switch can be broken into two types of component: switch fabric and port controllers.

Port controllers are analogous to line cards in a telephone exchange. Their main functions in the Fairisle switch are to map VCIs, manage queues, select priority, select routing tags, and deal with blocking in the fabric. Each port controller (there are 16 in each switch) is connected to an input and output of the switch fabric.

The fabric is a very regular interconnection network. It is the place where cells contend for bandwidth. The fabric is relatively straightforward to describe; we will do this first.

# 3.2 The Fairisle Switching Fabric

## **Functional Description**

The main thrust of Fairisle is to experiment with networks. For this reason we have choosen to use a simple and easy to implement switch fabric, based almost entirely upon the Cambridge Fast Packet Switch [Newman 88]. A fabric based on a full crossbar would provide greater per line utilisation. However, using the same technology we can implement a somewhat faster version of our fabric and achieve approximately the same throughput; this is possible as our switch design does not require us to run the fabric at the same rate as the transmission system.

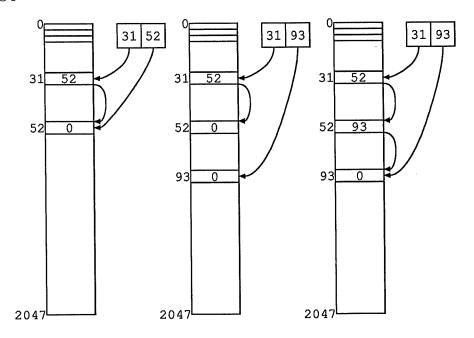

The Fairisle switch fabric is a 16 by 16 (that is 16 inputs, 16 outputs) fabric built up from

<sup>&</sup>lt;sup>5</sup>That is a cell may block another cell even though the cells are destined for different outputs

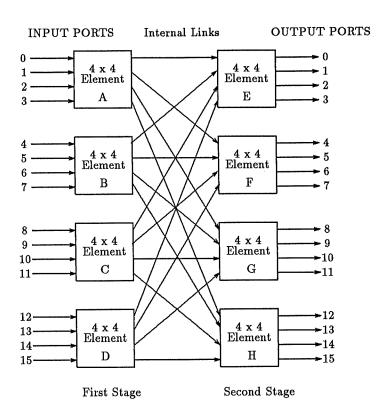

eight 4 by 4 crossbar switching elements arranged in a delta network as shown in figure 2. The delta network gives rise to the internal blocking. (Consider when port 0 and 1 both wish to send to ports 5 and 6 respectively. The cells both wish to use the internal link from element A to F; only one of them can.) Other switch sizes are permitted — in particular a non-blocking 4 by 4 switch can be built, or multipath 8 by 8.

Figure 2: A 16 Port Delta Network

Each arrow represents 8 data signals and a returning acknowledgement signal

The fabric is self routing, that is, the cells have prepended to them routing tags which tell the fabric which links the cells should be sent along. The routing tags also contain priority information (in fact a single bit is used) which is examined when two cells contend for the same link. The fabric is a two stage delta so there are two routing tags. Each switching crossbar element has four outputs so two bits of routing information are required for each tag. Each stage strips off the routing (and priority) information which it uses as it processes the cell. In fact it is easier for the fabric to strip off whole bytes so routing tags are padded to a full byte. This is shown in figure 3.

| (1 bit) (1 bit) (2 bits) (4 bits) |

|-----------------------------------|

|-----------------------------------|

Fabric Element Routing Tag

| Act     | Route   | Fill     |

|---------|---------|----------|

| (1 bit) | (1 bit) | (6 bits) |

Output Port Controller Routing Tag

|                 |                 | Output          | VCI       | FAS | DATA       |

|-----------------|-----------------|-----------------|-----------|-----|------------|

| Tag<br>(1 byte) | Tag<br>(1 byte) | Tag<br>(1 byte) | (4 bytes) | (2) | (48 bytes) |

Tagged Cell Entering Fabric

| Stage 2<br>Tag<br>(1 byte) | Output<br>Tag<br>(1 byte) | VCI<br>(4 bytes) | FAS<br>(2) |  |

|----------------------------|---------------------------|------------------|------------|--|

|----------------------------|---------------------------|------------------|------------|--|

Tagged Cell Entering Second Stage

| Output<br>Tag<br>(1 byte) | (4 1 | FAS<br>(2) |  |

|---------------------------|------|------------|--|

|---------------------------|------|------------|--|

Tagged Cell Leaving Fabric

Figure 3: Tagged Cell Formats at Various Stages

Since the fabric (or indeed an output port controller) may chose not to accept a cell, an acknowledgment signal is provided. If the cell is blocked in the fabric, the input port on which the cell was injected will see a low on the acknowledgement line, otherwise it will see whatever the output port controller chooses to respond with — in fact it is a clear return data path from output to input.

Whenever two or more cells contend for the same output of a switching element, arbitration takes place. Arbitration is done for each of the four outputs of a switching element. Each output arbiter runs an independent round robin system with two levels of priority. The input links are numbered 0 to 3 and the last input to have a cell (of any priority) selected is remembered:

- 1. A high priority cell (one with the priority bit set) is always selected in preference to a low priority cell

- 2. If two or more cells of the same priority contend, the last input which was selected is used as the base. The next input above (with suitable wrap around) the last selected is the one to be selected.

The question of priority within the fabric is an interesting one. Just how many priority levels within the fabric are required will be a subject for experimentation.

Our switch fabric implementation does not represent a large amount of work. We are hopeful that self routing crossbars of a reasonable size will appear on the market in the near future. We see no reason why we could not include them in a later version of the switch.

# Implementation

The fabric is implemented on a single board. The interconnection of switching elements into a delta network is entirely straight forward. The implementation problem is building a switching element.

Each element (a 4 by 4 crossbar) is built on a 4200 gate equivalent Xilinx programmable gate array. A link consists of eight unidirectional data signals and an acknowledgement signal travelling in the opposite direction. There are four input links and four output links making 72 signals for data and acknowledgement.

There are two other signals of importance — the byte clock and a frame start signal. The byte clock runs at 20 MHz giving a datarate of 160 Mbps. Frame start is used to synchronise cell submission to the fabric. The port controllers also use frame start for this purpose. The frame start pulse is in fact the only indication the fabric has about cell size; it is generated by a PAL on the fabric board.

## 3.3 The Fairisle Port Controller

# Requirements

A Fairisle Port Controller is attached to an input switch port and corresponding output switch port, since it acts as both an input and output port controller. The port controller also interfaces to the transmission system<sup>6</sup>.

Port controllers are MSNL routers. They receive cells from the transmission system and perform a lookup on cell VCIs in order to determine:

- 1. whether the VCI is valid,

- 2. which outgoing VCI(s) the cell should be forwarded on,

- 3. which output port on the switch the cell should be sent to,

- 4. which priority the cell should have through the fabric,

- 5. which queue the cell should be placed on

- 6. what discard and retry policies should be used on blocking

The switch is input buffered, that is, it is the input port controller which must buffer cells and deal with blocking in the fabric. Therefore as well as performing the lookup operation described above, the port controller must implement the retry and discard policies.

The output side is straightforward. There is a mechanism for routing cells either to the port controller itself (for management) or to the outgoing transmission system. Speed matching is provided by a simple FIFO technique, when the FIFO is logically full the output port blocks back through the fabric by keeping the acknowledgement signal unasserted.

The port controller can also gather statistics about cell flow. These can be use for policing and monitoring.

<sup>&</sup>lt;sup>6</sup>Local links will use TAXI devices; longer links will be based on SONET and/or SDH trasnmission.

# Implementation

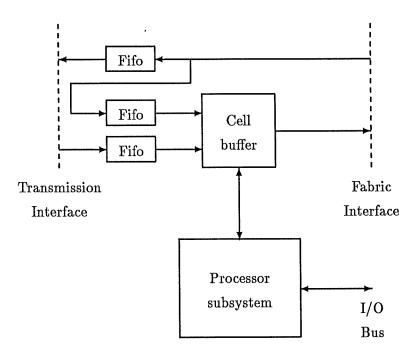

The port controller is based on a simple high speed RISC processor, the ARM3<sup>7</sup>. This provides the main control function of processing cell headers and running the queueing algorithms. It is not, however, involved in moving cell data. A schematic of the port controller is shown in figure 4.

Figure 4: The Fairisle Port Controller

# The main components are

- the ARM3 processor system which includes a memory controller, an I/O controller,

Mbyte of DRAM, 128 Kbyte of PROM and an IO bus.

- 2. the cell buffer which is 128K bytes of SRAM (35 ns) and three 32 bit buffers.

- 3. a Xilinx device which triple ports the cell buffer and provides the glue to the processor, the fabric and the transmission system.

- 4. the fabric and clock interface simply latches and terminations

<sup>&</sup>lt;sup>7</sup>Designed and used by Acorn Computers Ltd, this component is sourced by VLSI Technologies Inc., CA.

# 5. the transmission interface comprised of FIFOs and terminations

The use of a processor provides an extremely flexible port controller. This means that various queueing algorithms, service qualities, policing techniques, and congestion control algorithms can be explored.

The Xilinx device is a 4200 gate equivalent device. However a pin compatible 6400 gate equivalent device is available should we wish to put more functionality (for example all functionality) in hardware.

#### Port Controller Software

The run time system for the port controller is a micro kernel called Wanda. This is a locally developed micro kernel, providing interrupt handling, address space management, threads, and interprocess communication mechanisms. (Wanda also runs on multiprocessor Fireflies and on 680x0 processors.)

In the port controller cells are placed on and removed from queues by interrupt service routines. (The number of instructions per cell at a line rate of 100 Mbps is on the order of 50.) The choice of which queues should be serviced is implemented by management algorithms at the MSNL level which run on a longer timescale than the individual cell.

In fact the implementation of MSNL within Wanda provides this cell forwarding function between any network devices implementing MSDL. The software which controls the Xilinx chip and SRAM on the port controller simply fit into this generic mechanism.

A version of Wanda is held in PROM (including the Xilinx configuration). On reset the software in the PROM attempts to obtain the latest version of the software from a boot server. We currently provide one port controller with an Ethernet interface to enable it to boot over the Ethernet. This then acts as an MSNL router, and allows the remainder of the port controllers on the network to communicate with the boot server.

# 3.4 Management Platform

The original intention was to have a switch controller which would be a processor attached to all port controllers via a management bus. However, the use of a processor in the port controller enables us to use either one or all of the port controllers as management entities. As the network management function is necessarily distributed, we adopt the latter approach as it provides us with a testbed with the largest degree of distribution possible.

# 4 Using The Network

#### 4.1 Host Interface

Two configurations of a simple network interface for the VME bus are available, the choice of which to use is dependent on the function of the attached host. A simple programmed I/O interface provides cell level access to the network. A set of FIFOs interface directly between the VME bus and the transmission interface. As there is a considerable overhead in dealing with individual cells, such interfaces are only used when the machine is performing some dedicated task which leaves spare capacity on the processor.

Many hosts will wish to avoid handling cells and only deal in blocks, and in this case the VME board is combined with a port controller which provides the required segmentation and reassembly functions. The VME board attaches to the switch fabric interface of the port controller, so that, with simple modifications to the code in the port controller, incoming cells can be demultiplexed and reassembled into blocks before being passed on to the host.

# 4.2 Attachment to Other Networks

The port controller has an interface which conforms to Acorn Computer's expansion bus. Ethernet and CFR interfaces are readily available. Device drivers providing MSDL for these networks exist and hence each port controller can act as an MSNL router between Fairisle and these networks. In particular interworking with the CFR provides access to the Pandora multimedia workstations [Hopper 90] as sources of real time traffic.

An MSNL router is also available between Fairisle and the CBR. This uses a dedicated 68030 VME system to perform the MSNL cell forwarding between an attached backbone ring station and the simple cell interface to Fairisle.

## 4.3 Continuous Media Devices

As with the interconnection of Fairisle and other networks, two choices are available for the attachment of continuous media devices to the network. Both the port controller I/O bus and VME systems, equiped with the simple cell interface, allow us to connect inexpensive devices, such as frame acquisition systems, to generate real continuous streams.

## 4.4 Traffic Generation

We consider it important not only to attach existing and real multimedia devices to the network, but also to be able to generate streams with a wide range of traffic characteristics and requirements. For example, we could perform experiments on the implications of a new viedo coding mechanism on the network, even before equipment implementing the mechanism is available.

Again the programmability of the port controllers (including the Xilinx device) mean that it is a relatively simple matter to generate streams of cells for virtually any statistical arrival process (including multi layer arrival processes). Thus port controllers are used as traffic generators, either to inject cells directly into the fabric or down a transmission line to a real port controller.

# 5 Conclusion

The architecture of the Fairisle network and some of the network components have been described. At the time of writing (March 91) the port controller and switch element are

built and tested. We are currently awaiting PCBs for the switch fabric before commissioning the first switch. The VME bus interface is designed and now at the stage of PCB layout.

Projects within the laboratory will be making use of the Fairisle network for experiments and developments in multimedia applications. However, a key feature of the network components is their flexibility, and this also allows us perform a wide a range of network management and internetworking experiments.

# References

[Greaves 88] The Cambridge Backbone Network.

DJ Greaves and A Hopper.

Eurpoean Fibre Optic Conference (EFOC / LAN 88), Amsterdam. June 1988.

[Hopper 90] Pandora - An experimental system for multimedia applications.

A Hopper.

Operating Systems Review Vol.24 No.2. April 1990.

[McAuley 89] Protocol Design for High Speed Networks.

DR McAuley.

PhD Dissertation, University of Cambridge Computer Laboratory, Technical Report 186. September 1989.

[Newman 88] A Fast Packet Switch for the Integrated Services Backbone Network.

P Newman.

IEEE Journal on Selected Areas in Communications, Vol 6, No 9, December 1988.

[Tennenhouse 89] Layered Multiplexing Considered Harmful.

DL Tennenhouse.

IFIP Workshop on Protocols for High-Speed Networks, Zurich. May 1989.

# Fairisle Port Controller Design and Ideas

Mark Hayter and Richard Black March 1991

# 1 The Port Controller

The Fairisle Switch is based around a simple switch fabric with all the processing being done in the port controllers. The port controller consists of two parts. The first is a processing unit based around an ARM3 RISC processor. The second section consists of buffer memory and a DMA engine. Figure 1 shows an overview of the port controller, the lower half forming the processor section, and the upper the network section. There is a plug in transceiver card for connection of a fibre, alternatively for short links an 8 bit parallel connection can be made.

Figure 1: Port controller layout

The processing section of the port controller has an ARM3 processor and runs the Wanda micro-kernel. The current boards can have either 1 or 4 Mbytes of dynamic memory and 128, 256 or 512kbytes of ROM. The card includes an Acorn podule bus to allow the addition of other network interfaces. In addition to the standard ARM version of the Wanda kernel there will be a hand crafted interrupt routine to deal with the routing of cells. Cells are only buffered on the input to the fabric - the processor has no control of the fabric output.

The network section of the card contains 128kbytes of static memory, buffer fifos and the xilinx control chip. The static memory is used for cell buffering, and resides in the memory mapped I/O space of the processor. The xilinx arbitrates access to this memory between the processor, transmission to the fabric and reception from the network.

# 2 A Cell on the Port controller

The SRAM on the port controller is divided into cell buffers, which are written or read in a DMA fashion for incoming or outgoing data, and may be accessed as RAM by the processor. The cell buffer format is shown in table 1. The data from the network is bytes

| Byte  | Name    | Comment                                                     |  |

|-------|---------|-------------------------------------------------------------|--|

| 0     | FabR1   | Fabric 1st route byte                                       |  |

| 1     | FabP1   | Fabric 1st pad byte (always 0)                              |  |

| 2     | FabR2   | Fabric 2nd route byte                                       |  |

| 3     | FabP2   | Fabric 2nd pad byte (always 0)                              |  |

| 4     | PortPad | Portc pad byte (always 0)                                   |  |

| 5     | PortR   | Portc route byte (bit 0 - set, bit 1 set/clear for loop/tx) |  |

| 6-11  | Header  | VCI and SAR bytes                                           |  |

| 12-59 | Data    | User data bytes                                             |  |

| 60-63 | Spare   | Unused, only exist in port controller buffer                |  |

Table 1: Cell Buffer Format

6 to 59 of the cell buffer, the routing tag being added by the port controller. The full 60 bytes are sent into the fabric, which passes bytes 4 to 59 to the output port controller. The pad byte is removed and the route byte is replaced by a start of cell control signal for transmission on the network. The spare bytes are never used by the network section, so are free for internal use by the processor section. The route byte formats are given in tables 2 and 3. Note that since the routing bytes are discarded on the way through the fabric and port controller the spare bits cannot be used to send information. The fabric is being redesigned to remove the pad bytes, the port controller one is only present to word align data.

| Bit | Name     | Use                            |

|-----|----------|--------------------------------|

| 0   | Active   | Always set for a cell          |

| 1   | Priority | Set for high priority cell     |

| 2-3 | Route    | Output requested for this cell |

| 4-7 | Spare    | Unused                         |

Table 2: Fabric Route byte

| Bit | Name  | Use                                        |

|-----|-------|--------------------------------------------|

| 0   |       | Always set for a cell                      |

| 1   | Loop  | set for loopback, clear to transmit to net |

| 2-7 | Spare | Unused                                     |

Table 3: Port Controller Route byte

# 3 The xilinx DMA controller

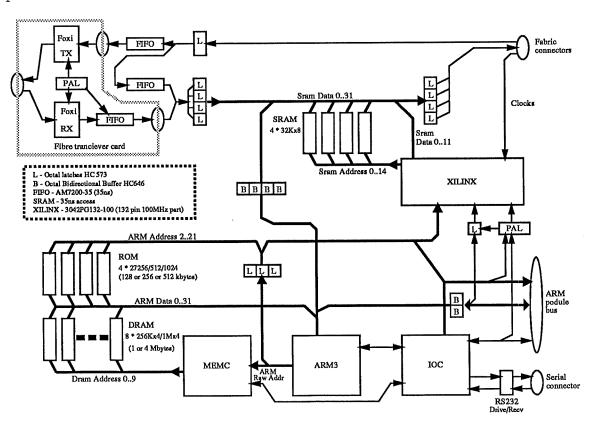

The xilinx chip, which controls the network part of the card, consists of five main sections: the processor interface, the SRAM interface, reception from the network, injection into the fabric and transmission to the network. It maintains two queues of buffer pointers into the SRAM. Buffers in the first queue are filled by incoming cells from the network, the processor then inserts a routing tag and adds the buffer to the second queue for injection into the fabric; it may be that the VCI of the cell is also changed at this stage. The processor is interrupted if either of the queues are not full of buffer pointers (indicating cell arrival or transmit availability), or a NACK is received from the fabric. Figure 2 shows the various parts of the DMA system and gives an outline of their interconnection. All the parts inside the grey border are on the xilinx device.

# 3.1 SRAM interface

The xilinx is the only device which drives the SRAM, arbitrating between its DMA use and the processor. The arbiter assigns top priority to the fabric transmission requests, next to network reception requests, and lowest to processor accesses. Access grants control a multiplexor which drives the SRAM address bus. Only part of the SRAM data bus is used directly by the xilinx, to load the buffer registers and output its internal status. Enables of SRAM data bus drivers are also controlled by the xilinx.

# 3.2 Injection to the fabric

The xilinx will start sending cells into the fabric if there are buffers in the transmit queue and the processor has strobed the RamRdGo line since reset or a fabric NACK. Transmission continues until the queue is empty, or a cell is NACKed by the fabric or destination port controller. If transmission stops because the queue becomes empty then it will restart as soon as a new item is put in the queue – strobing of the RamRdGo line

#### FAIRISLE PORT CONTROLER - XILINX ARM Rd/Wr req ARMINT ARBITRATE Reg load rec ARM Reg load req ARMDEC ARMMEM Signals Word Rd req RDQUEUE WRQUEUE Queue iten Cell start bit RDACTIVE WRACTIVE Cell dir bit FIFO2WORD FAB2FIFO WORD2FABRIC MUX 4 ZERO Status Reg M R A M SOC b ADDRESS Z E / FROM FOXI CARD ARM Data

Figure 2: Port controller DMA system

is only required after NACK or xilinx reset.1

To send a cell the "word2fabric" section of the xilinx first loads the register RdREG from the read queue location in the SRAM. Then words are read from the SRAM, using the register value to form the top part of the address and the read active counter to supply the offest into the buffer. The word is loaded into the latches and clocked into the fabric a byte at a time. The next word is loaded in the same cycle as the 4th byte is output. Since the arbiter gives these memory reads top priority, this ensures the stream of bytes to the fabric is continuous. The fabric uses the bottom bit to mark the start of the cell, so an external buffer is used to force this bit to a zero when no cell is being transmitted.

The Ack signal from the fabric is monitored just after the header has been sent. If a NACK is seen at this point then transmission of this cell is stopped at once. If the cell buffer pointer has its retry bit clear or the cell has been retried already the transmission system is disabled. The processor can be interrupted by transmission stopping and can determine which cell was rejected (from the status register) then implement the correct retry strategy.

<sup>&</sup>lt;sup>1</sup>It would be easy to change the hardware so that the line had to be strobed to restart after a queue empty state. Currently I can see no advantage to doing this.

# 3.3 Fabric output to network

Data from the fabric is moved under control of the xilinx "fab2fifo" section, into one of the two fifos. The cell arriving from the fabric has had the fabric routing information removed but still contains the port controller route byte. The route byte contains two bits that are used by the port controller. The cell Active bit is always a 1, and is used to indicate the start of the full cell in the same way as in the fabric. The loopback bit indicates whether the cell is destined for transmission or for looping back into the port controller.

Bytes arriving from the fabric are latched to provide a cycle delay for decoding the routing information. On recognition of a cell the loopback bit is used to indicate which fifo should be used for the duration of this cell. Bytes are then strobed into the fifo for the number of bytes in a cell. The fifo contains 256 nine bit words. The ninth bit is used as a start of cell marker and is set as the porter outer byte is strobed into the fifo. This byte will be removed by the FOXI transmission card and replaced by a control code. The data associated with this byte is ignored by the transmission system.

The Half Full signal from the selected fifo is used to generate the Ack signal to the fabric. Thus as soon as the fifo becomes half full back pressure is applied. Since the transmitting port controller only senses the Ack signal for one byte time just after the header has been transmitted it is possible for almost an entire cell to be put in the fifo past its half full point.

# 3.4 Reception from network or loopback fifo

The FOXI reception card contains a fifo into which an incoming cell has been strobed. The start of cell control sequence will have been replaced by a byte with the SOC bit set. Thus the format of the data is the same in both the loopback fifo and the receive fifo. The data in this byte is currently not defined <sup>2</sup>.

If either fifo is seen to contain data then it is selected for reading, if both contain data then they are read alternately. When a SOC bit is seen from one of the fifos it is selected. This also causes the WrREG to be loaded from the write queue location. Bytes are read from the selected fifo and assembled into words in the latches. When a word has been assembled it is written to the SRAM using the register buffer address and the offset suplied by the write active section. The write active starts with an offset of one word and the latch loading starts half way through the word. This leaves 6 bytes at the start of the buffer for the processor to insert the route tag. If a new SOC is seen part way through reading a cell then the first cell is discarded and the new one read into the same cell buffer, a status bit is set to indicate this happening.

# 3.5 The processor interface

The processor control signals are decoded and I/O accesses to the xilinx space (0x3180000 - 0x31FFFFF) are detected. The use of I/O space causes the access cycle to be asynchronous, allowing the xilinx to arbitrate the memory access. The SRAM is mapped into this area for 32 bit word accesses. The top address bits allow modifications to the access method. A basic access allows reading or writing of the memory. If the strobe bit is set then on a write operation one of the queue insertion lines will be strobed, bit 5 determining

<sup>&</sup>lt;sup>2</sup>In most cells this byte is strobed into the porte route byte location in the cell buffer, one idea is that an identification be assigned to each type of interface so the port controller could use this byte to determine the characteristics of the interface.

which. The final access method is a read with the status bit set, this causes a fake memory access with the data being supplied from the xilinx status register. Addresses 0x3180000 and 0x31C0000 are ARM immediate constants and so the most used access methods are placed at these addresses. A byte write usually results in all 4 bytes in the addressed word being set to the value given. Since an asynchronous memory access is used it will take at least 2 cycles of the ARM REF8M 8MHz clock to perform the access.

| Start     | End                                    | Use                                                 |

|-----------|----------------------------------------|-----------------------------------------------------|

| 0x3180000 | 0x319FFFF                              | Read / Write access to SRAM                         |

| 0x31A0000 | 0x31BFFFF                              | Read xilinx status word, write SRAM                 |

| 0x31C0000 | $0\mathrm{x}31\mathrm{C}001\mathrm{F}$ | Read SRAM / Write output queue with strobe          |

| 0x31C0020 | 0x31C003F                              | Read SRAM / Write input queue with strobe           |

| 0x31C0040 | 0x31DFFFF                              | Read SRAM / Write SRAM and strobe (bit 5 -> in/out) |

| 0x31E0000 | 0x31FFFFF                              | Read status, write with strobe                      |

Table 4: Memory map

The memory map is shown in table 4. The first 8 words of the SRAM are the output queue, the next 8 the input queue. Both are circular, with the processor inserting buffer pointers, and the xilinx consuming them. It is the responsibility of the processor to ensure a new buffer pointer is stored in the correct memory location to be added as the tail of the

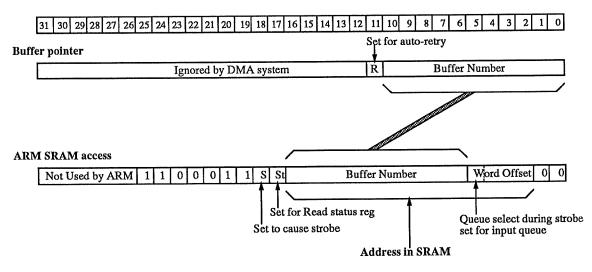

Figure 3: Buffer pointer and memory addresses

queue. There is no protection against the processor strobing pointers into a full queue - if it does it will overwrite an existing buffer pointer but the internal tail will not advance. The processor can cause a queue strobe signal by writing anywhere in the memory with the appropriate high order bits set.

The SRAM is divided into cell buffers. The zeroth buffer contains the queues, the rest are available for cell DMA. The mapping from buffer pointer to buffer address is simply a left shift six bits of the bottom eleven bits of the pointer. The higher order bits of the pointer are not used by the DMA system, so may be used by the control software. Note that it is the buffer pointer, and not the buffer address, that is stored in the queue. Figure

3 shows the buffer pointer value and an ARM memory address and their relationship to the SRAM address (which accesses a long word).

The buffer pointer includes a retry bit. If this is set then the DMA system will do one automatic retry should the cell be NACKed on the first attempt. If the retry fails then transmission stops and the processor is interrupted. If the retry bit is clear then the system stops on the first NACK.<sup>3</sup> The ARM memory address shows the bits that are decoded to cause a status register read, or a strobe with write.

# 4 Status and Control

The xilinx status can be found from its internal status register, and from signals passed to the processor section I/O controller (IOC). The lines on the IOC can be set to cause a high priority, low latency, interrupt (a FIQ) to the processor. Tables 5<sup>4</sup>, 10 and 7 describe the status signals.

| bit   | name                       | use                                                             |

|-------|----------------------------|-----------------------------------------------------------------|

| 0-2   | $\operatorname{RdTailAdr}$ | Buffer queue number for cell being or about to be sent. Only    |

|       |                            | useful if sending has stopped, when it contains the queue       |

|       |                            | number for the next cell to be sent.                            |

| 3     | Spare                      | Always zero                                                     |

| 4     | RamRdReady                 | Set if there are buffers to send. Clear if the queue is empty.  |

| 5     | RamRdFull                  | Set if output queue is full                                     |

| 6     | RamRdOKbar                 | Set if not sending                                              |

| 7     | RamRdRun                   | Set if output system is ok, cleared by reset or fabric NACK.    |

| 8     | SICseen                    | Set if Start of cell mark has been seen in a cell, Cleared when |

|       |                            | status register is read                                         |

| 9     | StrayBytes                 | Set if bytes seen from the fifo which were not part of a cell,  |

|       |                            | Cleared when status register is read                            |

| 10-11 | Spare                      | Not used - always zero                                          |

| 12-31 | -                          | Undefined. May read as any value.                               |

Table 5: xilinx status register

The xilinx status register is mainly intended so that the processor can determine why sending to the fabric stopped. If the system is not sending (and has been) the RamRdRun bit indicates if it stopped because the buffer queue was emptied or because of a fabric NACK. The RdTailAdr gives the RdQueue index into the output queue. This index is for the next cell to be transmitted, so if transmission was stopped by a NACK it is the previous queue entry which contains the buffer pointer for the rejected cell. Since the index value is incremented part way through transmission of a cell it only gives useful information if the system is not sending. Some of the data bits are cleared after the status

<sup>&</sup>lt;sup>3</sup>I have no idea if this is useful, but it is there to be tried. The number of retries could be increased easily.

<sup>&</sup>lt;sup>4</sup>The spare bits may be used to bring out other internal signals if required. The undefined bits are not available.

register is read, these all latch unexpected conditions (such as short cells) seen by the xilinx <sup>5</sup>.

The IOC control lines are used to control aspects of the xilinx chip, as detailed in table 6.

| Bit | Name                   | use                                      |

|-----|------------------------|------------------------------------------|

| 0-1 | I2C[0-1]               | Podule Bus control                       |

| 2   | RamRdGobar             | Strobe low to start xilinx sending cells |

| 3   | ${f FifoReset}$        | High to reset the Fifos, low to enable   |

| 4   | Led1                   | Low to turn on red LED                   |

| 5   | $\operatorname{Led} 2$ | Low to turn on yellow LED                |

Table 6: IOC Control lines

The control register lines have pull up resistors on them so on reset, when they are undriven, they will go high. Thus a card reset will cause the fifos to be reset, and the strobe line to be deasserted. The RamRdGobar line should be strobed low to start cells being sent after the xilinx is reset or a NACK has been received, it should be set high (ie undriven) again immediately. Extra strobes of the RamRdGobar line may cause NACKs to be missed (since they could be cleared before the processor has noticed them). The top two bits of the IOC control register must always be set when the register is written.

# 5 Programming the xilinx chip on the port controller

The xilinx gate array on the port controller is configured in peripheral mode (M0=M2=+5V M1=gnd) for easy programming under software control. There are three status lines which come from the xilinx chip to the IOC. These are INIT, HDC and RDY/BUSYbar which appear in IOC status register B<sup>6</sup> as noted in table 7.

| Bit | name      | use                              |

|-----|-----------|----------------------------------|

| 0   | PFIQbar   | Podule FIQ                       |

| 1   | XiInitbar | Xilinx Init line                 |

| 2   | XiHdc     | Xilinx high during configuration |

| 3   | XiRdy     | Xilinx ready                     |

| 4   | LIRQ      | Transputer link IRQ              |

| 5   | PIRQ      | Podule bus IRQ                   |

| 6   | STx       | KART Tx Data empty               |

| 7   | SRx       | KART Rx Data full                |

Table 7: IOC Interrupt status register B

In addition to the data there are three control lines which affect the xilinx chip. These control lines are manipulated by the processor through a simple PAL. These lines are the

<sup>&</sup>lt;sup>5</sup>There is a problem routing these signals on the chip so they may be removed.

<sup>&</sup>lt;sup>6</sup>These interrupts are not enabled so do not appear in the request register

WriteStobe (WRTbar) active low line, a low to high transition on which causes the current value on the data lines to be read in by the chip. The other lines are the reprogram line which can be used to cause an already programmed chip to be wiped, and the reset line which is connected to global reset on the chip. In addition the PAL controls the enable line of a buffer between the IOC data bus lines and the xilinx data lines.

On power on reset or board reset the PAL asserts and holds the reset signal and deasserts all other signals. This ensures there are no board conflicts and prevents the xilinx chip from operating until the software chooses to bring it out of the reset state.

The PAL operations are controlled by the address bus only, appearing in the IOC space at device 1, see table 9, and are activated by a write to the given address. The pal equations may be found in /usr/groups/fairisle/designs/portc/revisions/PALREV.MAP.

| Name       | Assert    | Deassert  |

|------------|-----------|-----------|

| WriteData  | 0x3210000 | 0x3210004 |

| DataEnable | 0x3210008 | 0x321000C |

| Reprogram  | 0x3210010 | 0x3210014 |

| Reset      | 0x3210018 | 0x321001C |

Table 8: PAL access addresses

The first thing that the software does is to being the chip out of reset and wait for the INIT signal to go inactive. This indicates that the xilinx chip has completed its internal clearing operation. (If the chip has currently got a configuration in it then this signal will not have gone active and the chip will be running with the old configuration).

Then the HDC (High During Configuration) signal is tested. This signal is not valid during reset or initialisation phases but otherwise indicates if the chip is ready to receive a configuration. This signal will be high at this point iff there is no configuration in the chip. If this signal is low then the chip must have its current data removed, this is performed by asserting the reprogram line for a short period and waiting for the INIT line to go inactive. The xilinx allows for the HDC pin to become a user I/O pin after configuration but this is not permitted on the port controller. This line has a pull down resistor so can be left unused in the xilinx design.

In either case the chip is now ready to be programmed. This is performed by loading the configuration data bytewise, with the BUSY line being checked to ensure handshaking. Bytes are written using four operations.

- 1. The Data connect line is asserted. This links the xilinx data lines with the IOC data lines. The IOC data lines are isolated from the processor data lines except when the processor issues an address in the I/O space. Thus opcode fetches do not reach the xilinx data pins.

- 2. The Write line is asserted; the value written being the data byte required to be sent to the chip. At the end of this cycle the data is floating on the linked I/O xilinx bus.

- 3. The write line is deasserted causing the xilinx to latch the data. Again the byte written to the address is the data byte for the chip. This ensures that the IOC buffers enforce rather than destroy the required data floating on the capacitance of the I/O bus from the previous cycle.

4. The data connect line is deasserted, decoupling the busses and permitting the processor to read the IOC register and wait for the handshaking signal.

It should be noted that these operations are extremely sensitive not only to delay but also to potential accesses to the I/O space. For this reason these operations should be performed with interrupts disabled. Once all the data has been written the HDC line should be checked for inactivity to ensure that the chip has accepted the data and assumed the configuration. After configuration strobing the reset line will reset the xilinx device, clearing all the internal flipflops. If this is done the fifos should also be reset using the IOC control line (see table 6).

# 6 The network interface

The port controller has a parallel network interface. On to this may be connected a transceiver for a fibre, or it may be used to directly connect devices. The interface is byte wide, and is asynchronous. Two connectors are used, one for transmission and one for reception, as detailed in table 9.

| Pin       | Signal    | Transmit  | Receive   | Use                          |

|-----------|-----------|-----------|-----------|------------------------------|

|           | Name      | Direction | Direction |                              |

| Even 2-24 | Gnd       |           |           | Ground                       |

| Odd 1-15  | Data[0-7] | Out       | In        | Bytewide data lines          |

| 17        | SOC       | Out       | In        | Set for start of cell byte   |

| 19        | Readbar   | In        | Out       | Strobe low to read next byte |

| 21        | Emptybar  | Out       | In        | Clear if there is no data    |

| 23        | N/C       |           |           | Not used                     |

| 25,26     | (VCC)     | LK5       | LK4       | Power if link is made        |

Table 9: Port Controller network interface

Data is extracted a byte at a time on the transmit side by strobing the Readbar line low. The start of a cell is marked by having the SOC bit set, the data which accompanies this is undefined. Following the SOC are the 54 bytes of the cell, being bytes 6-59 of the cell buffer described in table 1. If there is no data available then the Emptybar line will go low, and reads are undefined. The transmission system should read this stream of bytes and convert them into the from required by the link. The reception system should convert the form on the link back into the SOC and bytes form 7, which it should supply bytewise when the read request is strobed on the receive side. The port controller expects to receive in the same form as it sent, so the simplest link may be provided by cross connecting the transmit and receive connections of two port controllers using ribbon cable. Alternatively a card is being made which will use the FOXI chips to allow a fibre link to be made. Another possibility is for a parallel connection to be made to the interface card of a host machine. The timing details for the reads and empty signal are as for a Am7200-35 CMOS fifo, with a 45nS read cycle, 35ns read access and empty going low 30ns after the read cycle of the last byte is initiated.

<sup>&</sup>lt;sup>7</sup>Possibly the data of the SOC byte will contain an interface type identifier.

# 7 The interrupt handler

As mentioned in section 1 the ARM processing part of the port controller includes a hand crafted interrupt routine known as a FIQ. This is a low latency interrupt which may respond with a minimum delay of 170ns.<sup>8</sup> In order to further improve the latency of fiq interrupt response the ARM provides six banked registers which are only accessible in fiq mode and which may be used both to preserve state from one fiq to the next and to avoid having to save registers before use.

| bit | Name                   | Use                          |

|-----|------------------------|------------------------------|

| 0   | FH[0]                  | Set on input queue not full  |

| 1   | FH[1]                  | Set on output queue not full |

| 2   | $\operatorname{FLbar}$ | Set if output has stopped    |

| 3   | C[3]                   | State of fifo reset signal   |

| 4   | C[4]                   | State of LED1 (red)          |

| 5   | C[5]                   | State of LED2 (yellow)       |

| 6   | IL0                    | Podule FIQ line              |

| 7   | _                      | Always set                   |

Table 10: IOC FIQ Status register

The fiq interrupt can be generated by three separate lines from the xilinx device as described in table 10. The status of these lines is always software readable and they may be individually masked.

The fiq is responsible for the flow of data through the port controller using the xilinx device as a fancy DMA engine. The fiq's tasks can be divided as follows.

- It must transfer "forward" received cells to the transmit queue for injection to the switch fabric, inserting the routing tag and performing VCI remapping.

- It must keep the xilinx receive queue full to avoid packet loss.

- It must bring management and connection setup cells to the attention of the higher level Wanda system.

- It must merge management and connection setup cells being sent by the Wanda code with cells being forwarded.

- It must maintain statistics on forwarded cells to permit the Wanda code to perform policing and quality of service operations.

- It must restart injection under circumstances of Fabric NACK.

For testing the only fiq interrupt which is enabled is the receive queue not full interrupt. On receipt of this interrupt the fiq reads from the xilinx receive queue entry of the cell that arrived, converting the buffer number to the address. One byte of the VCI of the arrived cell is retrieved for inspection. If the value is greater than 15 then the cell is posted

<sup>&</sup>lt;sup>8</sup>Due to the asynchronous nature of some ARM I/O accesses there is no obvious bound on the maximum value.

to Wanda by writing the buffer pointer into a global variable and generating an "always IRQ" (note a potential overrun could occur here if another such cell arrives before the Wanda system has processed the first.) If the byte was less than 16 then the Fabric, Port Controller, VCI and SAR fields are replaced by entries in an indexed table. The buffer number is then written into the transmit queue at the tail position as indicated by the xilinx status register. No check is made for this queue being full and no interlock with Wanda transmissions is provided. Finally in both cases the receive queue is filled up with the next numerical buffer number (this is held in a state register.) Again no check is made that this buffer is actually free.

This implementation is obviously very naive but gives an idea of the requirements and is good for testing the hardware.

# 7.1 Timing

The port controller's design speeds are 100Mbits/s on the network interface and 20Mbytes/s on the fabric interface. The ARM processor has internal (FCLK) cycles clocked at 30MHz. Cells arriving from the network contain 55 bytes, cells to the fabric 60 bytes with one frame pulse every 64 clock periods. Thus at saturation there could be one receive interrupt every 132 FCLK, and one transmit every 96 FCLK. This is not counting NACKs (which may occur on 60% of cells at saturation), but assuming that more is being injected than is being received (which is unlikely). In the current experimental phase without real sources of traffic or multiple port controllers it is difficult to determine the frequency and conditions under which a NACK interrupt is likely to occur.

The ARM can perform one cycle in an FCLK period provided the data is in the cache. Non-cache accesses are slower, an access to the sram taking at least two REF8M cycles, more than 8 FCLKs <sup>9</sup>. Time is therefore of the essence and it seems likely that a statistical, if not absolute, target should be 60 FCLKs for an interrupt.

It is expected that under normal operation the fabric will be able to sink all the traffic arriving from the network, and therefore that most of the time one does not want the transmit queue not full interrupt enabled since there will be no appropriate action to take. Thus the perceived situation is that the tx interrupt is not enabled but the rx interrupt is. In this mode, when an interrupt is taken and a cell needs to be forwarded, there will be space in the transmit queue so the cell can immediately be inserted in it. Although this is likely to be the most common state its operation is logically a subset of the general case where queueing is required. So it is the general cases that will be described. The normal "idling" case will be returned to at the end.

# 7.2 Queues

Queues of cells are required both for cells that are being forwarded into the fabric and those which are being delivered to or transmitted by Wanda. Ideally the fiq code should not have to take different action depending on what type of consumer a particular queue has. For time reasons it is very important that when Wanda is accessing these queues it is not necessary to lock out or disable fiq interrupts. The structure of a queue must therefore allow for Wanda to have a queue which it is accessing asynchronously updated.

A queue consists of a head pointer and a tail pointer. A map is kept with one integer per cell buffer and the chaining of the cells is done implicitly in this map. Cell buffer zero

<sup>&</sup>lt;sup>9</sup>It may prove possible to run the REF8M clock at 10 or even 12MHz rather than the usual 8Mhz

can never be used because it holds the xilinx queues so it is possible to use zero as its traditional meaning of "null". It is also intended to reserve two additional cell buffers. One to read cells into under overload conditions where multiple cells may overwrite one another. This is preferable to not giving a buffer pointer to the xilinx as otherwise the fifos would fill up and there would be short cell problems, and also problems for the multicast ring (if present). The other would contain zeros (no start of cell bit) and could be used under panic conditions to avoid a xilinx transmit interrupt without consuming fabric or destination resources.

In order to allow the asynchronous updating of the queues the head pointer must only be updated by the consumer and the tail pointer by the producer. This in turn requires there to always be a valid pointer in these fields ie. that there is always one buffer associated with a given queue.

The entry in the map for a particular buffer contains a pointer to the next cell in this queue. A zero indicates the end of the queue. <sup>10</sup> Since there must always be a buffer in a queue even if it is empty a buffer whose next pointer is zero does not contain valid data but is the one into which the next set of valid data should be placed. Unfortunately this slightly complicates checking if the queue is empty.

Since the fiq is not-interruptible it may update the structures in whatever way it sees fit. However when Wanda, which is interruptible, accesses the queues it must obey the following procedures.

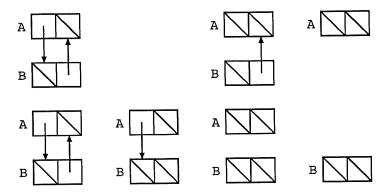

Figure 4: Inserting a cell buffer into a queue.

#### 7.2.1 Insertion

The tail pointer of the queue is read. That buffer is then filled with the appropriate data. A new end of queue cell buffer must be allocated and its next pointer set to zero. The previous tail cell's tail pointer is set to the newly allocated buffer. This is a single

<sup>&</sup>lt;sup>10</sup>Buffer 0 is not valid anyway since it holds the xilinx queues.

atomic write operation which validates the new data and makes it possible to be consumed. Finally the queue tail pointer is set to the new tail value.

#### 7.2.2 Removal

The head pointer of the queue is read yielding a buffer number. If that buffer's tail pointer is zero then the queue is empty. Otherwise the data may be consumed. The next field of that cell is written to the queue head pointer and the buffer may later be freed.

Figure 5: Removing a cell buffer from a queue.

# 7.2.3 Free List

The problem with the free list which is worse than the queues is that both the fiq and Wanda will want to update at both ends. There are three possible implementations.

- 1. Have a conventional queue as above but make Wanda prepare all the things in advance and then briefly disable the fiq interrupt and do the operation. The biggest disadvantage with this is that it requires the fiq to be disabled.

- 2. Have a doubly linked list with success checking by Wanda. This involves a conventional doubly linked list with the fiq working at one end and Wanda working at the other, with the rule as for the queues that there is always at least one buffer in the list. Again the fiq may perform whatever operations it requires and Wanda must obey special conditions when consuming a cell. The problem occurs when there are only two cells left and as Wanda allocates one, the fiq allocates the other. Referring to figure 6 the first line shows the positions of the data structures as Wanda removes a cell ("B") with the fiq idle. However if the fiq removes cell "A" between Wanda following the previous pointer from "B" and clearing the pointer from "A" to "B" then it would be the case that both cells would be allocated and both end pointers would be incorrect. To avoid this Wanda must check the "B" to "A" pointer

Figure 6: Arangement of the free list.

after clearing the "A" to "B" pointer to check that it still points to "A". If it does then everything is OK, if it is null then there are no free cells and if it has changed then the fiq must have both removed and added a cell and the procedure should be repeated. This algorithm now works except if the fiq allocates "A", deallocates another (say "C"), and then deallocates "A" again in the critical period. This is unlikely to happen.

3. Have an circular array of size 2048 with a single region of entries which contain the available cell buffers. A value of zero indicates no free buffer known for this slot in the array. Again the fiq and Wanda work from different ends. In this case Wanda uses is the ARM's indivisible swap operation to allocate a cell. If the value pointed to by Wanda's pointer is zero then the queue is empty. Otherwise Wanda swaps in a zero and gets the current value. If that value is zero then the list has just become empty. Otherwise the value obtained is the number of a free buffer and the pointer may be increased. This is the preferred method due to the much smaller overhead required from the fiq to allocate a cell buffer.

#### 7.2.4 Size

If required the size of the queue would be kept as the difference between counters of the number of cells inserted and the number of cells removed. This keeps atomic update but means that the size of the queue may not necessarily be accurately known.

# 7.3 Arriving Cells

Arriving cells have their VCI used as an index to a table. This table shall contain at least three control flags as follows.

- 1. An indication whether the cell should be discarded immediately or not. This is likely to be used for cells on the "myaddress" type VCI after startup or to discard cells on chosen VCIs when running short of buffer space.

- 2. An IRQ request. If this is set then an arrival of a cell on this VCI will be triggered to Wanda by posting a conventional interrupt.

- 3. Mapping required. Indicates whether the VCI, multicast, portc and fabric routing information of the cell should be replaced with data in other fields in the VCI table.

This is likely to be that case except for cells on connection setup VCIs and other such VCIs which are consumed by Wanda.

Obviously not all combination of these flags are necessarily meaningful.

Current experience with the CFR gateway indicates, albeit with mainly booting traffic, that about 1% of traffic only requires connection setup type higher level processing. Thus the typical case will be mapping and no IRQ.

It is also possible that the VCI table will include a counter of the number of cells received on this VCI which would be increased when one arrived.

If the cell is not to be discarded then the table should include a handle for the queue into which the cell should be inserted.

After this has been performed the xilinx receive queue must be refilled. In the case of a discarded cell the same buffer number may be re-used. Otherwise a buffer must be allocated from the free list.

# 7.4 Departing cells

When a transmit space available interrupt occurs the cell buffer must be added to the free list. Then a new cell to be transmitted must be found. This is likely to be done with some sort of pool of queue references which Wanda has decided require scheduling for transmission. It is not yet clear how this will be performed. When a queue is chosen a cell will be removed from it as described above and inserted in the xilinx queue.

A possible method for finding a queue is to have a chain of eight queue pointers where each queue is associated with a xilinx queue entry ie. If the next xilinx insertion point is n then a cell is inserted from queue n. It is then the responsibility of the Wanda scheduling software to update these pointers as appropriate.

Cells from Wanda requiring to be merged into the injection stream would be placed in some appropriate queue which Wanda would then schedule for transmission when appropriate.

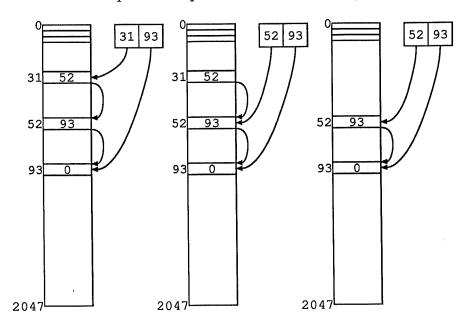

#### 7.5 Blocked cells

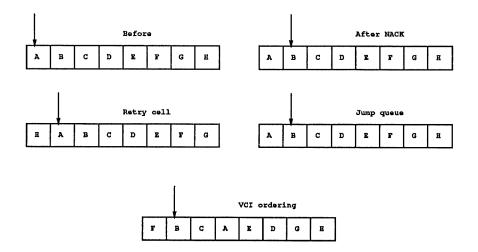

The Fabric generates a NACK whenever there has been contention, either for an output port or due to blocking within the fabric, and this port controller's cell has lost. A NACK is also generated by the destination port controller if its fifo is becoming full. On seeing a NACK the xilinx (possibly after one automatic retry) generates a fiq interrupt and stops transmission. At this point there remains about three quarters of a frame cycle left in which to prepare for restarting the xilinx chip. Failing this deadline will result in a frame being missed. This interrupt is thus even more time critical than usual. The tail of the transmit queue is incremented as usual at the same time as the NACK occurs positioning to the next cell. The position of the queue before and immediately after the NACK can be seen in figure 7.

Care must be taken if both a transmit interrupt and a NACK interrupt are pending since there may have been other successfully sent cells whose interrupts were not handled before the cell that was nacked.

There are a number of things that could be done to reschedule a nacked cell.

1. Retry the same cell. This is the simplest system to envisage requiring each buffer number in the queue to be shifted along. Unfortunately this mechanism has poor sta-

Figure 7: Fabric injection queues affected by NACK

tistical properties because one heavily accessed output port would delay all circuits. This is known as head of the line blocking.

- 2. Allow other cells in the xilinx queue to jump ahead of the NACKed one. This requires no moving of the queue <sup>11</sup> but suffers from a serious problem. If any of the cells which jump past have the same VCI then cell reordering will have taken place. This must be avoided by ensuring that there is never more than one cell on any VCI in the xilinx queue. Unfortunately this leads to cells waiting for transmission with empty slots in the queue and is also difficult to manage.

- 3. VCI reordering is essentially the same as the previous case except that on a NACK the queue is shuffled / sorted, eliminating the need for restricting which cells may be placed in the queue, though at substantial cost on a NACK. <sup>12</sup> In fig 7 for example if cells A,D and F were of the same VC, then the queue would have to be reordered as shown.

- 4. Another possibility is a variation of VCI reordering where the sort is done on the fabric routing information rather than the VCI. This is likely to be a little cheaper, but may or may not be statistically preferable to VCI reordering.

If the ideas of bundling (or grouping) of VCIs are used then it is VCIs in the same bundle which must not be reordered, so the size of the problem is increased. In this case the shuffle may need to be done on some other parameter, which is computed at connection setup time.

The xilinx control chip can do one automatic retry. This will suffer the same head of line blocking as (1) above, but used in conjunction with one of the other methods it may prove useful. It would also be possible for the hardware to generate an interrupt to indicate that it was about to do an automatic retry. The software could use this to start working out what to do if the retry fails. If software recovery takes longer than the critical time this might prove the best method, since the only loss is processor cycles should the retry succeed.

<sup>&</sup>lt;sup>11</sup>If the queue is not full then the NACKed cell must be put at the end

<sup>&</sup>lt;sup>12</sup>However the xilinx chip could be re-started as soon as the first cell of this re-ordering was completed.

#### 7.6 The Idle state

As mentioned earlier it is expected that most of the time the port controller will not be queuing but idling. In this state the transmit queue available interrupt must be disabled, but the receive and nack interrupts must remain enabled. It may prove worthwhile to vector special code for this state instead of the general case. When a cell arrives, if it is to be forwarded then a check is made on the status of the transmit interrupt and if it is pending then the cell can be written into the xilinx transmit queue immediately without passing through any queue structures. If there is no such available slot then the fiq will queue the cell and switch to normal mode. If Wanda wishes to transmit in this mode then it will enable the normal mode, the fiq will transmit its cells and then automatically return to idling mode.

# Fairisle VME Interface — DRAFT —

Reto Beeler

March 1991

## 1 Introduction

The Fairlisle VME Interface is a half-duplex single channel VME slave inter- face for the Fairisle ATM transmission system. It supports D32 transfers (both A24 and A32), and it must operate under control of an external CPU or DMA bus master station.

## 2 General Overview

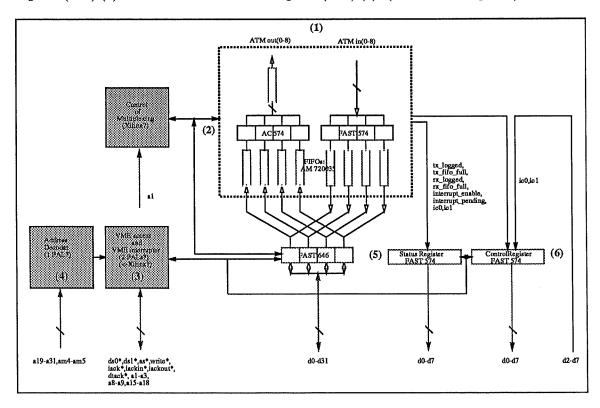

The Fairisle VME Interface is subdivided in a bytewide Fairisle ATM Interface (1), a MUX/DeMUX unit (2), VME access and VME interrupter logic (3), an address decoder (4), an Interface Status Register (ISR) (5) and an Interface Control Register (ICR) (6). (references to figure 1)

Figure 1: General Overview

# 3 Addressing

#### 3.1 Links

The current implementation of the address decoder allows for two alternative base addresses of the VME Interface Board: FDE0.0000 or FDF0.000. The base address is chosen by a link. A second link allows to select A24 transfers. Other links allow to set the VME interrupt level. (see Chapter 6)

| Link | Link Function            | Open      | Closed    |

|------|--------------------------|-----------|-----------|

| 1    | Base Address             | FDE0.0000 | FDF0.0000 |

| 2    | Address Width            | VME A32   | VME A24   |

| 3-5  | Interrupt Level (binary) | One       | Zero      |

| 6-12 | Interrupt Level (unary)  | Off       | Selected  |

Table 1: Link Setting Options

#### 3.2 Device Addresses