# Digital Electronics: Sequential Logic

## Introduction, Latches and Flip-Flops

#### Introduction

- The logic circuits discussed previously are known as *combinational*, in that the output depends only on the condition of the latest inputs

- However, we will now introduce a type of logic where the output depends not only on the latest inputs, but also on the condition of earlier inputs. These circuits are known as *sequential*, and implicitly they contain *memory* elements

- A memory stores data usually one bit per element

- A snapshot of the memory is called the *state*

- A one bit memory is often called a *bistable*, i.e., it has 2 stable internal states

- *Flip-flops* and *latches* are particular implementations of bistables

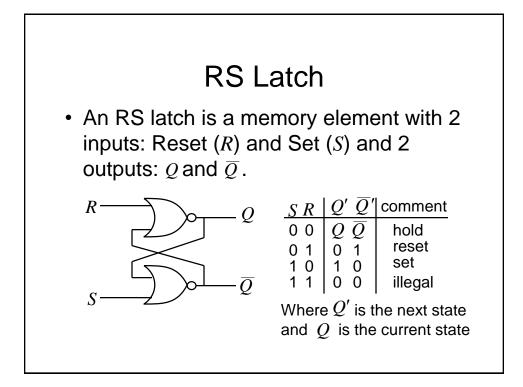

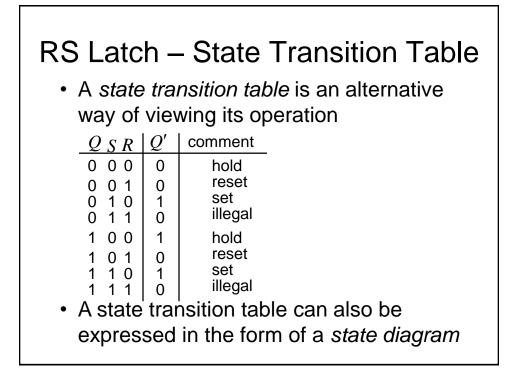

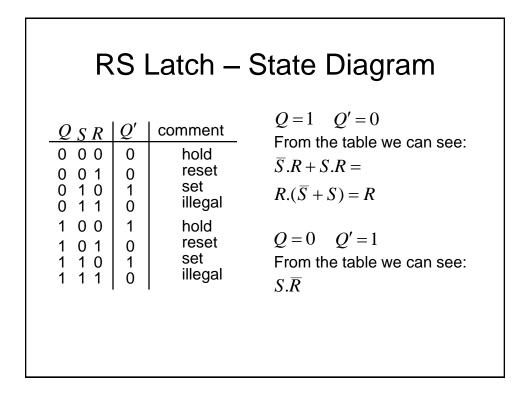

| RS Latch – State Diagram                                                                                                                                                                         |                                                                               |                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\begin{array}{c c c} Q & S & R & Q' \\ \hline 0 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 1 & 0 & 1 \\ 0 & 1 & 1 & 0 \\ 1 & 0 & 0 & 1 \\ 1 & 0 & 1 & 0 \\ 1 & 1 & 0 & 1 \\ 1 & 1 & 1 & 0 \end{array}$ | comment<br>hold<br>reset<br>set<br>illegal<br>hold<br>reset<br>set<br>illegal | Q = 0  Q' = 0<br>From the table we can see:<br>$\overline{S}.\overline{R} + \overline{S}.R + S.R =$<br>$\overline{S}.(\overline{R} + R) + S.R = \overline{S} + S.R =$<br>$(\overline{S} + S).(\overline{S} + R) = \overline{S} + R$<br>Q = 1  Q' = 1<br>From the table we can see:<br>$\overline{S}.\overline{R} + S.\overline{R} = \overline{R}.(\overline{S} + S) =$<br>$\overline{R}$ |

## **Clocks and Synchronous Circuits**

- The Clock: What is it and what is it for?

- Typically it is a square wave signal at a particular frequency

- It imposes order on the state changes

- Allows lots of states to appear to update simultaneously

- How can we modify an asynchronous circuit to act synchronously, i.e., in synchronism with a clock signal?

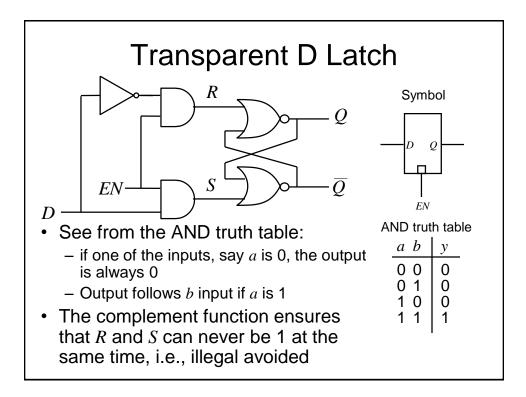

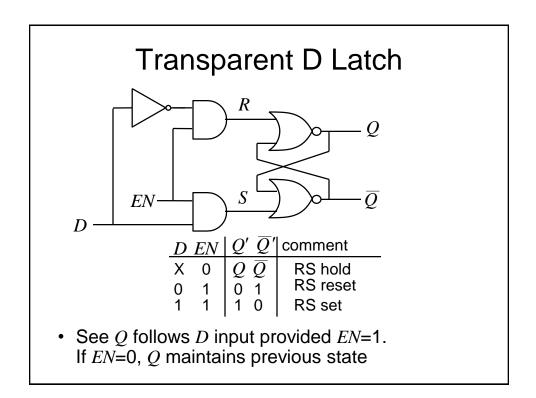

- We now modify the RS Latch such that its output state is only permitted to change when a valid enable signal (which could be the system clock) is present

- This is achieved by introducing a couple of AND gates in cascade with the R and S inputs that are controlled by an additional input known as the *enable* (EN) input.

#### Master-Slave Flip-Flops

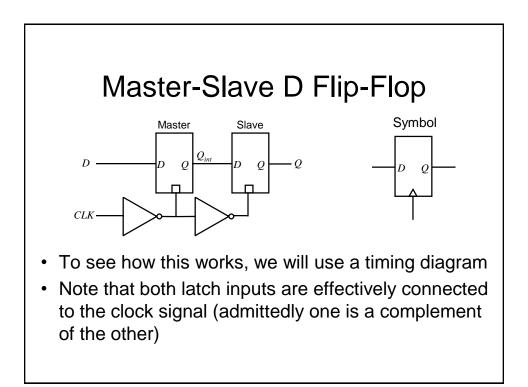

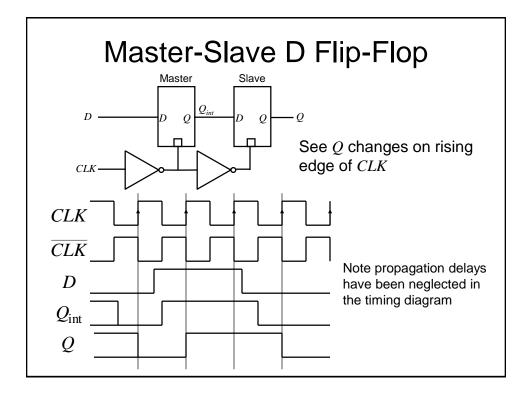

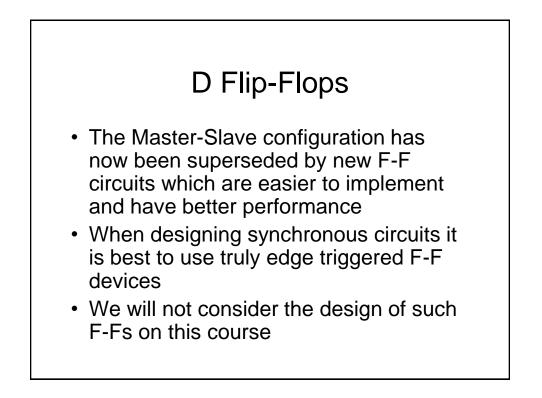

- The transparent D latch is so called '*level*' triggered. We can see it exhibits transparent behaviour if *EN*=1. It is often more simple to design sequential circuits if the outputs change only on the either rising (positive going) or falling (negative going) '*edges*' of the clock (i.e., enable) signal

- We can achieve this kind of operation by combining 2 transparent D latches in a so called *Master-Slave* configuration

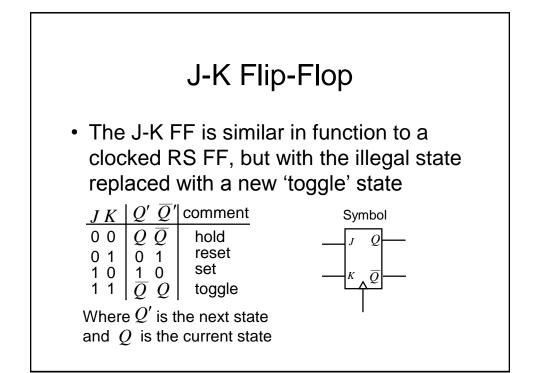

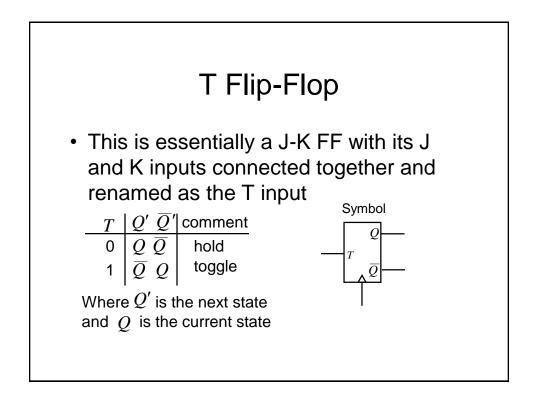

#### Other Types of Flip-Flops

- Historically, other types of Flip-Flops have been important, e.g., J-K Flip-Flops and T-Flip-Flops

- However, J-K FFs are a lot more complex to build than D-types and so have fallen out of favour in modern designs, e.g., for field programmable gate arrays (FPGAs) and VLSI chips

## Asynchronous Inputs

- It is common for the FF types we have mentioned to also have additional so called 'asynchronous' inputs

- They are called asynchronous since they take effect independently of any clock or enable inputs

- Reset/Clear force Q to 0

- Preset/Set force Q to 1

- Often used to force a synchronous circuit into a known state, say at start-up.