# Digital Electronics: Sequential Logic

### **Further Considerations**

### Elimination of Redundant States

- Sometimes, when designing state machines it is possible that unnecessary states may be introduced

- In general, reducing the number of states may reduce the number of FFs required and may also reduce the complexity of the next state logic owing to the presence of more unused states (don't cares)

## Elimination of Redundant States - Example

- Consider the following State Table that corresponds with a Mealy Machine implementation

- This is so, since the inputs and outputs from the machine are on the transitions (arcs) between states

- The following state table is drawn in a compact form by incorporating the 2 possible input values as parallel columns within both the next state and output columns of the table

| Example          |                  |             |             |                |   |                                                     |  |  |  |

|------------------|------------------|-------------|-------------|----------------|---|-----------------------------------------------------|--|--|--|

| Current<br>State | Ne<br>Sta<br>X=0 | ate         |             | out (Z)<br>X=1 | • | From the table, we see<br>that there is no way of   |  |  |  |

| Α                | В                | С           | 0           | 0              |   | telling states H and I apart,                       |  |  |  |

| BC               | D٣               | EG          | 00          | 0<br>0         |   | so we can replace I with H                          |  |  |  |

| DE               | H<br>J           | l<br>K      | 0<br>0      | 0<br>0         |   | when it appears in the<br>Next State portion of the |  |  |  |

| F<br>G           | L<br>N           | M<br>P      | 0<br>0      | 0<br>0         |   | table                                               |  |  |  |

| H                | A                | A           | 0           | 0              |   |                                                     |  |  |  |

| J                | A<br>A           | A<br>A      | 0           | 0<br>1         |   |                                                     |  |  |  |

| K                | Â                | Â           | 0           | Ö              |   |                                                     |  |  |  |

| L                | A<br>A           | A           | 0           | 1              |   |                                                     |  |  |  |

| N<br>N<br>P      | A<br>A<br>A      | A<br>A<br>A | 0<br>0<br>0 | 0<br>0<br>0    |   |                                                     |  |  |  |

|                  | Example               |                       |                       |                  |   |                                                                                  |  |  |  |  |

|------------------|-----------------------|-----------------------|-----------------------|------------------|---|----------------------------------------------------------------------------------|--|--|--|--|

| Current<br>State | Ne:<br>Sta<br>X=0     | te                    |                       | out (Z)<br>X=1   | • | We also see that there is now no way to get to state                             |  |  |  |  |

| A<br>B<br>C      | B<br>D<br>F           | C<br>E<br>G           | 0<br>0<br>0           | 0<br>0<br>0      |   | I so we can remove row I from the table                                          |  |  |  |  |

| D<br>E<br>F<br>G | H<br>J<br>L<br>N      | H<br>K<br>M<br>P      | 0<br>0<br>0<br>0      | 0<br>0<br>0<br>0 | • | Similarly, rows K, M, N and<br>P have the same next<br>state and output as H and |  |  |  |  |

| H                | A<br>A                | A<br>A                | 0                     | 0                |   | can be replaced by H                                                             |  |  |  |  |

| K L<br>M<br>P    | A<br>A<br>A<br>A<br>A | A<br>A<br>A<br>A<br>A | 0<br>0<br>0<br>0<br>0 | 0<br>1<br>0<br>0 |   |                                                                                  |  |  |  |  |

| Current<br>State<br>A<br>B<br>C<br>D<br>E<br>F |             | ate         | Outp<br>X=0<br>0<br>0<br>0<br>0 | out (Z)     | • | <b>The Similarly</b> , there is now no<br>way to get to states K, M,<br>N and P and so we can<br>remove these rows from<br>the table<br>Also, the next state and |

|------------------------------------------------|-------------|-------------|---------------------------------|-------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| H<br>J<br>L                                    | A<br>A<br>A | A<br>A<br>A | 0<br>0<br>0                     | 0<br>1<br>1 |   | outputs are identical for<br>rows J and L, thus L can<br>be replaced by J and row L<br>eliminated from the table                                                 |

|                                                |             |             |                                 |             |   |                                                                                                                                                                  |

|                                                                 | Next  | Ex                                                                                   | ample                                                                                                                                                                                                          |

|-----------------------------------------------------------------|-------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Current<br><u>State</u><br>A<br>B<br>C<br>D<br>E<br>F<br>G<br>H | State | Output (Z)<br>X=0 X=1<br>0 0<br>0 0<br>0 0<br>0 0<br>0 0<br>0 0<br>0 0<br>0 0<br>0 1 | <ul> <li>Now rows D and G are identical, as are rows E and F.</li> <li>Consequently, G can be replaced by D, and row G eliminated. Also, F can be replaced by E and row F eliminated from the table</li> </ul> |

|                  | Example         |   |         |   |                                                                                  |  |  |  |  |  |

|------------------|-----------------|---|---------|---|----------------------------------------------------------------------------------|--|--|--|--|--|

| Current<br>State | State<br>X=0 X= |   | out (Z) | • | The procedure employed                                                           |  |  |  |  |  |

| A                | B C             | _ | 0       |   | to find equivalent states in this example is known as                            |  |  |  |  |  |

| B<br>C           |                 | 0 | 0<br>0  |   | row matching.                                                                    |  |  |  |  |  |

| DE               | H H<br>J H      | - | 0<br>0  | • | However, we note row<br>matching is not sufficient to<br>find all the equivalent |  |  |  |  |  |

| H                | A A             | 0 | 0       |   | states except for certain                                                        |  |  |  |  |  |

| J                | A A             | 0 | 1       |   | special cases                                                                    |  |  |  |  |  |

|                  |                 |   |         |   |                                                                                  |  |  |  |  |  |

#### Implementation of FSMs

- We saw previously that programmable logic can be used to implement combinational logic circuits, i.e., using PLA devices

- PAL style devices have been modified to include D-type FFs to permit FSMs to be implemented using programmable logic

- One particular style is known as Generic Logic Array (GLA)

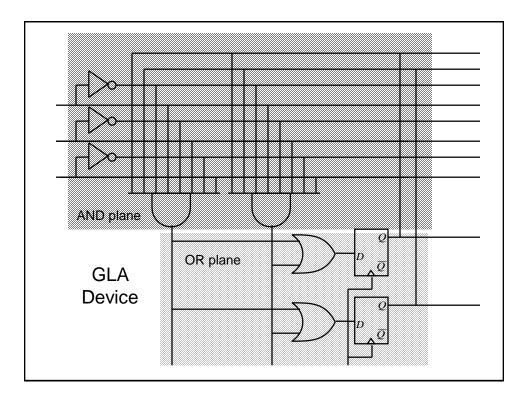

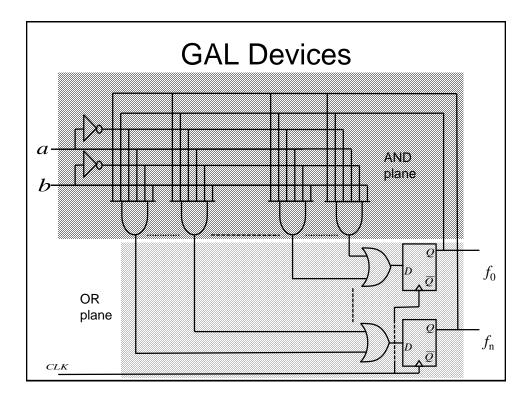

#### **GLA Devices**

- They are similar in concept to PLAs, but have the option to make use of a D-type flipflops in the OR plane (one following each OR gate). In addition, the outputs from the Dtypes are also made available to the AND plane (in addition to the usual inputs)

- Consequently it becomes possible to build programmable sequential logic circuits

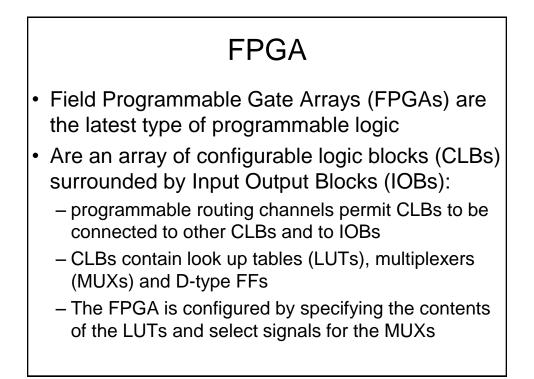

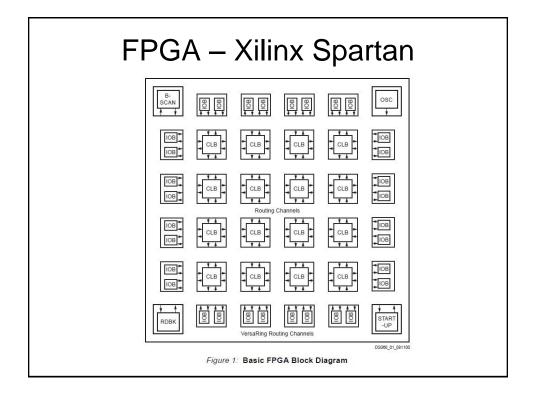

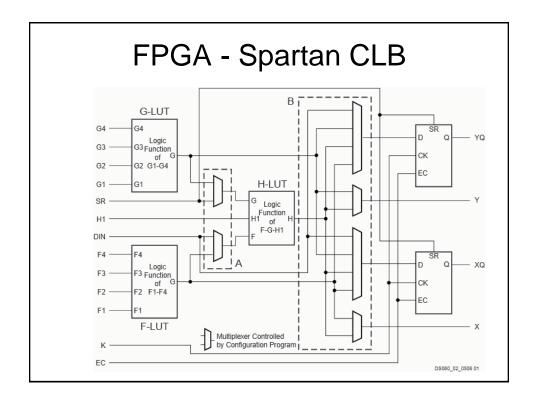

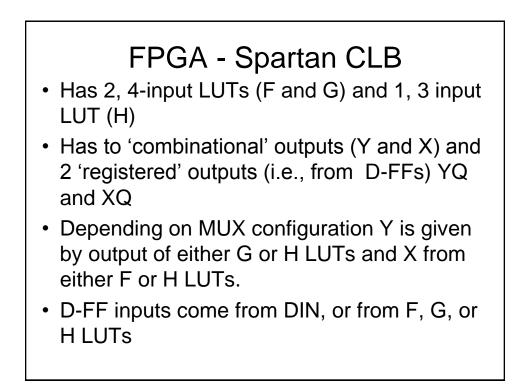

## FPGA - Spartan CLB

- Thus each CLB can perform up to 2 combinational and/or 2 registered functions

- All functions can involve at least 4 input variables (e.g., G1 to G4, and F1 to F4), but can be up to 9 (owing to the possibility of implementing 2-level combinational logic functions), i.e., G1 to G4, F1 to F4, H1.

- Created using either a schematic (block) diagram or more likely a Hardware Description Language (HDL) of the design

## FPGA - Spartan CLB

- The synthesis tool determines how the LUTs, MUXs and routing channels are configured

- This configuration information is then downloaded to the FPGA

- Xilinx devices store their configuration information in static RAM (SRAM) so can be easily reprogrammed

- The SRAM contents can be downloaded either from a computer or from an EEPROM device when the system is powered-up