**Transistors and Gates**

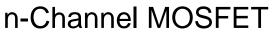

- We will now briefly introduce the n-channel MOSFET

- The charge carriers in this device are electrons

The current flow from D to

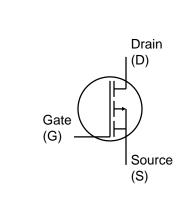

The current flow from D to S ( $I_{DS}$ ) is controlled by the voltage applied between G and S ( $V_{GS}$ ), i.e., G has to be +ve wrt S for current  $I_{DS}$  to flow (transistor **On**)

We will consider enhancement mode devices in which no current flows ( $I_{\rm DS}$ =0, i.e., the transistor is **Off**) when  $V_{\rm GS}$ =0V

## p-Channel MOSFET

• Similarly we have p-channel MOSFETs where the charge carriers are holes

The current flow from S to D ( $I_{DS}$ ) is controlled by the voltage applied between G and S ( $V_{GS}$ ), i.e., G has to be -ve wrt S for current  $I_{DS}$  to flow (transistor **On**)

We will be consider enhancement mode devices in which no current flows ( $I_{DS}$ =0, i.e., the transistor is **Off**) when  $V_{GS}$ =0V

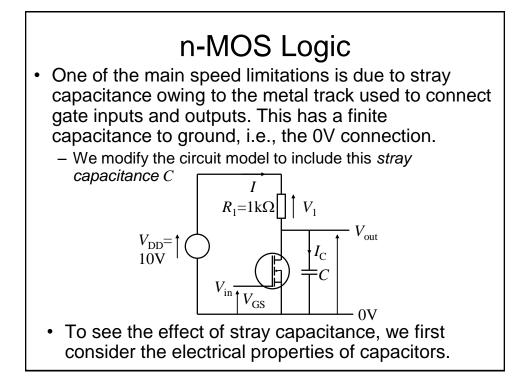

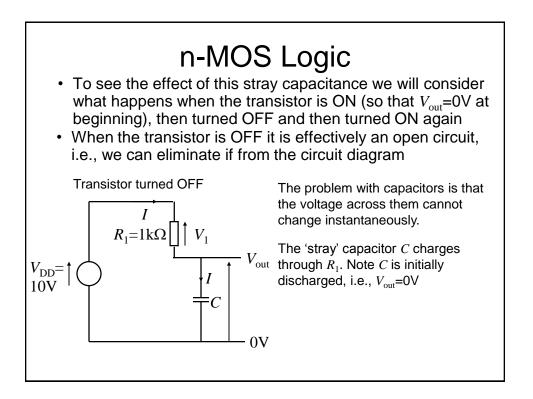

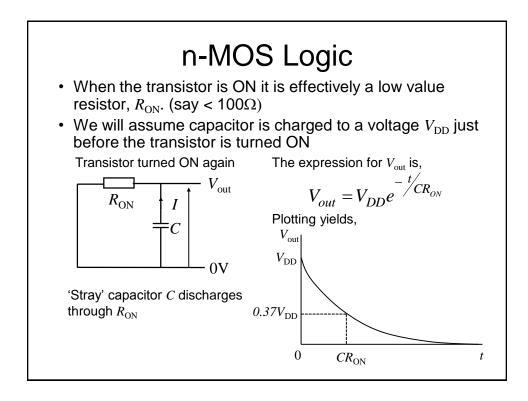

## Capacitors

- So, parallel conductors brought sufficiently close (but not touching) will form a capacitor

- Parallel conductors often occur on circuit boards (and on integrated circuits), thus creating unwanted (or parasitic) capacitors.

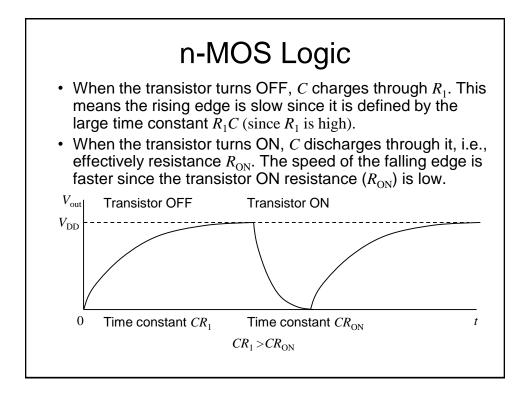

- We will see that parasitic capacitors can have a significant negative impact on the switching characteristics of digital logic circuits.

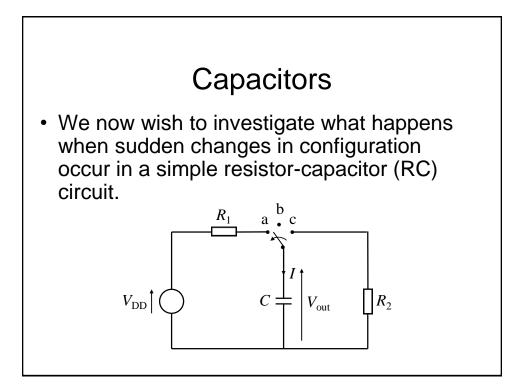

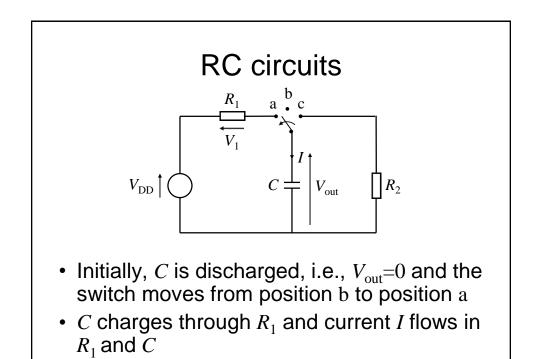

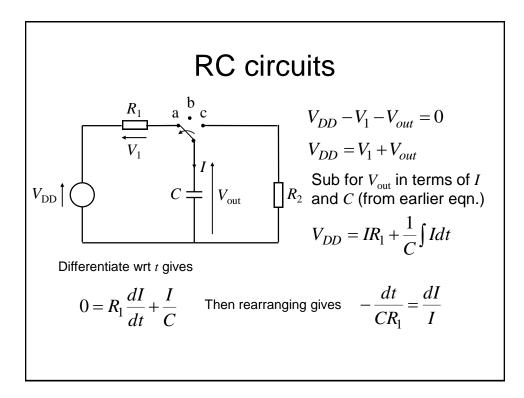

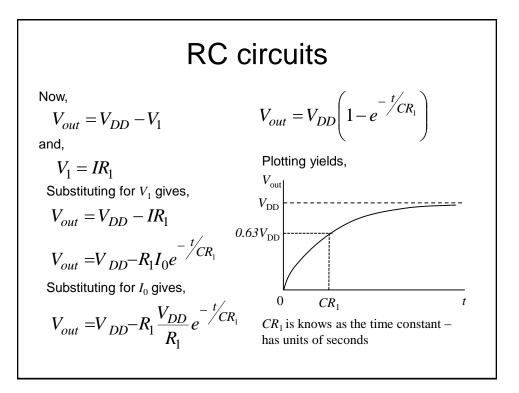

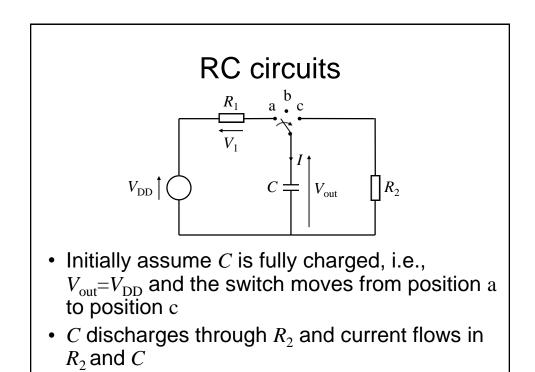

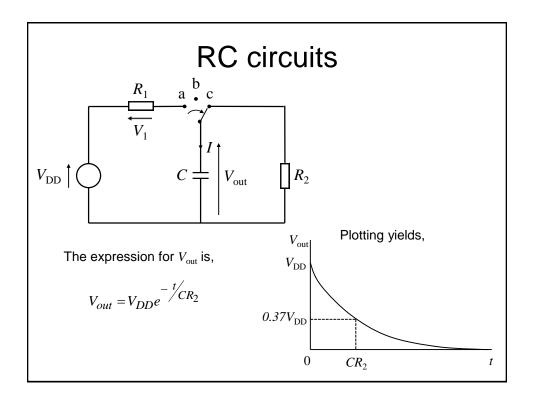

#### **RC** circuits

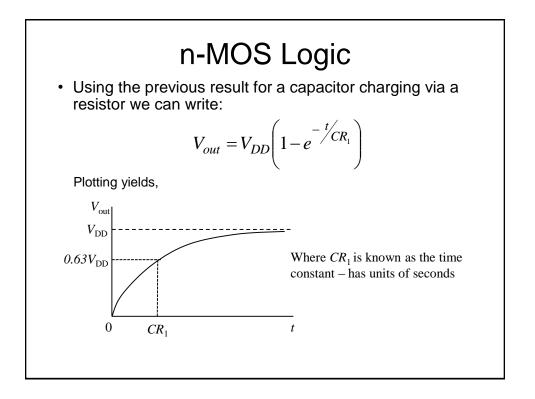

Integrating both sides of the previous equation gives

$$-\frac{t}{CR_1} + a = \ln I$$

We now need to find the integration constant a.

To do this we look at the initial conditions at t = 0, i.e.,  $V_{out}=0$ . This gives an initial current  $I_0=V_{DD}/R_1$

$$a = \ln I_0 = \ln \left(\frac{V_{DD}}{R_1}\right)$$

So,

$$-\frac{t}{CR_1} + \ln I_0 = \ln I$$

$$-\frac{t}{CR_1} = \ln \frac{I}{I_0}$$

Antilog both sides,

$$e^{-\frac{t}{CR_1}} = \frac{I}{I_0}$$

$$I = I_0 e^{-\frac{t}{CR_1}}$$

9

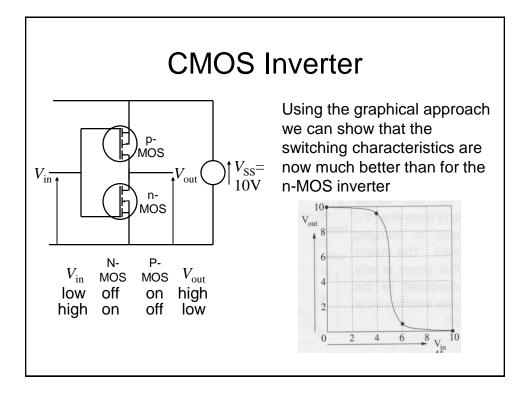

# CMOS Logic

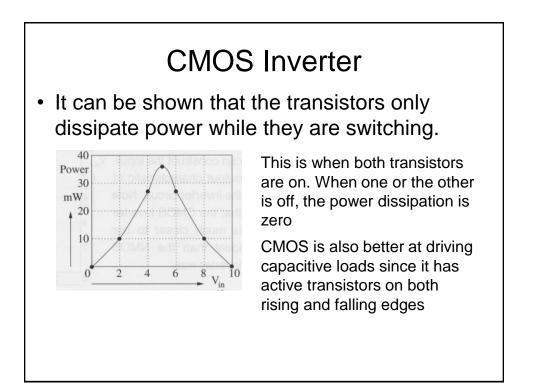

- To overcome these problems, complementary MOS (CMOS) logic was developed

- As the name implies it uses p-channel as well as n-channel MOS transistors

- Essentially, p-MOS transistors are n-MOS transistors but with all the polarities reversed!

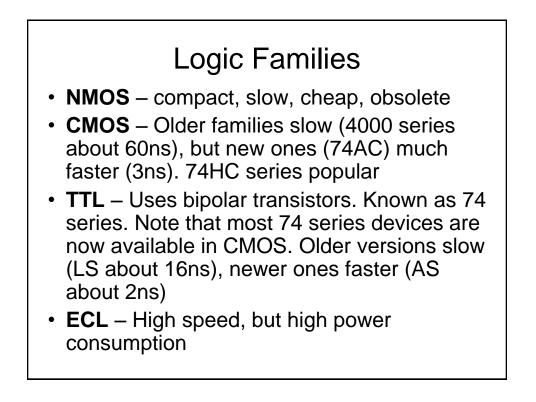

## Logic Families

- Best to stick with the particular family which has the best performance, power consumption cost trade-off for the required purpose

- It is possible to mix logic families and sub-families, but care is required regarding the acceptable logic voltage levels and gate current handling capabilities