# Comparative Architectures

#### **CST** Part II, 16 lectures

#### Lent Term 2006

#### **David Greaves**

David.Greaves@cl.cam.ac.uk

Slides Lectures 1-13

(C) 2006 IAP + DJG

# **Course Outline**

- 1. Comparing Implementations

- Developments fabrication technology

- Cost, power, performance, compatibility

- Benchmarking

- 2. Instruction Set Architecture (ISA)

- Classic CISC and RISC traits

- ISA evolution

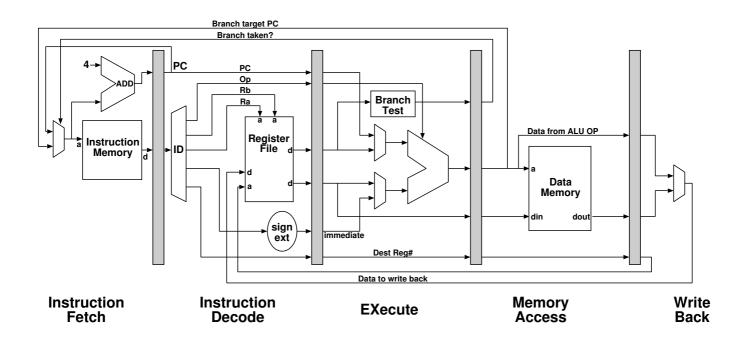

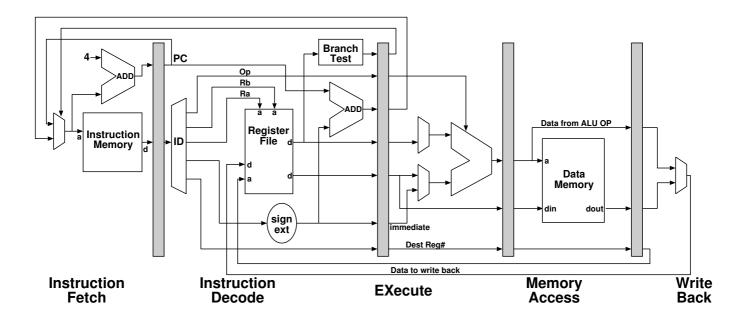

- 3. Microarchitecture

- Pipelining

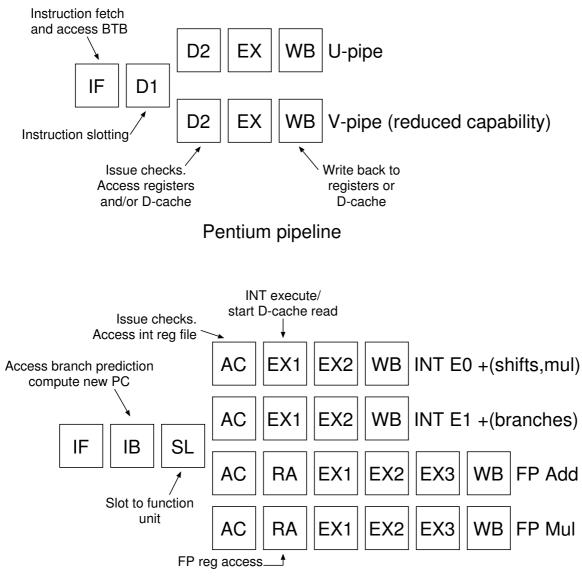

- Super-scalar

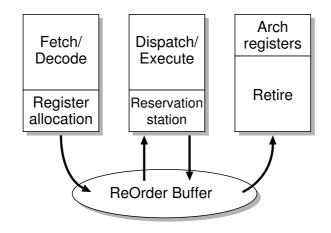

- static & out-of-order

- Multi-threading

- Effects of ISA on  $\mu {\rm architecture}$  and vice versa

- 4. Memory System Architecture

- Memory Hierarchy

- 5. Multi-processor systems

- Cache coherent and message passing

### Understanding design tradeoffs

## **Reading material**

- OHP slides, articles

- Recommended Book: John Hennessy & David Patterson, Computer Architecture: a Quantitative Approach (3rd ed.) 2002 Morgan Kaufmann

- MIT Open Courseware: 6.823 Computer System Architecture, by Krste Asanovic

- The Web

http://bwrc.eecs.berkeley.edu/CIC/ http://www.chip-architect.com/ http://www.geek.com/procspec/procspec.htm http://www.realworldtech.com/ http://www.anandtech.com/ http://www.arstechnica.com/ http://open.specbench.org/

• comp.arch News Group

### Further Reading and Reference

- M Johnson Superscalar microprocessor design 1991 Prentice-Hall

- P Markstein IA-64 and Elementary Functions 2000 Prentice-Hall

- A Tannenbaum, Structured Computer Organization (2nd ed.) 1990 Prentice-Hall

- A Someren & C Atack, The ARM RISC Chip, 1994 Addison-Wesley

- R Sites, Alpha Architecture Reference Manual, 1992 Digital Press

- G Kane & J Heinrich, MIPS RISC Architecture 1992 Prentice-Hall

- H Messmer, The Indispensable Pentium Book, 1995 Addison-Wesley

- Gerry Kane and HP, The PA-RISC 2.0 Architecture book, Prentice Hall

# **Course Pre-requisites**

- Computer Design (Ib)

- Some ARM/x86 Assembler

- Classic RISC pipeline model

- Load/branch delay slots

- Cache hierarchies

- Memory Systems

- Compilers (Ib/II)

- Code generation

- Linkage conventions

- Structured Hardware Design

- Critical paths

- Memories

- (Concurrent Systems)

σ

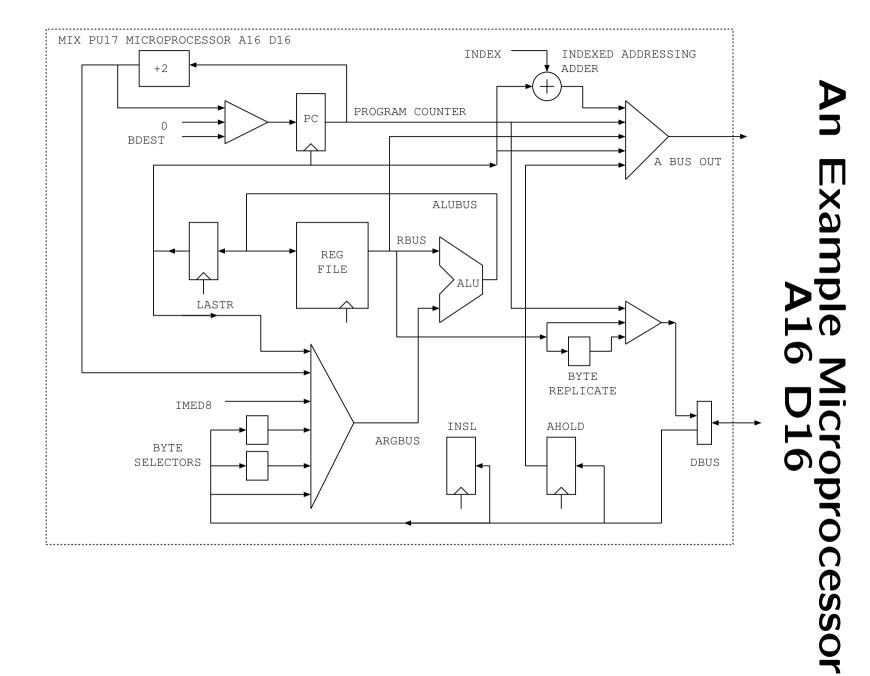

#### P 1 pu17.v microprocessor djg

module PU17CORE(abus16, dbus16 in, dbus16 out, clk, reset, opreg, irg, rwbar, byteop, w\$ aitb); wire advance = f0a | f1; PCM pcm(pc, next pc, advance, clk, waitb, reset, branch, bdest); output [15:0] abus16; RFILE rfile(.rfile in(alubus), .rfile out(rbus), .regnum(regnum), input [15:0] dbus16 in: .cen(waitb), .clk(clk), .regwen(regwen)); output [15:0] dbus16 out; output byteop; assign dbus16 out = (rlasave) ? pc: (byteop) ? { rbus[7:0], rbus[7:0]} :rbus; input clk, reset; output opreg, rwbar; input irq; // The ALU defaults to straight through on the b input, needing fc=12 input waitb; // Acts as a clock enable essentially PUALU pualu(.y(alubus), .a(rbus), .b(argbus), .fc(fc), .clk(clk), .cen(waitb), // Wait should be changed to not gate internal cycles ?\$ .update flags(update flags), .branch condition(branch condition), .branch\_yes(branch\_yes)); // Locals always @(posedge clk) if (sreset) begin f0a <= 0; wire [15:0] pc, next\_pc; f0b <= 0; f0c <= 0; wire [15:0] rbus, alubus, argbus; reg [15:0] ahold, lastr; f1 <= 0; wire branch\_yes; // One if branch condition matches argcycle <= 0; // Synchronise reset input execute <= 0; internal <= 0; req sreset; always @(posedge clk) sreset <= reset; lastr <= 0; ahold <= 0; end req execute; // Execute cvcle reg internal; // Internal cycle (when execute also needed) // Instruction decode wires else if (waitb) begin reg update flags; reg [3:0] branch\_condition; if (~execute & ~f0a & ~f1) rea reawen; begin reg [15:0] bdest; // Branch destination f0a <= 1; // start of day event. reg [2:0] regnum; // Register file read and write ports. f0b <= 1;// start of day event. // start of day event. f0c <= 1; reg write; end else begin reg byteop, byteopreq; reg imed8; f0a <= last\_cycle;</pre> f0b <= last cvcle; reg argreq, argcycle; reg linkf; // Branch and link fOc <= last cycle; reg regind; // Register indirect end // Even offsets to a base reg reg idx7; reg rlasave; // High to save PC as a return address f1 <= f1req;</pre> // High to request an extension argcycle <= argreq;</pre> reg exreq; // Fetch0 and fetch 1 parts of inst reg f0a,f0b,f0c, f1; byteop <= byteopreq;</pre> // End cycle of current instruction execute <= exreq; reg last\_cycle; if (f0a | f1) ahold <= dbus16\_in; // Request for second inst word reg flreg; reg branch; reg [3:0] fc; // ALU function code internal <= internal reg; // Used for reg to reg operations on single ported file\$ reg argislast; // lastr is simply the register read the cycle before. reg multiple; // USed for LDM/STM if (!multiple) lastr <= rbus; reg internal\_reg; end reg [3:0] multiple\_reg; // current register to transfer in STM/LDM initial begin // Form a transparent latch for the old instruction. multiple = 0;reg[15:0] ins l; // Latched instruction opcode (use in fl onwards to re\$ update flags = 0; branch\_condition = 0;

$last_cycle = 0;$

update flags = 0;

reg[15:0] ins\_1; // Latched instruction opcode (use in fl onwar duce combinatorial loops in net list). wire [15:0] ins = (f0a) ? dbus16\_in: ins\_1; // Always valid. always @(posedge clk) if (f0a) ins\_1 <= dbus16\_in;</pre>

#### P 2 pul7.v microprocessor djg

rlasave = 0;regnum = (ins[11:10]==3) ? 7: {1'b0, ins[11:10]}; // Read ex reg to lastr in an internal cycle imed8 = 0;exreg = 1;write = 0;byteopreg = ins[13]; byteopreg = 0;argreg = 1;regnum = 0;end requen = 0;if (execute) begin argreg = 0;regnum = ins\_1[9:7]; argcvcle = 0;last cycle = 1; f1req = 0: regwen = 1: // Indexed load with 6 bit offset fc = 4'd12;idx7 = 1: // ALU default to load mode argislast = 0:end multiple = 0;and end 4'hB, // Instruction decoder. 4'h9: // Store to memory with index always @(ins or ins 1 or f1 or f0a or f0b or f0c or execute or alubus or branch cond\$ begin ition or lastr if (f0c) begin or multiple\_reg or internal or pc or branch\_yes or dbus16\_in or fc) begin regnum = (ins[11:10]==3) ? 7: {1'b0, ins[11:10]}; // Read i last cycle = 0; x reg to lastr in an internal cycle fc = 4'd12;// ALU default to load mode exreq = 1;rlasave = 0;byteopreg = ins[13]; update flags = 0; argreq = 1; update\_flags = 0; end if (execute) begin imed8 = 0;regnum = ins 1[9:7];write = 0;last\_cycle = 1; regnum = 0;write = 1; requen = 0;idx7 = 1;argreq = 0;end bvteopreg = 0;flreq = 0;end linkf = 0;idx7 = 0;4'hC: // C is relative branch (BSR not supported) regind = 0;begin internal\_reg = 0; // not used ? branch condition = ins[11:8]; exreq = 0;branch = branch ves; argislast = 0: bdest = pc + { 7 { ins[7] }, ins[7:0], 1'b0 }; branch = 0; $last_cycle = 1;$ bdest = 0;end branch condition = ins[5:2]; multiple = 0;4'hD: if (ins[11:10] == 2'b00) begin // D0 is arith reg, reg fc = ins[6:3]; case(ins[15:12]) if (f0c) begin 4'h0, 4'h1, 4'h2, 4'h3, 4'h4, 4'h5, 4'h6, 4'h7: exreq = 1;// Read reg on first cycle regnum = ins[2:0]; // Arith/alu immed 8 bits, one cycle. // If a shift, the immed arg is ignored and a shift of one is always done. end if (f0c) begin if (execute) begin last cycle = 1; regnum = ins 1[9:7];fc = ins[6:3];argislast = 1; regnum = ins[9:7]; $last_cycle = 1;$ regwen = (fc!=5 && fc!=13); // Not cmp or tst ; regwen = (fc!=5 && fc!=13); // Not cmp or tst update\_flags = 1; update\_flags = 1; imed8 = 1;end end end else if (ins[11:10] == 2'b01) begin // Load/store from memory abs 16 4'hA, regnum = ins[9:7]; 4'h8: // Load from memory with index byteopreq = ins\_l[6]; begin if (ins[5]==0) begin // Load from an abs 16 bit address if (f0c) begin if (f0b) begin

#### P 3 pu17.v microprocessor djg

flreg = 1;else begin // load if (f0c) begin end if (f1) begin f1req = 1;exreq = 1;regnum = 7;argreg = 1;end end if (f1) begin if (execute) begin flreg = multiple reg != 8; reawen = 1: multiple = 1; last cycle = 1; last\_cycle = multiple\_reg == 8; end requen = 1; regnum = multiple\_reg; and end else// Store to memory abs 16 end begin regnum = ins[9:7];if (f0b) begin and flreg = 1;end 4′hF: if (f1) begin exreq = 1;if (ins[11:10] == 0) begin // F0 is register jump (used for ret) and bxl which is indirect bran and link argreq = 1; if (ins[0]) begin // with link is two cycles end if (execute) begin if (f0c) begin write = 1; exreq = 1;last cycle = 1; regnum = ins[9:7];end end end end if (execute) begin  $last_cycle = 1;$ bdest = lastr; else if (ins[11:10] == 2'b10) begin // D8, abs cond jump or link regnum = 6;if (f0c) flreg = 1; linkf = 1;if (f1) begin requen = 1;if (branch condition == 15) begin // Branch with save o\$ branch = 1; f PC in r6 end regnum = 6;end requen = 1; else begin // without link linkf = 1;if (f0c) begin branch = 1;regnum = ins[9:7]; end last\_cycle = 1; else branch = branch\_yes; bdest = alubus; bdest = dbus16\_in; branch = 1;last\_cycle = 1; fc = 0;// function code 0 f end reg unmodified end end end else if (ins[11:10] == 2'b11) begin // LDM/STM end if (ins[1]) begin// store if (f0c) begin flreq = 1;else if (ins[11:10] == 1) begin // F4 is load immediate 16 bit regnum = 7;regnum = ins[9:7]; if (f0c) begin end if (f1) begin flreq = 1;flreq = multiple\_reg != 8; end multiple = 1; if (f1) begin last\_cycle = multiple\_reg == 8; requen = 1; write = 1; last cycle = 1; regnum = multiple\_reg; end end end end

#### P 4 pu17.v microprocessor djg

endcase and 4: multiple reg <= (ins[7]) ? 5: (ins[8]) ? 6: (ins[9]) ? 7: 8; assign rwbar = ~write: assign opreq = argcycle | f0a | f1; 5: multiple\_reg <= (ins[8]) ? 6: assign abus16 = (ins[9]) ? 7: 8; (f0a|f1) ? pc: // Instruction fetch (multiple) ? lastr + { multiple\_reg, 1'b0 }: // LDM STM 6: multiple\_reg <= (ins[9]) ? 7: 8; (idx7) ? lastr + { 8 {ins\_1[5]}, ins\_1[6:0], 1'b0 }: // 7 bit indexe\$ d addressing 7: multiple reg <= 8; (regind) ? lastr: // Register indirect ahold; // General absolute addresses endcase //wire [15:0] testt = { 10'b0+ins[5:0]}; and assign argbus = (imed8) ? { 8'b0, ins[14:10], ins[2:0] }: endmodule (argislast) ? lastr: 11 (linkf) ? next pc: 11 (byteop & ~abus16[0]) ? { 8'h00, dbus16\_in[7:0] }: // Little endian 11 (byteop & abus16[0]) ? { 8'h00, dbus16\_in[15:8] }: 11 // ALU AND FLAGS dbus16 in; 11 module PUALU(y, a, b, fc, clk, cen, update\_flags, branch\_condition, branch\_yes); // LDM STM next register logic reg old\_multiple; input [3:0] fc; // Function code always @(posedge clk) begin input [15:0] a, b; old multiple <= multiple; input clk, cen, update flags; if (~old\_multiple) begin input [3:0] branch\_condition; multiple reg <= (ins[2]) ? 0: output branch\_yes; (ins[3]) ? 1: (ins[4]) ? 2: reg carry, zero, negative, overflow; (ins[5]) ? 3: (ins[6]) ? 4: output [15:0] v; (ins[7]) ? 5: reg [15:0] y; (ins[8]) ? 6: wire [15:0] addsub; (ins[9]) ? 7: 8; end always @(a or b or fc or addsub) case (fc) else case (multiple\_reg) 0: y = a; // straight through of register bus, used for store. 0: multiple reg <= (ins[3]) ? 1: 1: y = addsub;2: v = addsub;(ins[4]) ? 2: (ins[5]) ? 3: 3: y = addsub;(ins[6]) ? 4: 4: y = addsub;5: y = addsub;(ins[7]) ? 5: // CMP (ins[8]) ? 6: 6: y = a | b;7: y = a & b; (ins[9]) ? 7: 8; 1: multiple\_reg <= (ins[4]) ? 2: 8:  $y = a^{h}$ ; (ins[5]) ? 3: 9: y = a << 1;// ASL/LSL (ins[6]) ? 4: 10: y = { a[15], a[15:1] }; // ASR (ins[7]) ? 5: 11: y = a >> 1;// LSR 12: y = b;// Used for mov/load (ins[8]) ? 6: 13: y = a & b; // TST (ins[9]) ? 7: 8; 2: multiple\_reg <= (ins[5]) ? 3: default : y = addsub; // y = 16' bx;(ins[6]) ? 4: endcase (ins[7]) ? 5: (ins[8]) ? 6: wire n\_carry; (ins[9]) ? 7: 8; wire n\_overflow; 3: multiple\_reg <= (ins[6]) ? 4: ADDSUB addsub(addsub, a, b, n\_carry, carry, n\_overflow, fc); (ins[7]) ? 5: (ins[8]) ? 6: (ins[9]) ? 7: 8; always @(posedge clk) if (update\_flags & cen) begin

#### P 5 pul7 microprocessor djg

```

carry <= (fc==9)?a[15]: (fc==10)?a[0]: (fc==11)?a[0]: n carry;

zero <= (v==16'h0);

negative \leq v[15];

overflow <= 0;

and

// These conditions follow exactly the 6800 processor.

reg branch yes;

always @(branch condition or carry or overflow or zero or negative)

case (branch condition)

0: branch_yes = zero; // EQ

1: branch_yes = ~zero; // NE

2: branch yes = (negative ^ overflow); // LT

3: branch_yes = ~(negative ^ overflow) | zero; // GE

4: branch_yes = ~(negative ^ overflow) & ~zero; // GT

5: branch_yes = (negative ^ overflow) | zero; // LE

6: branch yes = carry;

7: branch_yes = ~carry;

8: branch_yes = overflow;

9: branch yes = ~overflow;

10: branch_yes = 1; // unconditional

11: branch yes = ~carry & ~zero; // HI

12: branch_yes = carry | zero; // LS

13: branch_yes = negative; // MI

14: branch yes = ~negative; // PL

default: branch yes = 1; // Used for link

endcase

endmodule

11

11

11

11

module ADDSUB(addsub, a, b, n carry, carry, n overflow, fc);

input [3:0] fc;

// Function code

input [15:0] a, b;

input carry;

output [15:0] addsub;

output n_overflow, n_carry;

1: y = a + b;

11

11

2: y = a - b;

3: y = a + b + carry;

11

4: y = a - b - carry;

11

11

11

reg c;

reg [15:0] bb;

always @(fc or b or carry) case (fc)

1: begin bb = b; c = 0; end

default: begin bb = ~b; c = 1; end // Subtract, compare and test.

3: begin bb = b; c = carry; end

4: begin bb = ~b; c = carry; end

endcase

wire [25:0] g, neta, netb;

```

assign neta = { 8'b0, 1'b0, a, c }; assign netb = { 8'b0, 1'b0, bb, c }; ADDER26 adder26(g, neta, netb); assign n carry = g[17]; // carry is in bit 18 if we had 1 in bit17 of netb assign addsub =  $\alpha[16:1]$ : wire msb a = a[15]; wire msb bb = bb[15]: assign n overflow = (msb a == msb bb) && (n carry ^ g[16]); endmodule 11 11 11 11 11 11 11 module RFILE(rfile in, rfile out, regnum, clk, cen, regwen); input [15:0] rfile in; output [15:0] rfile out; input [2:0] regnum; input clk, cen; wire [15:0] y; input requen; wire wen = cen & regwen; // Write new data wire [15:0] nd = rfile in; // Write adderess wire [3:0] wa = { 1'b0, regnum }; 'ifndef SYNTHESIS // Put this in for ease of tracing during behev simulation. reg [15:0] r0, r1, r2, r3, r4, r5, r6, r7; always @(posedge clk) begin if (wen && wa == 0) r0 <= nd; if (wen && wa == 1) r1 <= nd; if (wen && wa == 2)  $r^{2} <= nd;$ if (wen && wa == 3) r3 <= nd; if (wen && wa == 4) r4 <= nd; if (wen && wa == 5) r5 <= nd; if (wen && wa == 6) r6 <= nd; if (wen && wa == 7) r7 <= nd; end assign rfile out = (regnum == 0) ? r0: (regnum == 1) ? r1: (regnum == 2) ? r2: (regnum == 3) ? r3: (regnum == 4) ? r4: (regnum == 5) ? r5: (regnum == 6) ? r6:

r7;

'else

#### 11

#### P 6 pul7 microprocessor djg

assign rfile\_out = y;

// 16 words of RAM here, but use only first few for R0-7

RAMS16x16 register\_ram(y, nd, wen, clk, wa);

'endif

endmodule

module PCM (pc, next\_pc, advance, clk, cen, sreset, branch, bdest);

input branch; input [15:0] bdest; output [15:0] pc, next\_pc; input clk, cen, sreset, advance;

reg [15:0] pc;

always @(posedge clk) if (sreset) pc <= 0; else if (cen & branch) pc <= bdest; else if (cen & advance) pc <= next\_pc;</pre>

assign next\_pc = pc+2; endmodule

#### P 1 pu17-opcode-map djg

\_\_\_\_\_ 0-7 0xxx. R3DEST, ALU4, IMMED8 : Imm 8 bit 7, 3, 14-10, 2-0 8-B 10xx. BYTEF, STOREF, IDXR2, REG3, IDX7, : Indexed load/stores/add/sub 13, 12, 10, 7, 0 : \_\_\_\_\_ C 1100. COND4, OFFSET8 : Relative branches + bsr 8 0 D0 1101.00 R3DEST, ALU4, R3SRC : ALU reg, reg ops 7 3 0 \_\_\_\_\_ D4 1101.01 REG3, BYTEF1, STOREF, ABS16 : Abs16 load/store 7 6 5, next \_\_\_\_\_ D8 1101.10 COND4, ABS16 : Absolute jmp jsr 2, \_\_\_\_\_ : Load/store multiple DC 1101.11 RLIST8 STOREF 2, 1 : Upwards from R7, r7 not chang\$ ed F0 1111.00 REG3 LinkF : Branch indirect 7, 0 : bx, bxl \_\_\_\_\_ F4 1111.01 REG3, Immed16 : Load immediate (mov special c\$ ase)

PU17 OPCODE MA

#### P 1 pul7-assembly-example djg

| 781                                                                                                                                                                                        |                                                                                                                                                                                                                                                            | ; int iread(len)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 842                                                                                                                                                                                                        |                                     | dy33            | ; anon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 782                                                                                                                                                                                        |                                                                                                                                                                                                                                                            | ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 843                                                                                                                                                                                                        | 032C FCAC                           |                 | lodb R1,[R7,#-8] ; risf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 783                                                                                                                                                                                        |                                                                                                                                                                                                                                                            | ; {                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 844                                                                                                                                                                                                        | 032E 9718                           |                 | sub R1,#55 ; alu_i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 784                                                                                                                                                                                        |                                                                                                                                                                                                                                                            | i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 845                                                                                                                                                                                                        | 0330 61D0                           |                 | mov R0,R1 ; ltmv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 785                                                                                                                                                                                        |                                                                                                                                                                                                                                                            | ; int $r = 0$ ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 846                                                                                                                                                                                                        |                                     | dv34            | ; anon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 786                                                                                                                                                                                        |                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 847                                                                                                                                                                                                        | 0332 7CBC                           |                 | strb R0,[R7,#-8] ; assign                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 787                                                                                                                                                                                        |                                                                                                                                                                                                                                                            | ; int i;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 848                                                                                                                                                                                                        | 0002 /000                           |                 | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                            |                                                                                                                                                                                                                                                            | , 111, 1,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                            |                                     |                 | , , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 788                                                                                                                                                                                        |                                                                                                                                                                                                                                                            | ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 849                                                                                                                                                                                                        |                                     |                 | ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 789                                                                                                                                                                                        |                                                                                                                                                                                                                                                            | ; for (i=0; i < len; i++)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 850                                                                                                                                                                                                        | 0334 7E8C                           |                 | lod R0,[R7,#-4] ; risf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 790                                                                                                                                                                                        |                                                                                                                                                                                                                                                            | ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 851                                                                                                                                                                                                        | 0336 4900                           |                 | asl R0,#1 ; fshif                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 791                                                                                                                                                                                        | 02D4 6000                                                                                                                                                                                                                                                  | lod R0,#0 ; lti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 852                                                                                                                                                                                                        | 0338 4900                           |                 | asl R0,#1 ; fshif                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 792                                                                                                                                                                                        | 02D6 7D9C                                                                                                                                                                                                                                                  | str R0,[R7,#-6] ; assign                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 853                                                                                                                                                                                                        | 033A 4900                           |                 | asl R0,#1 ; fshif                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 793                                                                                                                                                                                        |                                                                                                                                                                                                                                                            | dy29 ; anon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 854                                                                                                                                                                                                        | 033C 4900                           |                 | asl R0,#1 ; fshif                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 794                                                                                                                                                                                        | 02D8 7D8C                                                                                                                                                                                                                                                  | lod R0,[R7,#-6] ; risf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 855                                                                                                                                                                                                        | 033E FCAC                           |                 | lodb R1,[R7,#-8] ; risf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 795                                                                                                                                                                                        | 02DA 818C                                                                                                                                                                                                                                                  | lod R1,[R7,#2] ; risf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 856                                                                                                                                                                                                        | 0340 09D0                           |                 | add R0,R1 ; alu-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 796                                                                                                                                                                                        |                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 857                                                                                                                                                                                                        | 0342 7E9C                           |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                            | 02DC 29D0                                                                                                                                                                                                                                                  | cmp R0,R1 ; alu-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                            |                                     |                 | str R0,[R7,#-4] ; assign                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 797                                                                                                                                                                                        | 02DE 0CD84C03                                                                                                                                                                                                                                              | bge dy30 ; fjump F ; cfj                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 858                                                                                                                                                                                                        | 0344 7D8C                           |                 | lod R0,[R7,#-6] ; risf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 798                                                                                                                                                                                        |                                                                                                                                                                                                                                                            | ; {                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 859                                                                                                                                                                                                        | 0346 0900                           |                 | add R0,#1 ; qas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 799                                                                                                                                                                                        |                                                                                                                                                                                                                                                            | ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 860                                                                                                                                                                                                        | 0348 7D9C                           |                 | str R0,[R7,#-6] ; qasmi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 800                                                                                                                                                                                        |                                                                                                                                                                                                                                                            | ; local c [R7,#-8]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 861                                                                                                                                                                                                        | 034A C7CA                           |                 | bra dy29 ; anon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 801                                                                                                                                                                                        |                                                                                                                                                                                                                                                            | ; S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 862                                                                                                                                                                                                        |                                     | dy30            | ; anon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 802                                                                                                                                                                                        | 02E2 80D410DF                                                                                                                                                                                                                                              | lod R1,_inpoi ; ris                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 863                                                                                                                                                                                                        |                                     | -               | ; }                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 803                                                                                                                                                                                        | 02E6 61D0                                                                                                                                                                                                                                                  | mov R0,R1 ; gasp1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 864                                                                                                                                                                                                        |                                     |                 | , .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 804                                                                                                                                                                                        | 02E8 0900                                                                                                                                                                                                                                                  | , , , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 865                                                                                                                                                                                                        |                                     |                 | ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                            |                                                                                                                                                                                                                                                            | add R0,#1 ; qasp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                            |                                     |                 | ; return r;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 805                                                                                                                                                                                        | 02EA 20D410DF                                                                                                                                                                                                                                              | str R0,_inpoi ; qasp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 866                                                                                                                                                                                                        |                                     |                 | ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 806                                                                                                                                                                                        | 02EE 00A4                                                                                                                                                                                                                                                  | lodb R0,[R1] ; risf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 867                                                                                                                                                                                                        | 034C 7EAC                           |                 | lodb R0,[R7,#-4] ; risf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 807                                                                                                                                                                                        |                                                                                                                                                                                                                                                            | ; force VRO to O ; call                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 868                                                                                                                                                                                                        |                                     |                 | ; force VRO to 0 ; loadtod0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 808                                                                                                                                                                                        | 02F0 67D1                                                                                                                                                                                                                                                  | mov r2,r7 ; call                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 869                                                                                                                                                                                                        | 034E 7F8F                           |                 | lod R6,[R7,#-2] ; cr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 809                                                                                                                                                                                        | 02F2 1405                                                                                                                                                                                                                                                  | sub r2,#12 ; call                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 870                                                                                                                                                                                                        | 0350 808F                           |                 | lod r7,[r7] ; cr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 810                                                                                                                                                                                        | 02F4 3CD88E21                                                                                                                                                                                                                                              | jsr _toupper ; call                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 871                                                                                                                                                                                                        | 0352 00F3                           |                 | ret ; cr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |