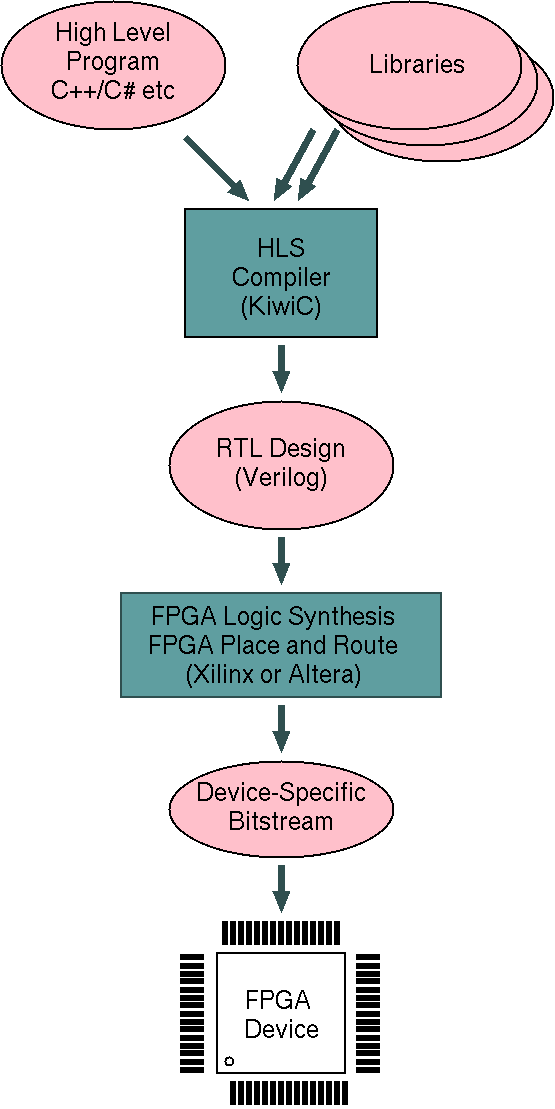

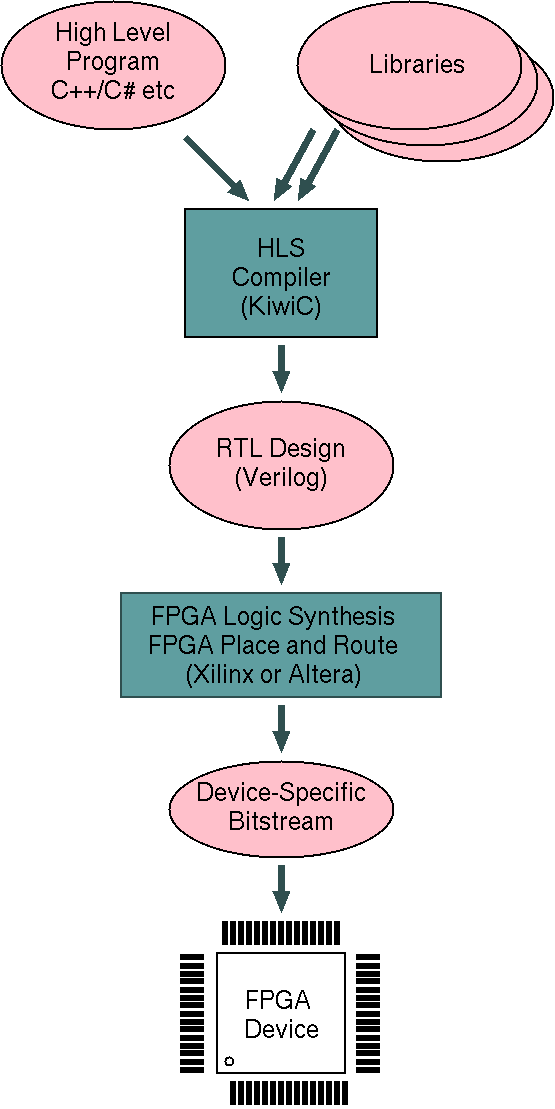

Basic Steps of an HLS Flow.

Generally speaking, High-Level Synthesis (HLS) compiles software into hardware.

Although a research topic for decades, HLS is now seeing industrial traction.

An HLS system revolves around an HLS compiler for a high-level language (typically C++). This

The output from an High-Level Synthesis (HLS) compiler is generally RTL which is then fed to an RTL compiler, aka Logic Synthesiser, that performs logic synthesis. As we have seen, the logic synthesizer

Traditional RTL design entry (Verilog/VHDL) needs:

Performing a Time-for-Space re-folding (i.e. doing the same job with more/less silicon over less/more time) requires a complete redesign when entered manually in RTL!

Optimising schedules in terms of memory port and ALU uses ? RTL requires us use Pen and paper?

Can we do better than manual RTL coding ? Yes, we use High-Level Synthesis.

Dark silicon facilitates `Conservation Cores'. A paper at ASPOLOS'10 about putting common kernels in silicon and `Reducing the Energy of Mature Computations' by power gating. »PDF

| 3: (C) 2008-18, DJ Greaves, University of Cambridge, Computer Laboratory. |