The four-phase handshake just described is suitable for asynchronous interfaces. It does not refer to a clock.

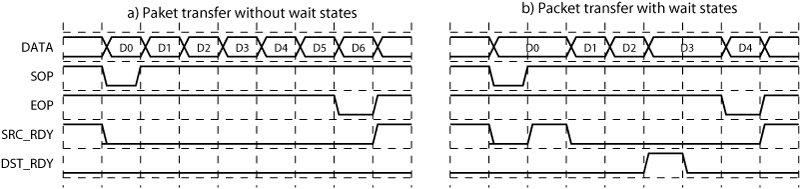

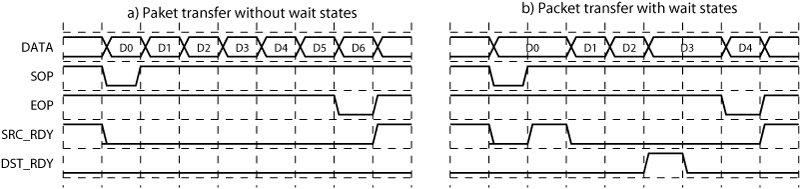

A very common paradigm for synchronous flow control of a uni-directional bus is to have a handshake net in each direction with bus data being qualified as valid on any positive clock edge where both handshake nets are asserted. The nets are typically called `enable' and `ready'.

This paradigm forms the essence of the LocalLink protocol from Xilinx and AXI-streaming protocols defined by ARM.

Like the four-phase handshake, LocalLink has contra-flowing

The interface nets for an eight-bit transmitting interface are:

input clk; output [7:0] xxx_data; // The data itself output xxx_sof_n; // Start of frame output xxx_eof_n; // End of frame output xxx_src_rdy_n; // Req input xxx_dst_rdy_n; // Ack

To impose packed delineation on the bus, LocalLink defines start and end of frame signals.

Note: all control signals are active low (denoted with the underscore n RTL suffix ) in LocalLink.

| 4: (C) 2008-18, DJ Greaves, University of Cambridge, Computer Laboratory. |