HOME

UP

PREV

NEXT (FPGA As The Main Or Only Processor ?)

FPGA Computing to replace Von Neumann Dominance?

The Von Neumann computer hit a wall in terms of increasing clock frequency. It is widely accepted that

Parallel Computing is the most energy-efficient way forward.

The FPGA is intrinsically massively-parallel and can exploit the abundant transistor count of contemporary VLSI.

Andre DeHon points out that the Von Neumann architecture no

longer addresses the correct problem: he writes

»`Stored-program processors are about compactness, fitting the computation into the minimum area possible.'

Why is computing on an FPGA becoming a good idea ?

Spatio-Parallel processing uses less energy than equivalent temporal processing (ie at higher clock rates) for

various reasons. David Greaves gives nine:

- Pollack's rule states that energy use in a Von Neumann CPU grows with square of its IPC. But the FPGA with a static

schedule moves the out-of-order overheads to compile time.

- To clock CMOS at a higher frequency needs a higher voltage, so energy use has quadratic growth with frequency.

- Von Neumann SIMD extensions greatly amortise fetch and decode energy, but FPGA does better, supporting precise custom word widths, so no waste at all.

Standard computers support fixed data sizes only and only two encodings (integer and floating point), both of which can waste a lot of energy compared with better encodings

»[Constantinidies].

- FPGA can implement massively-fused accumulate rather than re-normalising after each summation.

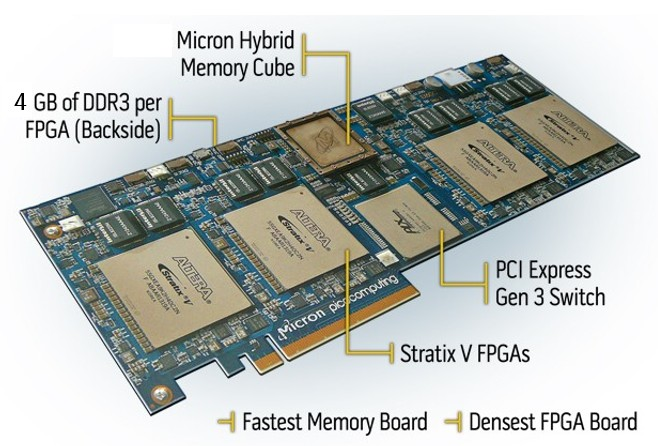

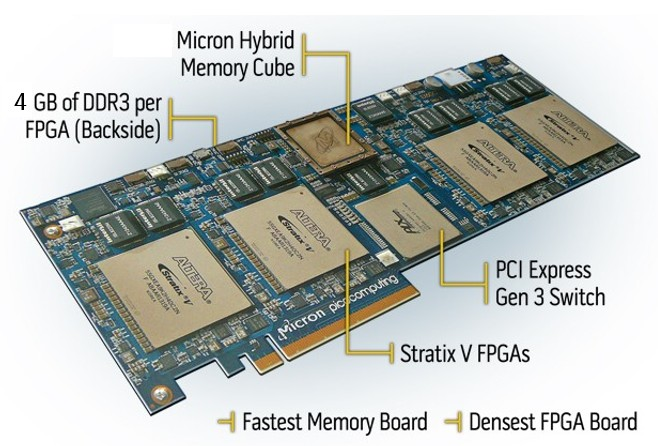

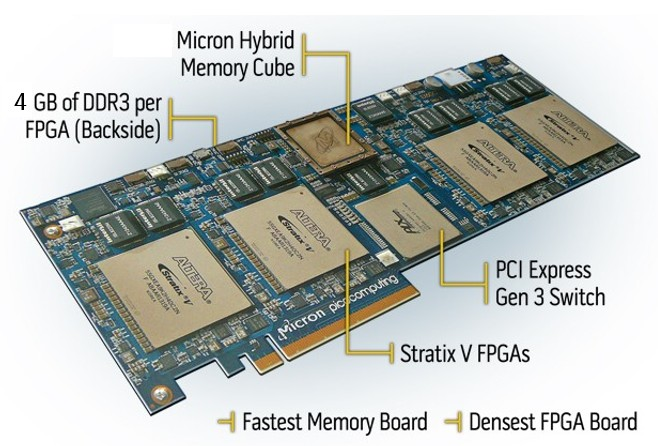

- Memory bandwidth: FPGA has always had superb on-chip memory bandwidth but latest generation FPGA exceeds CPU on DRAM bandwidth too.

- FPGA using combinational logic uses zero energy re-computing sub-expressions whose support has not changed. And it has no overhead determining whether it has changed.

- FPGA has zero conventional instruction fetch and decode energy and its controlling micro-sequencer or predication energy can be close to zero.

- Data locality can easily be exploited on FPGA --- operands are held closer to ALUs near-data-processing

(but the FPGA overall size is x10 times larger (x100 area) owing to overhead of making it reconfigurable.

So

- The massively-parallel premise of the FPGA is the correct way forward, as indicated by asymptotic limit studies [DeHon].

Programming an FPGA has been a problem. As we shall discuss in a later section, end users cannot be expected to be hardware or RTL experts.

Instead, new compiler techniques to port software-style programming to the FPGA are developing. The main approaches today are OpenCL and HLS.