Dr. I. J. Wassell

## Aims

- · To familiarise students with

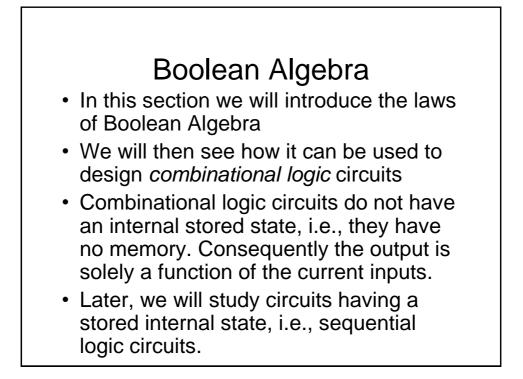

- Combinational logic circuits

- Sequential logic circuits

- How digital logic gates are built using transistors

- Design and build of digital logic systems

- At the end of the course you should

- Be able to design and construct simple digital electronic systems

- Be able to understand and apply Boolean logic and algebra – a core competence in Computer Science

- Be able to understand and build state machines

## Simulation Software

- There are a number of packages available that enable simulation of digital electronic circuits using a graphical interface e.g.,

- National Instruments (NI) Multisim

- Yenka Electronics (Technology Package)

- The former is much more powerful (and expensive), but the latter is relatively straightforward to use and is free to use (except between 8.30 and 15.00)

- You may have used Yenka Electronics at school. It is free to download

### Semiconductors to Computers

- Increasing levels of complexity

- Transistors built from semiconductors

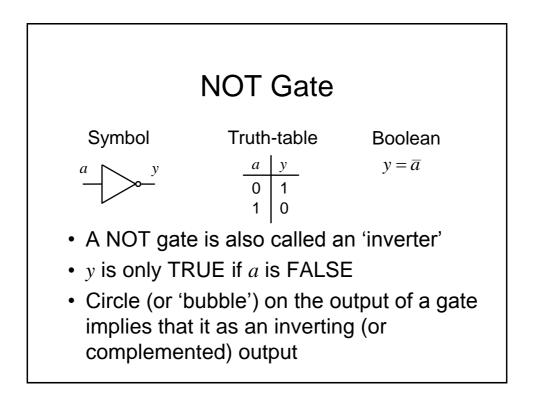

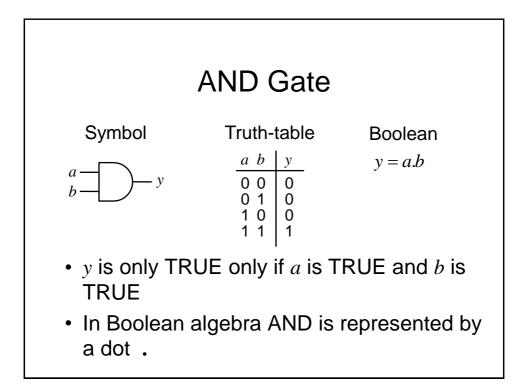

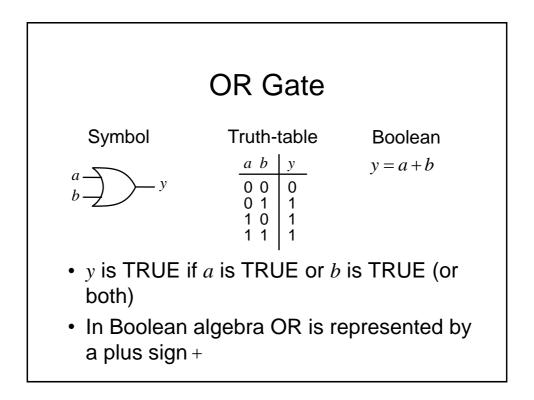

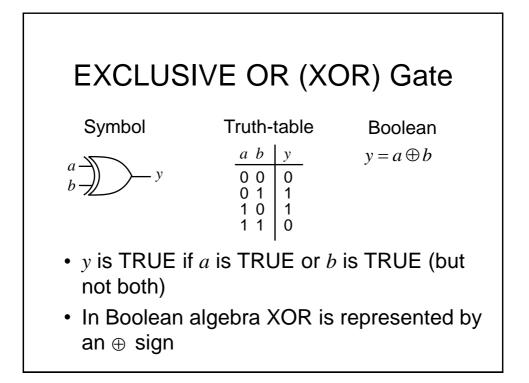

- Logic gates built from transistors

- Logic functions built from gates

- Flip-flops built from logic

- Counters and sequencers from flip-flops

- Microprocessors from sequencers

- Computers from microprocessors

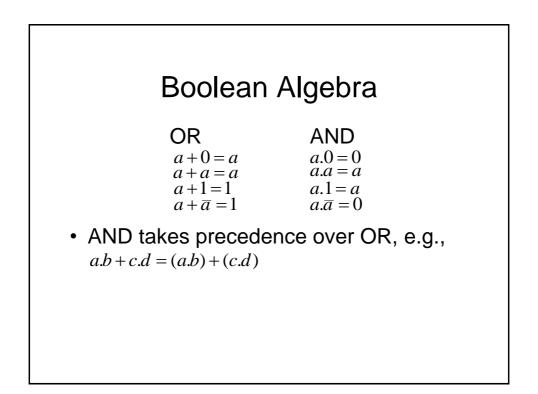

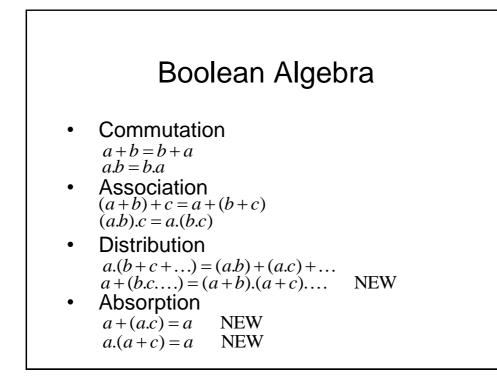

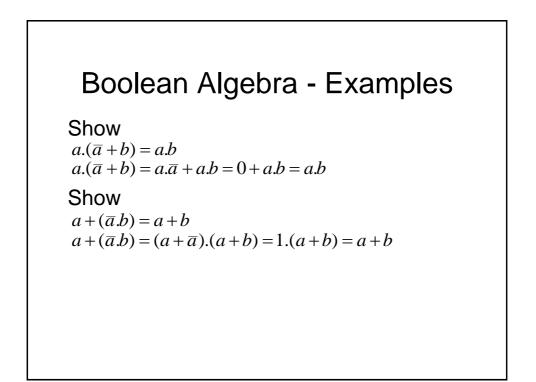

### **Boolean Algebra**

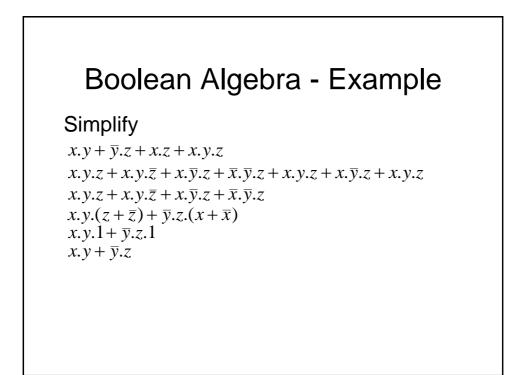

A useful technique is to expand each term until it includes one instance of each variable (or its compliment). It may be possible to simplify the expression by cancelling terms in this expanded form e.g., to prove the absorption rule:

$$a+a.b = a$$

$$a.b+a.\overline{b} + a.b = a.b + a.\overline{b} = a.(b+\overline{b}) = a.1 = a$$

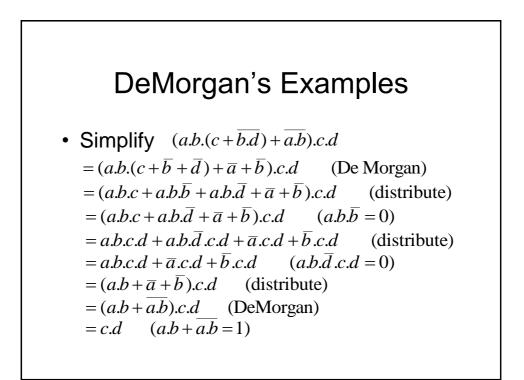

#### DeMorgan's Examples

• Simplify  $a.\overline{b} + a.(\overline{b+c}) + b.(\overline{b+c})$

- $= a.\overline{b} + a.\overline{b}.\overline{c} + b.\overline{b}.\overline{c}$  (DeMorgan)

- $= a.\overline{b} + a.\overline{b}.\overline{c}$  (b. $\overline{b} = 0$ )

- $=a.\overline{b}$  (absorbtion)

- Any Boolean function can be implemented directly using combinational logic (gates)

- However, simplifying the Boolean function will enable the number of gates required to be reduced. Techniques available include:

- Algebraic manipulation (as seen in examples)

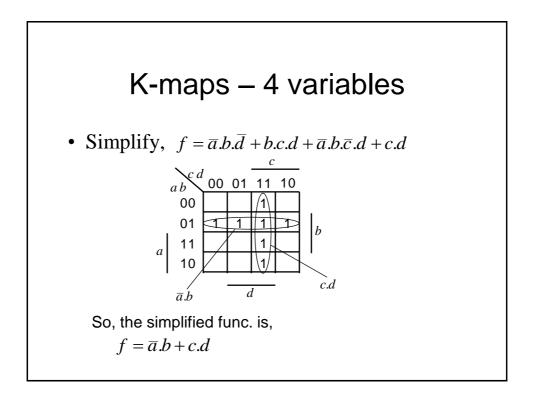

- Karnaugh (K) mapping (a visual approach)

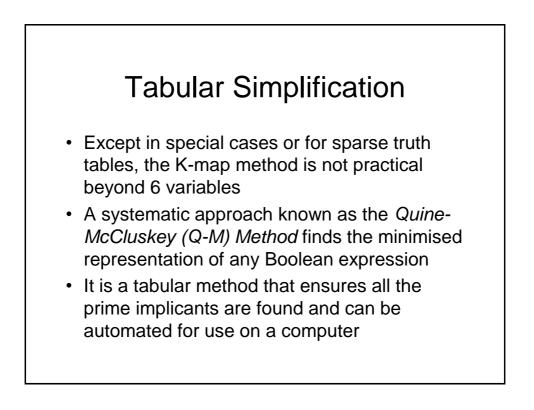

- Tabular approaches (usually implemented by computer, e.g., Quine-McCluskey)

- K mapping is the preferred technique for up to about 5 variables

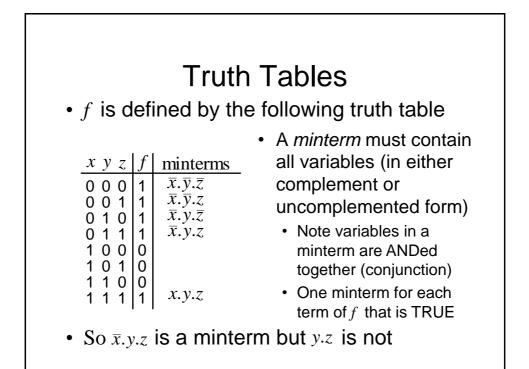

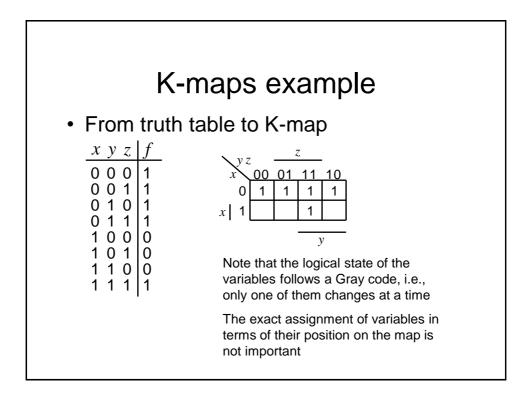

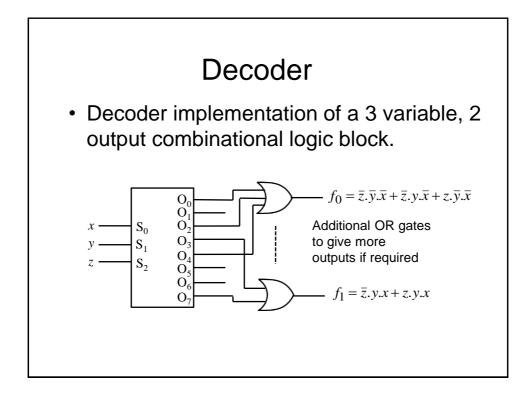

A Boolean function expressed as the disjunction (ORing) of its minterms is said to be in the Disjunctive Normal Form (DNF)

$f = \overline{x} \cdot \overline{y} \cdot \overline{z} + \overline{x} \cdot \overline{y} \cdot z + \overline{x} \cdot y \cdot \overline{z} + \overline{x} \cdot y \cdot z + x \cdot y \cdot z$

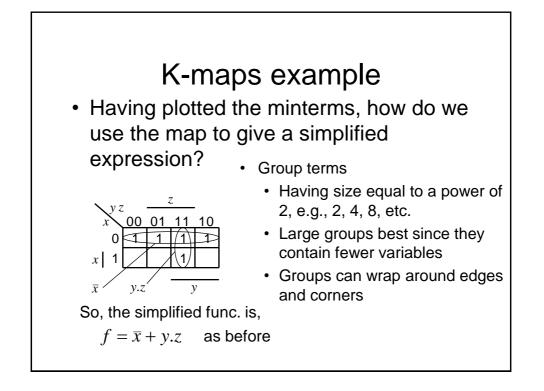

A Boolean function expressed as the ORing of ANDed variables (not necessarily minterms) is often said to be in Sum of Products (SOP) form, e.g.,

$f = \overline{x} + y.z$  Note functions have the same truth table

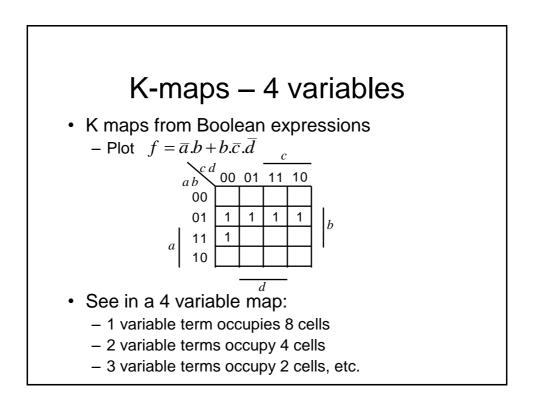

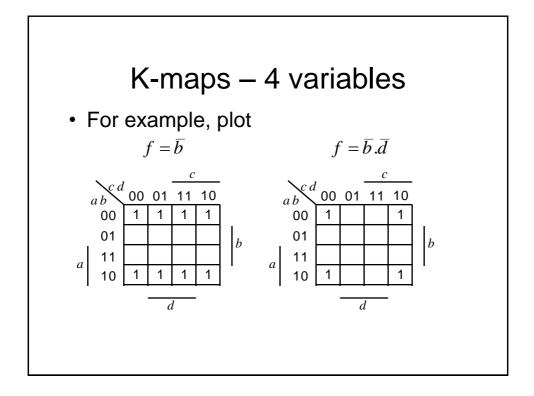

- Karnaugh Maps (or K-maps) are a powerful visual tool for carrying out simplification and manipulation of logical expressions having up to 5 variables

- The K-map is a rectangular array of cells

- Each possible state of the input variables corresponds uniquely to one of the cells

- The corresponding output state is written in each cell

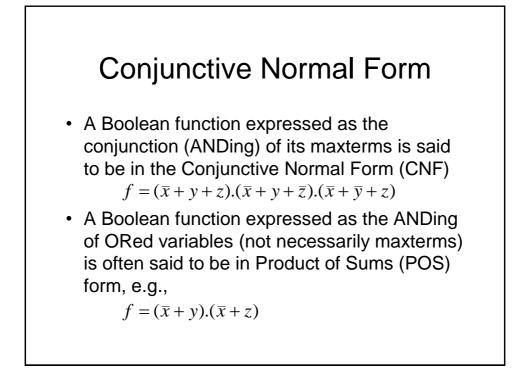

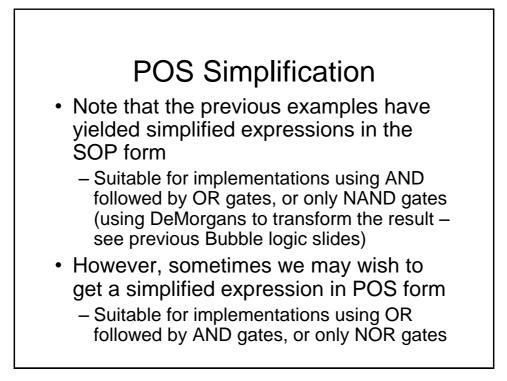

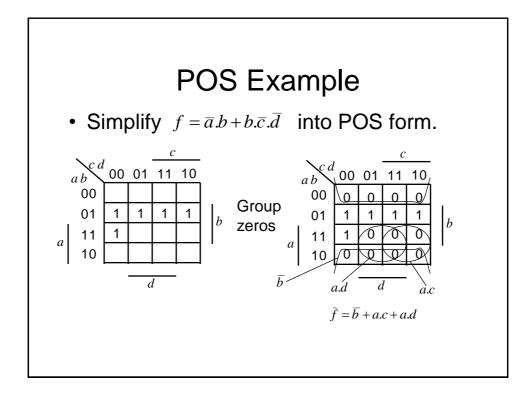

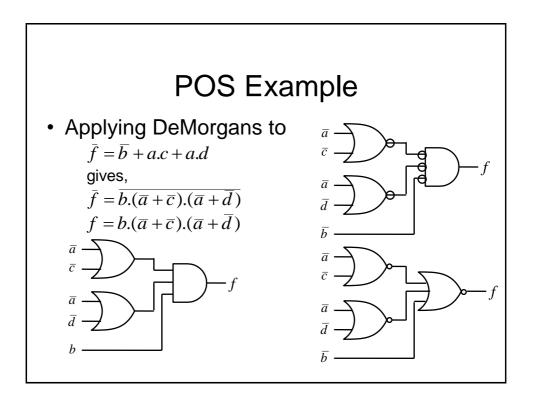

# Expression in POS form

- Apply DeMorgans and take complement, i.e.,  $\bar{f}$  is now in SOP form

- Fill in zeros in table, i.e., plot  $\bar{f}$

- Fill remaining cells with ones, i.e., plot *f*

- Simplify in usual way by grouping ones to simplify *f*

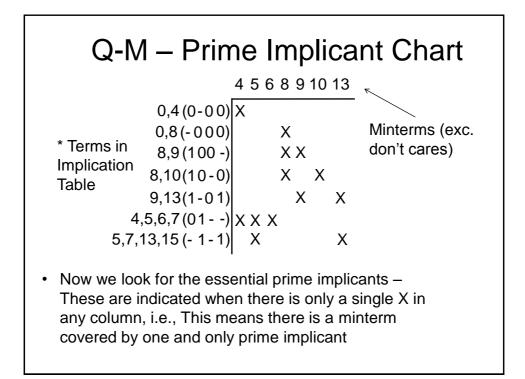

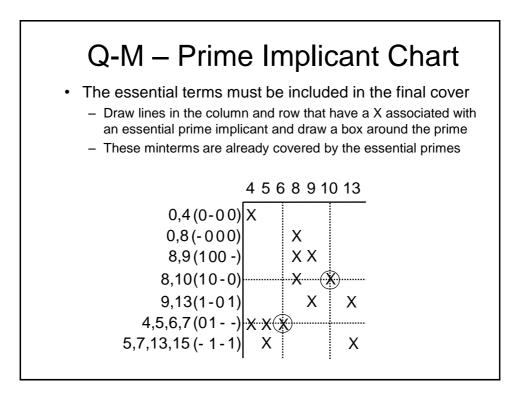

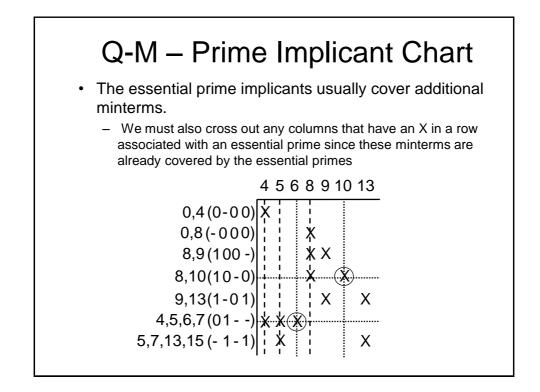

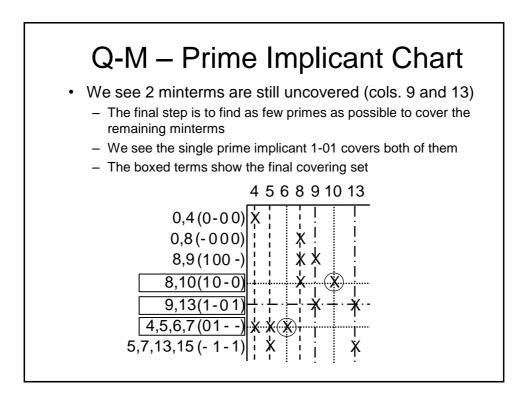

## Q-M Method

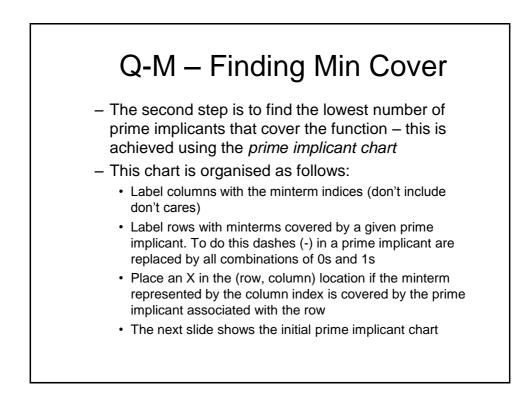

- The Q-M Method has 2 steps:

- First a table, known as the QM implication table, is used to find all the prime implicants;

- Next the minimum cover set is found using the prime implicant chart.

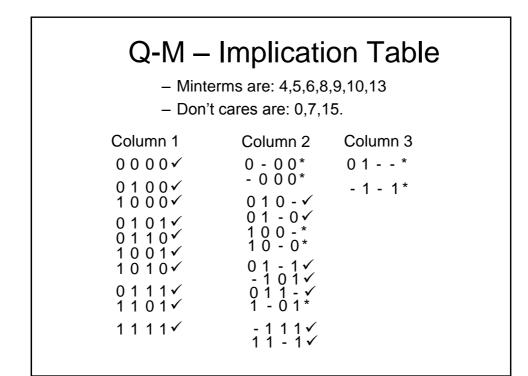

- We will use a 4 variable example to show the method in operation:

- Minterms are: 4,5,6,8,9,10,13

- Don't cares are: 0,7,15.

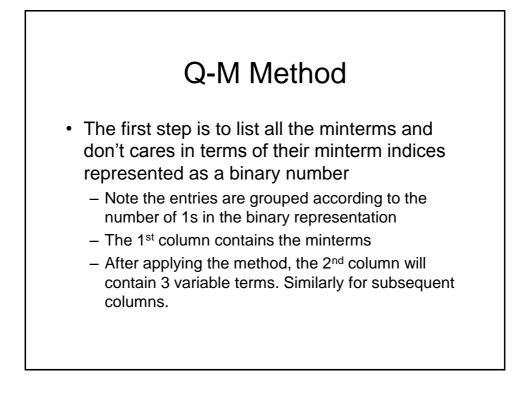

# Q-M Method

- The method begins by listing groups of minterms and don't cares in groups containing ascending numbers of 1s with a blank line between the groups

- Thus the first group has zero ones, the second group has a single 1 and the third has two 1s and so on

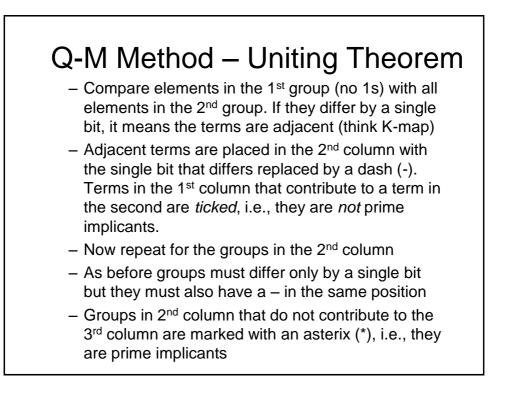

- We next apply the so called *uniting theorem* iteratively as follows

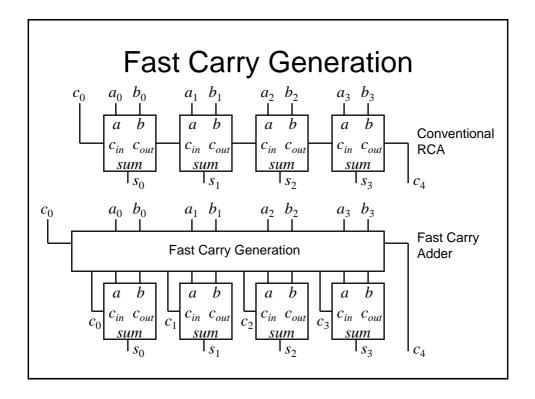

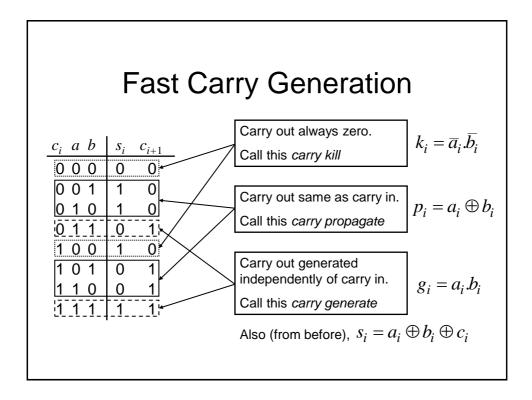

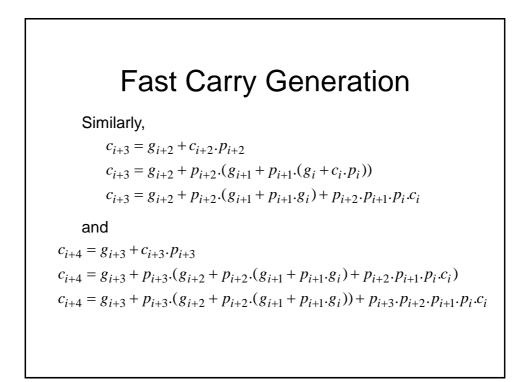

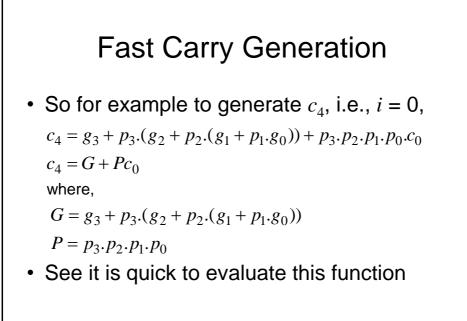

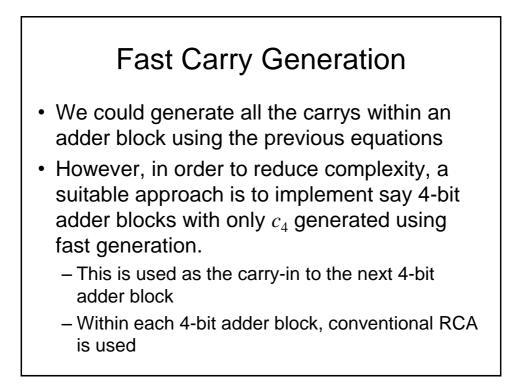

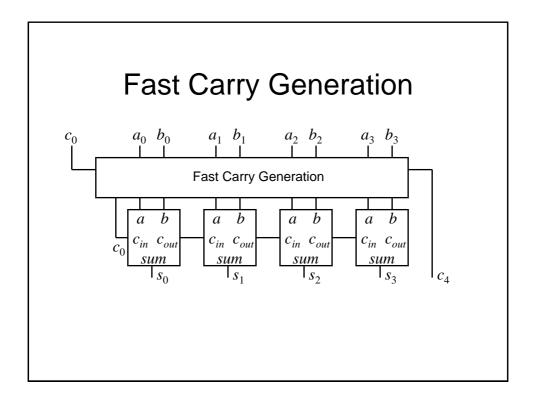

• Also from before we have,  $c_{i+1} = a_i.b_i + c_i.(a_i + b_i) \text{ or alternatively,}$   $c_{i+1} = a_i.b_i + c_i.(a_i \oplus b_i)$ Using previous expressions gives,  $c_{i+1} = g_i + c_i.p_i$ So,  $c_{i+2} = g_{i+1} + c_{i+1}.p_{i+1}$   $c_{i+2} = g_{i+1} + p_{i+1}.(g_i + c_i.p_i)$   $c_{i+2} = g_{i+1} + p_{i+1}.g_i + p_{i+1}.p_i.c_i$

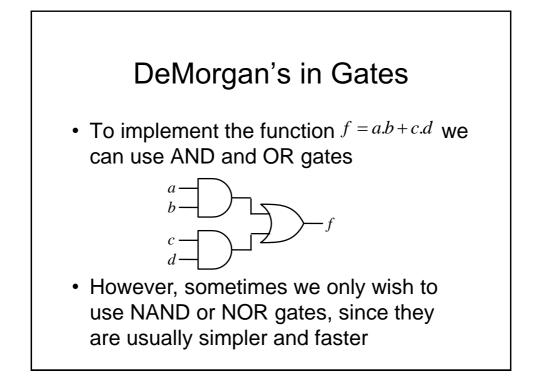

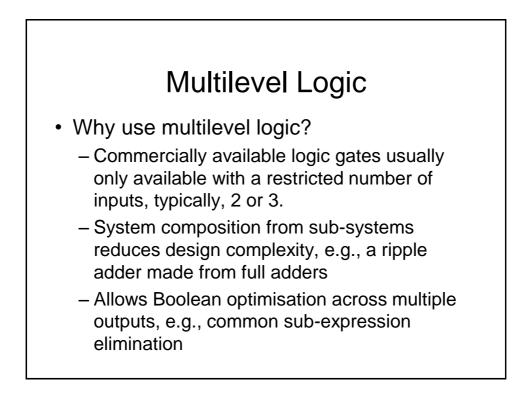

## Multilevel Logic

- We have seen previously how we can minimise Boolean expressions to yield so called '2-level' logic implementations, i.e., SOP (ANDed terms ORed together) or POS (ORed terms ANDed together)

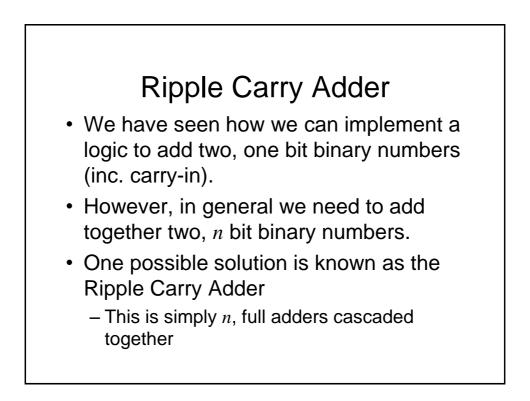

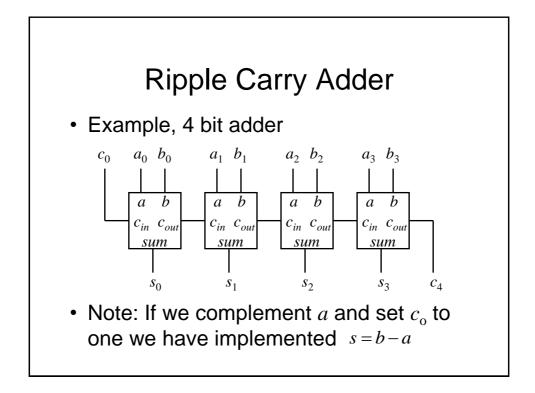

- Note also we have also seen an example of 'multilevel' logic, i.e., full adders cascaded to form a ripple carry adder – see we have more than 2 gates in cascade in the carry chain

## Gate Propagation Delay

- The cumulative delay owing to a number of gates in cascade can increase the time before the output of a combinational logic circuit becomes valid

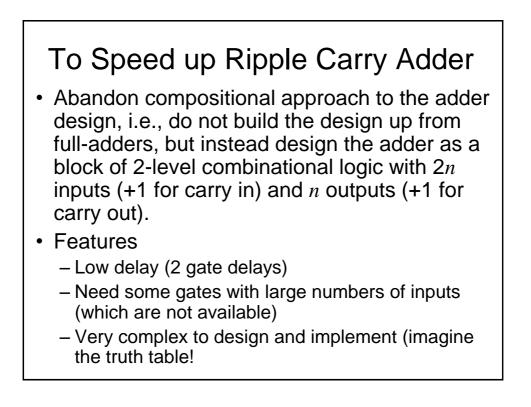

- For example, in the Ripple Carry Adder, the sum at its output will not be valid until any carry has 'rippled' through possibly every full adder in the chain – clearly the MSB will experience the greatest potential delay

# Hazards

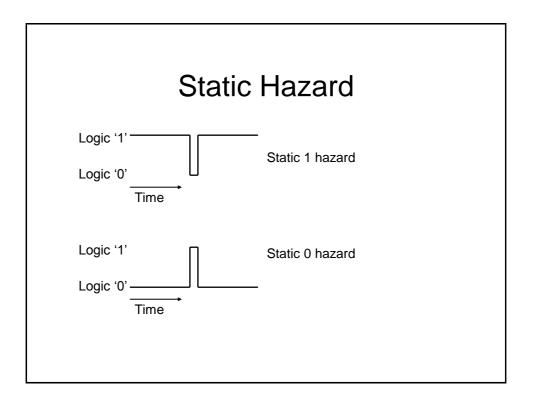

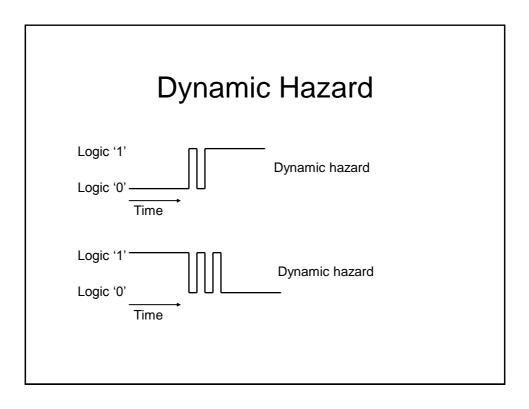

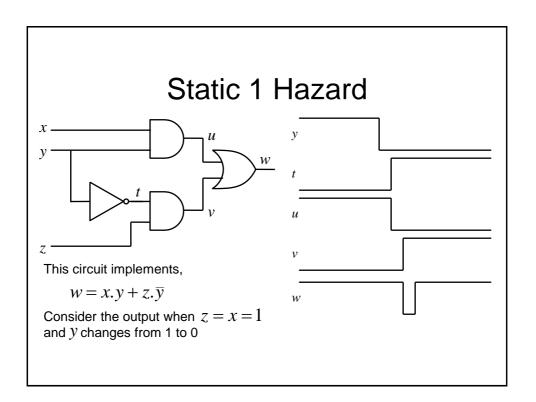

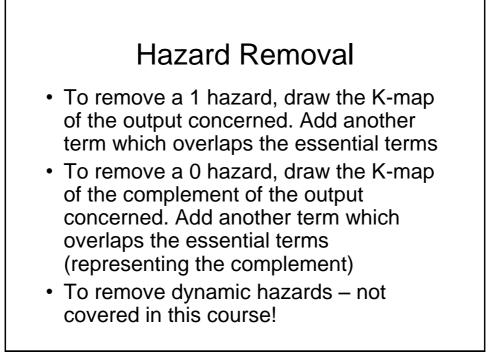

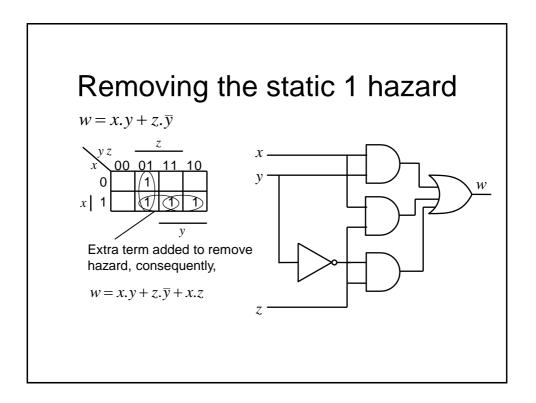

- Hazards are classified into two types, namely, static and dynamic

- Static Hazard The output undergoes a momentary transition when one input changes when it is supposed to remain unchanged

- Dynamic Hazard The output changes more than once when it is supposed to change just once

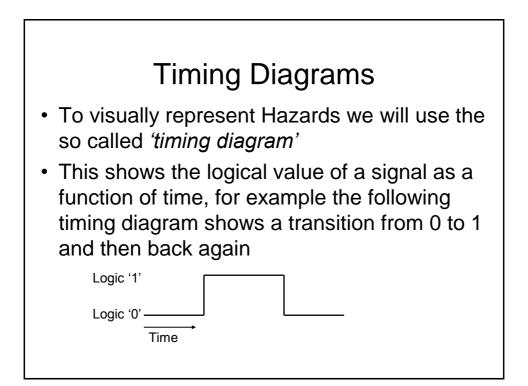

# **Timing Diagrams**

- Note that the timing diagram makes a number simplifying assumptions (to aid clarity) compared with a diagram which accurately shows the actual voltage against time

- The signal only has 2 levels. In reality the signal may well look more 'wobbly' owing to electrical noise pick-up etc.

- The transitions between logic levels takes place instantaneously, in reality this will take a finite time.

## Beyond Simple Logic Gates

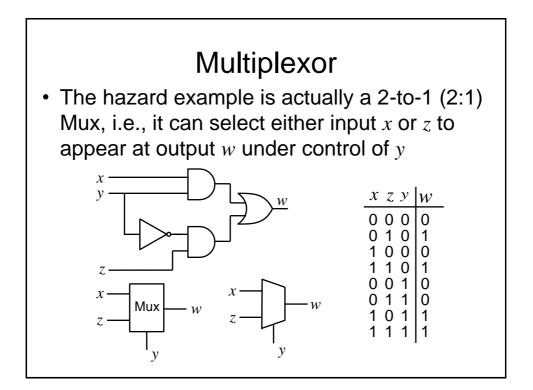

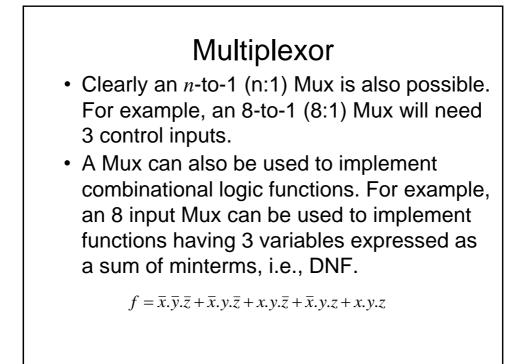

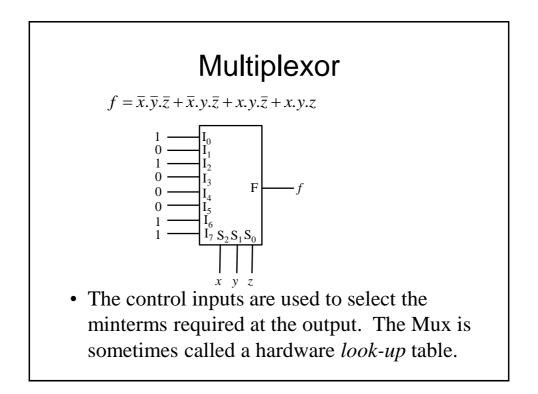

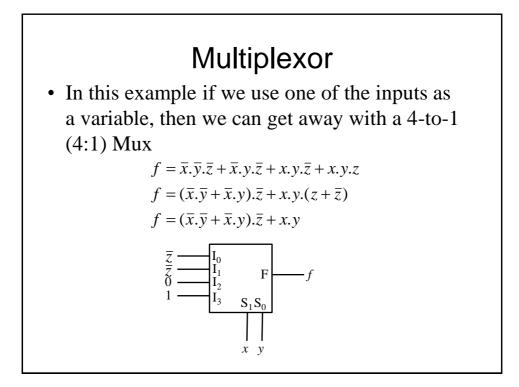

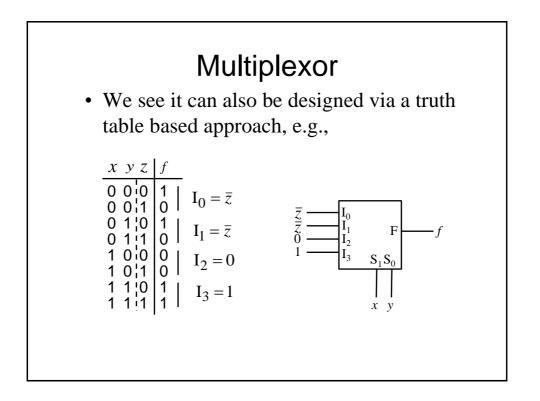

Multiplexor (Mux)/selector – chooses

of many inputs to steer to its single

output under the direction of control

inputs, e.g., if the input to a circuit can

come from several places a Mux is one

way to funnel the multiple sources

selectively to the single ouput.

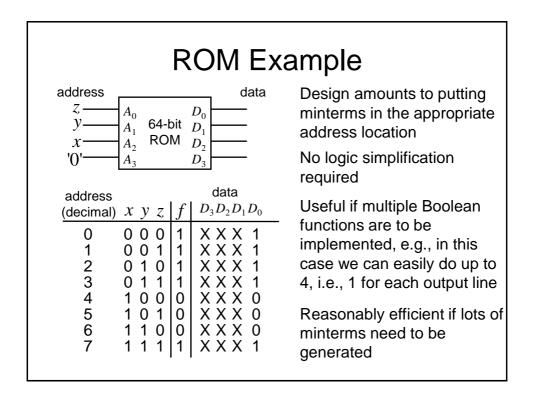

- Can be quite inefficient, i.e., become large in size with only a few non-zero entries, if the number of minterms in the function to be implemented is quite small

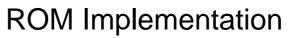

- Devices which can overcome these problems are known as programmable logic array (PLA)

- In PLAs, only the required minterms are generated using a separate AND plane. The outputs from this plane are ORed together in a separate OR plane to produce the final output

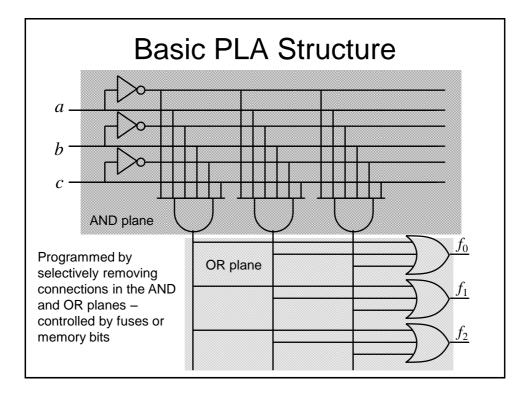

## Other PLA Style Structures

- In PLAs, only the required minterms are generated using a separate AND plane. Output from this plane are available to all OR gates to give the final output

- A modified structure known as Programmable Array Logic (PAL) does not have a programmable OR array and so outputs from the AND array can not be shared among the OR gates to give the final outputs.

- This simplifies the structure, but at the cost of lower efficiency

#### **Other Memory Devices**

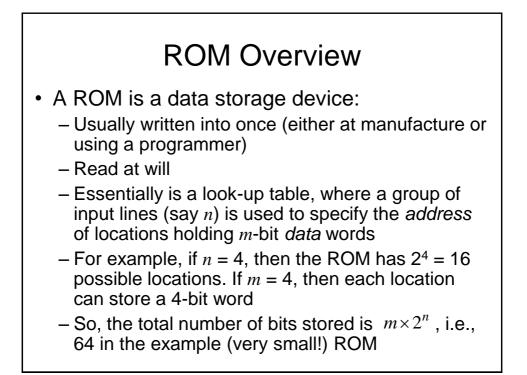

- Non-volatile storage is offered by ROMs (and some other memory technologies, e.g., FLASH), i.e., the data remains intact, even when the power supply is removed

- Volatile storage is offered by Static Random Access Memory (SRAM) technology

- Data can be written into and read out of the SRAM, but is lost once power is removed

#### **Memory Application**

- Memory devices are often used in computer systems

- The central processing unit (CPU) often makes use of busses (a bunch of wires in parallel) to access external memory devices

- The *address bus* is used to specify the memory location that is being read or written and the data bus conveys the data too and from that location

- So, more than one memory device will often be connected to the same data bus

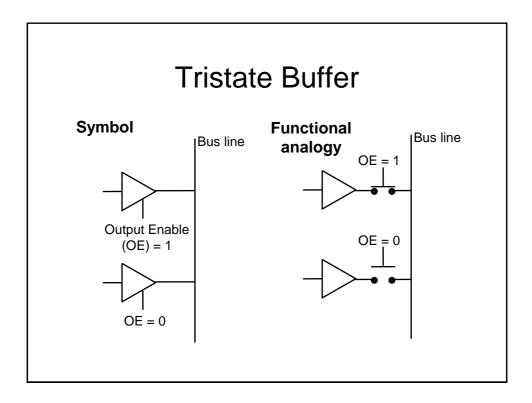

## **Bus Contention**

- In this case, if the output from the data pin of one memory was a 0 and the output from the corresponding data pin of another memory was a 1, the data on that line of the data bus would be invalid

- So, how do we arrange for the data from multiple memories to be connected to the some bus wires?