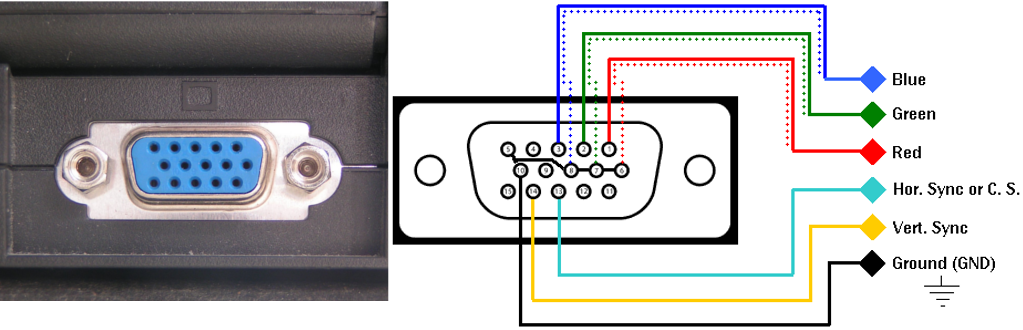

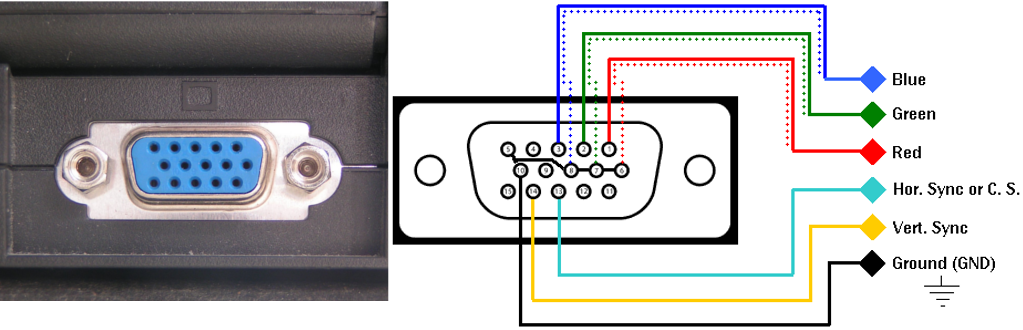

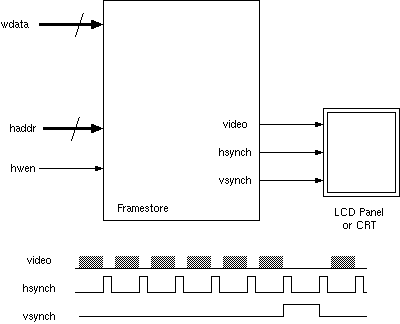

Super video graphics adaptor (SVGA) analog framestore output port.

|

reg [2:0] framestore[32767:0];

reg [7:0] hptr, vptr;

output reg [2:0] rgb_video;

output reg hsynch, vsynch;

always @(posedge clk) begin

hptr <= (hsynch) ? 0: hptr + 1;

hsynch <= (hptr >= 230)

if (hsynch) vptr <= (vsynch) ? 0: vptr + 1;

vsynch <= (vptr == 110)

if (hwen) framestore[haddr]<= wdata[2:0];

/*else*/ rgb_video <= framestore[{vptr[6:0], hptr}];

end

|

Alternate design uses main system RAM instead of a private SRAM (need a small staging FIFO).

The pixel clock rate, H/W dimensions and synch pulse widths are normally programmable.

The RAM cannot be read. Moreover it has two address ports: re-code with one arbitrated port ?

| 40: (C) 2008-16, DJ Greaves, University of Cambridge, Computer Laboratory. |