## **Multicore Semantics and Programming**

#### Peter Sewell Tim Harris

#### University of Cambridge Oracle

October – November, 2015

#### **These Lectures**

Part 1: Multicore Semantics: the concurrency of multiprocessors and programming languages

What concurrency behaviour can you rely on? How can we specify it precisely in semantic models? Linking to usage, microarchitecture, experiment, and semantics. x86, IBM POWER, ARM, Java, C/C++11

Part 2: Multicore Programming: Concurrent algorithms (Tim Harris, Oracle)

Concurrent programming: simple algorithms, correctness criteria, advanced synchronisation patterns, transactional memory.

#### **Multicore Semantics**

- Introduction

- Sequential Consistency

- x86 and the x86-TSO abstract machine

- x86 spinlock example

- Architectures

- Tests and Testing

# Implementing Simple Mutual Exclusion, Naively

| Initial state: x=0 and y=0               |                                          |

|------------------------------------------|------------------------------------------|

| Thread 0                                 | Thread 1                                 |

| x=1                                      | y=1                                      |

| <pre>if (y==0) {critical section }</pre> | <pre>if (x==0) {critical section }</pre> |

# Implementing Simple Mutual Exclusion, Naively

| Initial state: x=0 and y=0               |                                          |

|------------------------------------------|------------------------------------------|

| Thread 0                                 | Thread 1                                 |

| x=1                                      | y=1                                      |

| <pre>if (y==0) {critical section }</pre> | <pre>if (x==0) {critical section }</pre> |

repeated use?

thread symmetry (same code on each thread)?

performance?

fairness?

deadlock, global lock ordering, compositionality?

# Let's Try...

./runSB.sh

#### **Fundamental Question**

What is the *behaviour of memory*?

...at the programmer abstraction

...when observed by concurrent code

The abstraction of a *memory* goes back some time...

The calculating part of the engine may be divided into two portions

1st The Mill in which all operations are performed

2nd The Store in which all the numbers are originally placed and to which the numbers computed by the engine are returned.

[Dec 1837, On the Mathematical Powers of the Calculating Engine, Charles Babbage]

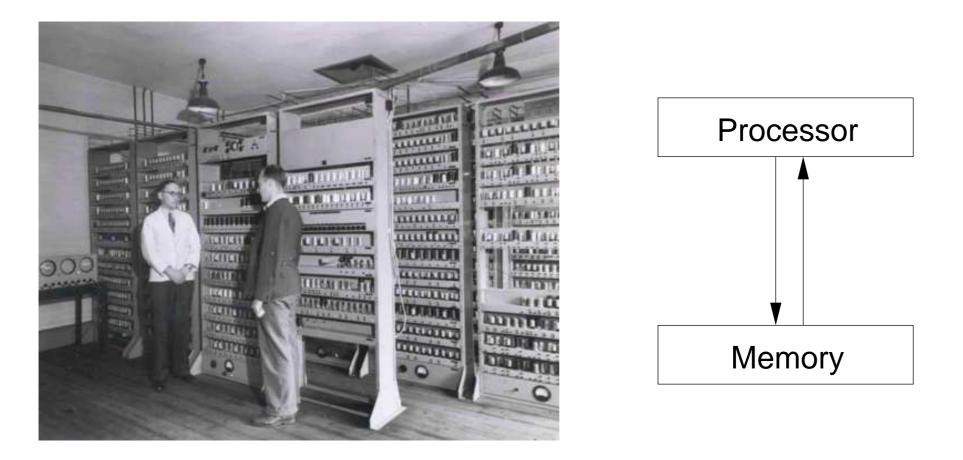

# The Golden Age, (1837–) 1945–1962

#### 1962: First(?) Multiprocessor

#### BURROUGHS D825, 1962

'Outstanding features include truly modular hardware with parallel processing throughout'

FUTURE PLANS The complement of compiling languages is to be expanded.''

#### ... with Shared-Memory Concurrency

#### Multiprocessors, 1962-now

Niche multiprocessors since 1962

IBM System 370/158MP in 1972

Mass-market since 2005 (Intel Core 2 Duo).

# Multiprocessors, 2015

Intel Xeon E7-8895 v3 36 hardware threads

**ARM**<sup>\*</sup> Commonly 4 or 8 hardware threads.

IBM Power 8 server (up to 1536 hardware threads)

Oracle Sparc, Intel Itanium

# Why now?

Exponential increases in transistor counts continuing — but not per-core performance

- energy efficiency (computation per Watt)

- Imits of instruction-level parallelism

Concurrency finally mainstream — but how to understand, design, and program concurrent systems? Still very hard.

#### Concurrency everywhere

At many scales:

- intra-core

- GPU

- datacenter-scale

- internet-scale

explicit message-passing vs shared memory abstractions

# Sequential Consistency

# Our first model: Sequential Consistency

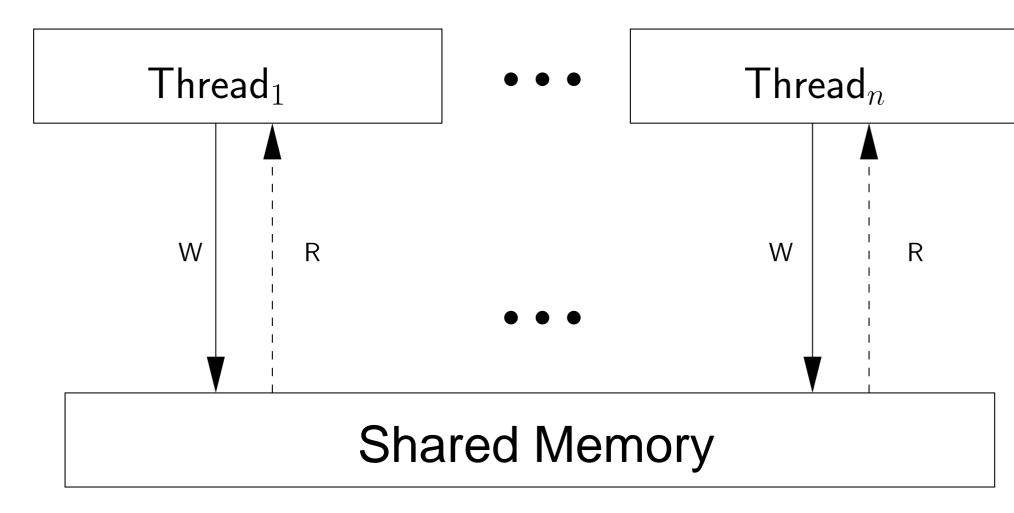

Multiple threads acting on a *sequentially consistent* (SC) shared memory:

the result of any execution is the same as if the operations of all the processors were executed in some sequential order, respecting the order specified by the program [Lamport, 1979]

# Defining an SC Semantics: SC memory

Define the state of an SC *memory* M to be a function from addresses x to integers n, with  $M_0$  mapping all to 0. Let t range over thread ids.

Describe the interactions between memory and threads with *labels*:

| $label, \ l$ | ::= | label      |                       |

|--------------|-----|------------|-----------------------|

|              |     | t:Wx=n     | write                 |

|              |     | t: R x = n | read                  |

|              |     | $t{:}	au$  | internal action (tau) |

Define the behaviour of memory as a labelled transition system (LTS): the least set of (M, l, M') triples satisfying these rules.

$M \xrightarrow{l} M'$  memory M does l to become M'

$$\frac{M(x) = n}{M \xrightarrow{t: \mathbb{R} x = n} M} \quad \mathsf{M}_{\mathsf{READ}}$$

M\_write

$\overline{M \xrightarrow{t: \mathsf{W} \, x = n} M \oplus (x \mapsto n)}$

#### SC, said differently

In any trace  $\vec{l} \in \text{traces}(M_0)$  of  $M_0$ , i.e. any list of read and write events:

$l_1, l_2, \ldots l_k$

such that there are some  $M_1, \ldots, M_k$  with

$M_0 \xrightarrow{l_1} M_1 \xrightarrow{l_2} M_2 \dots M_k,$

each read reads from the value of the most recent preceding write to the same address, or from the initial state if there is no such write.

#### SC, said differently

Making that precise, define an alternative SC memory state *L* to be a list of labels, most recent at the head. Define *lookup* by:

lookup x nil=0initial state valuelookup x (t:W x'=n)::L=nif x = x'lookup x l::L=lookup x Lotherwise

$L \xrightarrow{l} L'$  list memory L does l to become L'

$$\frac{lookup \ x \ L = n}{L \xrightarrow{t:\mathbb{R} \ x=n}} (t:\mathbb{R} \ x=n)::L} \quad \mathsf{LREAD}$$

$$\frac{L \xrightarrow{t:\mathbb{W} \ x=n}}{L \xrightarrow{t:\mathbb{W} \ x=n}} (t:\mathbb{W} \ x=n)::L} \quad \mathsf{LWRITE}$$

**Theorem 1 (?)**  $M_0$  and *nil* have the same traces

#### Extensional behaviour vs intensional structure

Extensionally, these models have the same behaviour

Intensionally, they have rather different structure – and neither is structured anything like a real hardware implementation.

In defining a model, we're principally concerned with the extensional behaviour: we want to precisely describe the set of allowed behaviours, as clearly as possible. But (see later) sometimes the intensional structure matters too, and we may also care about computability, performance, provability,...

#### SC, glued onto a tiny PL semantics

In those memory models:

- the events within the trace of each thread were implicitly presumed to be ordered consistently with the program order (a control-flow unfolding) of that thread, and

- the values of writes were implicity presumed to be consistent with the thread-local computation specified by the program.

To make these things precise, we can combine the memory model with a threadwise semantics for a tiny concurrent language....

# A Tiny Language: Design Choices

- A concurrent imperative language.

- Distinguish syntactically between (thread-local) "registers" and "memory".

- Include explicit parallel threads, with thread ids.

- Define an operational semantics that exposes the potential memory events (reads and writes of a value at a memory address) of a thread or process as labelled transitions; this lets us glue it on to an SC or TSO memory.

- Keep the register behaviour internal. Use an explicit register state rather than substitution to highlight the relationship to the memory semantics.

- Otherwise, as simple as possible: just enough computational power to write litmus tests (no loops, no thread creation,

#### A Tiny Language: Example

Thread 0: x = 1;  $r_0 = y$ Thread 1: y = 1;  $r_1 = x$

and, with the initial register state  $R_0$  for each thread, and an initial SC memory state:

$$\langle t_0 : \langle x = 1; r_0 = y, R_0 \rangle | t_1 : \langle y = 1; r_1 = x, R_0 \rangle, \{x \mapsto 0, y \mapsto 0\} \rangle$$

# A Tiny Language: Syntax

| register, r       | register name  |

|-------------------|----------------|

| location, x, y, m | address        |

| integer, n        | integer        |

| $thread\_id, t$   | thread id      |

| $event\_id, a$    | event id       |

| k                 | index variable |

Let *R* range over *register states*, functions from register names *r* to integers *n*. Write  $R_0$  for the initial register state in which all registers hold 0.

expression, e::=register expression|ninteger literal|rregister value|e + e'plus

# A Tiny Language: Syntax

| $statement, \ s ::=$             | statement                |

|----------------------------------|--------------------------|

| r = e                            | compute register value   |

| r = x                            | read from memory         |

| x = e                            | write to memory          |

| if ( $e == n$ ) $s_1$ else $s_2$ | conditional              |

| $s_1$ ; $s_2$                    | sequential composition   |

| skip                             | empty statement          |

| thread, T ::=                    | thread                   |

| $  t: \langle s, R \rangle$      | id, statement, reg state |

| process, P ::=                   | process                  |

| $\mid T$                         | thread                   |

| P P'                             | parallel composition     |

That was just the syntax — now we'll be precise about the permitted behaviours of programs

#### Defining the Semantics: expressions

$$\begin{split} \overline{\langle e, R \rangle \to n} & \text{ in register state } R, e \text{ evalutes to } n \\ \hline \overline{\langle n, R \rangle \to n} & \text{E\_INT} \\ \hline \frac{R(r) = n}{\langle r, R \rangle \to n} & \text{E\_REG} \\ \hline \langle e, R \rangle \to n \\ \langle e', R \rangle \to n' \\ \hline \frac{n'' = n + n'}{\langle e + e', R \rangle \to n''} & \text{E\_PLUS} \end{split}$$

These expressions read the register state, but do not mutate registers or memory (as you can see just from the form of the judgement).

#### Defining the Semantics: threads (1/2)

$$T'$$

thread T does l to reach  $T'$

$$\begin{array}{l} \hline t: \langle r=x, \ R \rangle \xrightarrow{t:R \ x=n} \ t: \langle \text{skip}, \ R \oplus (r \mapsto n) \rangle \end{array} \quad \text{T_READ} \\ \hline \frac{\langle e, R \rangle \to n}{t: \langle x=e, \ R \rangle \xrightarrow{t:W \ x=n} \ t: \langle \text{skip}, \ R \rangle} \quad \text{T_WRITE} \\ \hline \frac{\langle e, R \rangle \to n}{t: \langle r=e, \ R \rangle \xrightarrow{t:\tau} \ t: \langle \text{skip}, \ R \oplus (r \mapsto n) \rangle} \end{array}$$

Register writes mutate the thread's register state R; memory reads and writes are exposed as labelled transitions, with read values unconstrained.

#### Defining the Semantics: threads (2/2)

$$\begin{array}{l} \overline{T \xrightarrow{l} T'} & \text{thread } T \text{ does } l \text{ to reach } T' \\ & \begin{pmatrix} \langle e, R \rangle \to n' \\ n = n' \\ \hline n = n' \\ \hline t: \langle \text{if } (e == n) \ s_1 \text{ else } s_2, R \rangle \xrightarrow{t:\tau} t: \langle s_1, R \rangle \\ & \downarrow (e, R) \to n' \\ n \neq n' \\ \hline t: \langle \text{if } (e == n) \ s_1 \text{ else } s_2, R \rangle \xrightarrow{t:\tau} t: \langle s_2, R \rangle \\ \hline \hline t: \langle \text{skip}; s_2, R \rangle \xrightarrow{t:\tau} t: \langle s_2, R \rangle \\ \hline \hline t: \langle s_1; R \rangle \xrightarrow{l} t: \langle s'_1, R' \rangle \\ \hline \hline t: \langle s_1; s_2, R \rangle \xrightarrow{l} t: \langle s'_1; s_2, R' \rangle \\ \end{array} \quad \begin{array}{l} \text{T_SEQ_CONTEXT} \end{array}$$

– p. 30

$t_0: \langle r_1 = r_0 + 1, R_0 \rangle \xrightarrow{t_0:\tau} t_0: \langle \texttt{skip}, R_0 \oplus (r_1 \mapsto 1) \rangle$

$$t_{0}: \langle r_{1} = r_{0} + 1, R_{0} \rangle \xrightarrow{t_{0}:\tau} t_{0}: \langle \text{skip}, R_{0} \oplus (r_{1} \mapsto 1) \rangle$$

$$t_{0}: \langle r_{0} = 3; r_{1} = r_{0}, R_{0} \rangle \xrightarrow{t_{0}:\tau} t_{0}: \langle \text{skip}; r_{1} = r_{0}, R_{0} \oplus (r_{0} \mapsto 3) \rangle$$

$$\xrightarrow{t_{0}:\tau} t_{0}: \langle r_{1} = r_{0}, R_{0} \oplus (r_{0} \mapsto 3) \rangle$$

$$\xrightarrow{t_{0}:\tau} t_{0}: \langle \text{skip}, R_{0} \oplus (r_{0} \mapsto 3, r_{1} \mapsto 3) \rangle$$

$$t_0: \langle r_1 = r_0 + 1, R_0 \rangle \xrightarrow{t_0:\tau} t_0: \langle \text{skip}, R_0 \oplus (r_1 \mapsto 1) \rangle$$

$$\begin{array}{rcl} t_0: \langle r_0 = 3 \,; \, r_1 = r_0, \, R_0 \rangle & \xrightarrow{t_0:\tau} & t_0: \langle \texttt{skip} \,; \, r_1 = r_0, \, R_0 \oplus (r_0 \mapsto 3) \rangle \\ & \xrightarrow{t_0:\tau} & t_0: \langle r_1 = r_0, \, R_0 \oplus (r_0 \mapsto 3) \rangle \\ & \xrightarrow{t_0:\tau} & t_0: \langle \texttt{skip}, \, R_0 \oplus (r_0 \mapsto 3, r_1 \mapsto 3) \rangle \end{array}$$

The transitions are those derivable by trees of instantiations of the rules, e.g.

$$\frac{\overline{\langle 3, R_0 \rangle \to 3}}{t_0 : \langle r_0 = 3, R_0 \rangle \xrightarrow{t_0:\tau} t_0 : \langle \text{skip}, R_0 \oplus (r_0 \mapsto 3) \rangle} \text{T_COMPUTE}$$

$$\frac{t_0 : \langle r_0 = 3; r_1 = r_0, R_0 \rangle \xrightarrow{t_0:\tau} t_0 : \langle \text{skip}; r_1 = r_0, R_0 \oplus (r_0 \mapsto 3) \rangle}{t_0 : \langle \text{skip}; r_1 = r_0, R_0 \oplus (r_0 \mapsto 3) \rangle} \text{T_SEQ_CONTEXT}$$

where that instance of  $T_SEQ_CONTEXT$  has instantiation:

$$t_0: \langle r_1 = r_0 + 1, R_0 \rangle \xrightarrow{t_0:\tau} t_0: \langle \texttt{skip}, R_0 \oplus (r_1 \mapsto 1) \rangle$$

$$\begin{array}{ccc} t_0: \langle r_0 = 3 \ ; \ r_1 = r_0, \ R_0 \rangle & \xrightarrow{t_0:\tau} & t_0: \langle \texttt{skip} \ ; \ r_1 = r_0, \ R_0 \oplus (r_0 \mapsto 3) \rangle \\ & \xrightarrow{t_0:\tau} & t_0: \langle r_1 = r_0, \ R_0 \oplus (r_0 \mapsto 3) \rangle \\ & \xrightarrow{t_0:\tau} & t_0: \langle \texttt{skip}, \ R_0 \oplus (r_0 \mapsto 3, r_1 \mapsto 3) \rangle \end{array}$$

$$t_0: \langle x=3, R_0 \rangle \xrightarrow{t_0: W x=3} t_0: \langle \text{skip}, R_0 \rangle$$

$$t_0: \langle r_1 = r_0 + 1, R_0 \rangle \xrightarrow{t_0:\tau} t_0: \langle \text{skip}, R_0 \oplus (r_1 \mapsto 1) \rangle$$

$$\begin{array}{rcl} t_0: \langle r_0 = 3 \,; \, r_1 = r_0, \, R_0 \rangle & \xrightarrow{t_0:\tau} & t_0: \langle \texttt{skip} \,; \, r_1 = r_0, \, R_0 \oplus (r_0 \mapsto 3) \rangle \\ & \xrightarrow{t_0:\tau} & t_0: \langle r_1 = r_0, \, R_0 \oplus (r_0 \mapsto 3) \rangle \\ & \xrightarrow{t_0:\tau} & t_0: \langle \texttt{skip}, \, R_0 \oplus (r_0 \mapsto 3, r_1 \mapsto 3) \rangle \end{array}$$

$$t_0: \langle x=3, R_0 \rangle \xrightarrow{t_0: \mathsf{W} x=3} t_0: \langle \mathsf{skip}, R_0 \rangle$$

$$t_0: \langle r_0 = x, R_0 \rangle \xrightarrow{t_0: \mathbb{R} x = 7} t_0: \langle \text{skip}, R_0 \oplus (r_0 \mapsto 7) \rangle$$

$$t_0: \langle r_0 = x, R_0 \rangle \xrightarrow{t_0: \mathbb{R} x = 23} t_0: \langle \text{skip}, R_0 \oplus (r_0 \mapsto 23) \rangle$$

# Example thread transitions

$$t_0: \langle r_1 = r_0 + 1, R_0 \rangle \xrightarrow{t_0:\tau} t_0: \langle \texttt{skip}, R_0 \oplus (r_1 \mapsto 1) \rangle$$

$$\begin{array}{rcl} t_0: \langle r_0 = 3 \,; \, r_1 = r_0, \, R_0 \rangle & \xrightarrow{t_0:\tau} & t_0: \langle \texttt{skip} \,; \, r_1 = r_0, \, R_0 \oplus (r_0 \mapsto 3) \rangle \\ & \xrightarrow{t_0:\tau} & t_0: \langle r_1 = r_0, \, R_0 \oplus (r_0 \mapsto 3) \rangle \\ & \xrightarrow{t_0:\tau} & t_0: \langle \texttt{skip}, \, R_0 \oplus (r_0 \mapsto 3, r_1 \mapsto 3) \rangle \end{array}$$

$$t_0: \langle x = 3, R_0 \rangle \xrightarrow{t_0: \mathsf{W} x = 3} t_0: \langle \mathsf{skip}, R_0 \rangle$$

$$t_0: \langle r_0 = x, R_0 \rangle \xrightarrow{t_0: \mathbb{R} x = 7} t_0: \langle \text{skip}, R_0 \oplus (r_0 \mapsto 7) \rangle$$

$$t_0: \langle r_0 = x, R_0 \rangle \xrightarrow{t_0: \mathbb{R} x = 23} t_0: \langle \text{skip}, R_0 \oplus (r_0 \mapsto 23) \rangle$$

## Defining the Semantics: lifting to processes

Remember the process syntax:

| process, P ::= | process              |

|----------------|----------------------|

| $\mid T$       | thread               |

| P   P'         | parallel composition |

$P \xrightarrow{l} P'$  process *P* does *l* to become *P'*

$$\frac{T \xrightarrow{l} T'}{T \xrightarrow{l} T'} \quad \mathsf{P\_THREAD}$$

$$\frac{P_1 \stackrel{l}{\rightarrow} P'_1}{P_1 | P_2 \stackrel{l}{\rightarrow} P'_1 | P_2} \quad P\_PAR\_CONTEXT\_LEFT$$

$$\frac{P_2 \stackrel{l}{\rightarrow} P'_1 | P_2}{P_1 | P_2 \stackrel{l}{\rightarrow} P_1 | P'_2} \quad P\_PAR\_CONTEXT\_RIGHT$$

Free interleaving of the transitions of each thread.

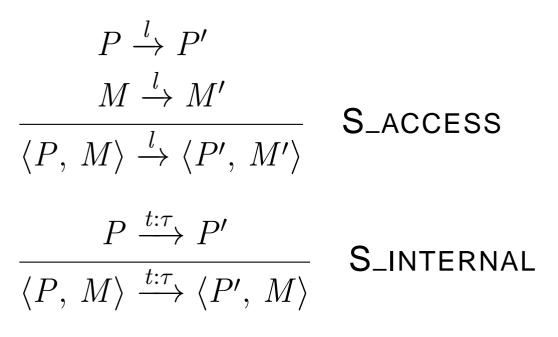

# Defining an SC Semantics: whole-system states

An SC system state  $S = \langle P, M \rangle$  is a pair of a process and an SC memory.

$S \xrightarrow{l} S'$  system *S* does *l* to become *S'*

The rules force synchronisation between the process and the memory, constraining the values of the process's read transitions to those the memory permits, and the memory's write transitions to those the process does (threads can also freely do internal transitions). -p.33

#### Example system transitions: SC Interleaving

All threads can read and write the shared memory.

Threads execute asynchronously – the semantics allows any interleaving of the thread transitions. Here there are two:

$$\begin{array}{c} \langle t_1: \langle x = 1, R_0 \rangle | \, t_2: \langle x = 2, R_0 \rangle, \, \{x \mapsto 0\} \rangle \\ \downarrow_{t_1: \forall x = 1} & \downarrow_{t_2: \forall x = 2} \\ \langle t_1: \langle \text{skip}, R_0 \rangle | \, t_2: \langle x = 2, R_0 \rangle, \, \{x \mapsto 1\} \rangle & \langle t_1: \langle x = 1, R_0 \rangle | \, t_2: \langle \text{skip}, R_0 \rangle, \, \{x \mapsto 2\} \rangle \\ \downarrow_{t_2: \forall x = 2} & \downarrow_{t_1: \forall x = 1} \\ \langle t_1: \langle \text{skip}, R_0 \rangle | \, t_2: \langle \text{skip}, R_0 \rangle, \, \{x \mapsto 2\} \rangle & \langle t_1: \langle \text{skip}, R_0 \rangle | \, t_2: \langle \text{skip}, R_0 \rangle, \, \{x \mapsto 1\} \rangle \end{array}$$

But each interleaving has a linear order of reads and writes to the memory. C.f. Lamport's

"the result of any execution is the same as if the operations of all the processors were executed in some sequential order, respecting the order specified by the program"

– p. 34

| Initial state: x=0 and y=0               |                                          |

|------------------------------------------|------------------------------------------|

| Thread 0                                 | Thread 1                                 |

| x=1                                      | y=1                                      |

| <pre>if (y==0) {critical section }</pre> | <pre>if (x==0) {critical section }</pre> |

| Initial state: x=0 and y=0                               |           |

|----------------------------------------------------------|-----------|

| Thread 0                                                 | Thread 1  |

| x = 1;                                                   | y = 1;    |

| $r_0 = y$                                                | $r_1 = x$ |

| Allowed? Thread 0's $r_0 = 0 \land$ Thread 1's $r_1 = 0$ |           |

| Initial state: x=0 and y=0                               |           |

|----------------------------------------------------------|-----------|

| Thread 0                                                 | Thread 1  |

| x = 1;                                                   | y=1 ;     |

| $r_0 = y$                                                | $r_1 = x$ |

| Allowed? Thread 0's $r_0 = 0 \land$ Thread 1's $r_1 = 0$ |           |

In other words: is there a trace

$$\begin{array}{l} \langle t_0 : \langle x = 1 ; r_0 = y, R_0 \rangle | t_1 : \langle y = 1 ; r_1 = x, R_0 \rangle, \{ x \mapsto 0, y \mapsto 0 \} \rangle \\ \xrightarrow{l_1} \dots \xrightarrow{ln} \\ \langle t_0 : \langle \text{skip}, R'_0 \rangle | t_1 : \langle \text{skip}, R'_1 \rangle, M' \rangle \end{array}$$

such that  $R'_0(r_0) = 0$  and  $R'_1(r_1) = 0$ ?

| Initial state: x=0 and y=0                               |           |

|----------------------------------------------------------|-----------|

| Thread 0                                                 | Thread 1  |

| x = 1;                                                   | y=1 ;     |

| $r_0 = y$                                                | $r_1 = x$ |

| Allowed? Thread 0's $r_0 = 0 \land$ Thread 1's $r_1 = 0$ |           |

In other words: is there a trace

$$\begin{array}{l} \langle t_0 : \langle x = 1 ; r_0 = y, R_0 \rangle | t_1 : \langle y = 1 ; r_1 = x, R_0 \rangle, \{ x \mapsto 0, y \mapsto 0 \} \rangle \\ \xrightarrow{l_1} \dots \xrightarrow{ln} \\ \langle t_0 : \langle \text{skip}, R'_0 \rangle | t_1 : \langle \text{skip}, R'_1 \rangle, M' \rangle \end{array}$$

such that  $R'_0(r_0) = 0$  and  $R'_1(r_1) = 0$ ?

In this semantics: no

| Initial state: x=0 and y=0                               |           |

|----------------------------------------------------------|-----------|

| Thread 0                                                 | Thread 1  |

| x = 1;                                                   | y=1 ;     |

| $r_0 = y$                                                | $r_1 = x$ |

| Allowed? Thread 0's $r_0 = 0 \land$ Thread 1's $r_1 = 0$ |           |

In other words: is there a trace

$$\begin{array}{l} \langle t_0 : \langle x = 1 ; r_0 = y, R_0 \rangle | t_1 : \langle y = 1 ; r_1 = x, R_0 \rangle, \{ x \mapsto 0, y \mapsto 0 \} \rangle \\ \xrightarrow{l_1} \dots \xrightarrow{ln} \\ \langle t_0 : \langle \text{skip}, R'_0 \rangle | t_1 : \langle \text{skip}, R'_1 \rangle, M' \rangle \end{array}$$

such that  $R'_0(r_0) = 0$  and  $R'_1(r_1) = 0$ ?

In this semantics: no

But on x86 hardware, we saw it!

# Options

- 1. the hardware is busted (either this instance or in general)

- 2. the program is bad

- 3. the model is wrong

# Options

- 1. the hardware is busted (either this instance or in general)

- 2. the program is bad

- 3. the model is wrong

#### SC is not a good model of x86 (or of Power, ARM, Sparc, Itanium...)

# Options

- 1. the hardware is busted (either this instance or in general)

- 2. the program is bad

- 3. the model is wrong

#### SC is not a good model of x86 (or of Power, ARM, Sparc, Itanium...)

Even though most work on verification, and many programmers, assume SC...

#### In SC, message passing should work as expected:

| Thread 1  | Thread 2        |

|-----------|-----------------|

| data = 1  |                 |

| ready = 1 | if (ready == 1) |

|           | print data      |

In SC, the program should only print nothing or 1, and on bare-metal x86 it does (not ARM/Power). What about Java/C?

| Thread 1  | Thread 2        |

|-----------|-----------------|

| data = 1  | int r1 = data   |

| ready = 1 | if (ready == 1) |

|           | print data      |

In SC, the program should only print nothing or 1, and on bare-metal x86 it does (not ARM/Power). What about Java/C?

It should be regardless of other reads.

| Thread 1  | Thread 2        |

|-----------|-----------------|

| data = 1  | int r1 = data   |

| ready = 1 | if (ready == 1) |

|           | print data      |

In SC, the program should only print nothing or 1, and on bare-metal x86 it does (not ARM/Power). What about Java/C?

But common subexpression elimination (e.g. in HotSpot) can rewrite

print data  $\implies$  print r1

| Thread 1  | Thread 2        |

|-----------|-----------------|

| data = 1  | int r1 = data   |

| ready = 1 | if (ready == 1) |

|           | print r1        |

In SC, the program should only print nothing or 1, and on bare-metal x86 it does (not ARM/Power). What about Java/C?

But common subexpression elimination (e.g. in HotSpot) can rewrite

print data  $\implies$  print r1

So the compiled program can print 0

# **Similar Options**

- 1. the hardware is busted

- 2. the compiler is busted

- 3. the program is bad

- 4. the model is wrong

## **Similar Options**

- 1. the hardware is busted

- 2. the compiler is busted

- 3. the program is bad

- 4. the model is wrong

#### SC is also not a good model of C, C++, Java,...

# **Similar Options**

- 1. the hardware is busted

- 2. the compiler is busted

- 3. the program is bad

- 4. the model is wrong

#### SC is also not a good model of C, C++, Java,...

Even though most work on verification, and many programmers, assume SC...

# What's going on? Relaxed Memory

Multiprocessors and compilers incorporate many performance optimisations

(hierarchies of cache, load and store buffers, speculative execution, cache protocols, common subexpression elimination, etc., etc.)

These are:

- unobservable by single-threaded code

- sometimes observable by concurrent code

Upshot: they provide only various *relaxed* (or *weakly consistent*) memory models, not sequentially consistent memory.

#### New problem?

No: IBM System 370/158MP in 1972, already non-SC

#### But still a research question!

The mainstream architectures and languages are key interfaces

...but it's been very unclear exactly how they behave.

More fundamentally: it's been (and in significant ways still is) unclear how we can specify that precisely.

As soon as we can do that, we can build above it: explanation, testing, emulation, static/dynamic analysis, model-checking, proof-based verification,....