# Digital Electronics Part I – Combinational and Sequential Logic

Dr. I. J. Wassell

### Aims

- · To familiarise students with

- Combinational logic circuits

- Sequential logic circuits

- How digital logic gates are built using transistors

- Design and build of digital logic systems

- At the end of the course you should

- Be able to design and construct simple digital electronic systems

- Be able to understand and apply Boolean logic and algebra – a core competence in Computer Science

- Be able to understand and build state machines

## Other Points

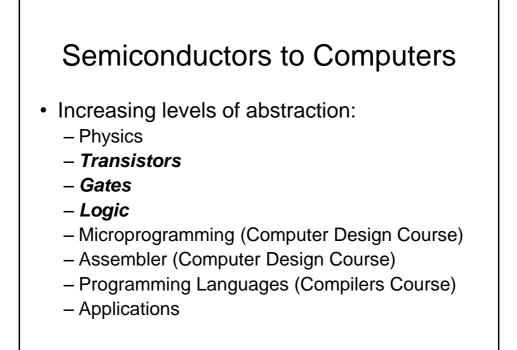

- This course is a prerequisite for

- Computer Design, ECAD and Architecture Practical Classes (Part IB)

- Comparative Architectures, System-on-Chip Design (Part II)

- Keep up with lab work and get it ticked.

- Have a go at supervision questions plus any others your supervisor sets.

- Remember to try questions from past papers

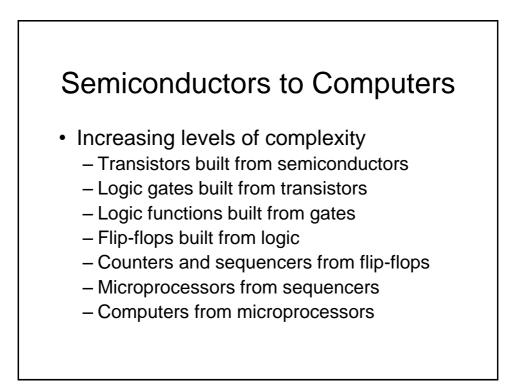

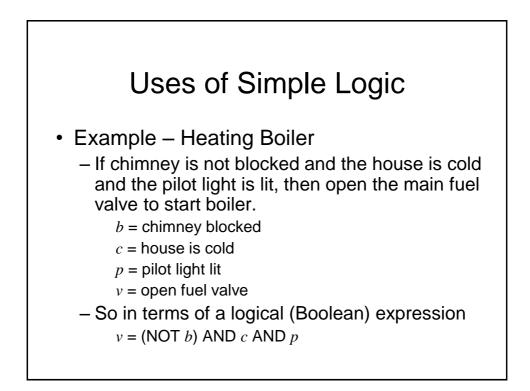

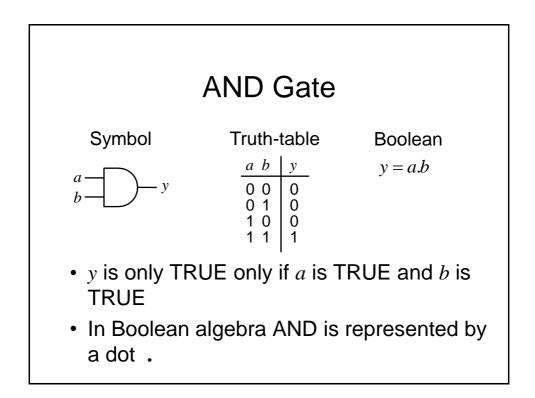

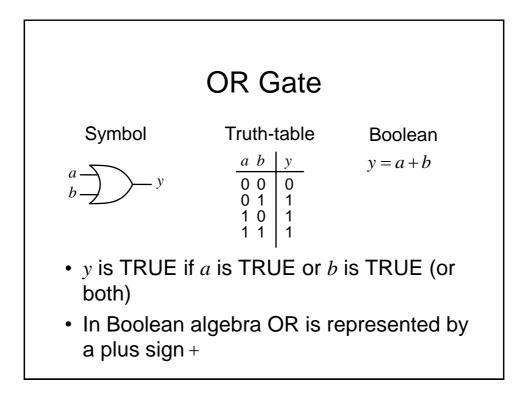

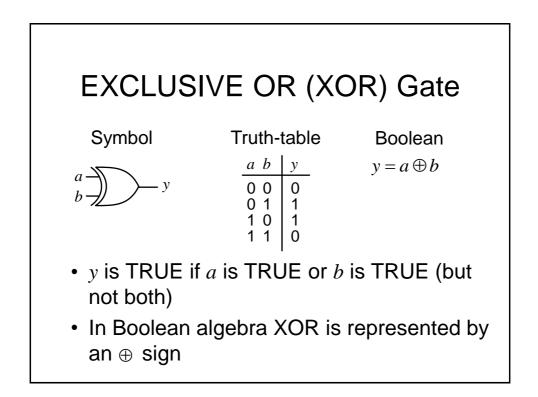

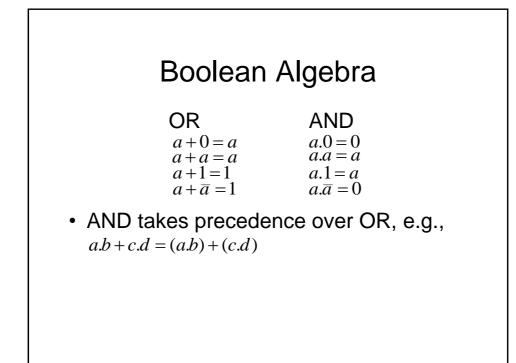

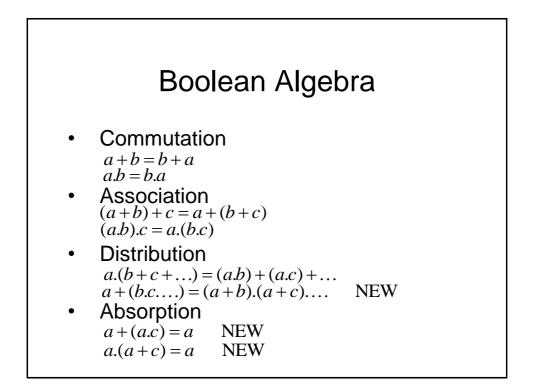

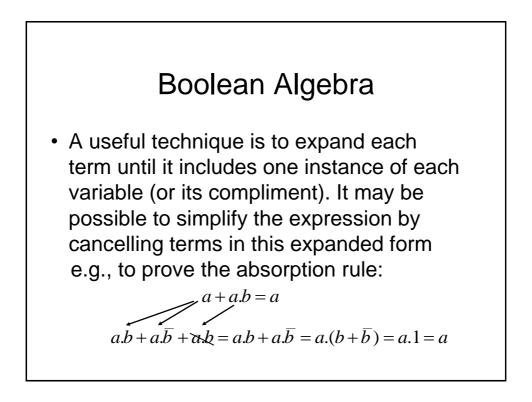

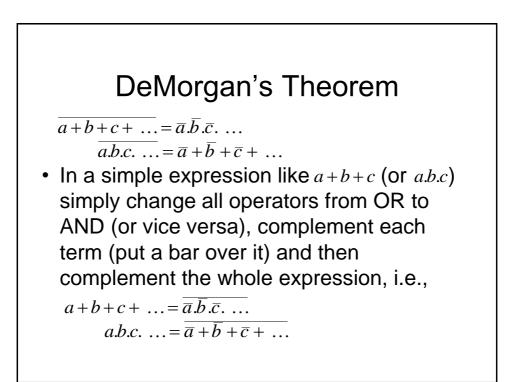

- We will introduce Boolean algebra and logic gates

- Logic gates are the building blocks of digital circuits

- In electronic circuits the two values can be represented by e.g.,

- High voltage for a 1

- Low voltage for a 0

- Note that since only 2 voltage levels are used, the circuits have greater immunity to electrical noise

## Logic Gates

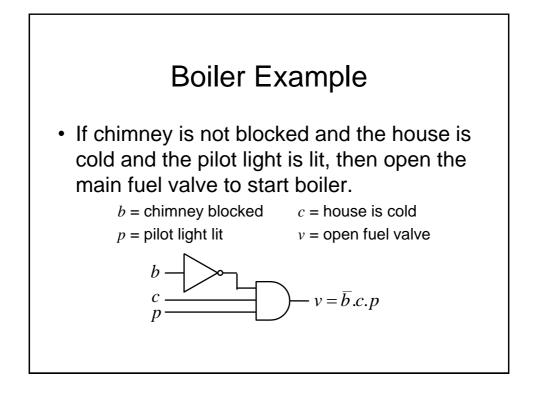

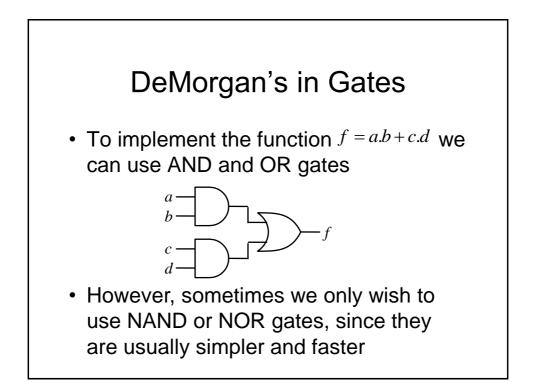

- Basic logic circuits with one or more inputs and one output are known as gates

- *Gates* are used as the building blocks in the design of more complex digital logic circuits

#### Boolean Algebra - Examples

Show  $a.(\overline{a}+b) = a.b$   $a.(\overline{a}+b) = a.\overline{a} + a.b = 0 + a.b = a.b$ Show  $a+(\overline{a}.b) = a+b$  $a+(\overline{a}.b) = (a+\overline{a}).(a+b) = 1.(a+b) = a+b$

### Boolean Algebra - Example

Simplify

$\begin{aligned} x.y + \overline{y}.z + x.z + x.y.z \\ x.y.z + x.y.\overline{z} + x.\overline{y}.z + \overline{x}.\overline{y}.z + x.y.z + x.\overline{y}.z + x.y.z \\ x.y.z + x.y.\overline{z} + x.\overline{y}.z + \overline{x}.\overline{y}.z \\ x.y.(z + \overline{z}) + \overline{y}.z.(x + \overline{x}) \\ x.y.1 + \overline{y}.z.1 \\ x.y + \overline{y}.z \end{aligned}$

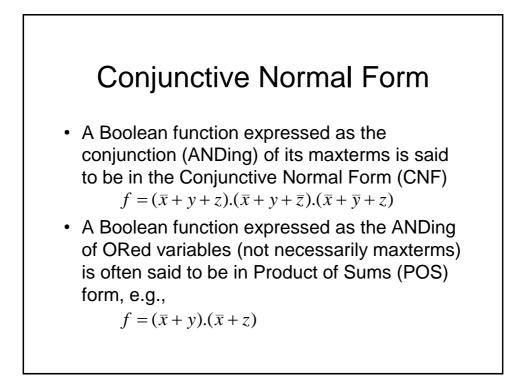

- A maxterm of *n* Boolean variables is the disjunction (ORing) of all the variables either in complemented or uncomplemented form.

- Referring back to the truth table for *f*, we can write,

$\overline{f} = x.\overline{y}.\overline{z} + x.\overline{y}.z + x.y.\overline{z}$

Applying De Morgan (and complementing) gives

$f = (\overline{x} + y + z).(\overline{x} + y + \overline{z}).(\overline{x} + \overline{y} + z)$

So it can be seen that the maxterms of f are effectively the minterms of  $\bar{f}$  with each variable complemented

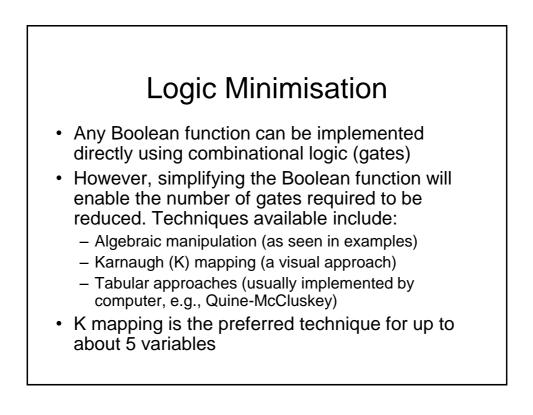

# Logic Simplification

As we have seen previously, Boolean algebra can be used to simplify logical expressions. This results in easier implementation

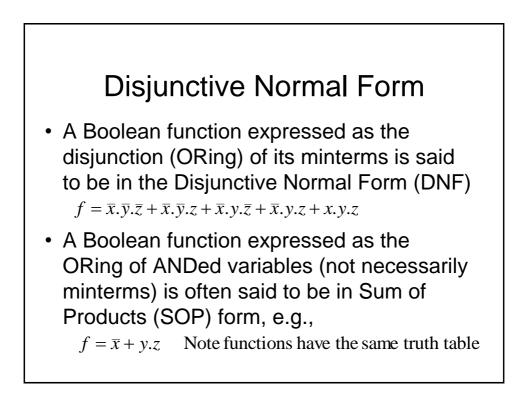

Note: The DNF and CNF forms are not simplified.

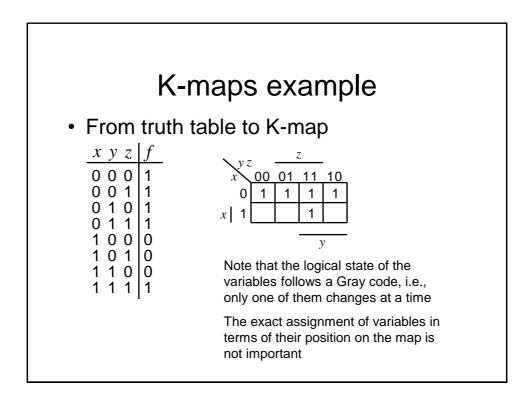

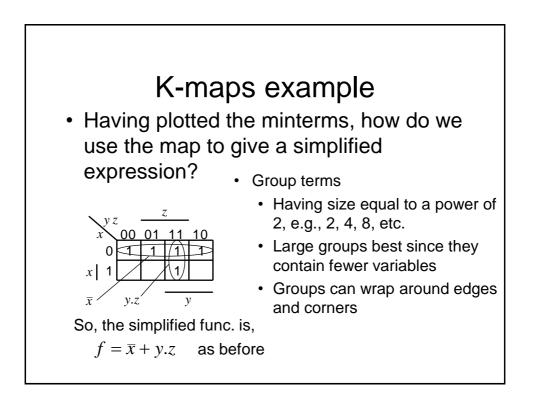

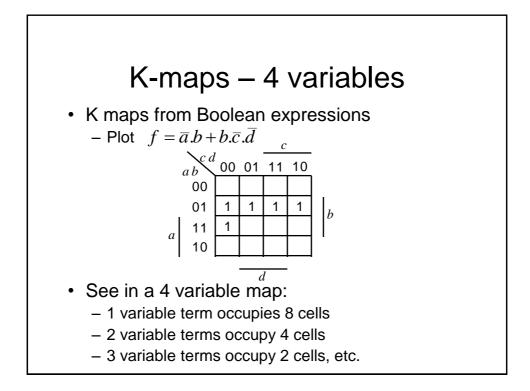

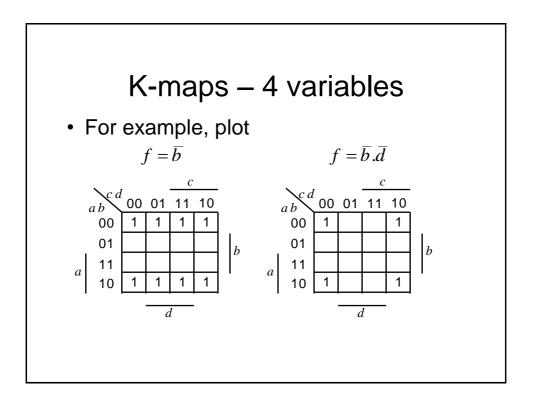

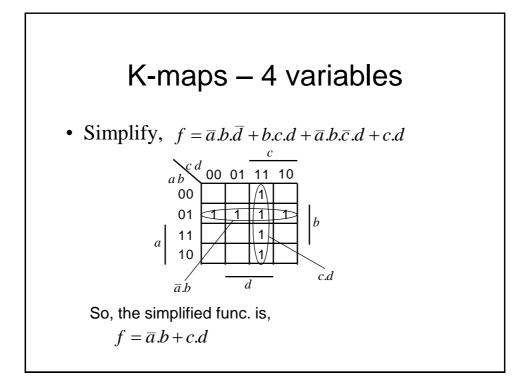

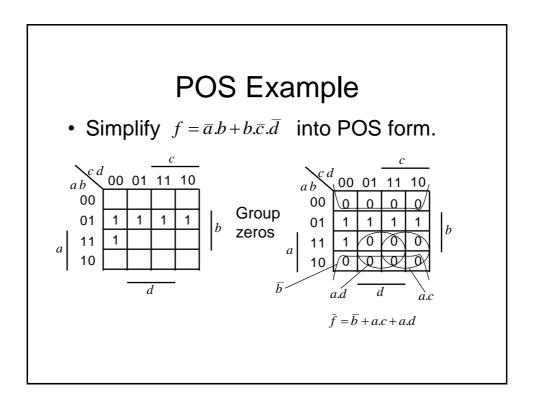

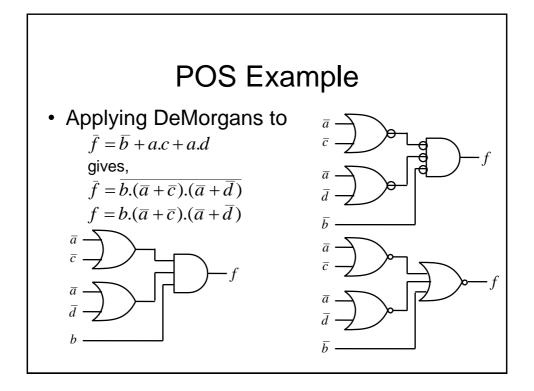

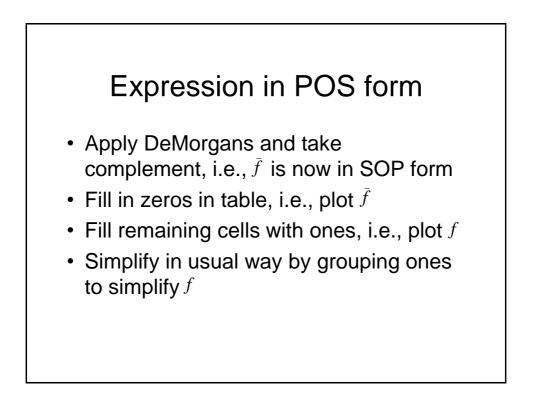

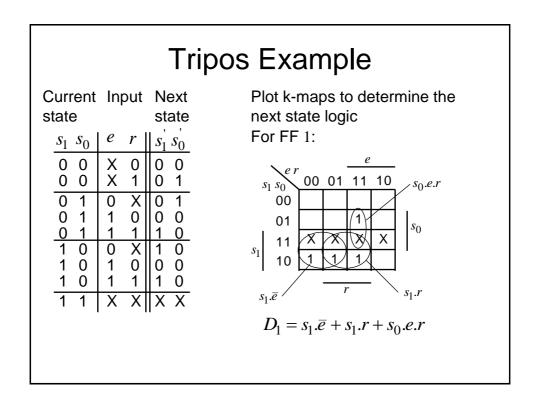

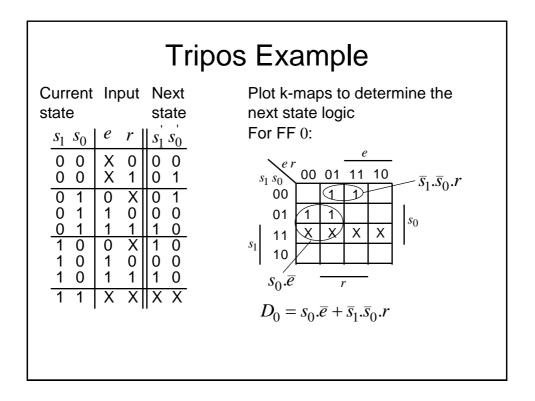

• However, it is often easier to use a technique known as Karnaugh mapping

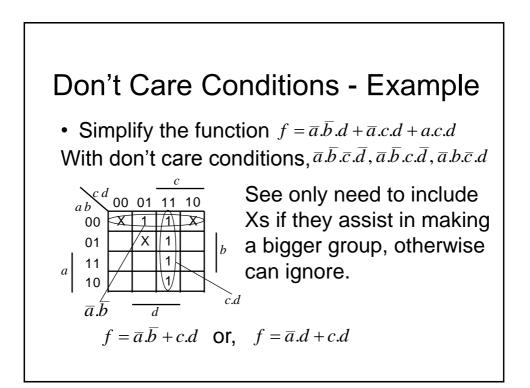

- Sometimes we do not care about the output value of a combinational logic circuit, i.e., if certain input combinations can never occur, then these are known as *don't care conditions*.

- In any simplification they may be treated as 0 or 1, depending upon which gives the simplest result.

- For example, in a K-map they are entered as Xs

## **Binary Adding Circuits**

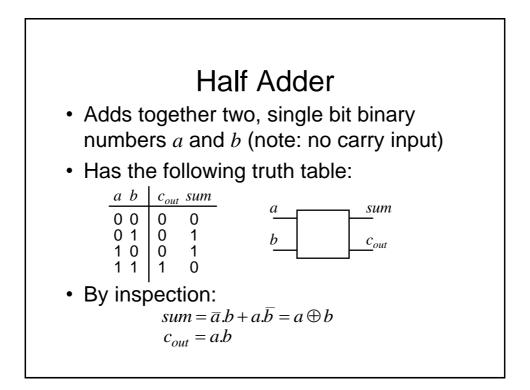

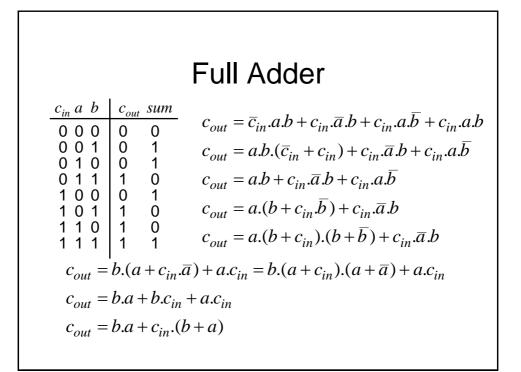

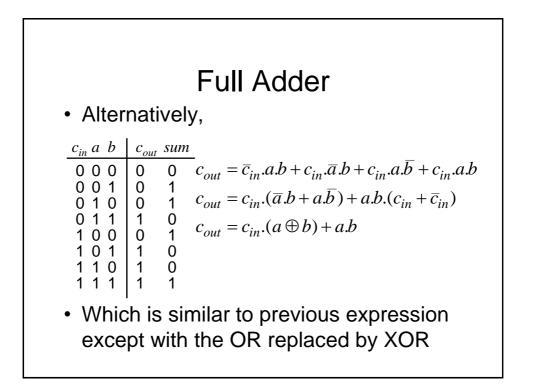

- We will now look at how binary addition may be implemented using combinational logic circuits. We will consider:

- Half adder

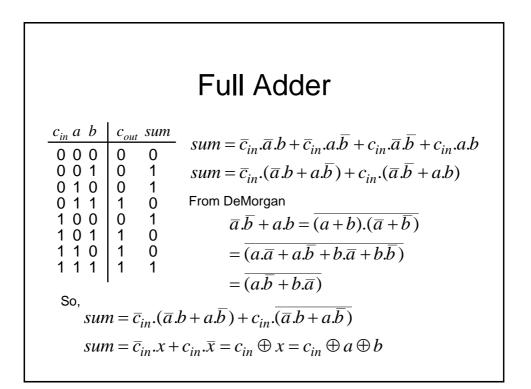

- Full adder

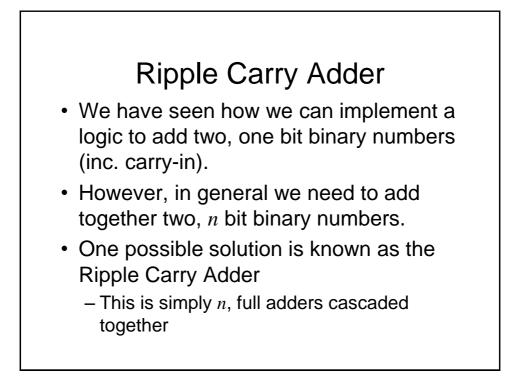

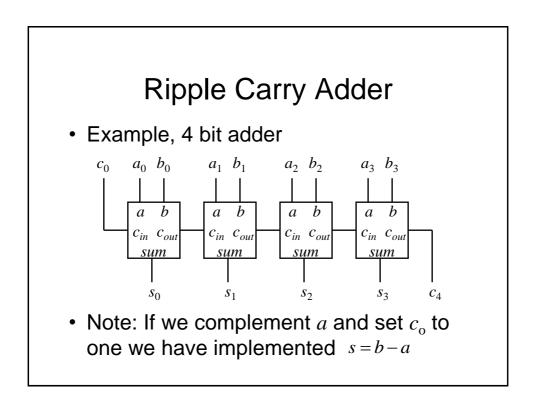

- Ripple carry adder

# To Speed up Ripple Carry Adder

- Abandon compositional approach to the adder design, i.e., do not build the design up from full-adders, but instead design the adder as a block of 2-level combinational logic with 2n inputs (+1 for carry in) and n outputs (+1 for carry out).

- Features

- Low delay (2 gate delays)

- Need some gates with large numbers of inputs (which are not available)

- Very complex to design and implement (imagine the truth table!

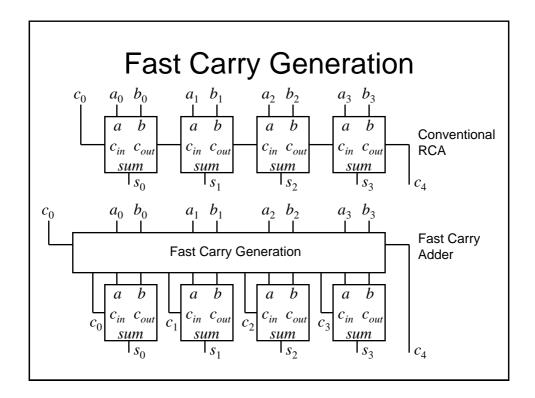

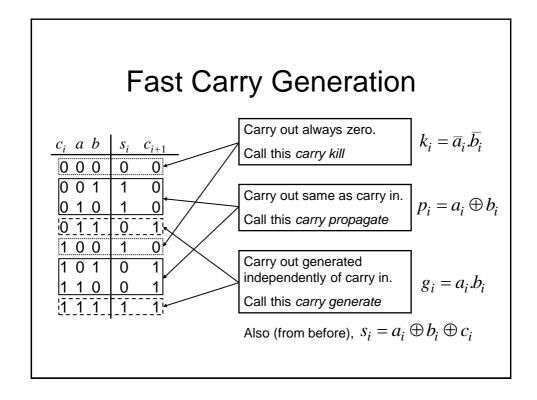

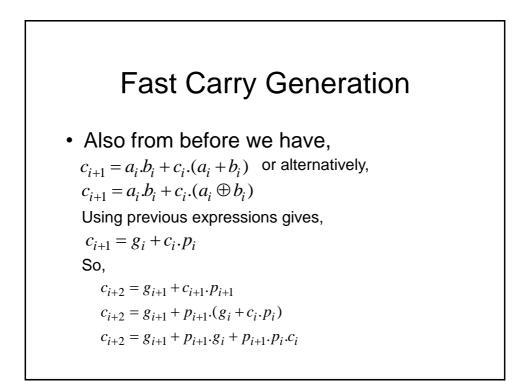

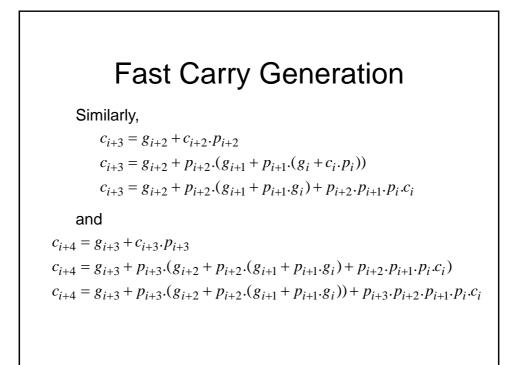

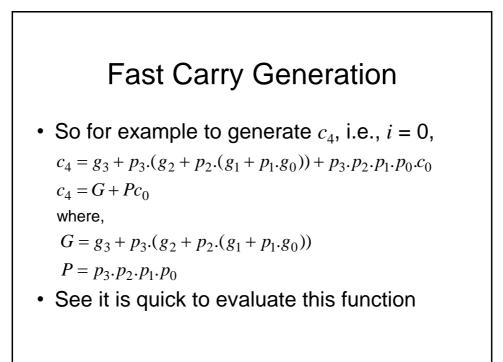

- We could generate all the carrys within an adder block using the previous equations

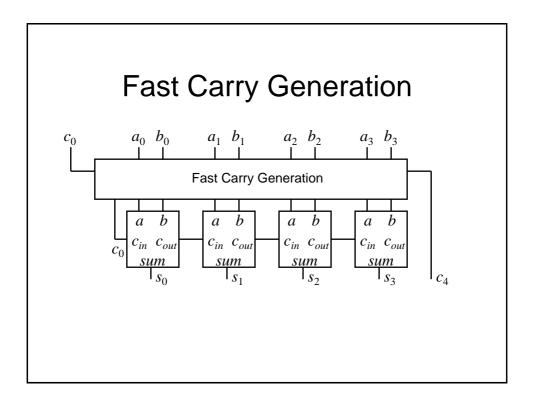

- However, in order to reduce complexity, a suitable approach is to implement say 4-bit adder blocks with only  $c_4$  generated using fast generation.

- This is used as the carry-in to the next 4-bit adder block

- Within each 4-bit adder block, conventional RCA is used

**Further Considerations**

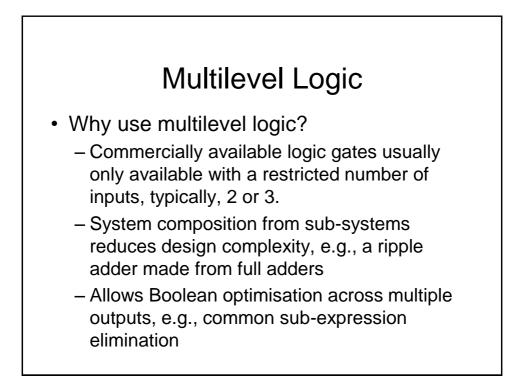

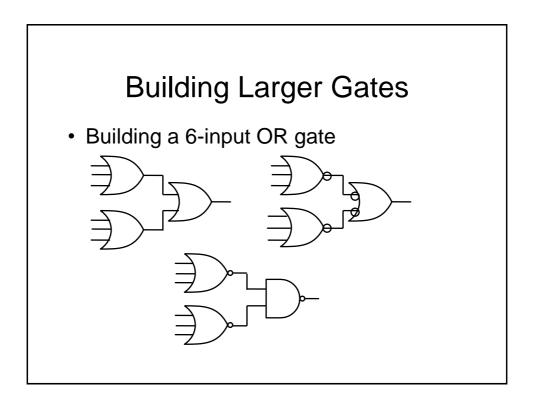

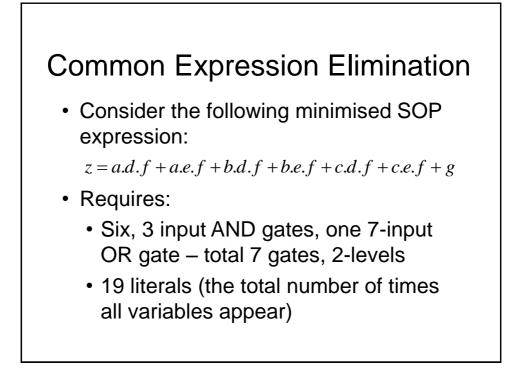

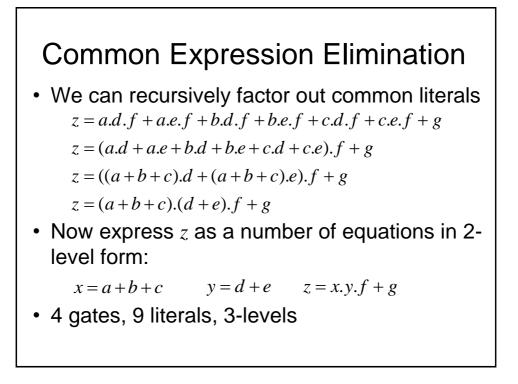

# Multilevel Logic

- We have seen previously how we can minimise Boolean expressions to yield so called '2-level' logic implementations, i.e., SOP (ANDed terms ORed together) or POS (ORed terms ANDed together)

- Note also we have also seen an example of 'multilevel' logic, i.e., full adders cascaded to form a ripple carry adder – see we have more than 2 gates in cascade in the carry chain

# Gate Propagation Delay

- So, multilevel logic can produce reductions in implementation complexity. What is the downside?

- We need to remember that the logic gates are implemented using electronic components (essentially transistors) which have a finite switching speed.

- Consequently, there will be a finite delay before the output of a gate responds to a change in its inputs – propagation delay

## Gate Propagation Delay

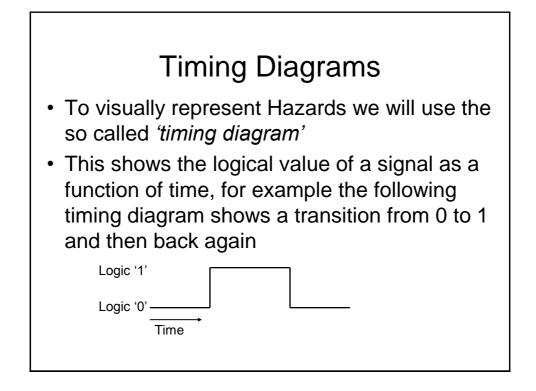

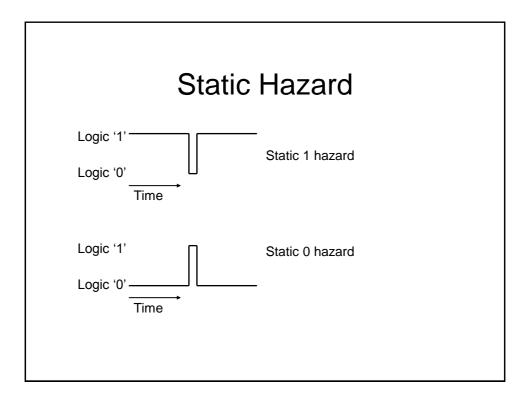

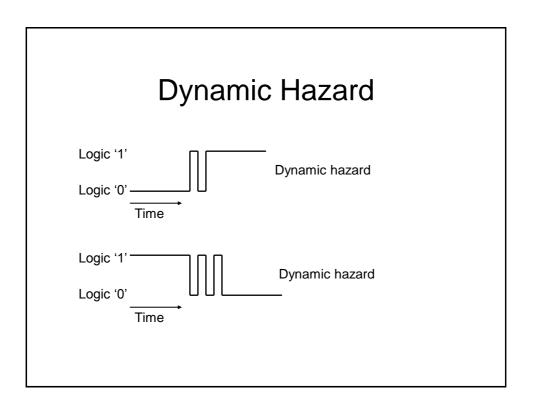

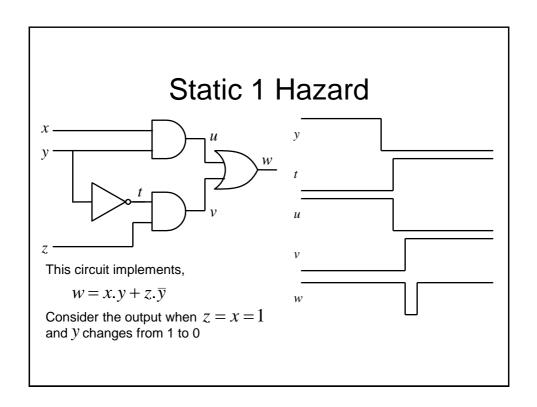

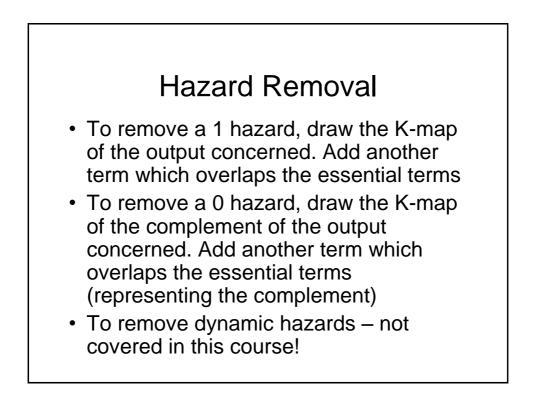

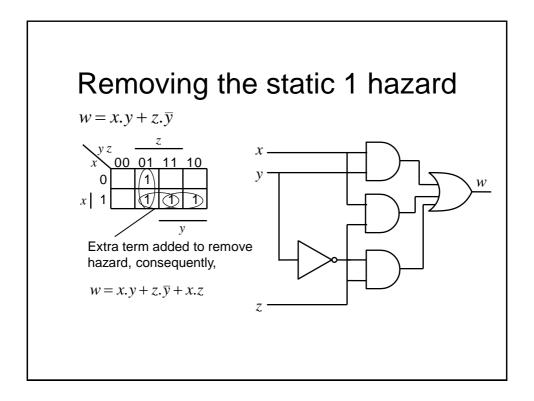

- As well as slowing down the operation of combinational logic circuits, gate delay can also give rise to so called '*Hazards*' at the output

- These *Hazards* manifest themselves as unwanted brief logic level changes (or *glitches*) at the output in response to changing inputs

- We will now describe how we can address these problems

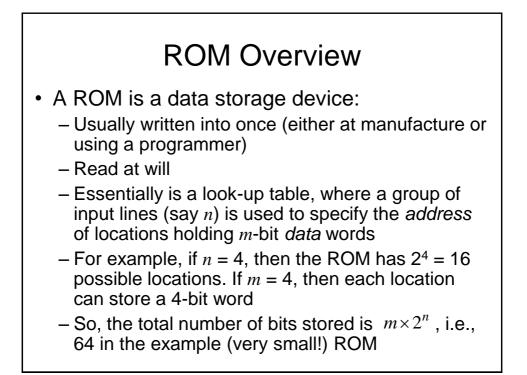

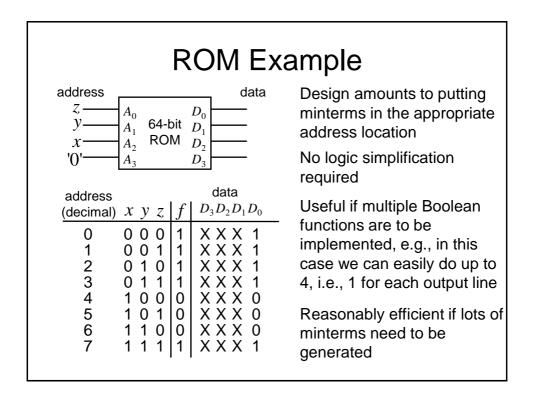

- Can be quite inefficient, i.e., become large in size with only a few non-zero entries, if the number of minterms in the function to be implemented is quite small

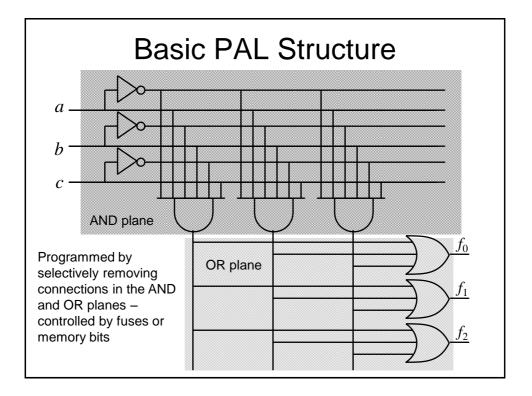

- Devices which can overcome these problems are known as programmable array logic (PAL)

- In PALs, only the required minterms are generated using a separate AND plane. The outputs from this plane are ORed together in a separate OR plane to produce the final output

## **Other Memory Devices**

- Non-volatile storage is offered by ROMs (and some other memory technologies, e.g., FLASH), i.e., the data remains intact, even when the power supply is removed

- Volatile storage is offered by Static Random Access Memory (SRAM) technology

- Data can be written into and read out of the SRAM, but is lost once power is removed

#### **Memory Application**

- Memory devices are often used in computer systems

- The central processing unit (CPU) often makes use of busses (a bunch of wires in parallel) to access external memory devices

- The *address bus* is used to specify the memory location that is being read or written and the data bus conveys the data too and from that location

- So, more than one memory device will often be connected to the same data bus

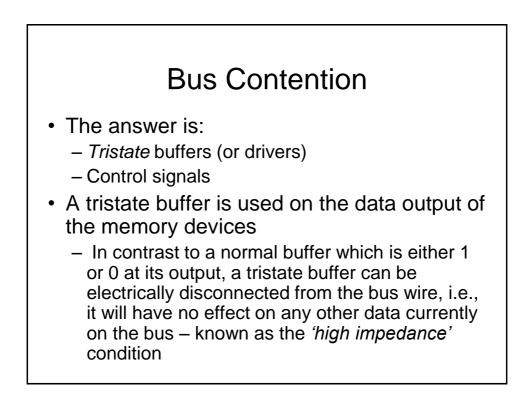

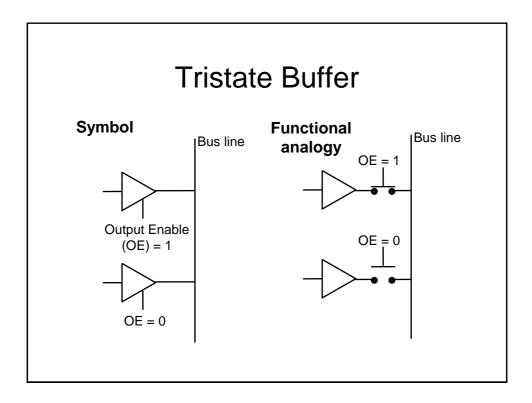

# **Bus Contention**

- In this case, if the output from the data pin of one memory was a 0 and the output from the corresponding data pin of another memory was a 1, the data on that line of the data bus would be invalid

- So, how do we arrange for the data from multiple memories to be connected to the some bus wires?

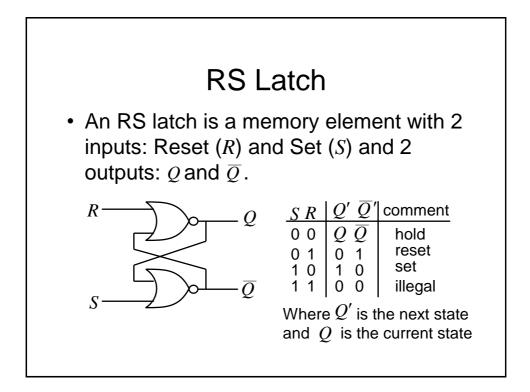

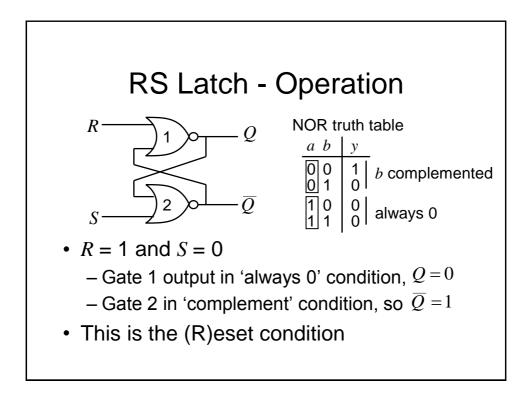

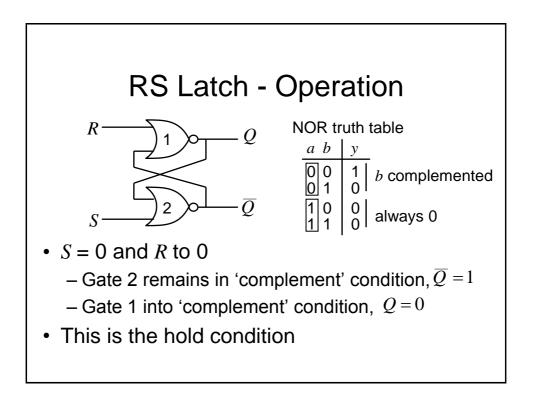

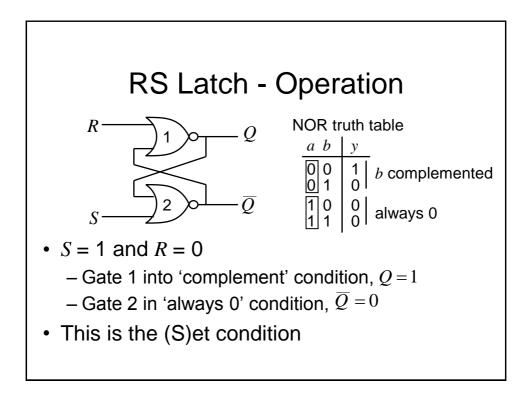

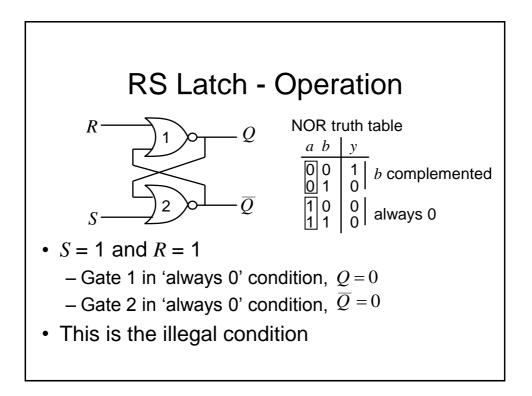

# **Sequential Logic**

Flip-flops and Latches

#### **Sequential Logic**

- The logic circuits discussed previously are known as *combinational*, in that the output depends only on the condition of the latest inputs

- However, we will now introduce a type of logic where the output depends not only on the latest inputs, but also on the condition of earlier inputs. These circuits are known as *sequential*, and implicitly they contain *memory* elements

- A memory stores data usually one bit per element

- A snapshot of the memory is called the *state*

- A one bit memory is often called a *bistable*, i.e., it has 2 stable internal states

- *Flip-flops* and *latches* are particular implementations of bistables

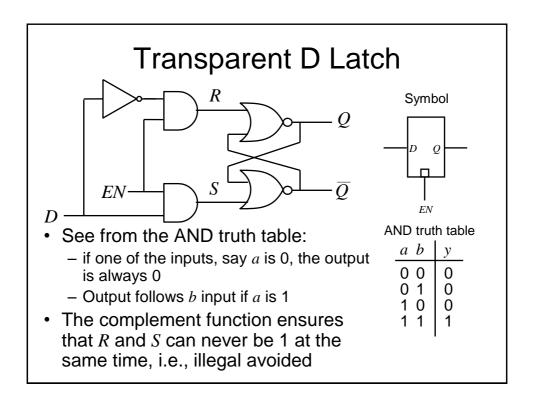

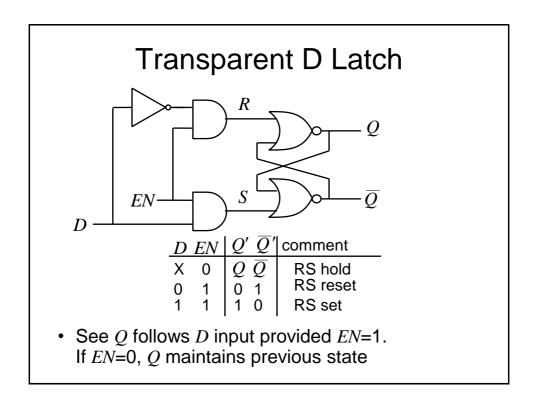

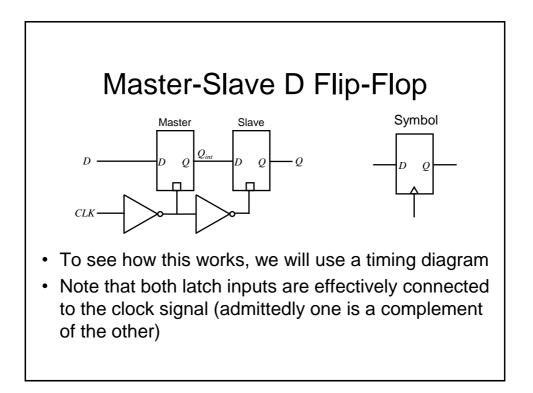

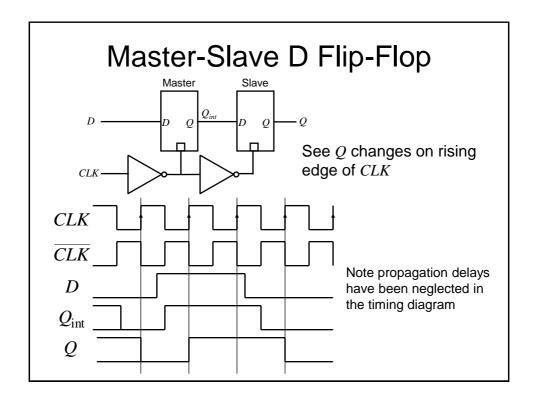

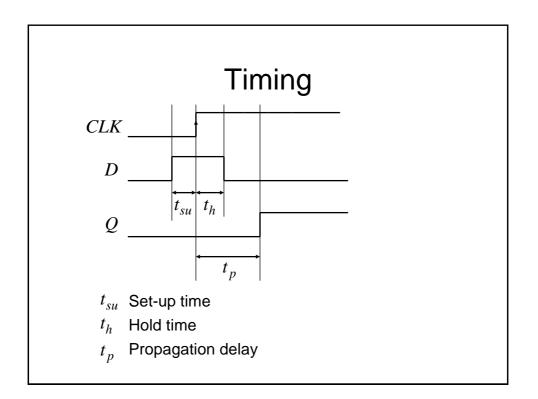

- The transparent D latch is so called '*level*' triggered. We can see it exhibits transparent behaviour if *EN*=1. It is often more simple to design sequential circuits if the outputs change only on the either rising (positive going) or falling (negative going) '*edges*' of the clock (i.e., enable) signal

- We can achieve this kind of operation by combining 2 transparent D latches in a so called *Master-Slave* configuration

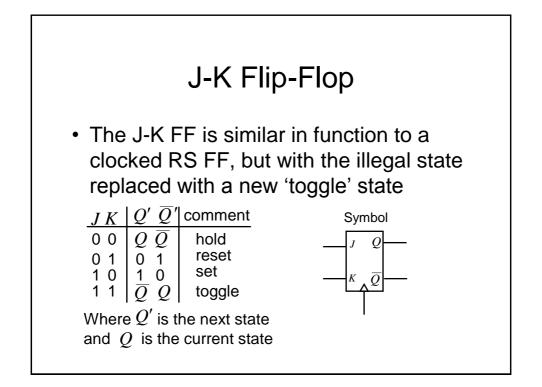

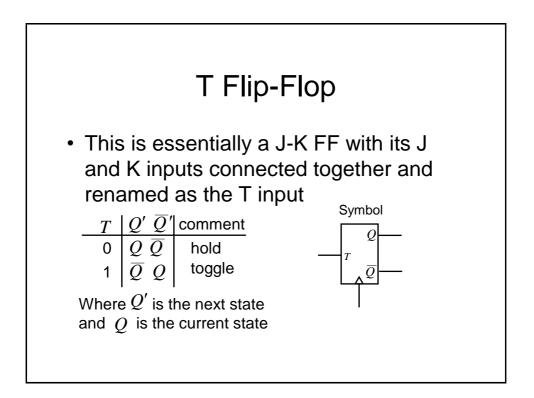

- Historically, other types of Flip-Flops have been important, e.g., J-K Flip-Flops and T-Flip-Flops

- However, J-K FFs are a lot more complex to build than D-types and so have fallen out of favour in modern designs, e.g., for field programmable gate arrays (FPGAs) and VLSI chips

## Asynchronous Inputs

- It is common for the FF types we have mentioned to also have additional so called 'asynchronous' inputs

- They are called asynchronous since they take effect independently of any clock or enable inputs

- Reset/Clear force Q to 0

- Preset/Set force *Q* to 1

- Often used to force a synchronous circuit into a known state, say at start-up.

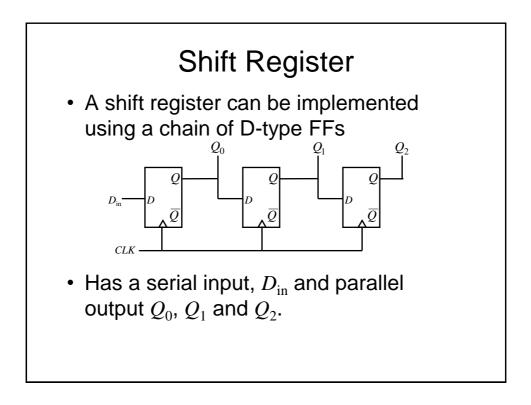

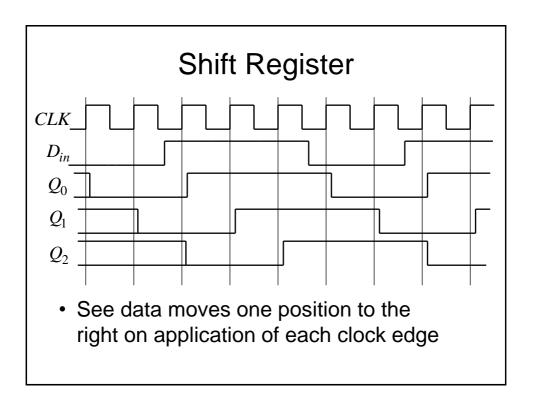

- Memories, e.g.,

- Shift register

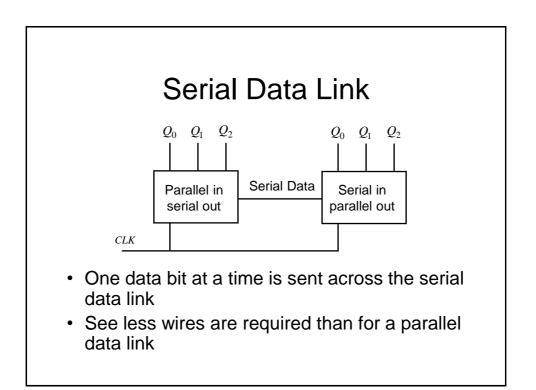

- Parallel loading shift register : can be used for parallel to serial conversion in serial data communication

- Serial in, parallel out shift register: can be used for serial to parallel conversion in a serial data communication system.

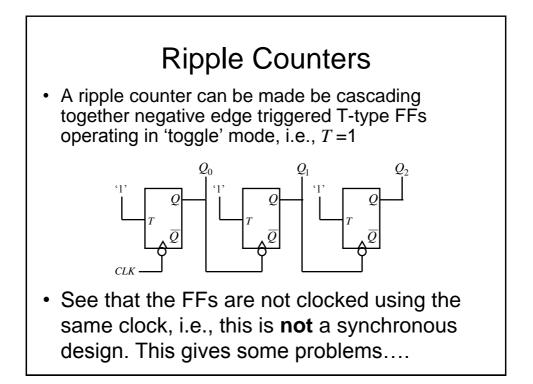

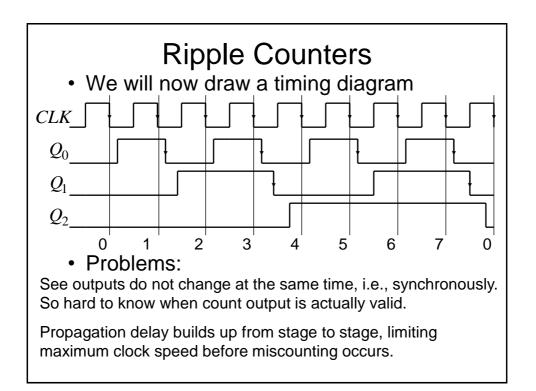

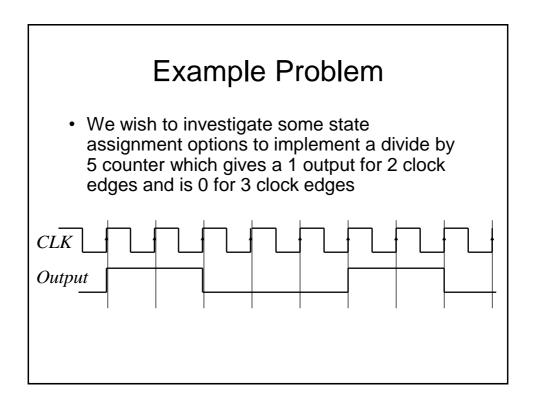

# **Ripple Counters**

- If you observe the frequency of the counter output signals you will note that each has half the frequency, i.e., double the repetition period of the previous one. This is why counters are often known as dividers

- Often we wish to have a count which is not a power of 2, e.g., for a BCD counter (0 to 9).To do this:

- use FFs having a Reset/Clear input

- Use an AND gate to detect the count of 10 and use its output to Reset the FFs

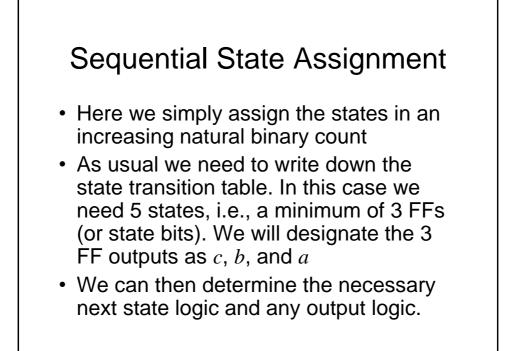

### Synchronous Counters

- We will now investigate the design of synchronous counters

- We will consider the use of D-type FFs only, although the technique can be extended to cover other FF types.

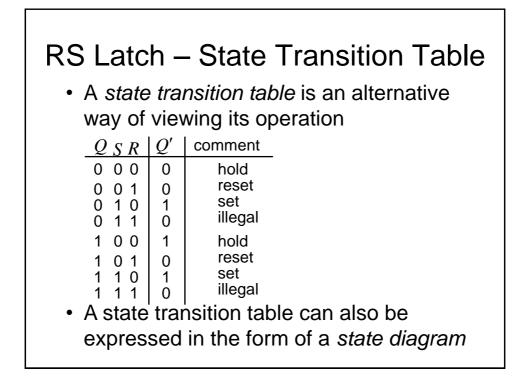

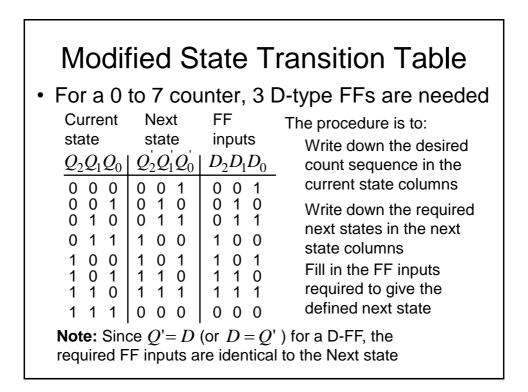

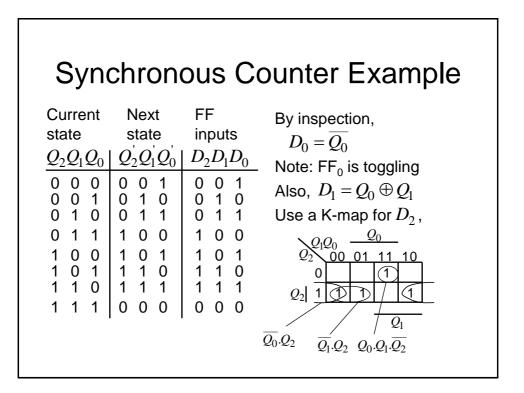

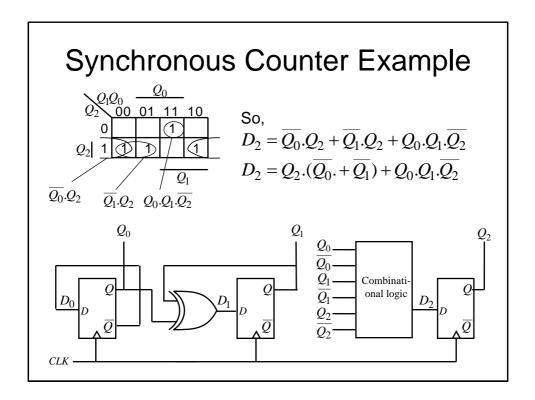

- As an example, we will consider a 0 to 7 up-counter

- To assist in the design of the counter we will make use of a modified *state transition table*. This table has additional columns that define the required FF inputs (or excitation as it is known)

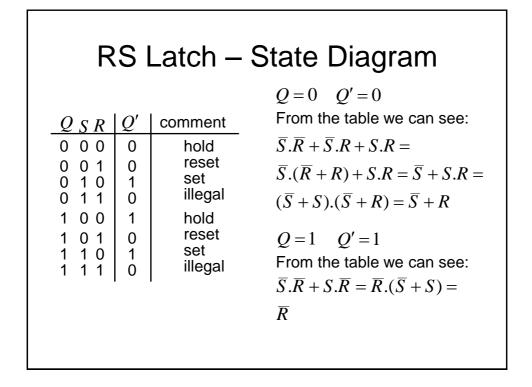

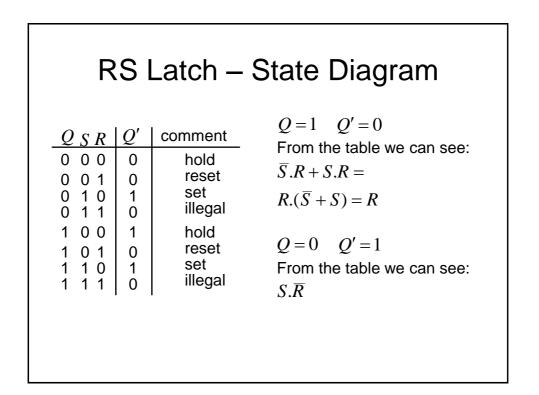

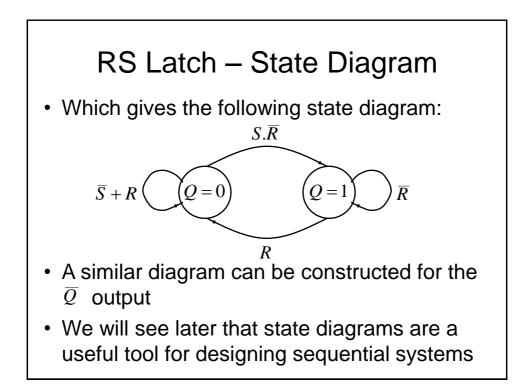

- Note we have used a state transition table previously when determining the state diagram for an RS latch

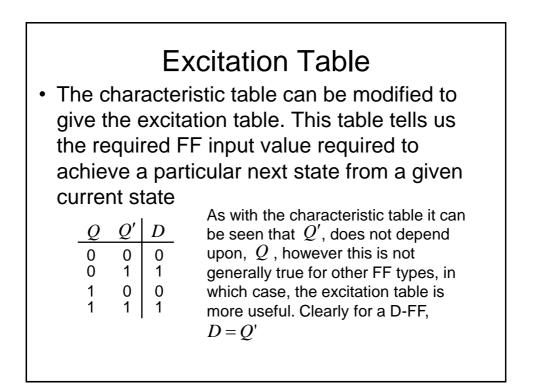

- We will also make use of the so called '*excitation table*' for a D-type FF

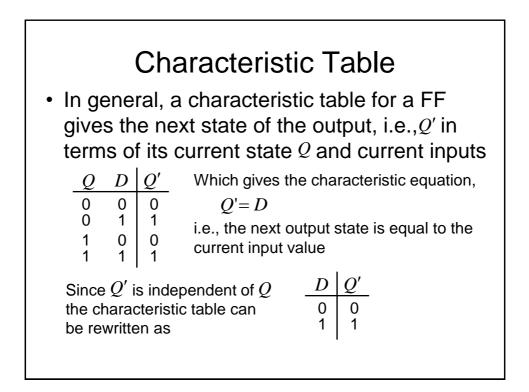

- First however, we will investigate the so called *characteristic table* and *characteristic equation* for a D-type FF

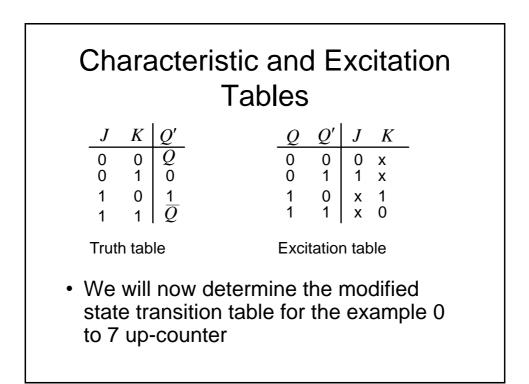

# Characteristic and Excitation Tables

- Characteristic and excitation tables can be determined for other FF types.

- These should be used in the design process if D-type FFs are not used

- For example, for a J-K FF the following tables are appropriate:

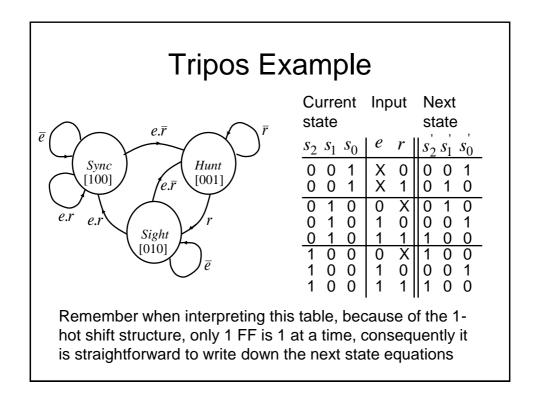

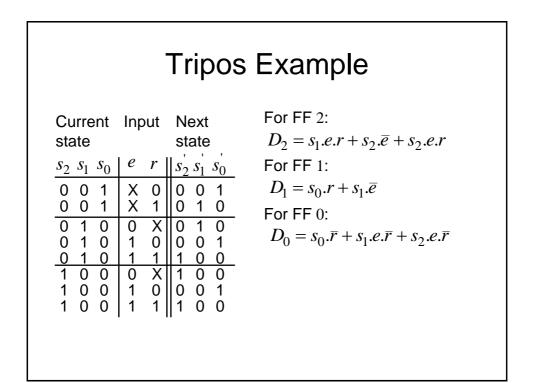

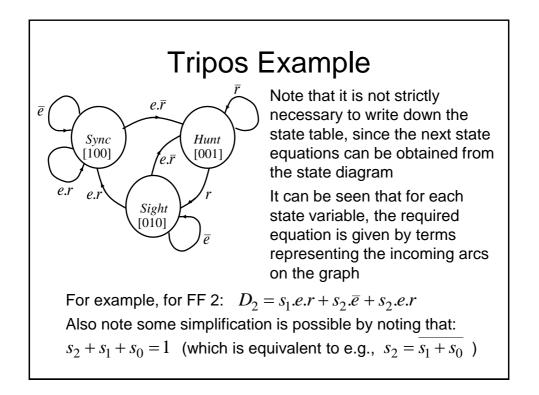

### Modified State Transition Table

In addition to columns representing the current and desired next states (as in a conventional state transition table), the modified table has additional columns representing the required FF inputs to achieve the next desired FF states

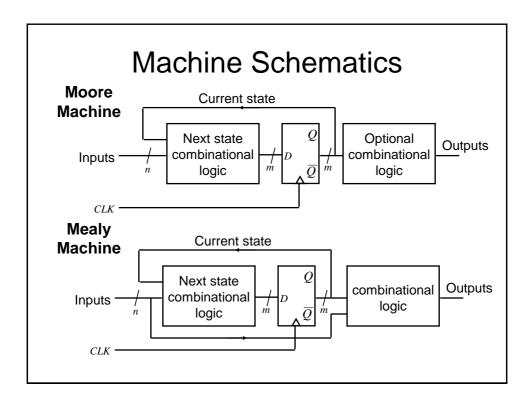

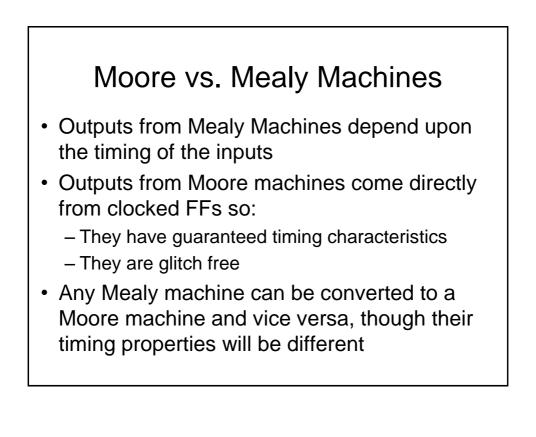

# Synchronous State Machines

#### Synchronous State Machines

- We have seen how we can use FFs (D-types in particular) to design synchronous counters

- We will now investigate how these principles can be extended to the design of synchronous state machines (of which counters are a subset)

- We will begin with some definitions and then introduce two popular types of machines

# Definitions

- Finite State Machine (FSM) a deterministic machine (circuit) that produces outputs which depend on its internal state and external inputs

- **States** the set of internal memorised values, shown as circles on the state diagram

- Inputs External stimuli, labelled as arcs on the state diagram

- Outputs Results from the FSM

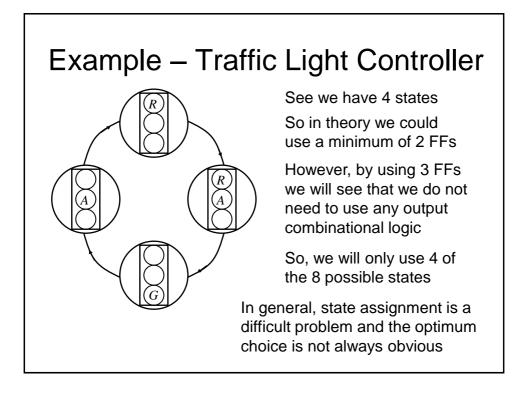

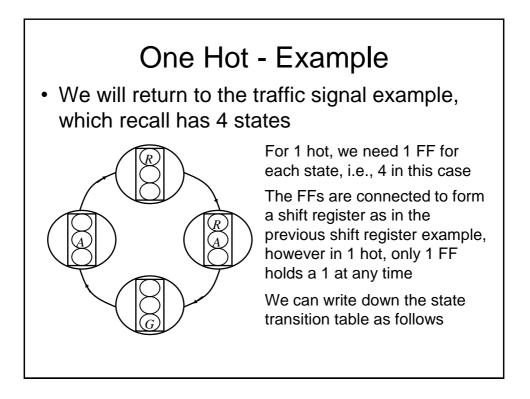

### Moore Machine - Example

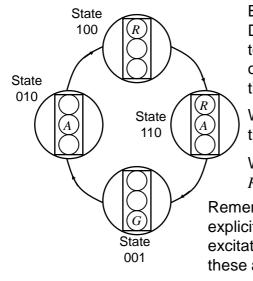

- We will design a Moore Machine to implement a traffic light controller

- In order to visualise the problem it is often helpful to draw the state transition diagram

- This is used to generate the state transition table

- The state transition table is used to generate

- The next state combinational logic

- The output combinational logic (if required)

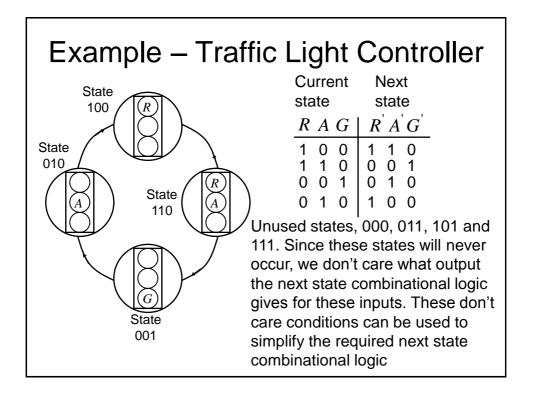

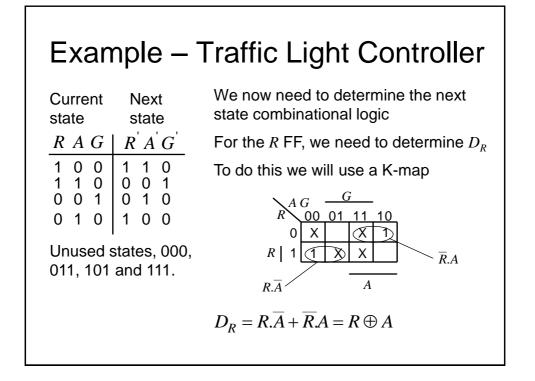

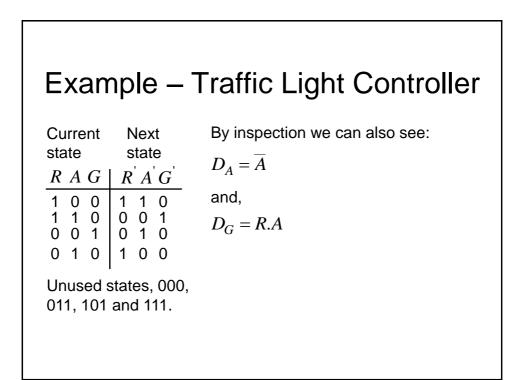

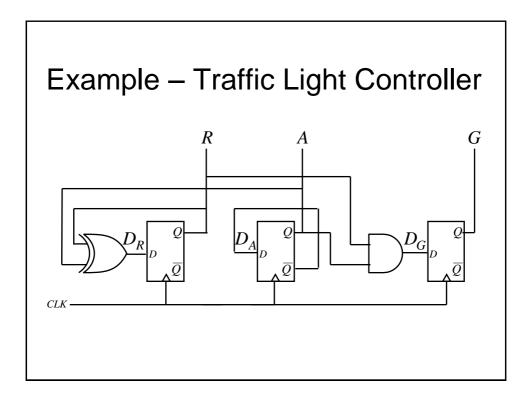

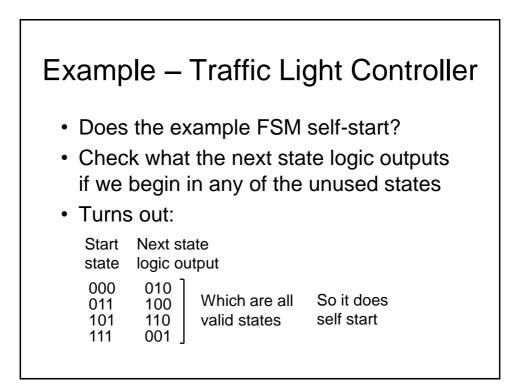

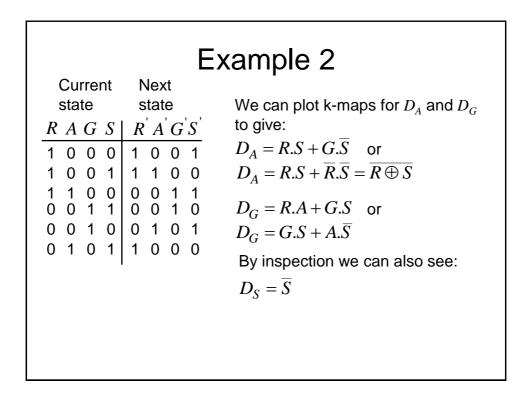

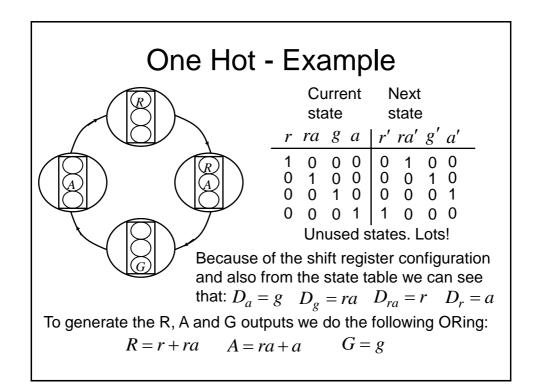

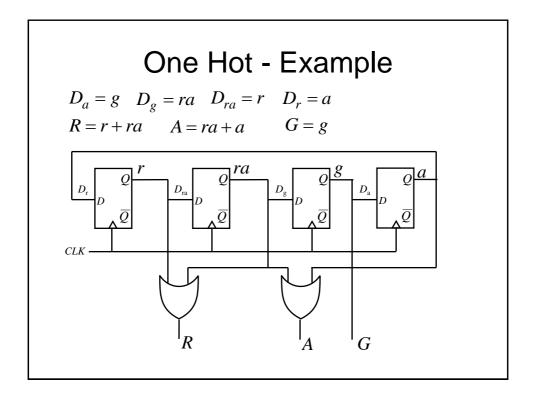

# Example – Traffic Light Controller

By using 3 FFs (we will use D-types), we can assign one to each of the required outputs (R, A, G), eliminating the need for output logic

We now need to write down the state transition table

We will label the FF outputs R, A and G

Remember we do not need to explicitly include columns for FF excitation since if we use D-types these are identical to the next state

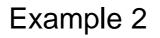

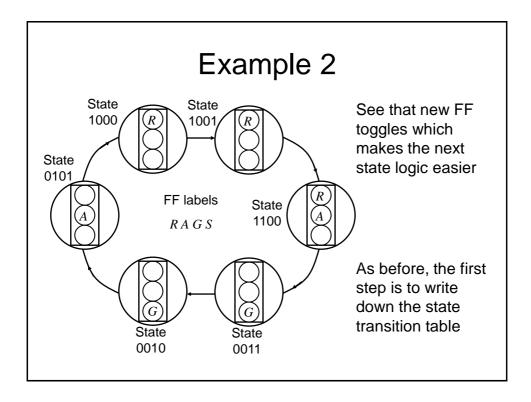

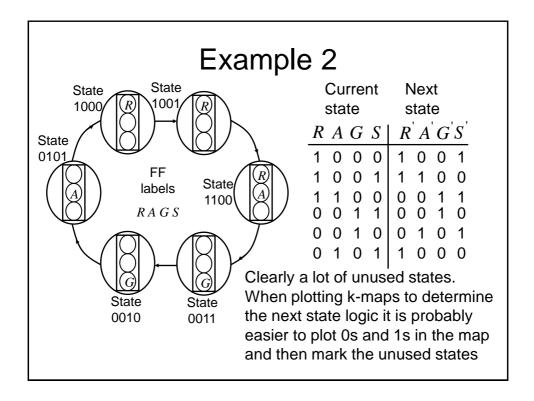

- We extend Example 1 so that the traffic signals spend extra time for the *R* and *G* lights

- Essentially, we need 2 additional states, i.e., 6 in total.

- In theory, the 3 FF machine gives us the potential for sufficient states

- However, to make the machine combinational logic easier, it is more convenient to add another FF (labelled *S*), making 4 in total

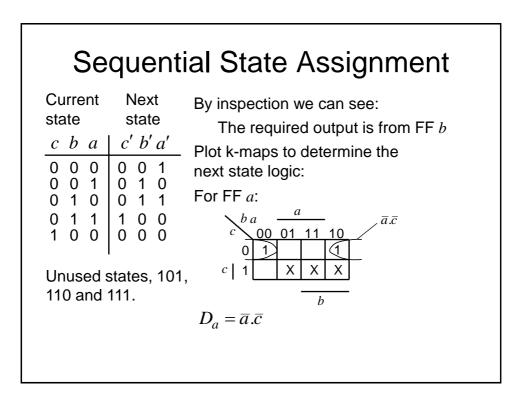

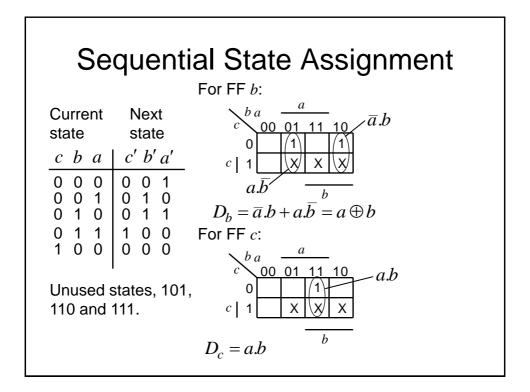

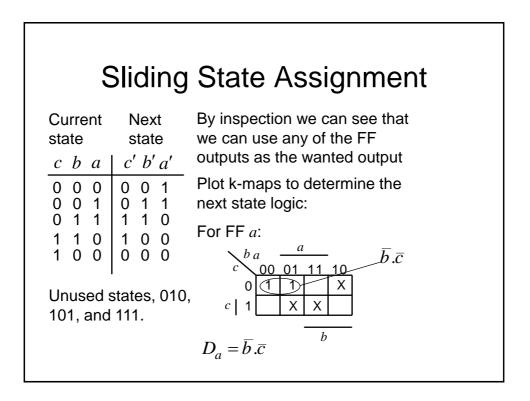

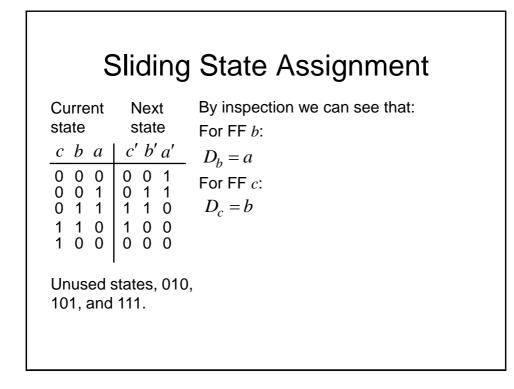

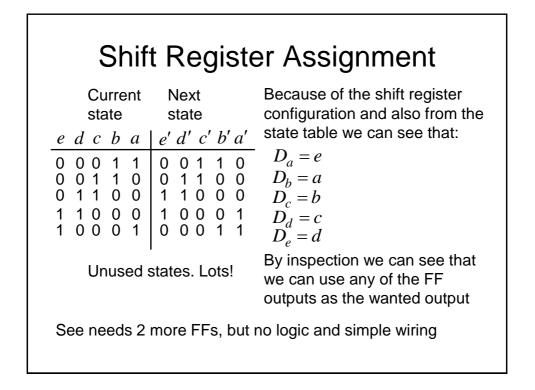

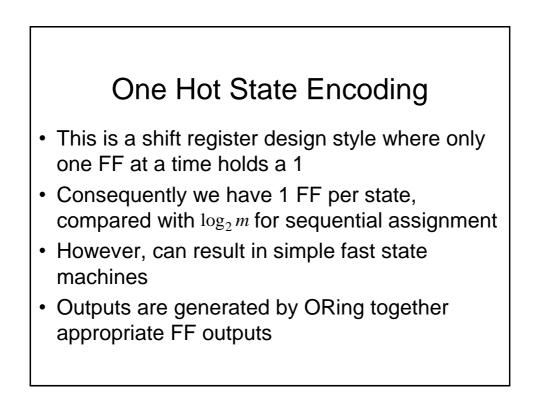

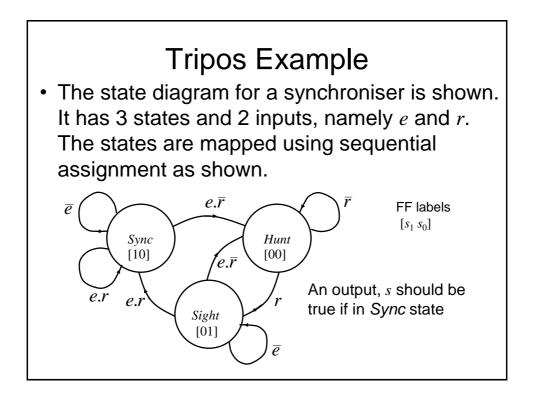

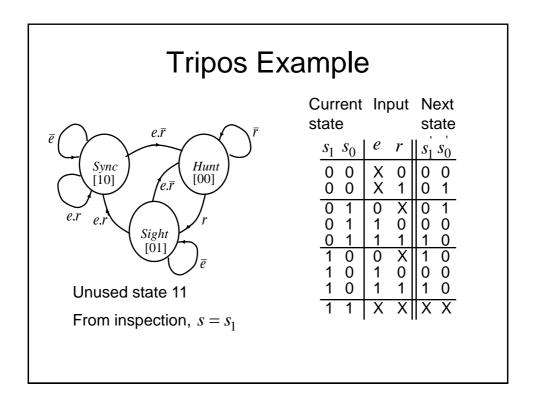

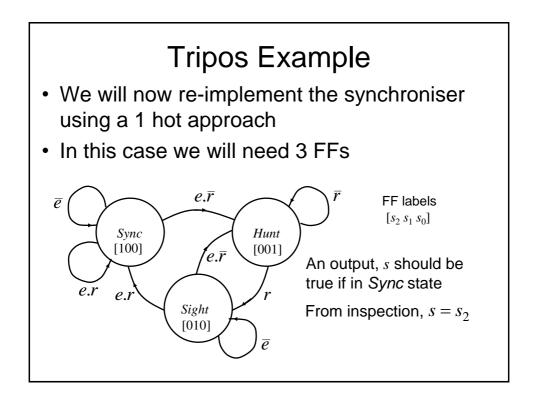

## State Assignment

- If we have *m* states, we need at least log<sub>2</sub>*m* FFs (or more informally, bits) to encode the states, e.g., for 8 states we need a min of 3

FFs

- We will now present an example giving various potential state assignments, some using more FFs than the minimum

- We saw previously that programmable logic can be used to implement combinational logic circuits, i.e., using PAL devices

- PAL style devices have been modified to include D-type FFs to permit FSMs to be implemented using programmable logic

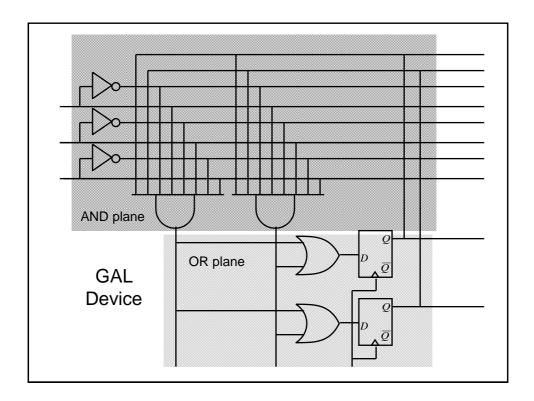

- One particular style is known as Generic Array Logic (GAL)

#### **GAL** Devices

- They are similar in concept to PALs, but have the option to make use of a D-type flipflops in the OR plane (one following each OR gate). In addition, the outputs from the Dtypes are also made available to the AND plane (in addition to the usual inputs)

- Consequently it becomes possible to build programmable sequential logic circuits