HOME

UP

PREV

FURTHER NOTES

NEXT (BVCI Net-Level Protocol.)

Practical Bus Protocols on IP Blocks

Last year you used the Altera Avalon bus in part IB ECAD+Arch workshops.

Many real-world IP blocks today are wired up using OCP's BVCI and ARM's AHB. Although

the port on the IP block is fixed, in terms of its protocol, it can

be connected to any system of bus bridges and on chip networks.

Open core protocol (wishbone) (OCP): freely available, bus-independent protocol for IP blocks.

Download full OCP documents from

»OCIP.org. See also

»bus-protocols-limit-design-reuse-of-ip

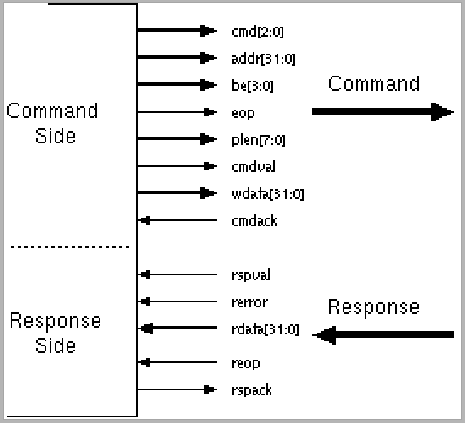

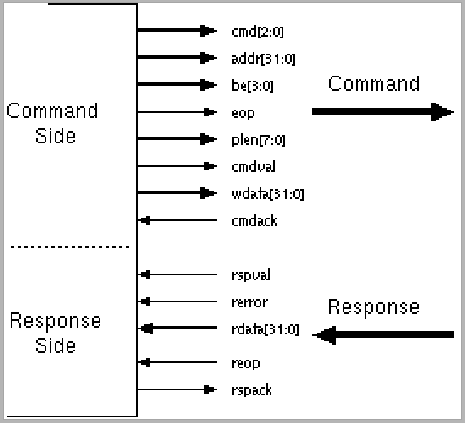

OCP BVCI Core Nets:

| - All IP blocks can sport this interface.

- Separate request and response ports.

- Data is valid on overlap of req and ack.

- Temporal decoupling of directions:

- Allows pipeline delays for crossing switch fabrics or crossing clock domains.

- Sideband signals: interrupts, errors and resets: vary on per-block basis.

- Two complete instances of the port are neeed if block is both an initiator and target.

- Arrows indicate signal directions on initiator. All are reversed on target.

|