reg [3:0] framestore[32767:0];

reg [7:0] hptr, vptr;

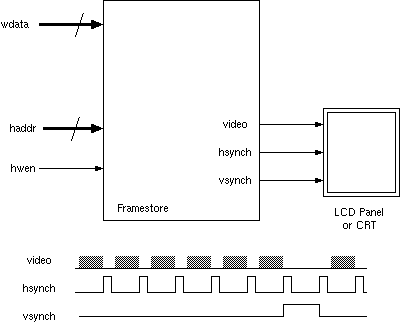

output reg [3:0] video;

output reg hsynch, vsynch;

always @(posedge clk) begin

hptr <= (hsynch) ? 0: hptr + 1;

hsynch <= (hptr >= 230)

if (hsynch) vptr <= (vsynch) ? 0: vptr + 1;

vsynch <= (vptr == 110)

video <= framestore[{vptr[6:0], hptr}];

if (hwen) framestore[haddr]<= wdata[3:0];

end