FPGA Development Guide

A typical work-flow for FPGA design may be separated into three main stages:

- Architecture

-

Describing your design at various levels of abstraction. The most basic components, from synchronisers to simple processors,

are written in an HDL, such as SystemVerilog; these are then combined (recursively) to form more complex systems.

- Simulation and Synthesis

-

Simulation tests your design by emulating hardware matching the semantics of the HDL. Synthesis is the compilation of

your design into a netlist, expressing it in terms of FPGA elements (e.g. wiring, LUTs, etc.).

- Software

-

Processor architectures can run programs compiled to the appropriate binary (machine code) format. A binary

is executed by reading its instructions from the device memory; some binaries may be incorporated into the device programming

file, others uploaded dynamically.

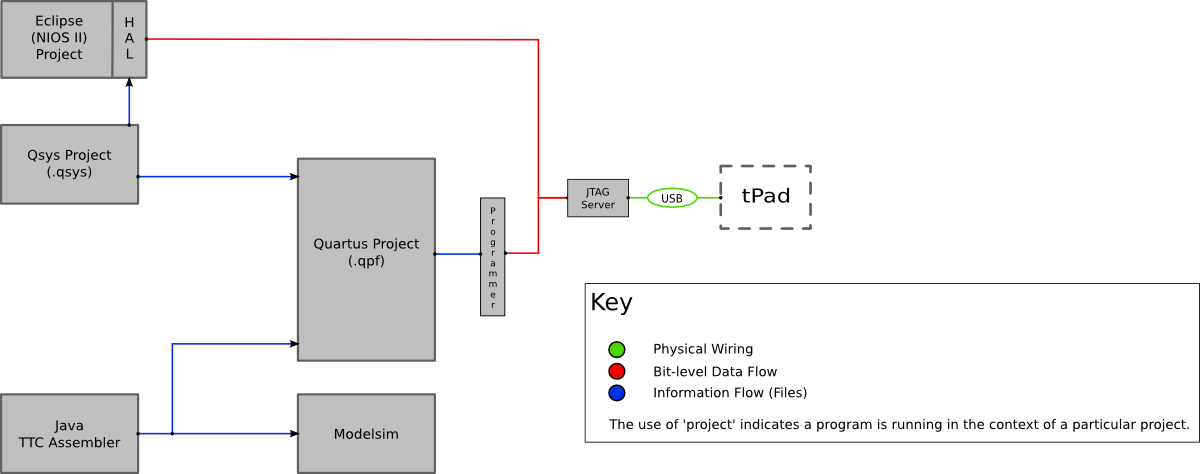

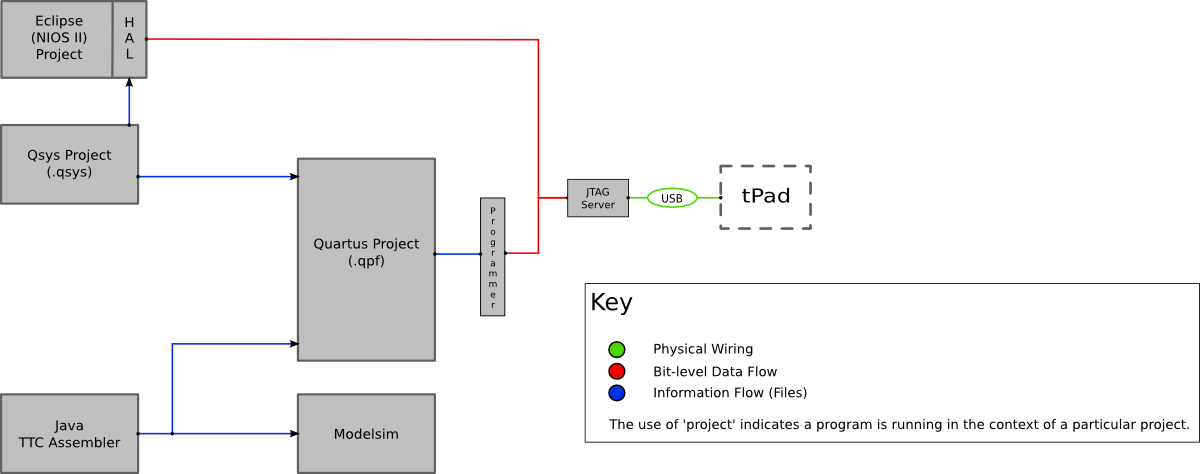

A general overview is given by the following schematic; the labs provide greater coverage.

- Eclipse

-

Software IDE. Includes a C compiler producing binaries (machine code) for the NIOS II processor.

- HAL

-

Hardware Abstraction Layer. A NIOS II Eclipse project providing a low-level, memory-mapped interface to a specified

architecture. The interface is basically a set of constants defining address ranges to which each component is mapped,

and procedures to read and write data.

- Quartus

-

Hardware IDE. Using an HDL, such as SystemVerilog, a Quartus project is a hierarchy of components or modules

from a specified root. A complete project may be synthesised for programming onto a specified FPGA device.

- Qsys

-

Qsys works at the component level of abstraction. A component in Qsys is a black box with a specified interface (wires), which can

be connected together using a switched interconnect memory system.

Each black box is ultimately a set of files in some HDL. Each Qsys project thus represents a hierarchy of Verilog components (much like

a Quartus project), meaning it can also be treated as a component for use in another project.

- Modelsim

-

Provides a simulation environment for (System)Verilog containing debug code (ignored for synthesis).

- Programmer / tPad

-

JTAG is a communications protocol for on-chip debug (e.g. via a JTAG UART) and programming, using a standard group

of dedicated pins. The FPGA is primarily configurable as a switch fabric and lookup tables, the former controlling

connections between wires and the latter implementing custom functions. The control logic of each configurable element

is memory-mapped to a dedicated SRAM module. An SRAM Object File (.sof), produced by a Quartus compilation, contains configuration data for each element,

which is loaded via JTAG into the corresponding (volatile) SRAM module to (temporarily) program the FPGA.