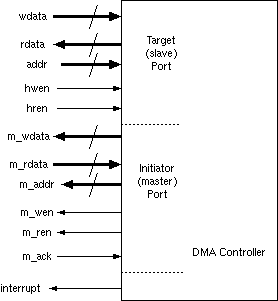

This controller just block copies: may need to keep src and/or dest constant for device access.

Typically, a multi-channel DMA controller is provided.

A more flexible DMA controller that follows linked lists

is as complex as a simple CPU: ultimately little theoretical distinction.

DMA controllers may be built into devices: SoC bus master ports needed.

// Programmers Model

reg [31:0] count, src, dest;

reg int_enable, active;

// Other local state

reg [31:0] datareg;

reg intt, rwbar;

always @(posedge clk) begin // Target

if (hwen && addr==0) begin

{ int_enable, active } <= wdata[1:0];

int <= 0; rwbar <= 1;

end

if (hwen && addr==4) count <= wdata;

if (hwen && addr==8) src <= wdata;

if (hwen && addr==12) dest <= wdata;

end

assign rdata = ...// Target readbacks

always @(posedge clk) begin // Initiator

if (active && rwbar && m_ack) begin

datareg <= m_rdata;

rwbar <= 0;

src <= src + 4;

end

if (active && !rwbar && m_ack) begin

rwbar <= 1;

dest <= dest + 4;

count <= count - 1;

end

if (count==1 && active && !rwbar) begin

active <= 0;

intt <= 1;

end

end

assign m_wdata = datareg;

assign m_ren = active && rwbar;

assign m_wen = active && !rwbar;

assign m_addr = (rwbar) ? src:dest;

assign interrupt = intt && int_enable;