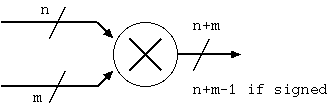

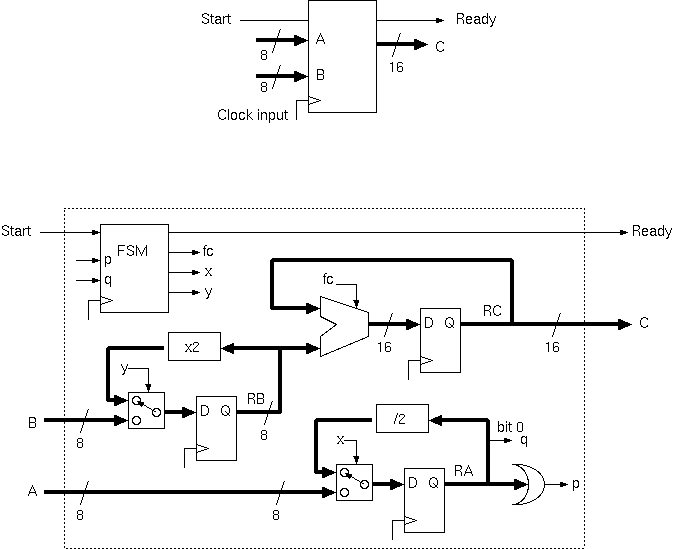

Behavioural algorithm:

while (1)

{

wait (Start);

RA=A; RB=B; RC=0;

while(RA>0)

{

if odd(RA) RC=RC+RB;

RA = RA >> 1;

RB = RB << 1;

}

Ready = 1;

wait(!Start);

Ready = 0;

}

|  |

It is certainly not fully-pipelined, it goes busy for many cycles, depening on the log of the A input. The illustration shows a common design pattern consisting of a datapath and a sequencer. Booth's algorithm (see additional material) is faster, still using one adder but needing half the clock ticks. Exercise: Write out the complete design, including sequencer, for the above multiplier, or that of Booth, or a long division unit, in Verilog or SystemC.