reg A, B;

always @(posedge ck) begin

A <= B;

B <= A;

end

// Separate example

reg zz;

reg [2:0] q;

always @(posedge ck) begin

zz <= ~zz;

if (zz) q <= q + 3'd1;

// Prev line sees old zz

end

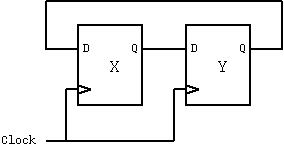

For correct behaviour of synchronous edge-triggered hardware, the progagation delay of D-types must be greater than their hold time.

Question : How can we ensuse this in a technology-neutral model that does not have any specific numerical delays ?

Answer: Hardware simulators commonly support the compute/commit or `signal' paradigm for non-blocking updates.

Two examples:

reg A, B;

always @(posedge ck) begin

A <= B;

B <= A;

end

|  | // Separate example

reg zz;

reg [2:0] q;

always @(posedge ck) begin

zz <= ~zz;

if (zz) q <= q + 3'd1;

// Prev line sees old zz

end

|