# Digital Electronics Part I – Combinational and Sequential Logic

Dr. I. J. Wassell

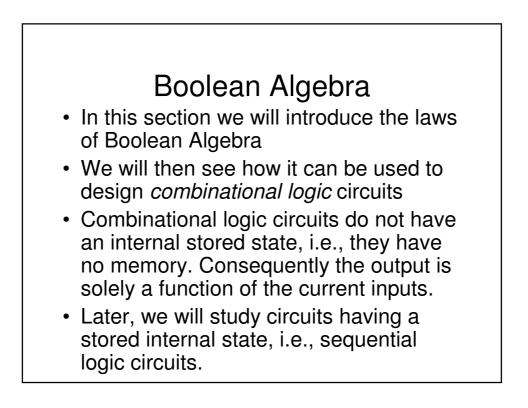

Introduction

# Aims

- · To familiarise students with

- Combinational logic circuits

- Sequential logic circuits

- How digital logic gates are built using transistors

- Design and build of digital logic systems

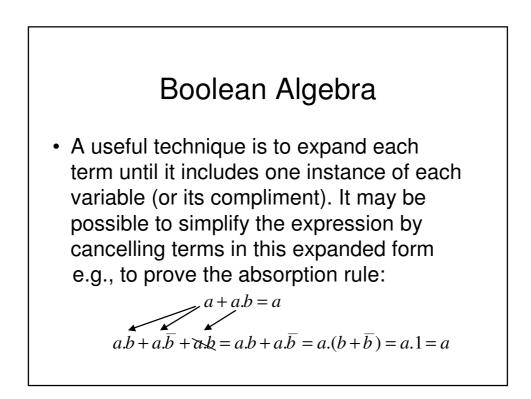

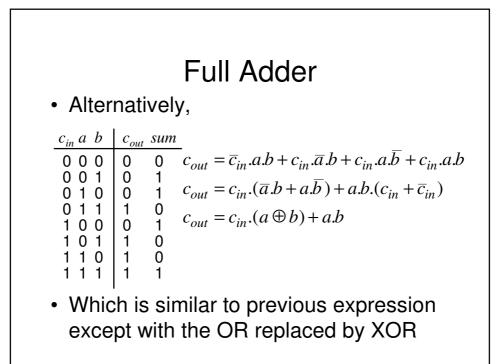

## **Boolean Algebra - Examples**

Show  $a.(\overline{a}+b) = a.b$   $a.(\overline{a}+b) = a.\overline{a} + a.b = 0 + a.b = a.b$ Show  $a+(\overline{a}.b) = a+b$  $a+(\overline{a}.b) = (a+\overline{a}).(a+b) = 1.(a+b) = a+b$

# Boolean Algebra - Example

### Simplify

$\begin{array}{l} x.y + \overline{y}.z + x.z + x.y.z \\ x.y.z + x.y.\overline{z} + x.\overline{y}.z + \overline{x}.\overline{y}.z + x.y.z + x.\overline{y}.z + x.y.z \\ x.y.z + x.y.\overline{z} + x.\overline{y}.z + \overline{x}.\overline{y}.z \\ x.y.(z + \overline{z}) + \overline{y}.z.(x + \overline{x}) \\ x.y.1 + \overline{y}.z.1 \\ x.y + \overline{y}.z \end{array}$

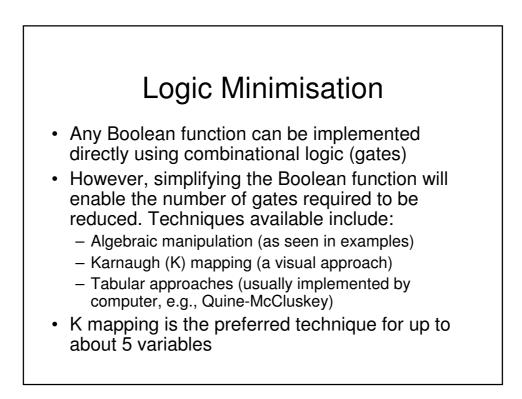

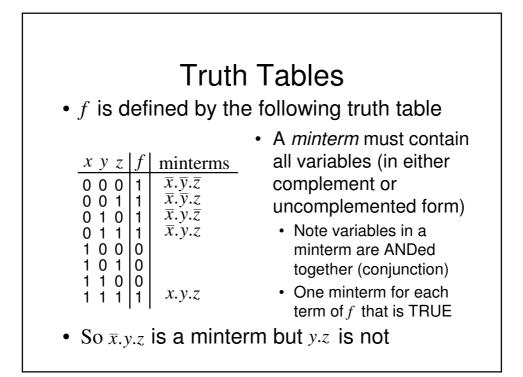

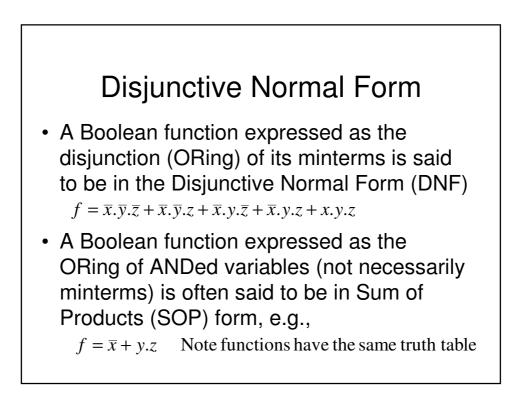

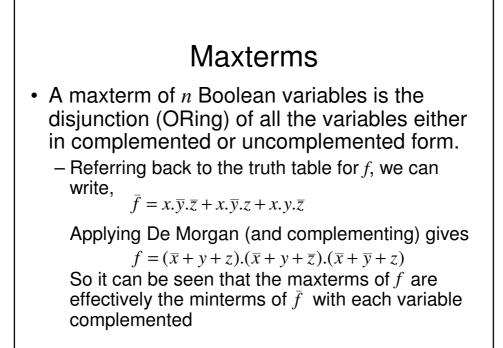

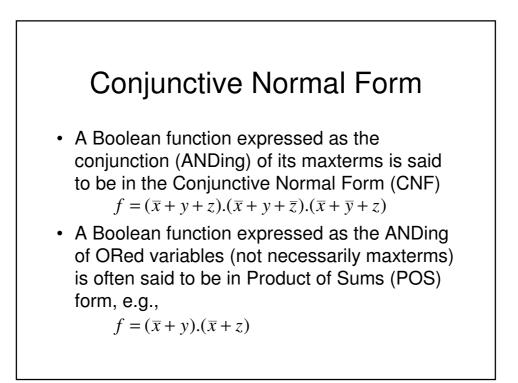

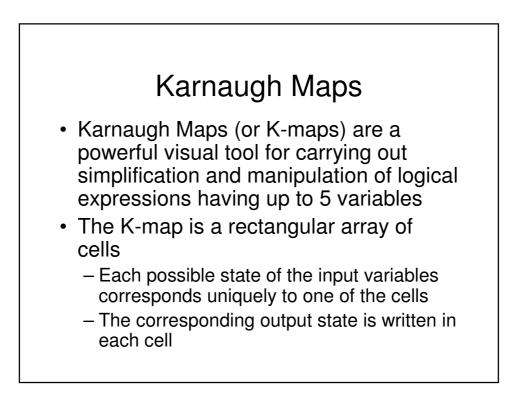

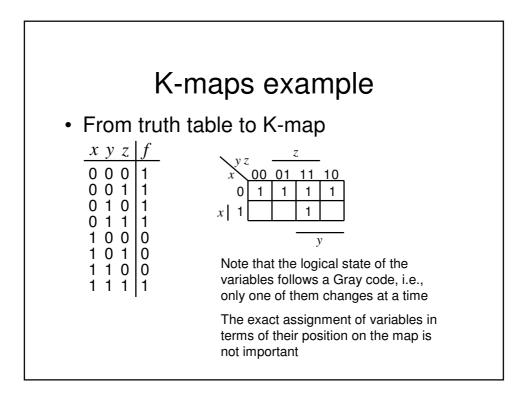

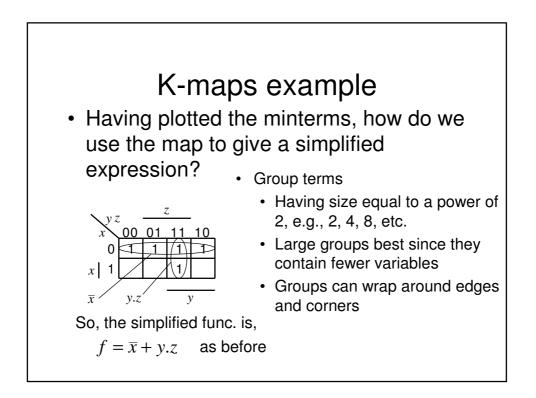

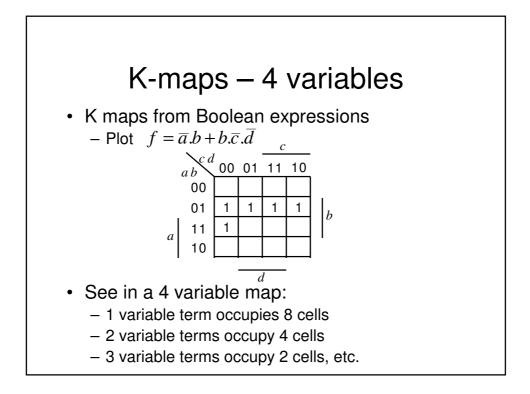

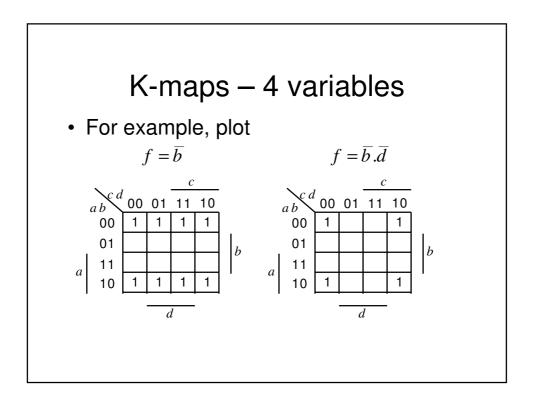

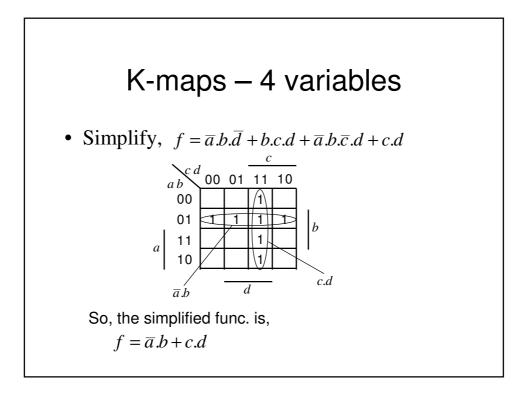

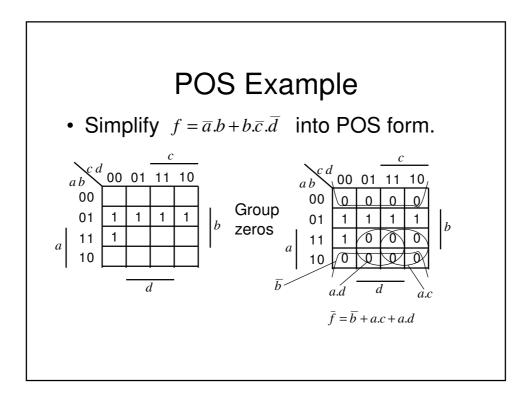

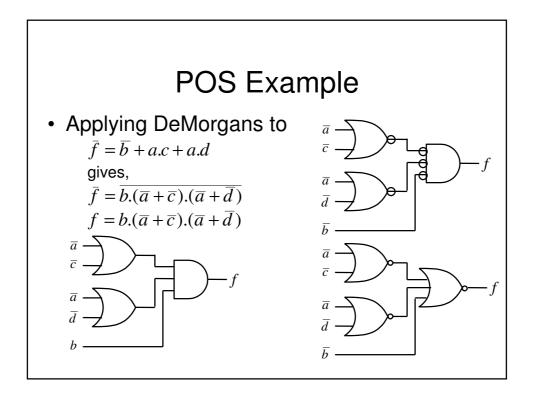

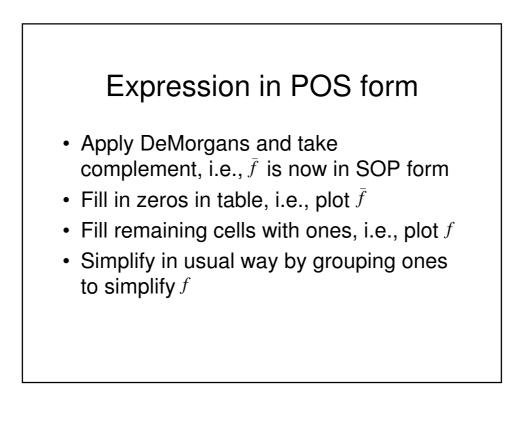

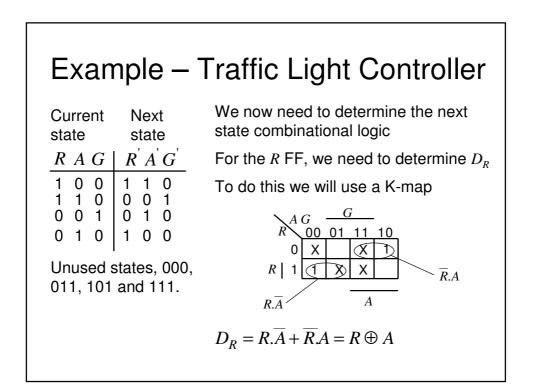

# Logic Simplification As we have seen previously, Boolean algebra can be used to simplify logical expressions. This results in easier implementation Note: The DNF and CNF forms are not simplified. However, it is often easier to use a technique known as Karnaugh mapping

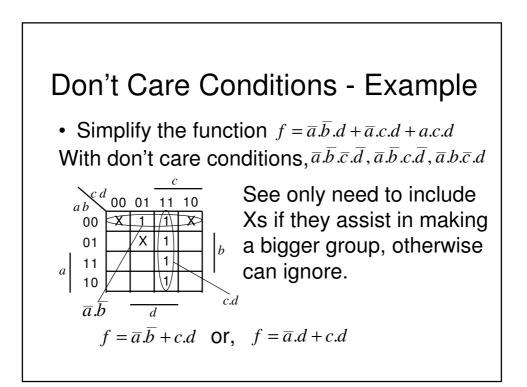

# Don't Care Conditions

- Sometimes we do not care about the output value of a combinational logic circuit, i.e., if certain input combinations can never occur, then these are known as *don't care conditions*.

- In any simplification they may be treated as 0 or 1, depending upon which gives the simplest result.

- For example, in a K-map they are entered as Xs

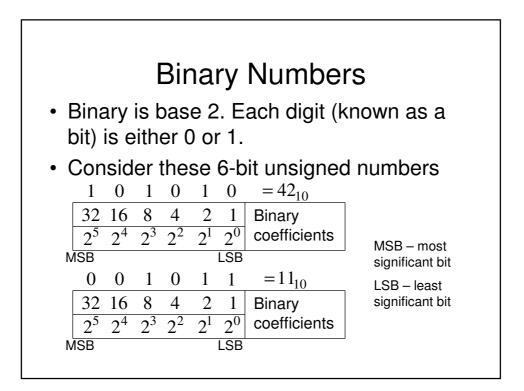

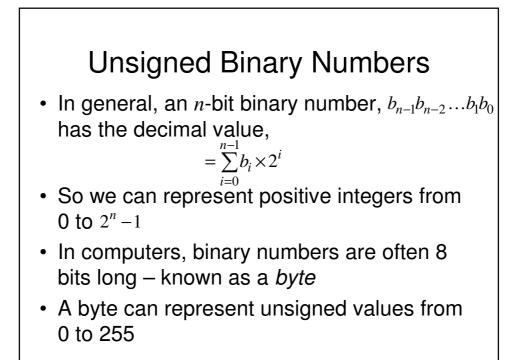

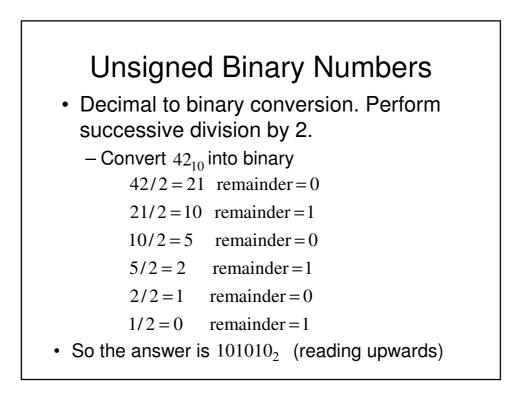

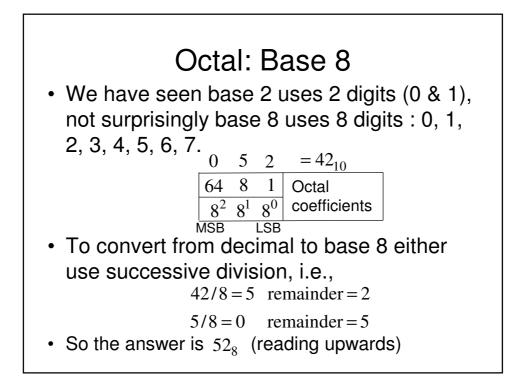

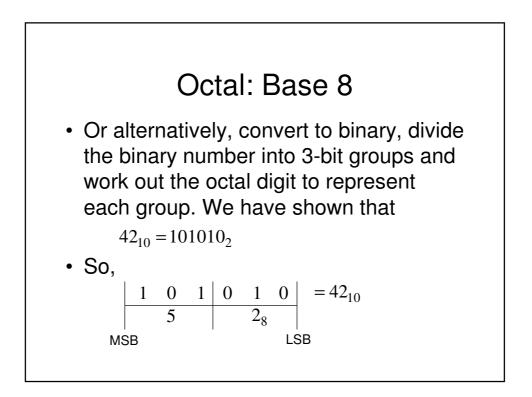

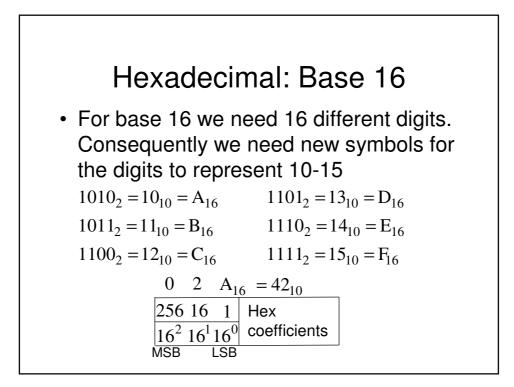

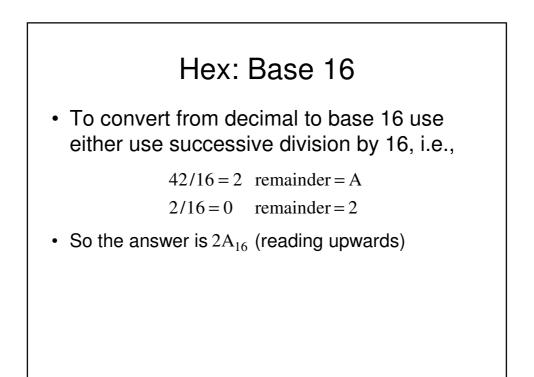

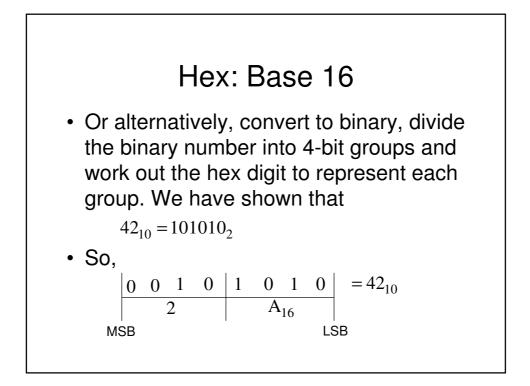

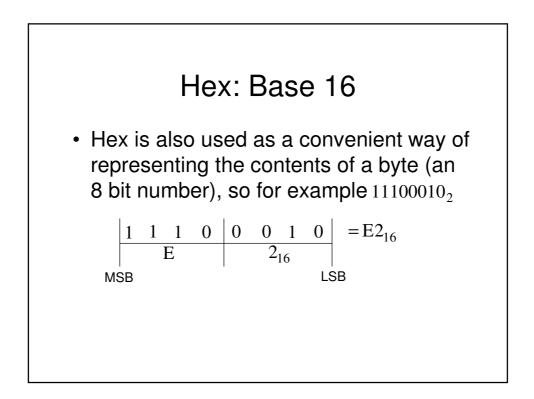

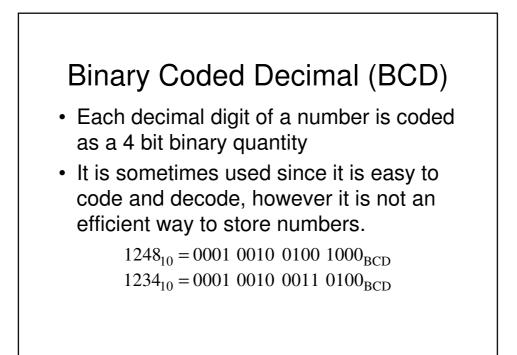

# **Binary Numbers**

- It is important to be able to represent numbers in digital logic circuits

- for example, the output of a analogue to digital converter (ADC) is an *n*-bit number, where *n* is typically in the range from 8 to 16

- Various representations are used, e.g.,

- unsigned integers

- 2's complement to represent negative numbers

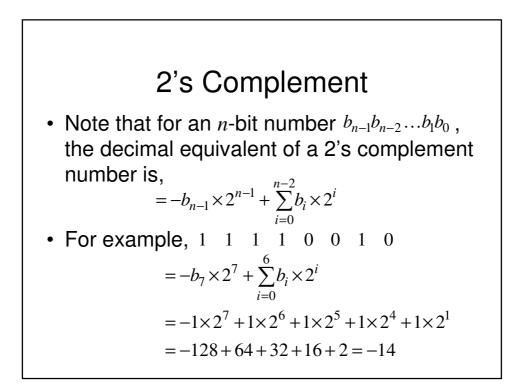

# Negative numbers

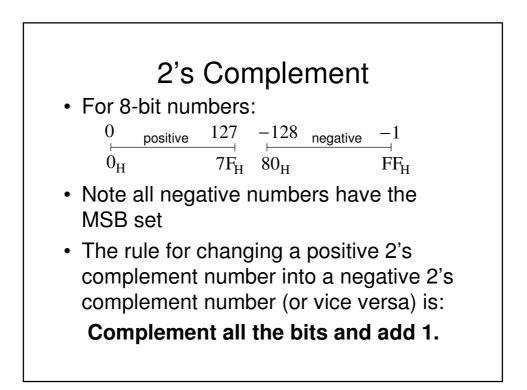

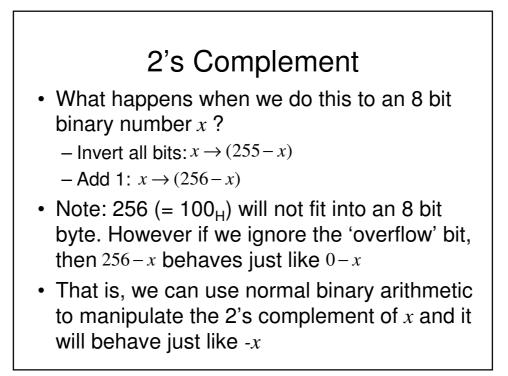

- So far we have only been able to represent positive numbers. For example, we have seen an 8-bit byte can represent from 0 to 255, i.e., 2<sup>8</sup> = 256 different combinations of bits in a byte

- If we want to represent negative numbers, we have to give up some of the range of positive numbers we had before

- A popular approach to do this is called 2's complement

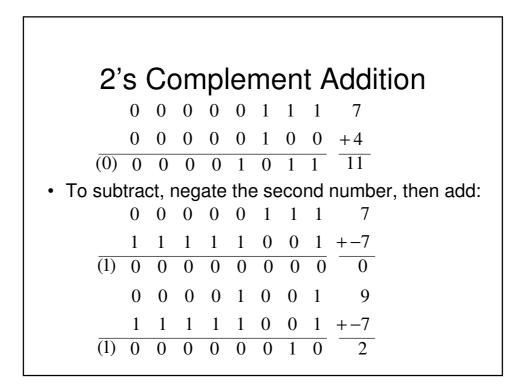

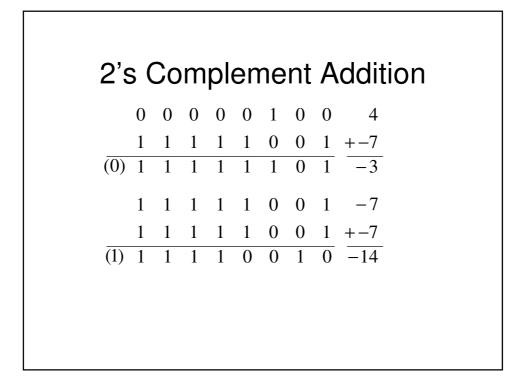

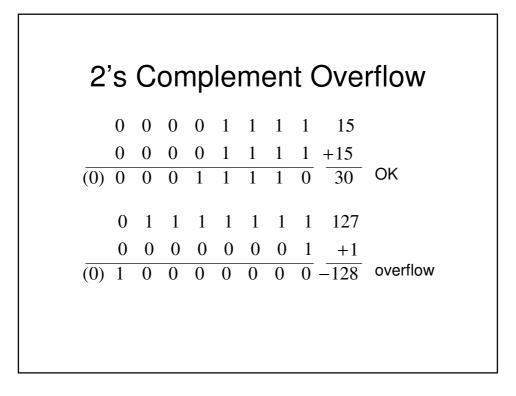

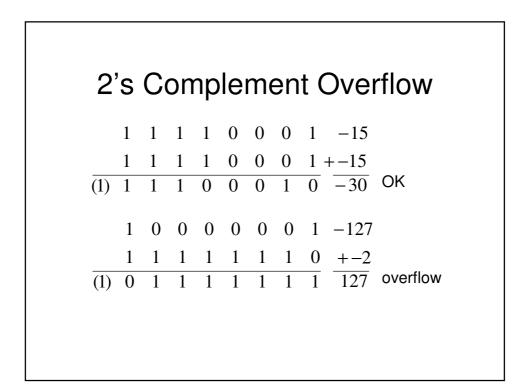

# 2's Complement Overflow

- For example, when working with 8-bit unsigned numbers, we can use the 'carry' from the 8th bit (MSB) to indicate that the number has got too big.

- With *signed* numbers we deliberately ignore any carry from the MSB, consequently we need a new rule to detect when a result is out of range.

### **Multilevel Logic**

- We have seen previously how we can minimise Boolean expressions to yield so called '2-level' logic implementations, i.e., SOP (ANDed terms ORed together) or POS (ORed terms ANDed together)

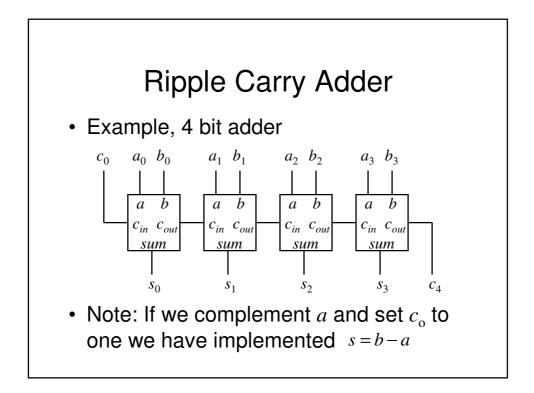

- Note also we have also seen an example of 'multilevel' logic, i.e., full adders cascaded to form a ripple carry adder – see we have more than 2 gates in cascade in the carry chain

### **Common Expression Elimination**

- We can recursively factor out common literals z = a.d.f + a.e.f + b.d.f + b.e.f + c.d.f + c.e.f + g z = (a.d + a.e + b.d + b.e + c.d + c.e).f + g z = ((a+b+c).d + (a+b+c).e).f + gz = (a+b+c).(d+e).f + g

- Now express *z* as a number of equations in 2-level form:

x = a + b + c y = d + e z = x.y.f + g

• 4 gates, 9 literals, 3-levels

### Gate Propagation Delay

- The cumulative delay owing to a number of gates in cascade can increase the time before the output of a combinational logic circuit becomes valid

- For example, in the Ripple Carry Adder, the sum at its output will not be valid until any carry has 'rippled' through possibly every full adder in the chain – clearly the MSB will experience the greatest potential delay

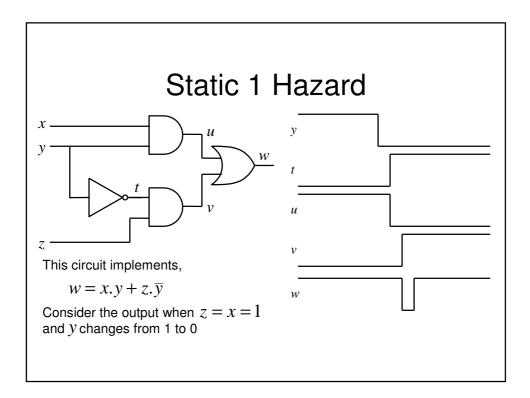

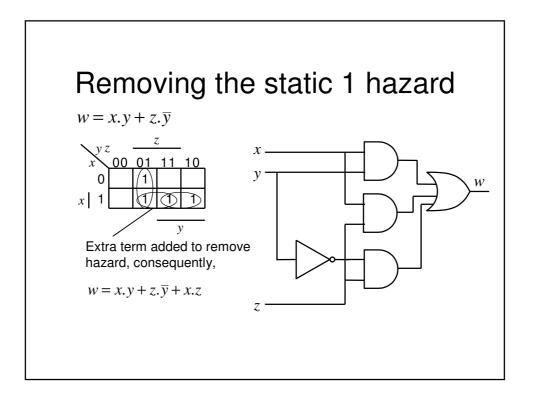

# Hazards

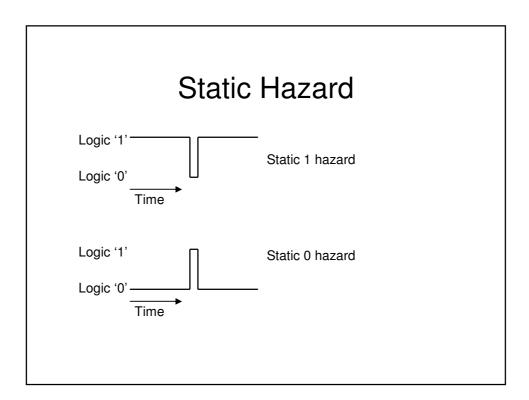

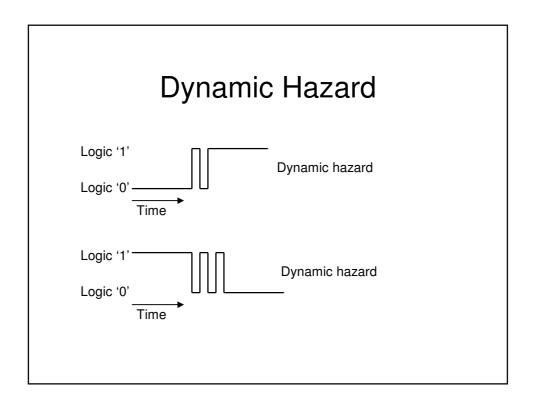

- Hazards are classified into two types, namely, static and dynamic

- Static Hazard The output undergoes a momentary transition when it is supposed to remain unchanged

- Dynamic Hazard The output changes more than once when it is supposed to change just once

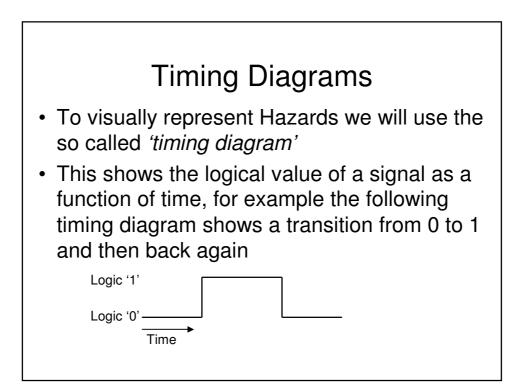

# **Timing Diagrams**

- Note that the timing diagram makes a number simplifying assumptions (to aid clarity) compared with a diagram which accurately shows the actual voltage against time

- The signal only has 2 levels. In reality the signal may well look more 'wobbly' owing to electrical noise pick-up etc.

- The transitions between logic levels takes place instantaneously, in reality this will take a finite time.

# To Speed up Ripple Carry Adder

- Abandon compositional approach to the adder design, i.e., do not build the design up from full-adders, but instead design the adder as a block of 2-level combinational logic with 2n inputs (+1 for carry in) and n outputs (+1 for carry out).

- Features

- Low delay (2 gate delays)

- Need some gates with large numbers of inputs (which are not available)

- Very complex to design and implement (imagine the truth table!

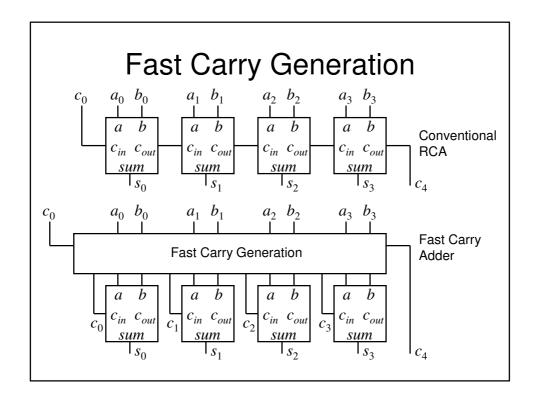

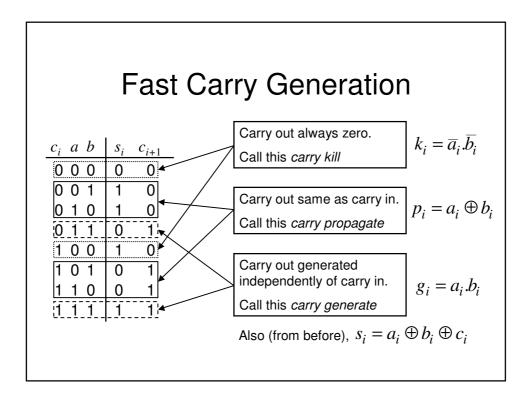

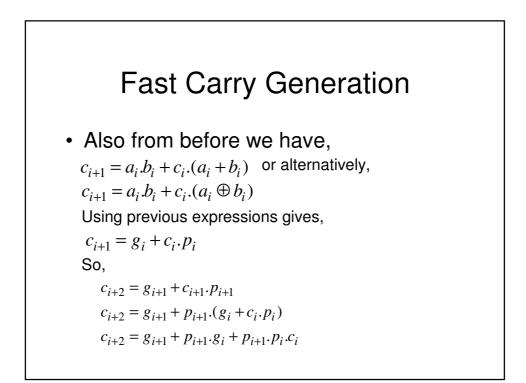

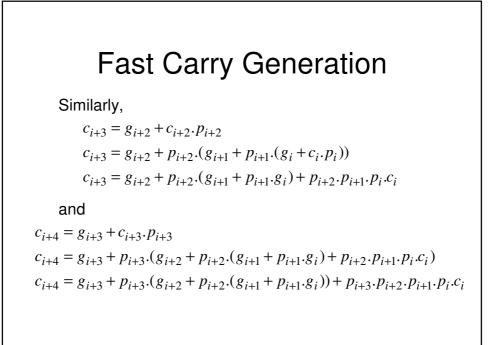

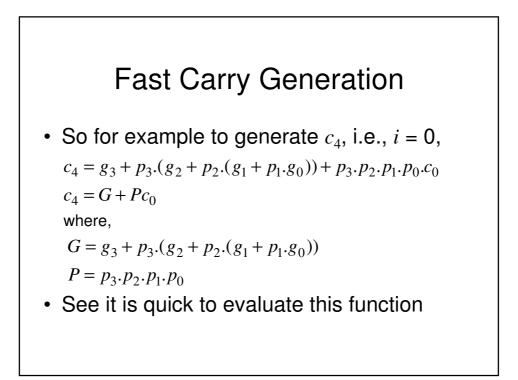

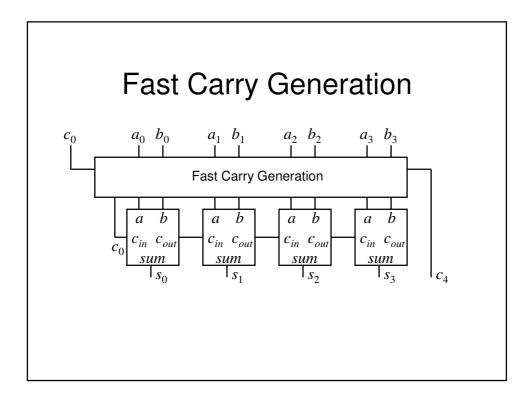

# Fast Carry Generation

- We could generate all the carrys within an adder block using the previous equations

- However, in order to reduce complexity, a suitable approach is to implement say 4-bit adder blocks with only c<sub>4</sub> generated using fast generation.

- This is used as the carry-in to the next 4-bit adder block

- Within each 4-bit adder block, conventional RCA is used

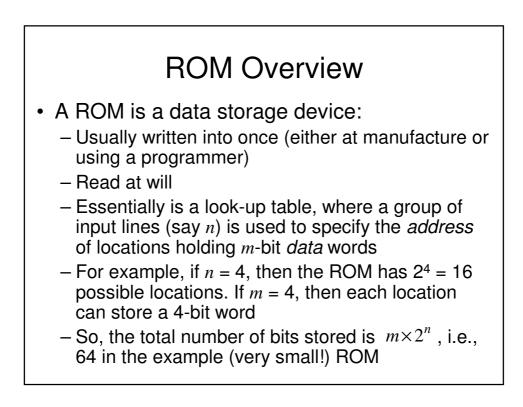

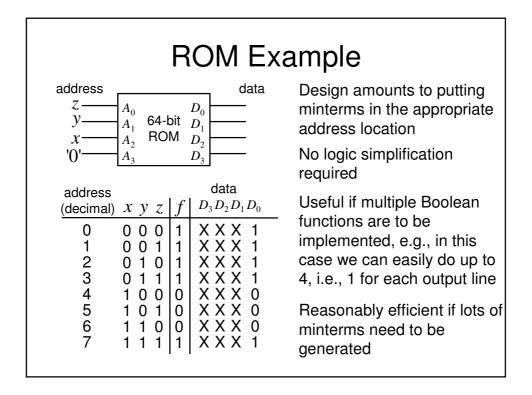

### Other Ways to Implement Combinational Logic

- We have seen how combinational logic can be implemented using logic gates, e.g., AND, OR etc.

- However, it is also possible to generate combinational logic functions using memory devices, e.g., Read Only Memories (ROMs)

# Memory Application Memory devices are often used in computer systems The central processing unit (CPU) often makes use of busses (a bunch of wires in parallel) to access external memory devices The *address bus* is used to specify the memory location that is being read or written and the data bus conveys the data too and from that location

• So, more than one memory device will often be connected to the same data bus

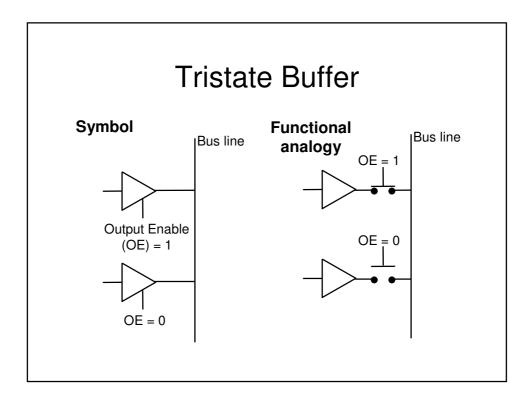

# **Control Signals**

- We have already seen that the memory devices have an additional control input (OE) that determines whether the output buffers are enabled.

- Other control inputs are also provided:

- Write enable (WE). Determines whether data is written or read (clearly not needed on a ROM)

- Chip select (CS) determines if the chip is activated

- Note that these signals can be active low, depending upon the particular device

# Sequential Logic

- The logic circuits discussed previously are known as *combinational*, in that the output depends only on the condition of the latest inputs

- However, we will now introduce a type of logic where the output depends not only on the latest inputs, but also on the condition of earlier inputs. These circuits are known as *sequential*, and implicitly they contain *memory* elements

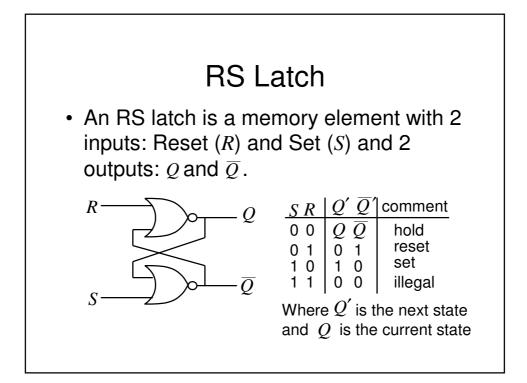

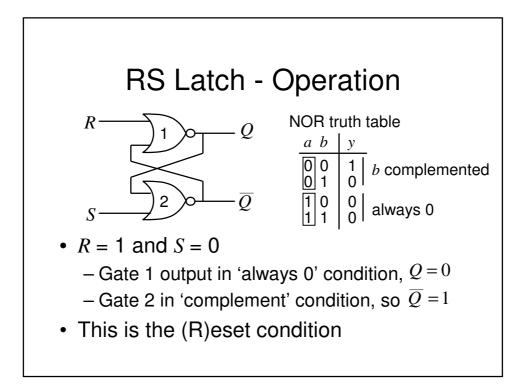

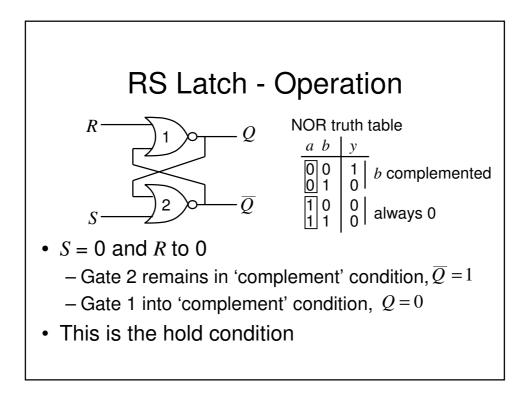

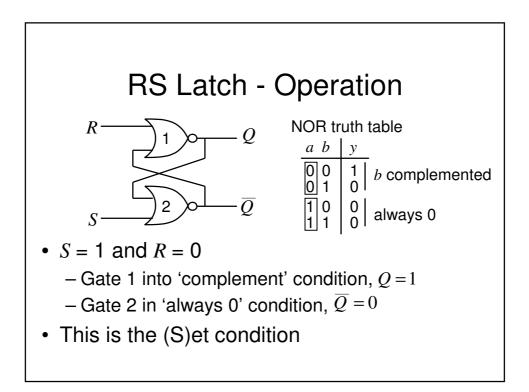

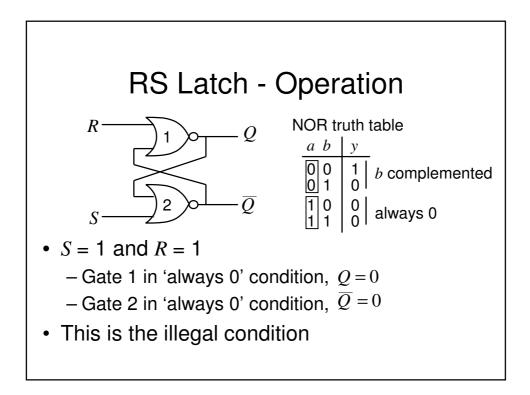

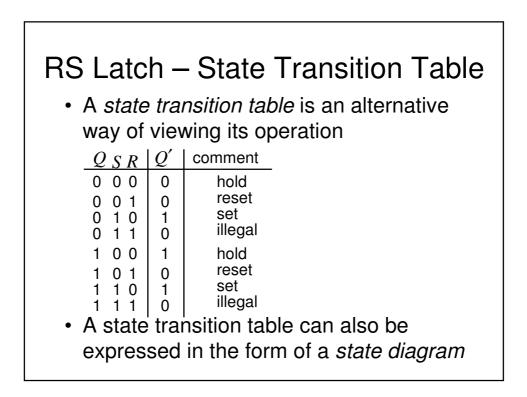

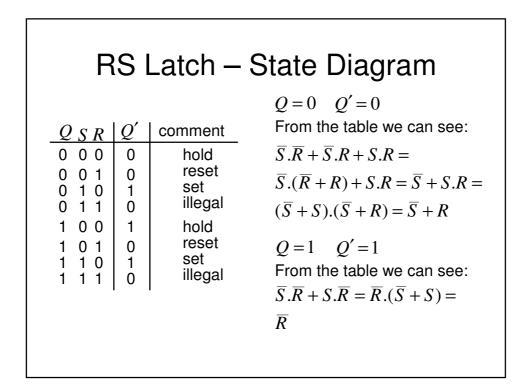

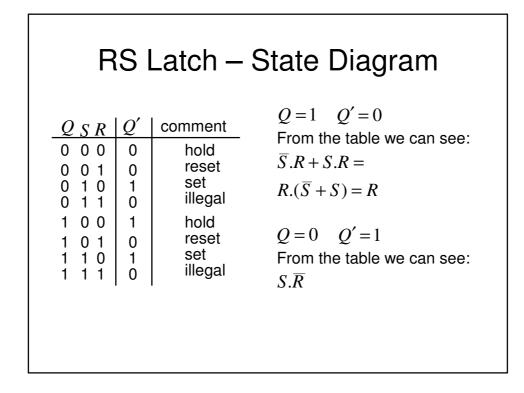

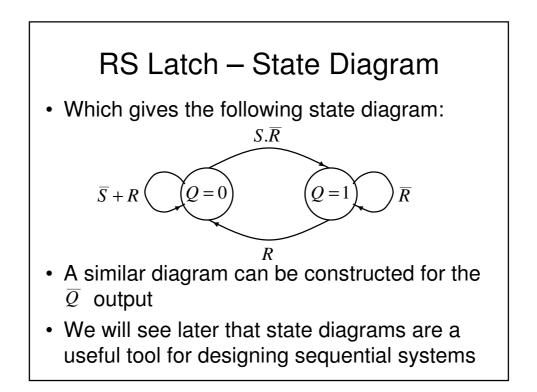

### RS Latch – State Diagram

- A state diagram in this case has 2 states, i.e., Q=0 and Q=1

- The state diagram shows the input conditions required to transition between states. In this case we see that there are 4 possible transitions

- · We will consider them in turn

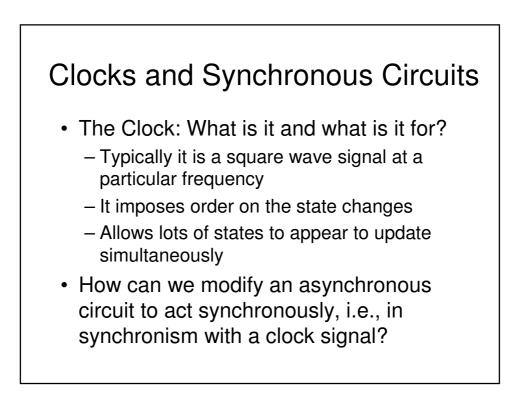

### **Clocks and Synchronous Circuits**

- For the RS latch we have just described, we can see that the output state changes occur directly in response to changes in the inputs. This is called *asynchronous* operation

- However, virtually all sequential circuits currently employ the notion of synchronous operation, that is, the output of a sequential circuit is constrained to change only at a time specified by a global *enabling* signal. This signal is generally known as the system *clock*

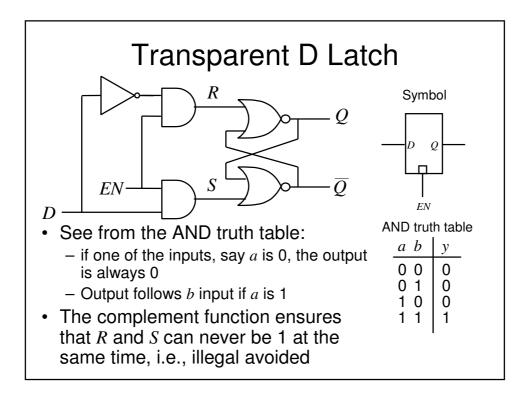

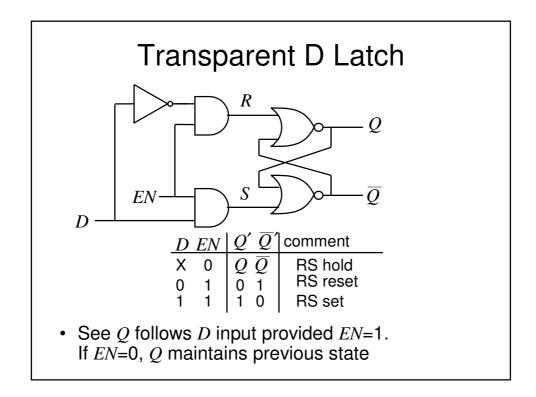

# Transparent D Latch

- We now modify the RS Latch such that its output state is only permitted to change when a valid enable signal (which could be the system clock) is present

- This is achieved by introducing a couple of AND gates in cascade with the R and S inputs that are controlled by an additional input known as the *enable* (EN) input.

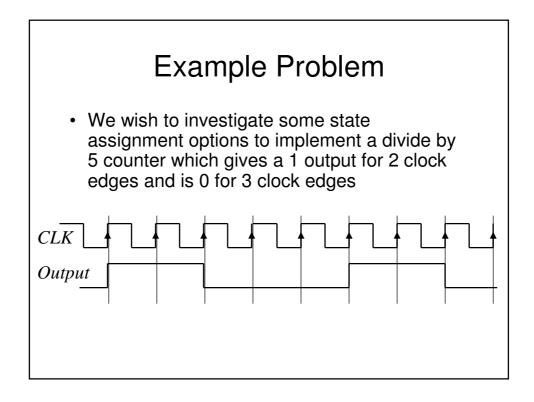

# **Applications of Flip-Flops**

#### Counters

- A clocked sequential circuit that goes through a predetermined sequence of states

- A commonly used counter is an *n*-bit binary counter. This has *n* FFs and 2<sup>n</sup> states which are passed through in the order 0, 1, 2, ....2<sup>n</sup>-1, 0, 1, .

- Uses include:

- Counting

- Producing delays of a particular duration

- Sequencers for control logic in a processor

- Divide by *m* counter (a divider), as used in a digital watch

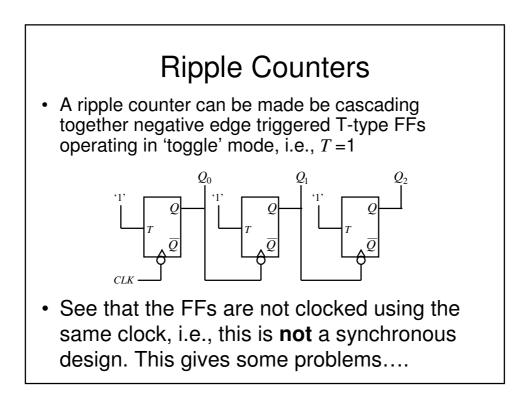

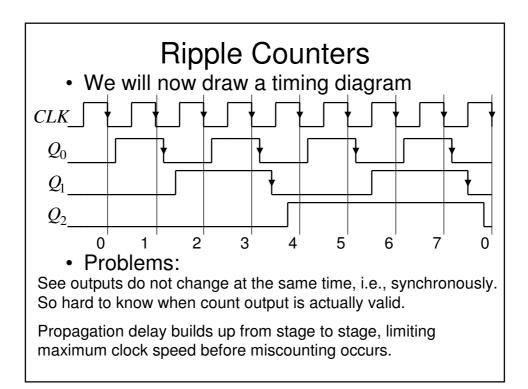

# Counters

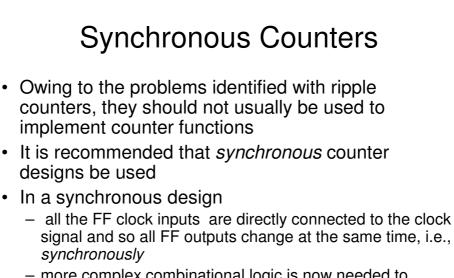

- In most books you will see 2 basic types of counters, namely *ripple* counters and *synchronous* counters

- In this course we are concerned with synchronous design principles. Ripple counters do not follow these principles and should generally be avoided if at all possible. We will now look at the problems with ripple counters

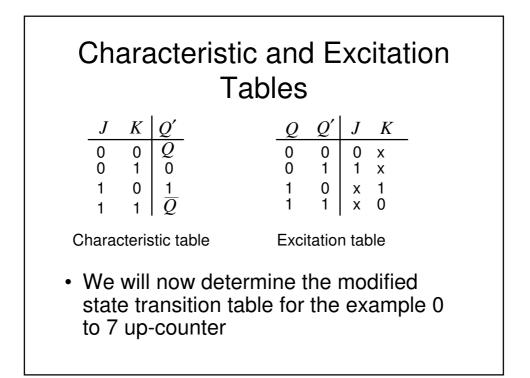

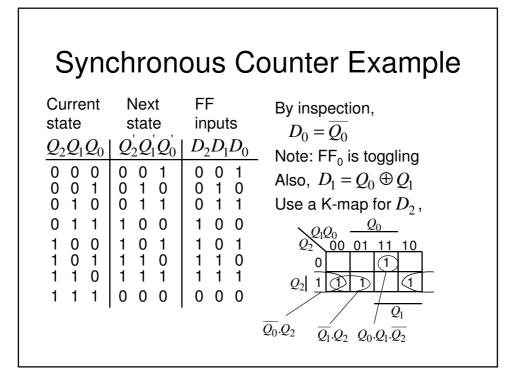

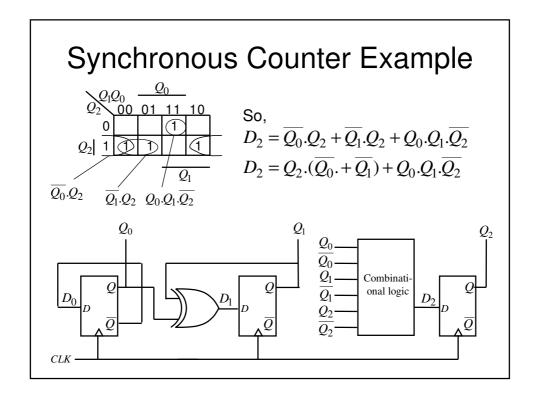

more complex combinational logic is now needed to generate the appropriate FF input signals (which will be different depending upon the type of FF chosen)

# Synchronous Counters

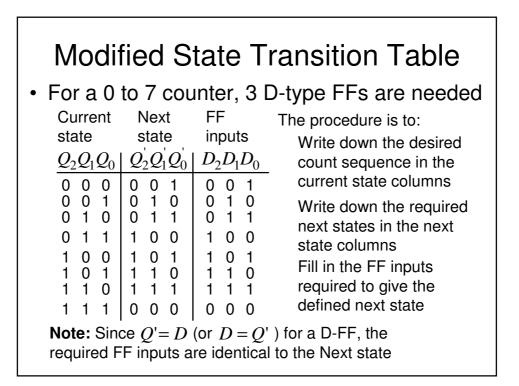

- To assist in the design of the counter we will make use of a modified state transition table. This table has additional columns that define the required FF inputs (or excitation as it is known)

- Note we have used a state transition table previously when determining the state diagram for an RS latch

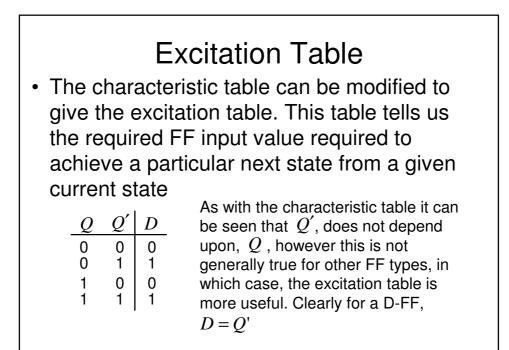

- We will also make use of the so called '*excitation table*' for a D-type FF

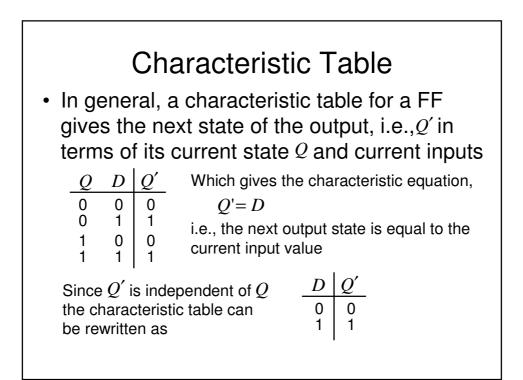

- First however, we will investigate the so called *characteristic table* and *characteristic equation* for a D-type FF

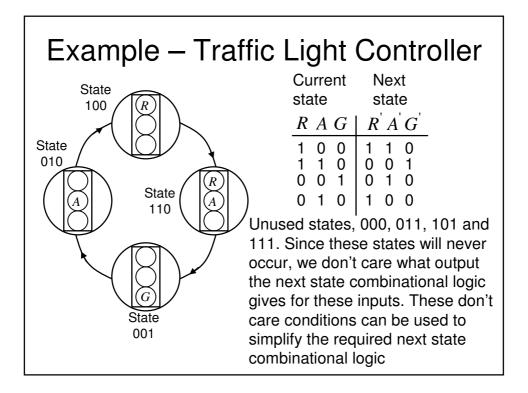

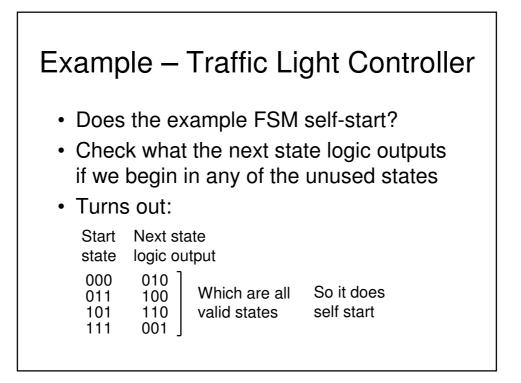

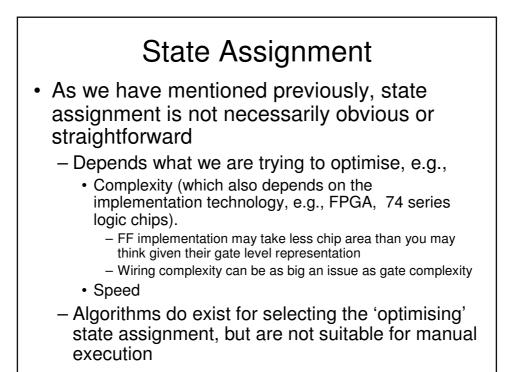

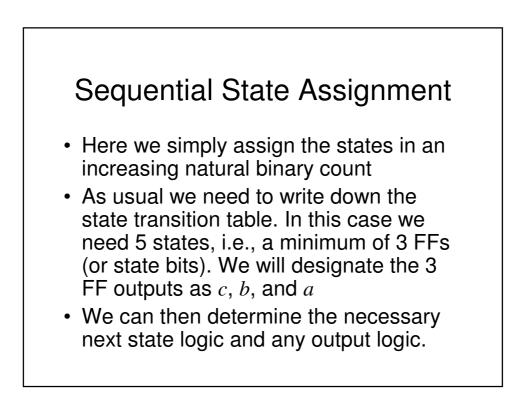

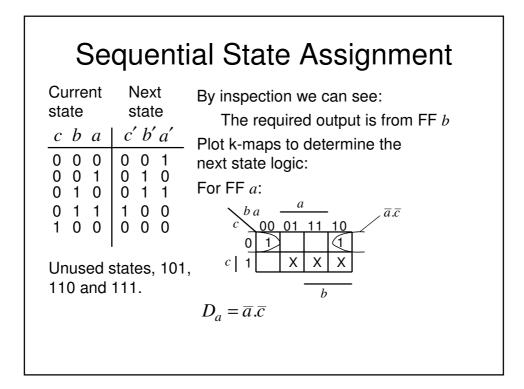

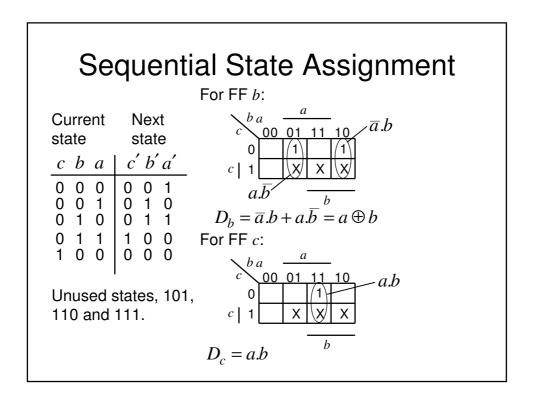

# Synchronous Counter

- A similar procedure can be used to design counters having an arbitrary count sequence

- Write down the state transition table

- Determine the FF excitation (easy for D-types)

- Determine the combinational logic necessary to generate the required FF excitation from the current states – Note: remember to take into account any unused counts since these can be used as don't care states when determining the combinational logic circuits

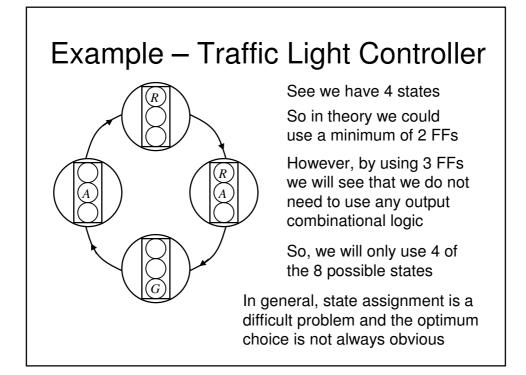

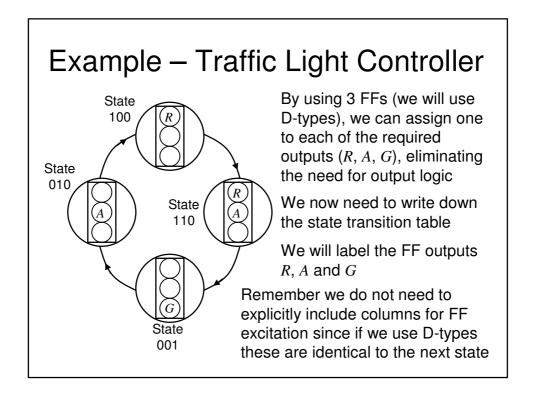

### Synchronous State Machines

- We have seen how we can use FFs (D-types in particular) to design synchronous counters

- We will now investigate how these principles can be extended to the design of synchronous state machines (of which counters are a subset)

- We will begin with some definitions and then introduce two popular types of machines

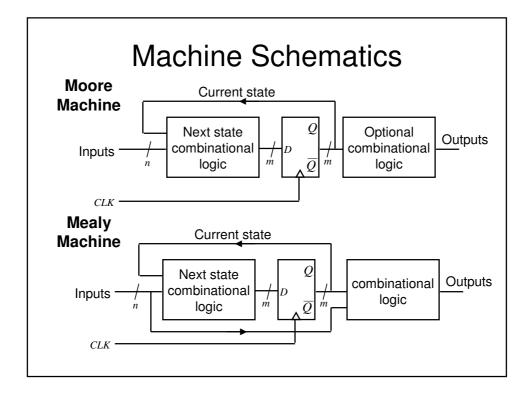

# Moore vs. Mealy Machines

- Outputs from Mealy Machines depend upon the timing of the inputs

- Outputs from Moore machines come directly from clocked FFs so:

- They have guaranteed timing characteristics

- They are glitch free

- Any Mealy machine can be converted to a Moore machine and vice versa, though their timing properties will be different

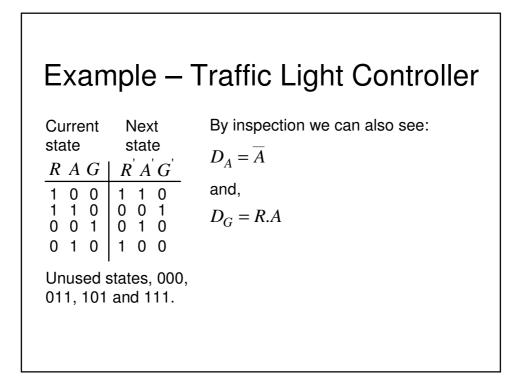

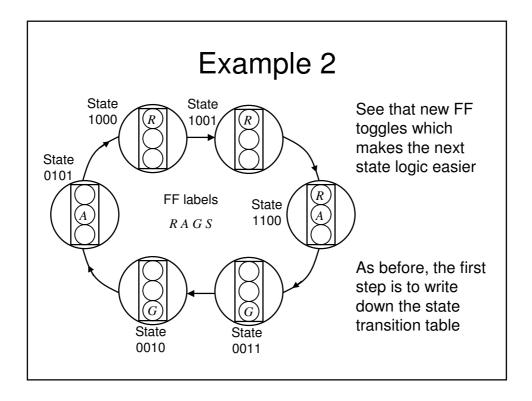

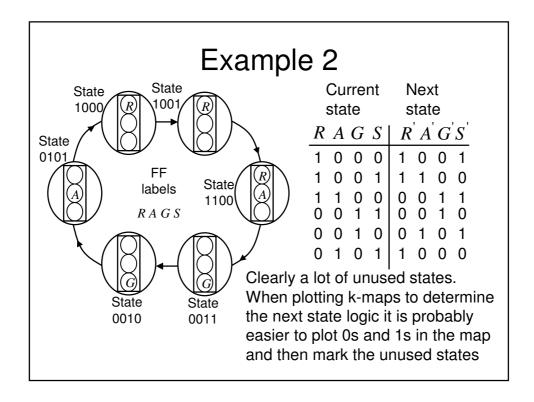

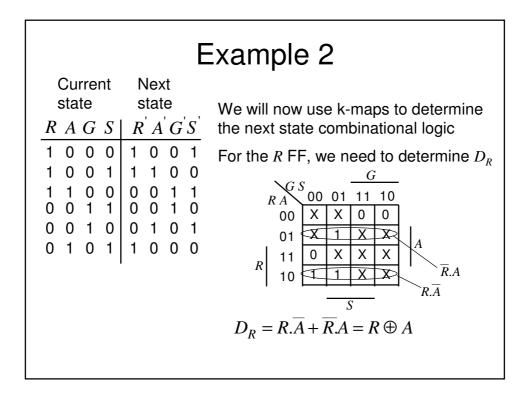

| Example 2                                             |                                                                 |  |

|-------------------------------------------------------|-----------------------------------------------------------------|--|

| Current Next                                          |                                                                 |  |

| state state                                           | We can plot k-maps for $D_A$ and $D_G$                          |  |

| R A G S   R' A' G' S'                                 | to give:                                                        |  |

| 10001001                                              | $D_A = R.S + G.\overline{S}$ or                                 |  |

| 10011100                                              | $D_A = R.S + \overline{R}.\overline{S} = \overline{R \oplus S}$ |  |

|                                                       |                                                                 |  |

| 00110010                                              | $D_G = R.A + G.S$ or                                            |  |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $D_G = G.S + A.\overline{S}$                                    |  |

|                                                       | By inspection we can also see:                                  |  |

|                                                       | $D_S = \overline{S}$                                            |  |

|                                                       | 5                                                               |  |

|                                                       |                                                                 |  |

|                                                       |                                                                 |  |

|                                                       |                                                                 |  |

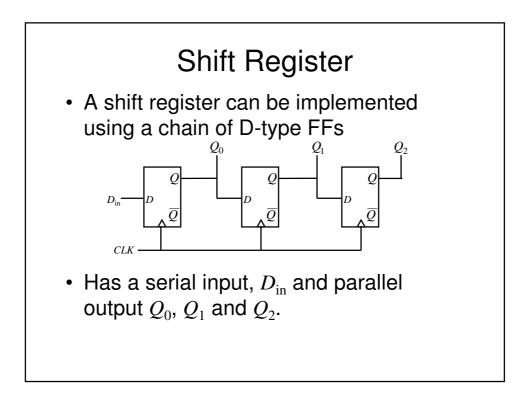

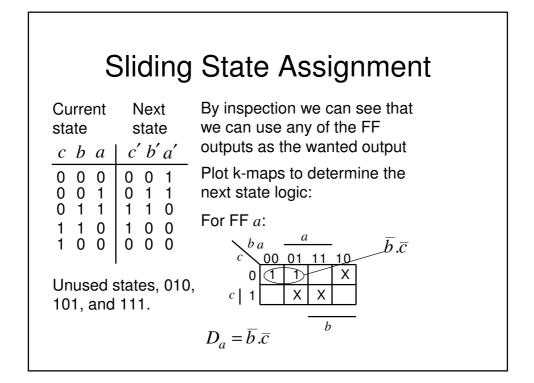

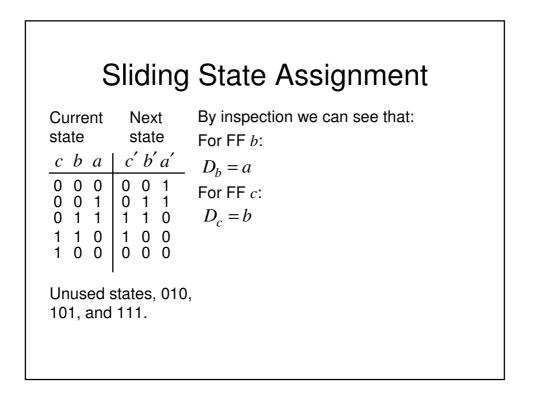

### Shift Register Assignment

- As the name implies, the FFs are connected together to form a shift register. In addition, the output from the final shift register in the chain is connected to the input of the first FF:

- Consequently the data continuously cycles through the register

| Shift Register Assignment                                                                                              |                                                                                                                                                 |  |

|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Current<br>stateNext<br>state $e \ d \ c \ b \ a \ e' \ d' \ c' \ b' \ a'$ $0 \ 0 \ 0 \ 1 \ 1 \ 0 \ 0 \ 1 \ 1 \ 0 \ 0$ | $\begin{array}{l} D_a = e \\ D_b = a \\ D_c = b \\ D_d = c \\ D_e = d \end{array}$<br>By inspection we can see that<br>we can use any of the FF |  |

| outputs as the wanted output<br>See needs 2 more FFs, but no logic and simple wiring                                   |                                                                                                                                                 |  |

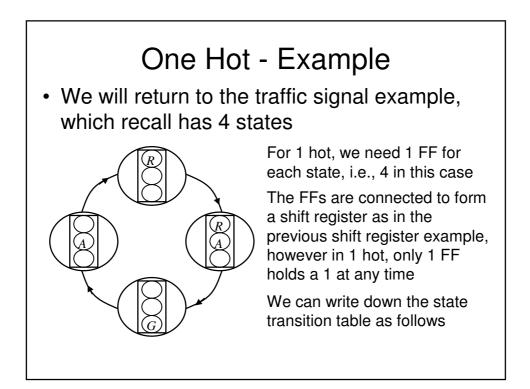

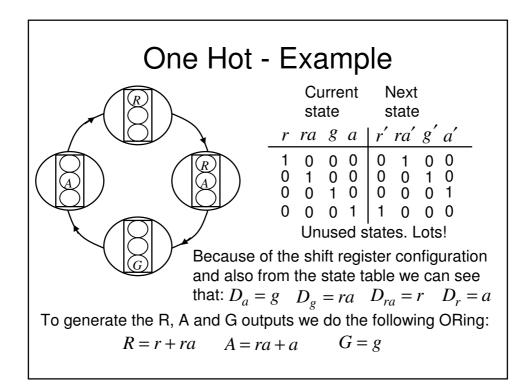

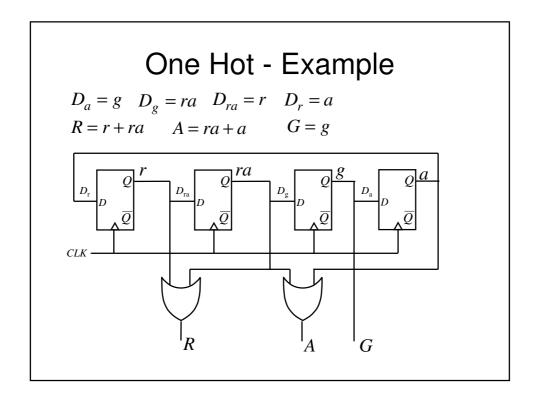

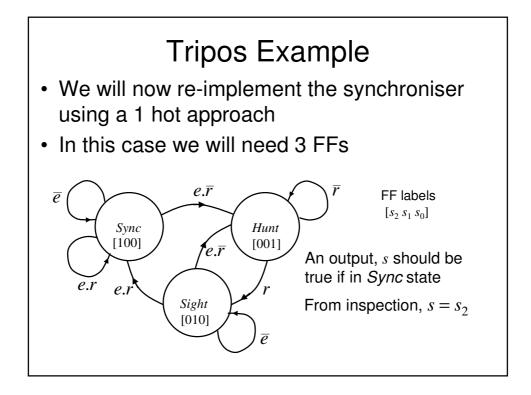

# One Hot State Encoding

- This is a shift register design style where only one FF at a time holds a 1

- Consequently we have 1 FF per state, compared with log<sub>2</sub> m for sequential assignment

- However, can result in simple fast state machines

- Outputs are generated by ORing together appropriate FF outputs

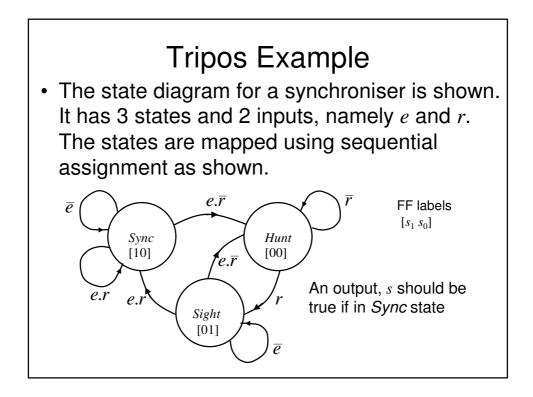

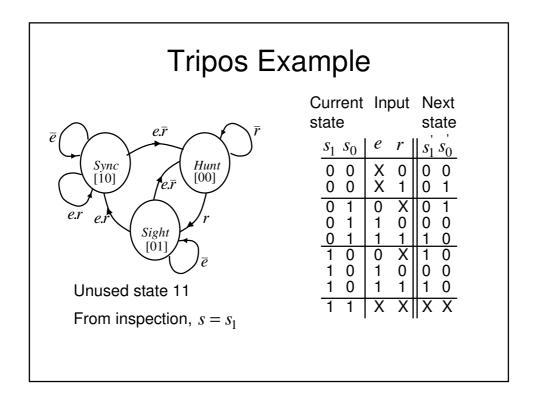

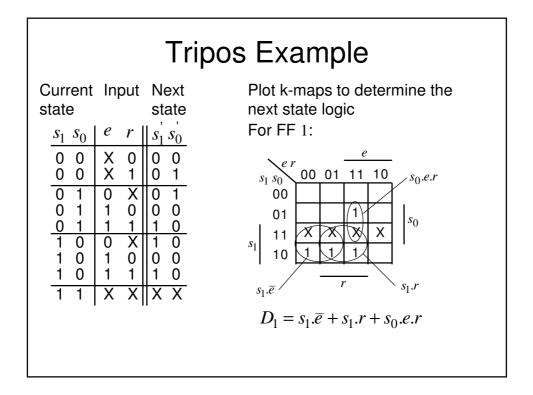

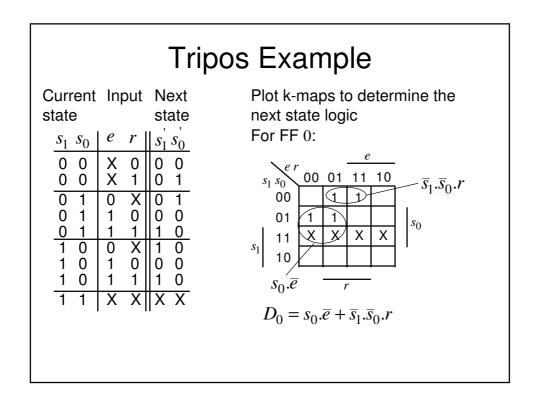

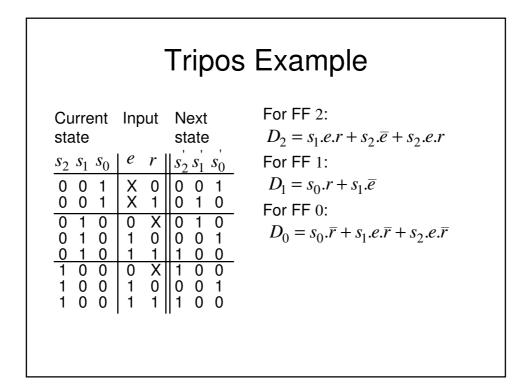

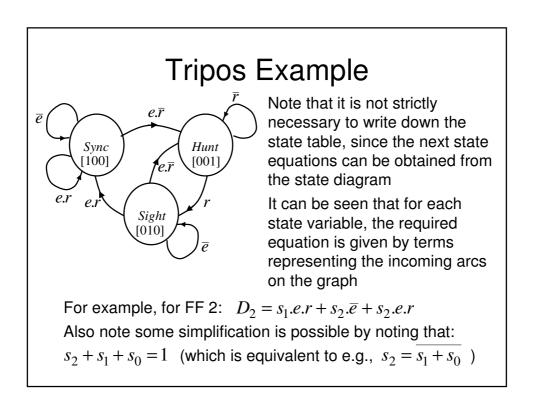

# **Tripos Example**

So in this example, the 1 hot is easier to design, but it results in more hardware compared with the sequential state assignment design

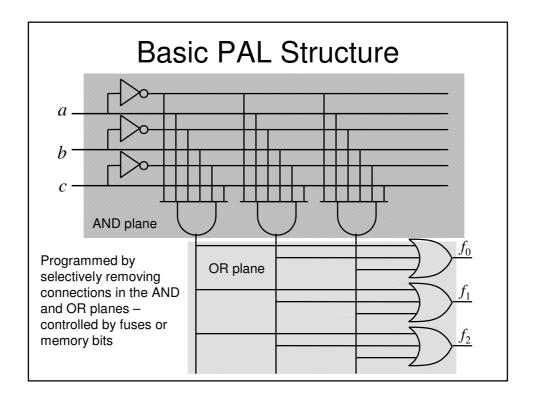

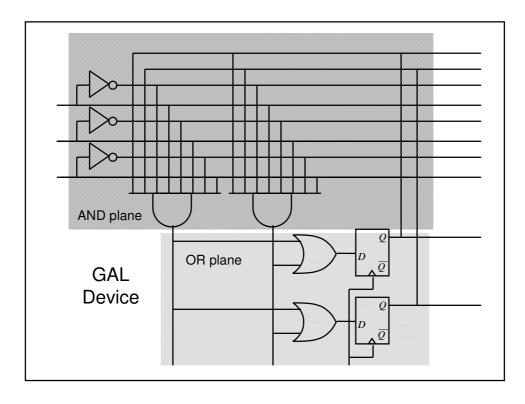

### **GAL** Devices

They are similar in concept to PALs, but have the option to make use of a D-type flipflops in the OR plane (one following each OR gate). In addition, the outputs from the Dtypes are also made available to the AND plane (in addition to the usual inputs)

Consequently it becomes possible to build programmable sequential logic circuits

# FPGA

- Field Programmable Gate Array (FPGA) devices are the latest type of programmable logic

- Are a sea of programmable wiring and function blocks controlled by bits downloaded from memory

- Function units contain a 4-input 1 output lookup table with an optional D-FF on the output