|   | Tutorial Outline                                                         |                                                                                                                 |  |  |  |

|---|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|

| • | Introduction                                                             |                                                                                                                 |  |  |  |

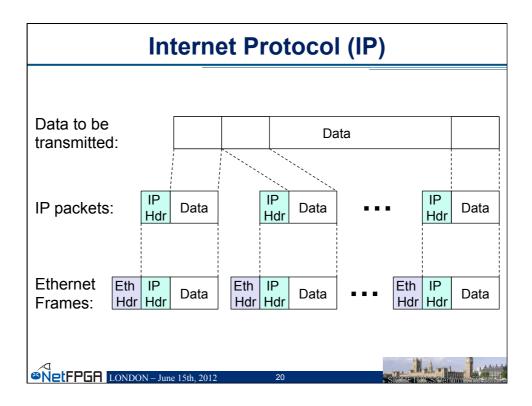

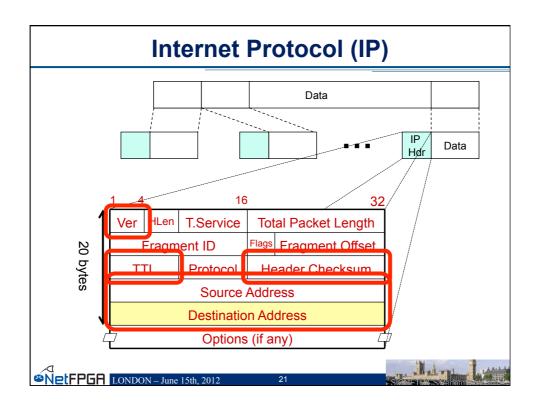

|   | Motivation     Network Review: Basics of an IP Router                    |                                                                                                                 |  |  |  |

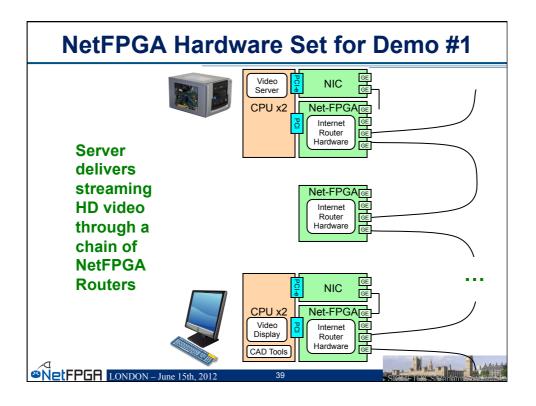

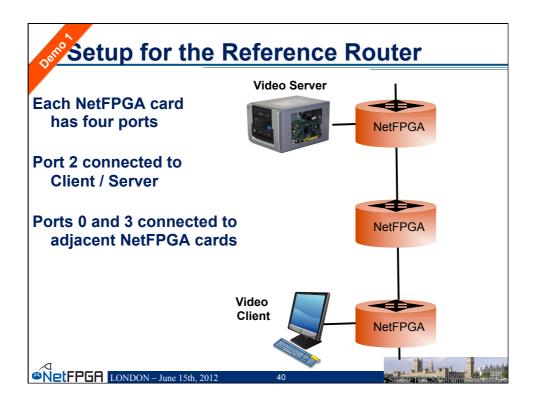

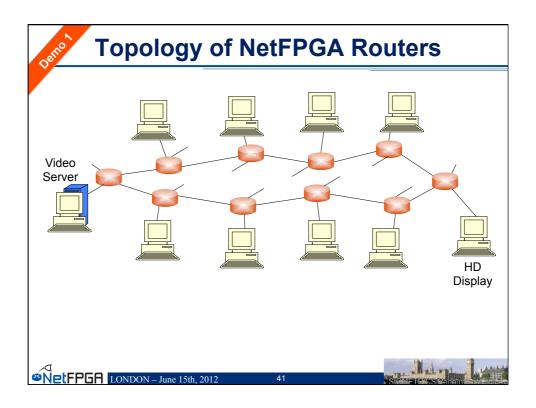

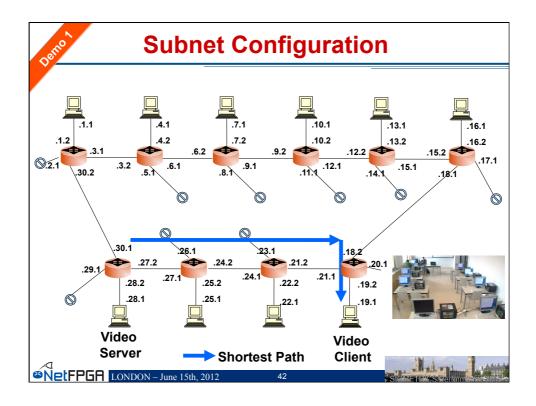

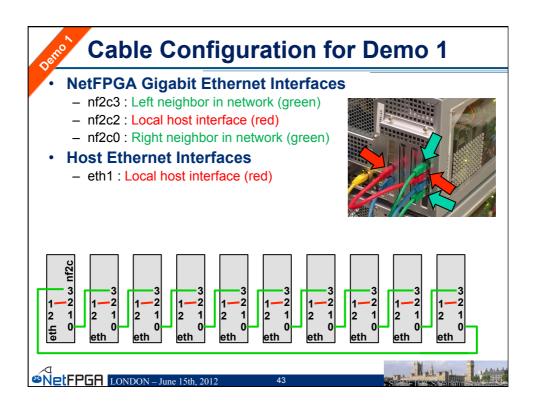

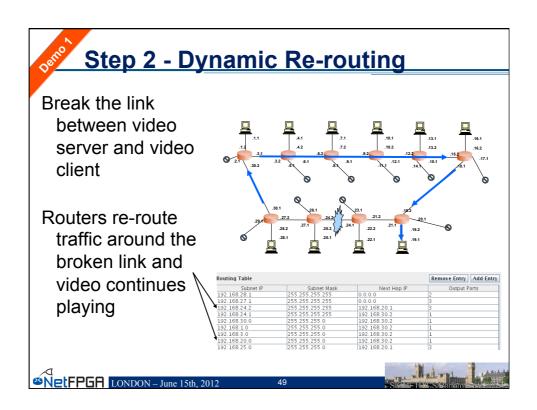

|   | <ul> <li>Demo 1: Reference Router running on the NetFPGA</li> </ul>      |                                                                                                                 |  |  |  |

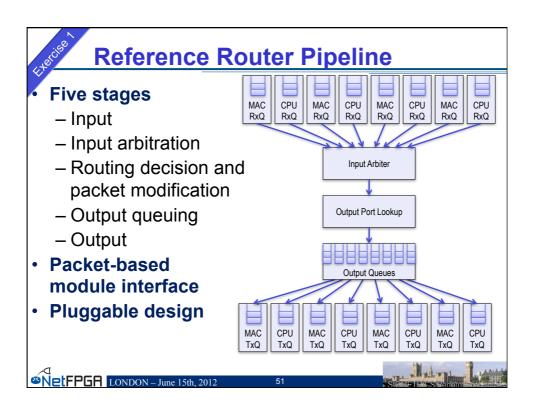

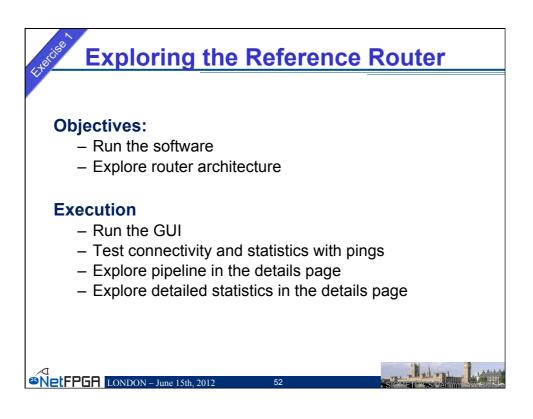

|   | Exercise 1: Exploring the Reference Router                               |                                                                                                                 |  |  |  |

|   | Exercise 1. Exploring the Reference Router                               | 10:30 – 11:00 Coffee/Tea break                                                                                  |  |  |  |

|   | <ul> <li>Hardware · NetEPGA Platforms · 1G and 10G</li> </ul>            |                                                                                                                 |  |  |  |

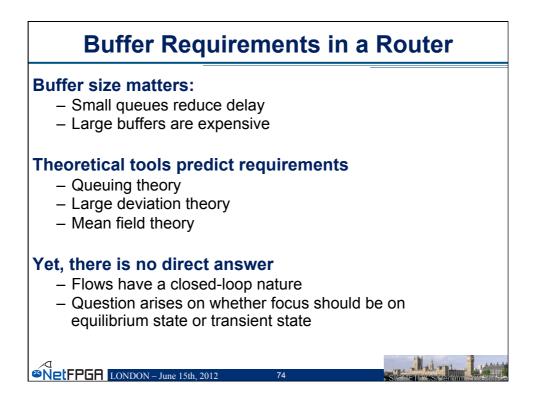

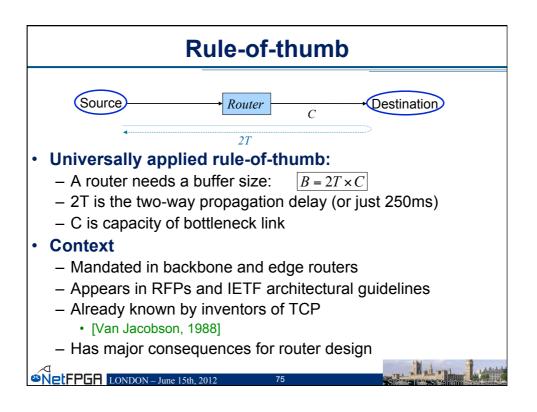

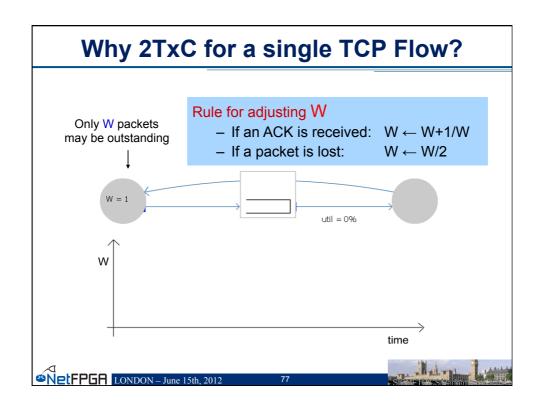

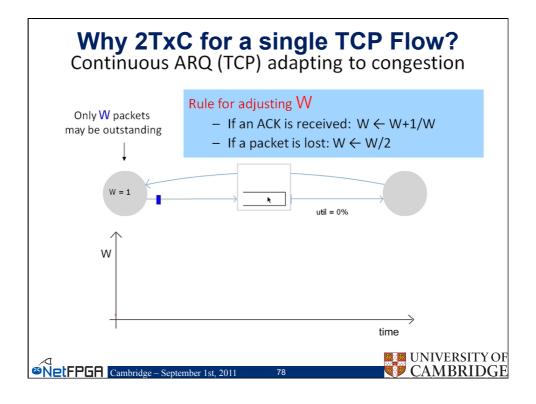

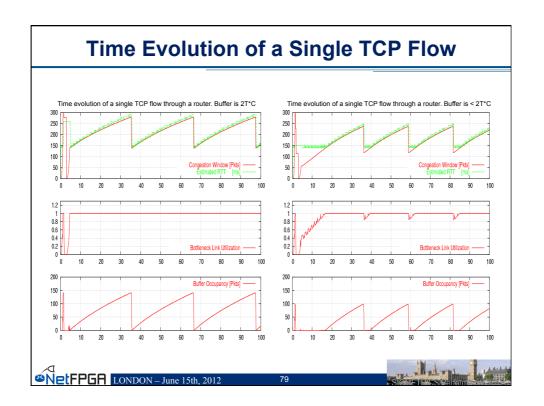

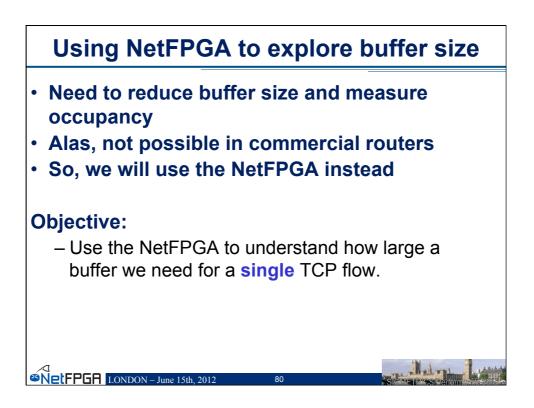

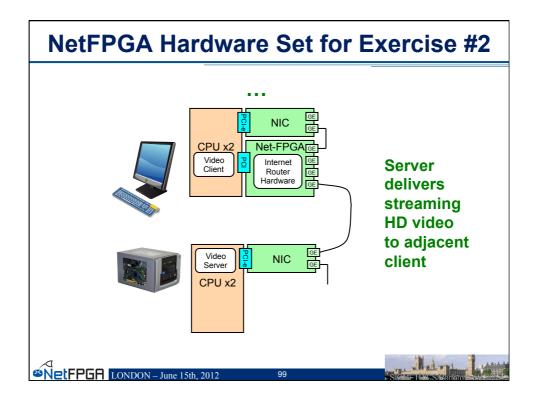

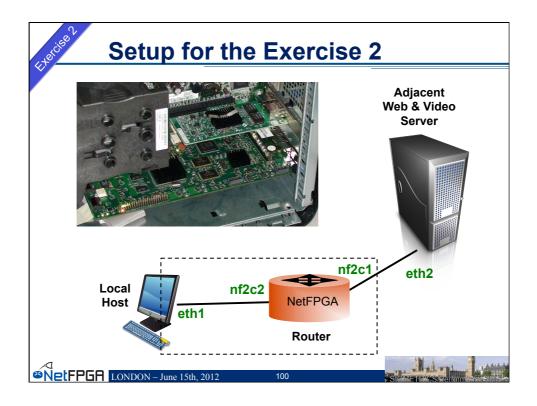

|   | <ul> <li>Problem: Understanding buffer size requirements in a</li> </ul> | router                                                                                                          |  |  |  |

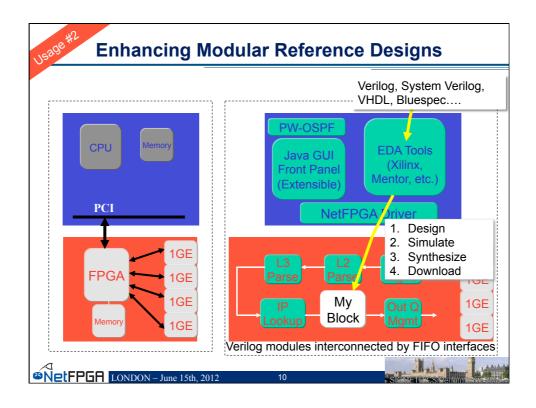

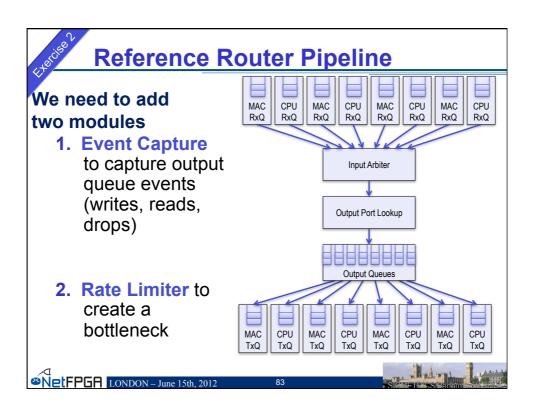

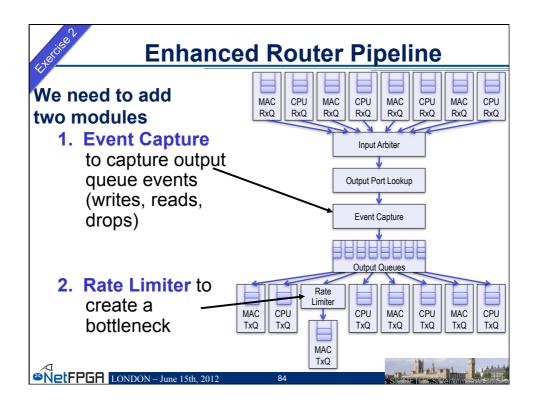

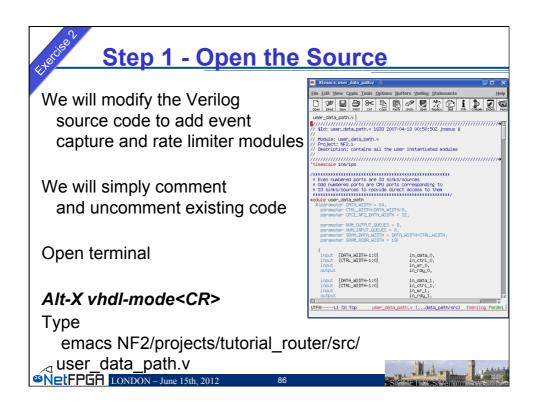

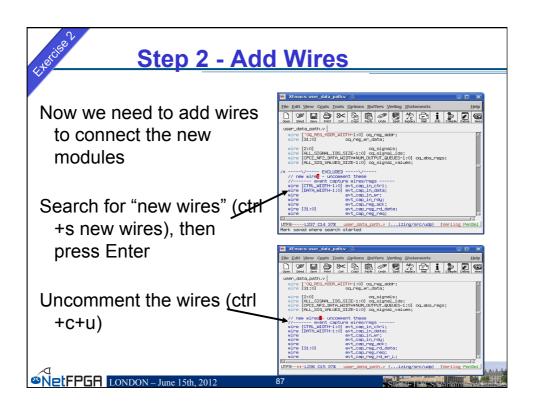

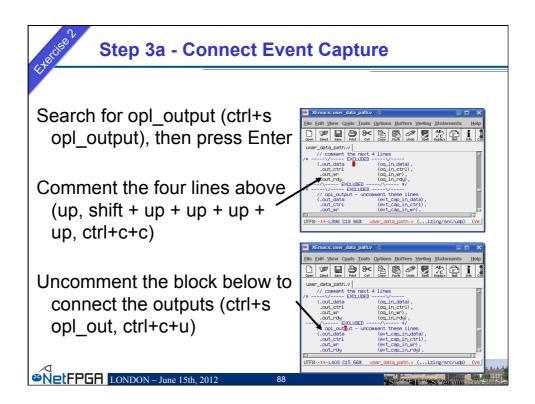

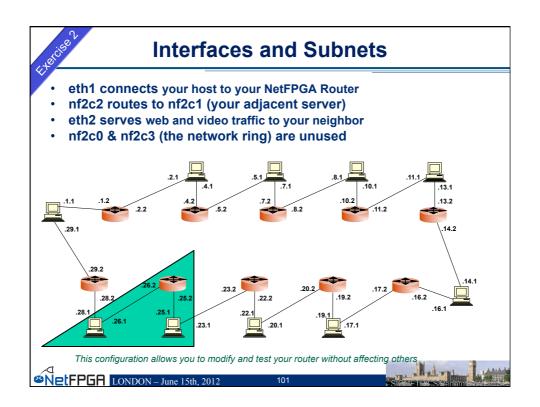

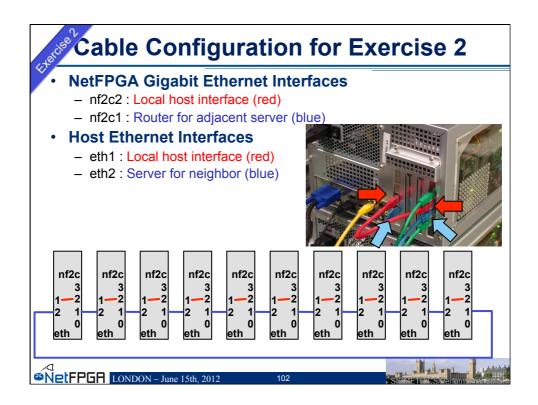

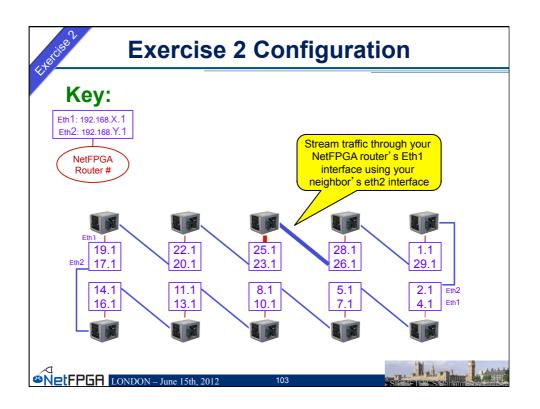

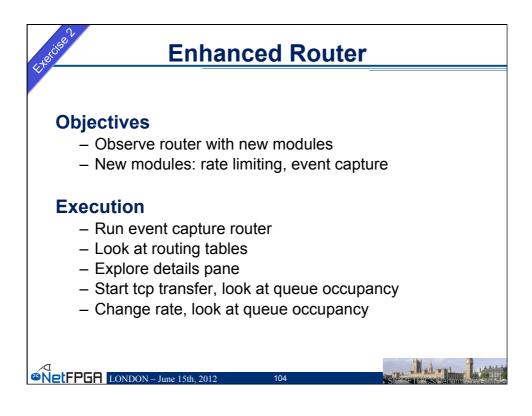

| • | Exercise 2: Enhancing the Reference Router                               |                                                                                                                 |  |  |  |

|   |                                                                          | 12:30 – 13:30 Lunch                                                                                             |  |  |  |

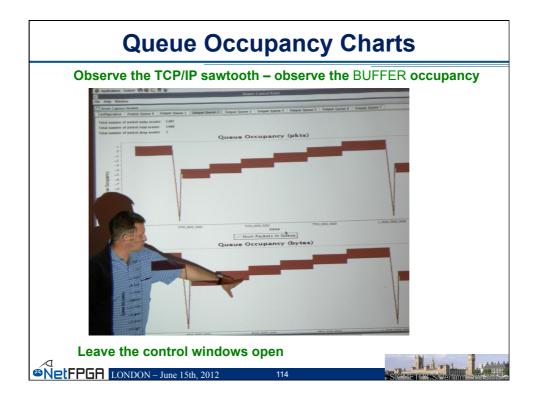

|   | <ul> <li>Observing and controlling the queue size</li> </ul>             |                                                                                                                 |  |  |  |

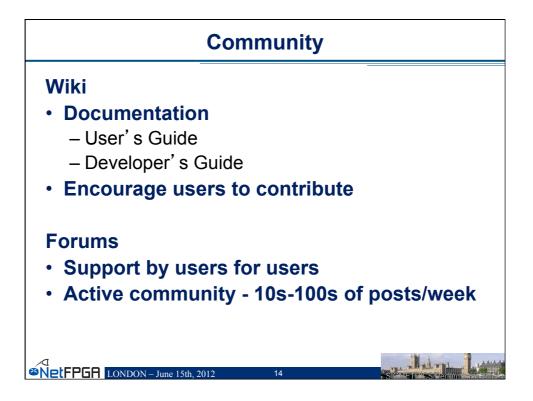

|   | <ul> <li>NetFPGA Community</li> </ul>                                    |                                                                                                                 |  |  |  |

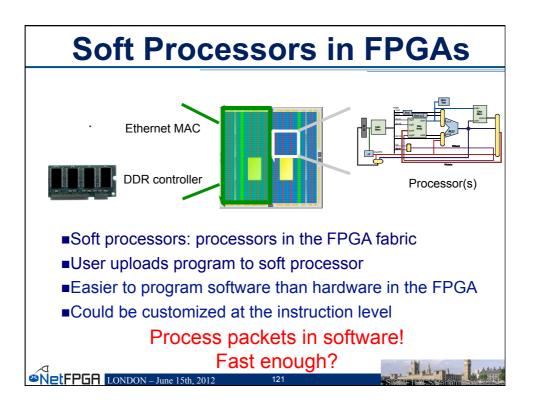

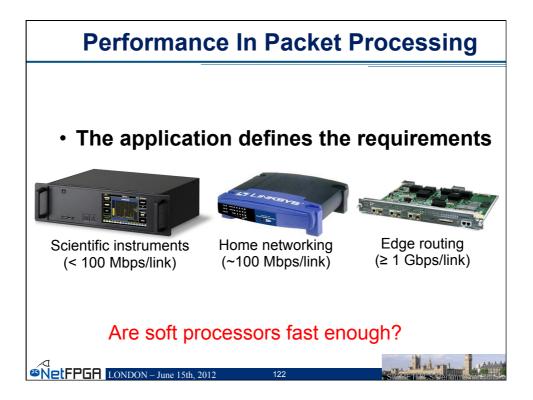

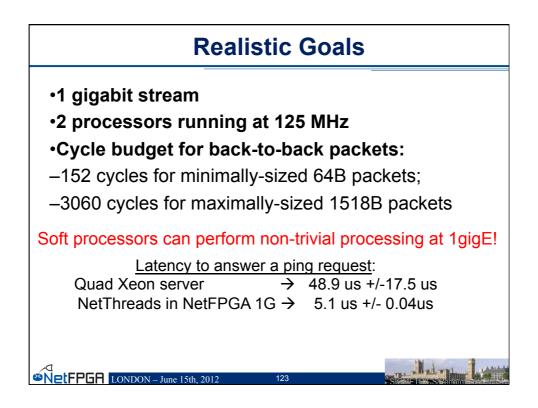

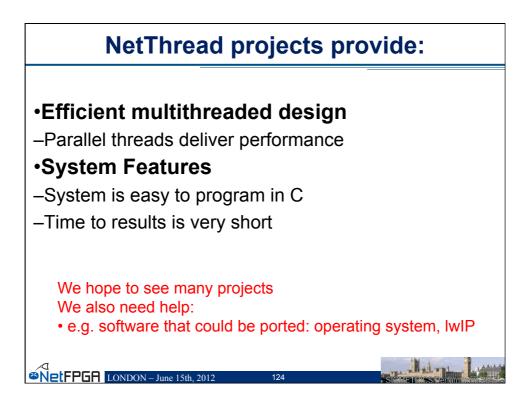

|   | NetThreads                                                               |                                                                                                                 |  |  |  |

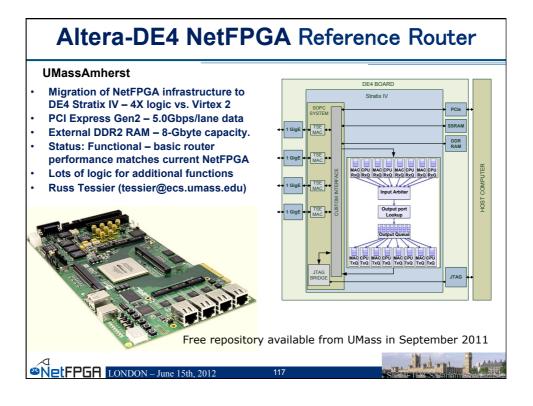

|   | Altera DE4 port                                                          |                                                                                                                 |  |  |  |

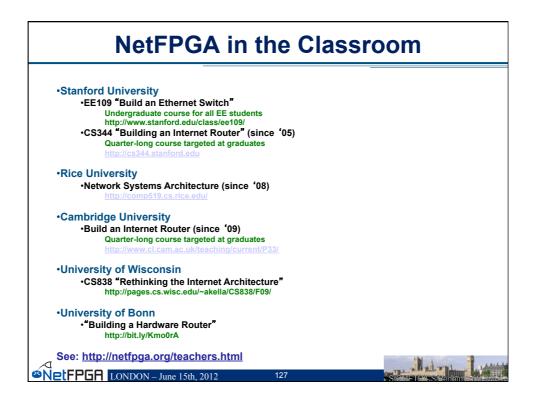

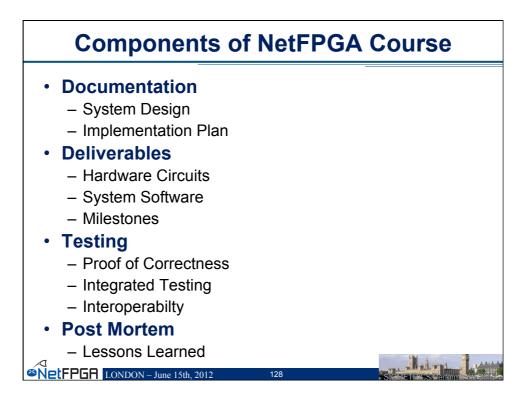

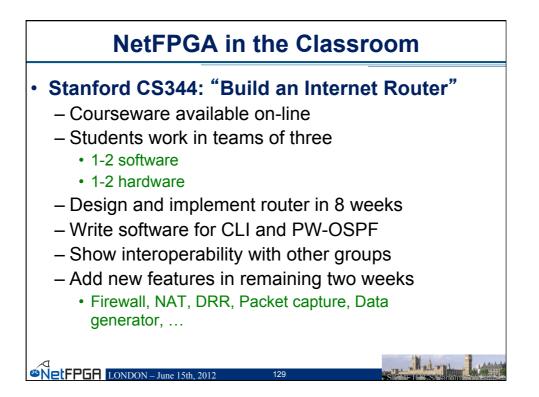

|   | <ul> <li>NetFPGA in the Classroom</li> </ul>                             |                                                                                                                 |  |  |  |

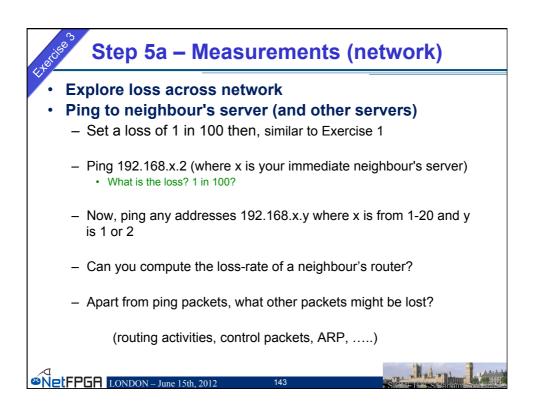

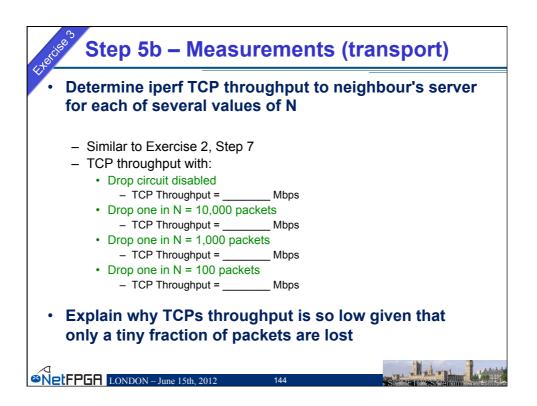

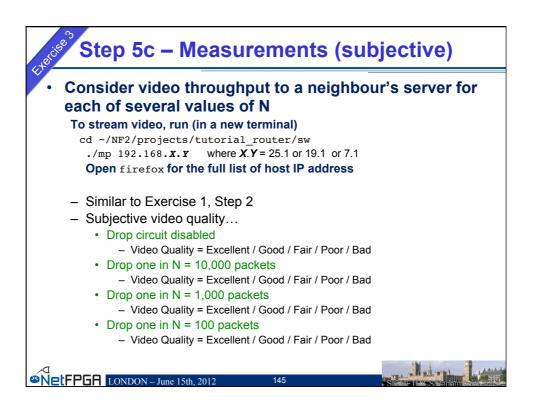

|   | <ul> <li>Problem: Exploring Controlled packet-loss</li> </ul>            |                                                                                                                 |  |  |  |

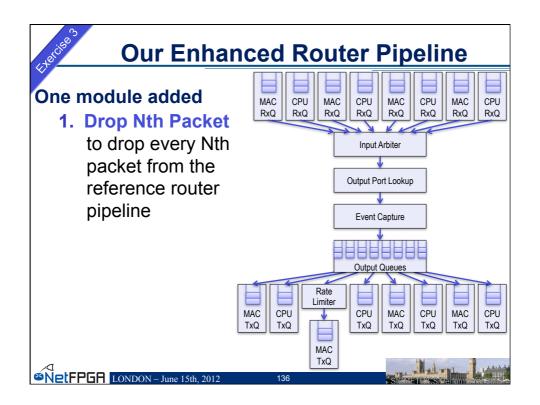

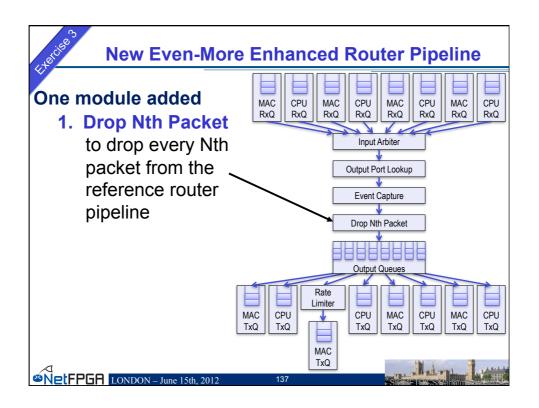

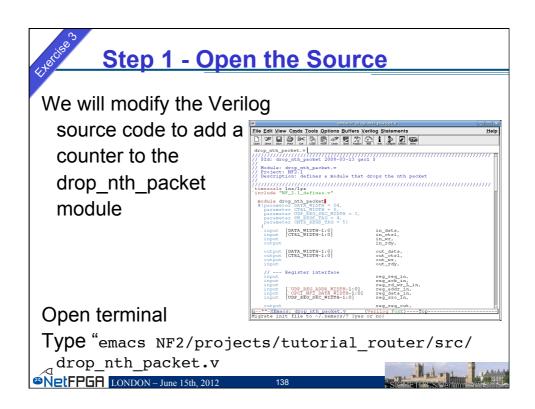

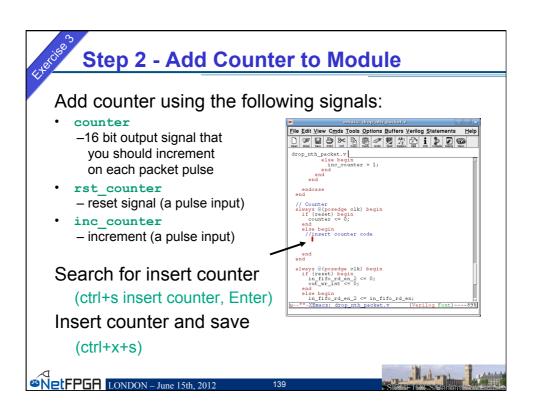

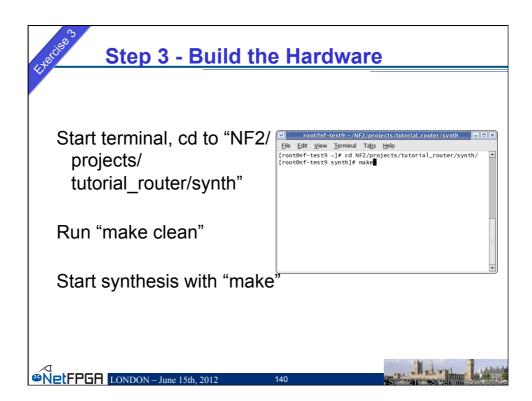

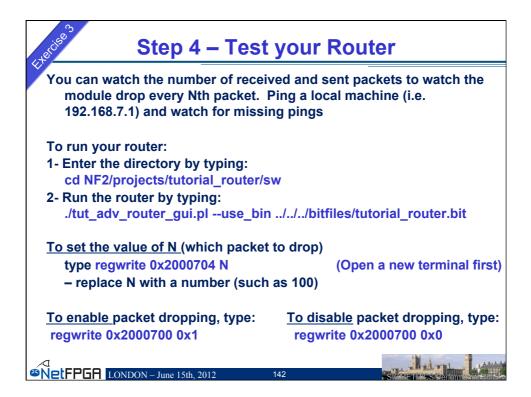

| • | Exercise 3: Drop 1 in N Packets                                          |                                                                                                                 |  |  |  |

|   | O an alextin a Dama alex                                                 | 15:00 – 15:30 Coffee/Tea break                                                                                  |  |  |  |

| • | Concluding Remarks                                                       |                                                                                                                 |  |  |  |

|   | - What next for you?                                                     |                                                                                                                 |  |  |  |

|   | <ul> <li>Group Discussion</li> </ul>                                     |                                                                                                                 |  |  |  |

|   |                                                                          |                                                                                                                 |  |  |  |

| 8 | NetFPGR LONDON – June 15th, 2012 3                                       | A starting to the second se |  |  |  |

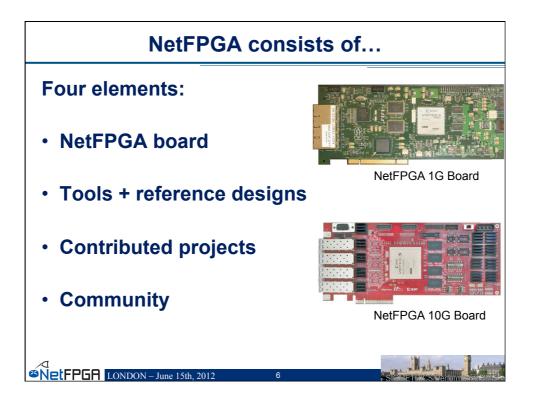

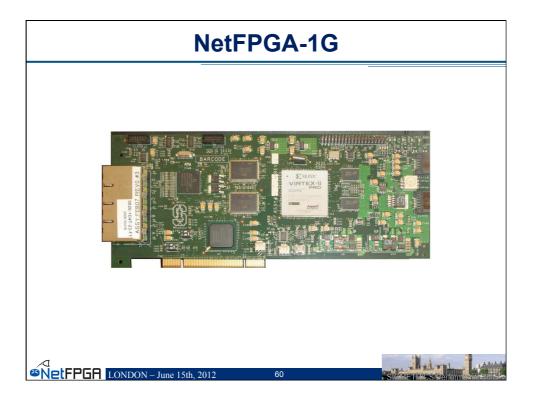

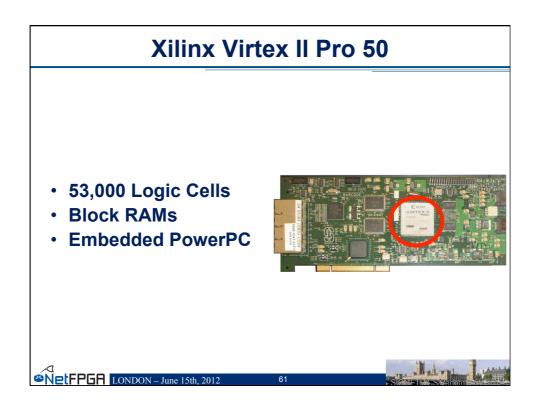

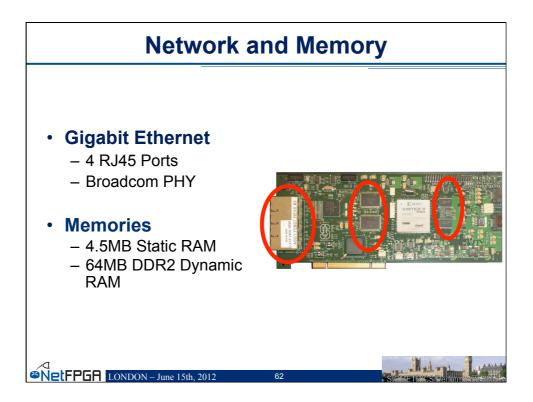

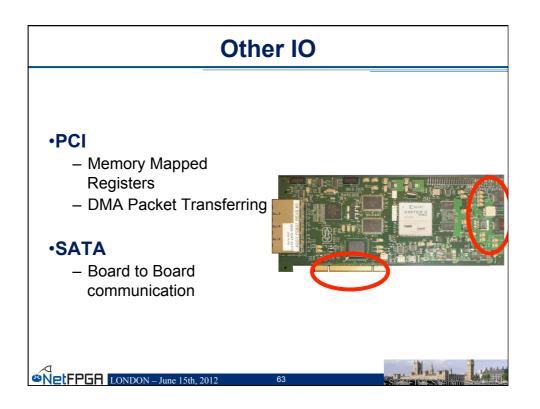

| NetFPGA 1G                          | NetFPGA 10G                          |

|-------------------------------------|--------------------------------------|

| 4 x 1Gbps Ethernet Ports            | 4 x 10Gbps SFP+                      |

| 4.5 MB ZBT SRAM<br>64 MB DDR2 SDRAM | 27 MB QDRII-SRAM<br>288 MB RLDRAM-II |

| PCI                                 | PCI Express x8                       |

| Virtex II-Pro 50                    | Virtex 5 TX240T                      |

| <b>Contributed Projects</b> |                          |                                                      |  |  |

|-----------------------------|--------------------------|------------------------------------------------------|--|--|

|                             | Project                  | Contributor                                          |  |  |

|                             | OpenFlow switch          | Stanford University                                  |  |  |

|                             | Packet generator         | Stanford University                                  |  |  |

|                             | NetFlow Probe            | Brno University                                      |  |  |

|                             | NetThreads               | University of Toronto                                |  |  |

|                             | zFilter (Sp)router       | Ericsson                                             |  |  |

|                             | Traffic Monitor          | University of Catania                                |  |  |

|                             | DFA                      | UMass Lowell                                         |  |  |

|                             | netfpga.org/foswiki/Netl | FPGA/OneGig/ProjectTable<br>re integrate NetFPGA10G) |  |  |

| NetFPGR                     | LONDON – June 15th, 2012 | 13                                                   |  |  |

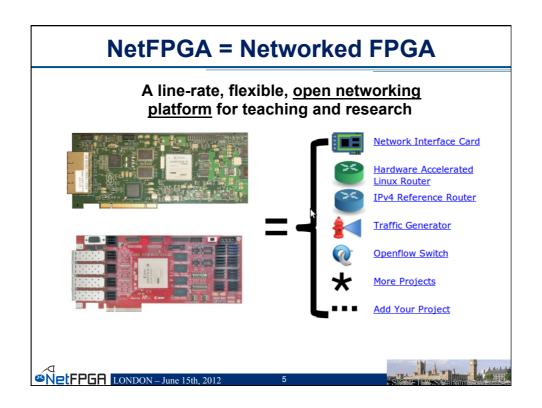

| NetFPGA's Defining Characteristics                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

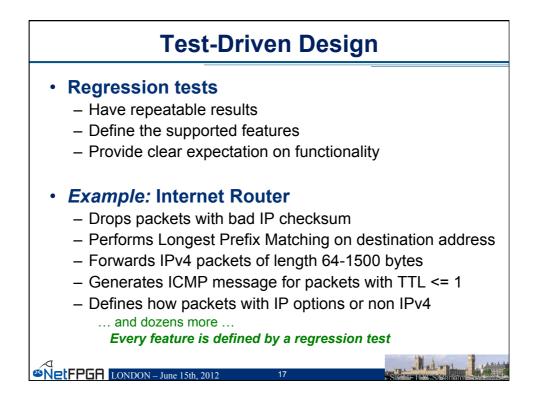

| <ul> <li>Line-Rate <ul> <li>Processes back-to-back packets</li> <li>Without dropping packets</li> <li>At full rate of Gigabit Ethernet Links</li> </ul> </li> <li>Operating on packet headers <ul> <li>For switching, routing, and firewall rules</li> </ul> </li> <li>And packet payloads <ul> <li>For content processing and intrusion prevention</li> </ul> </li> </ul> |  |  |  |

| <ul> <li>Open-source Hardware         <ul> <li>Similar to open-source software</li> <li>Full source code available</li> <li>BSD-Style License</li> </ul> </li> <li>But harder, because         <ul> <li>Hardware modules must meeting timing</li> <li>Verilog &amp; VHDL Components have more complex interfaces</li> </ul> </li> </ul>                                    |  |  |  |

| Hardware designers need high confidence in specification of modules                                                                                                                                                                                                                                                                                                        |  |  |  |

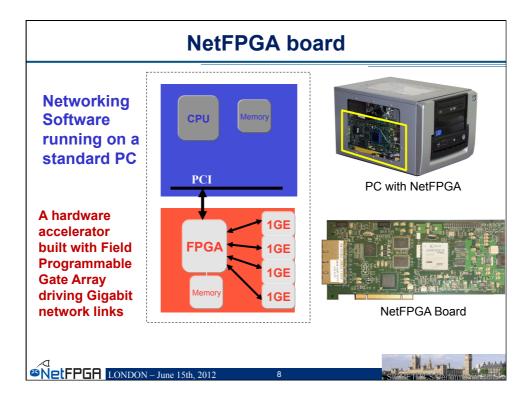

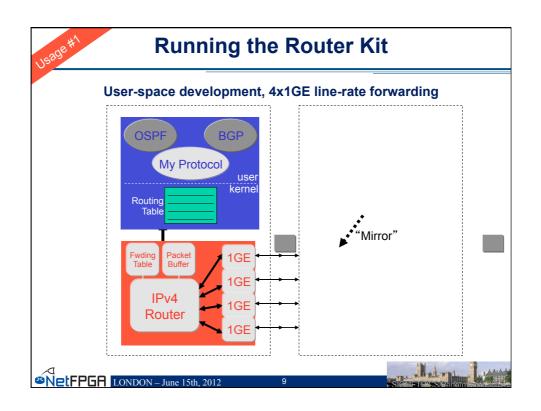

| Who, How, Why                                                                                                                                                                                  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

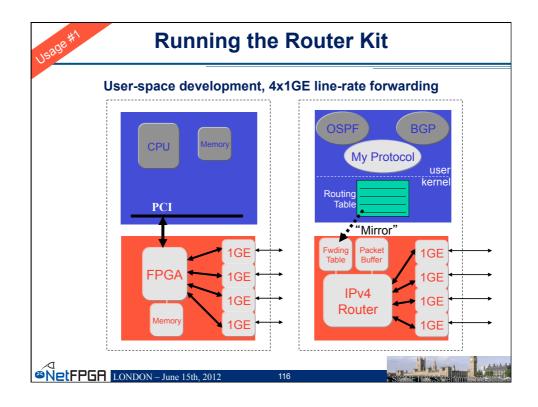

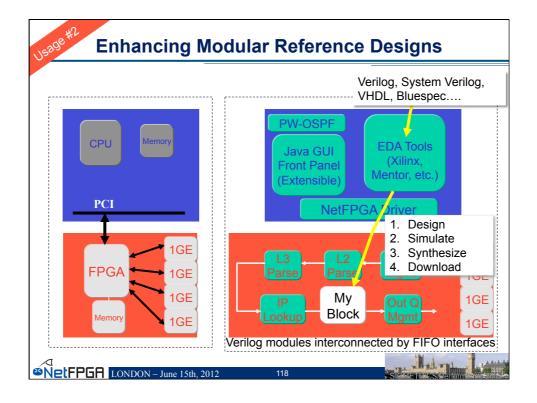

| Who uses the NetFPGA?<br>– Teachers<br>– Students<br>– Researchers                                                                                                                             |  |  |  |  |

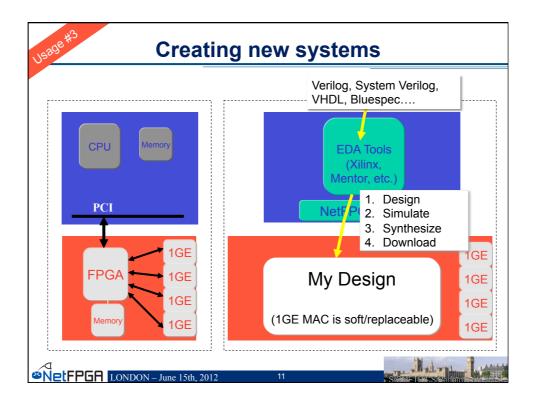

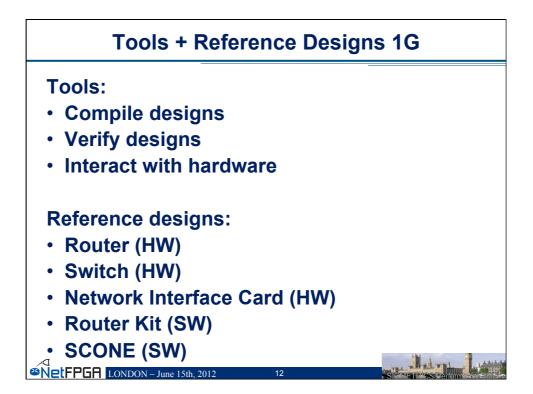

| <ul> <li>How do they use the NetFPGA?</li> <li>To run the Router Kit</li> <li>To build modular reference designs</li> <li>IPv4 router</li> <li>4-port NIC</li> <li>Ethernet switch,</li> </ul> |  |  |  |  |

| <ul> <li>Why do they use the NetFPGA?</li> <li>To measure performance of Internet systems</li> <li>To prototype new networking systems</li> </ul>                                              |  |  |  |  |

|                 | Naïve a                        |                                               |                   | ding tables<br>de → ~ 4 billion unique address |

|-----------------|--------------------------------|-----------------------------------------------|-------------------|------------------------------------------------|

|                 | Entry                          | Destination                                   | Port              |                                                |

|                 | 1<br>2<br>:<br>2 <sup>32</sup> | 0.0.0.0<br>0.0.0.1<br>:<br>255.255.255.255    | 1<br>2<br>:<br>12 | ~ 4 billion entries                            |

|                 | -                              | ved approach:<br>entries to reduce            | e table           | e size                                         |

|                 | Entry                          | Destinat                                      | ion               | Port                                           |

|                 | 1<br>2<br>:                    | 0.0.0.0 – 127.25<br>128.0.0.1 – 128.2         |                   |                                                |

| <sup>Q</sup> Ne | 50<br>EtFPGA                   | 248.0.0.0 – 255.2<br>LONDON – June 15th, 2012 |                   | 255 12<br>24 State 1000                        |

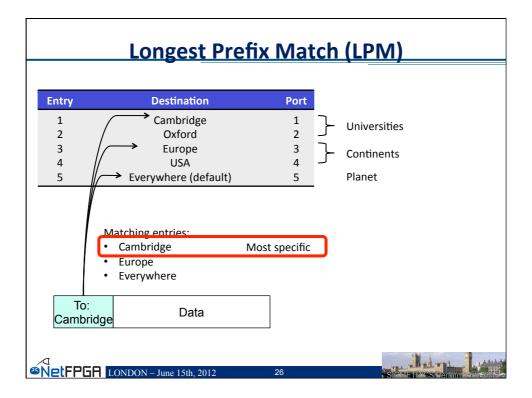

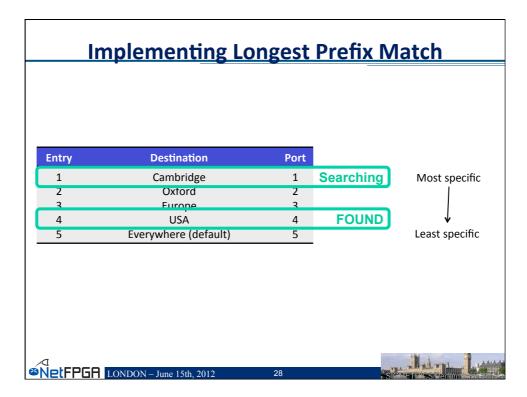

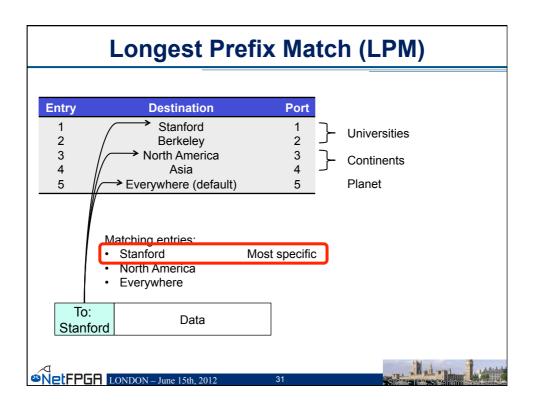

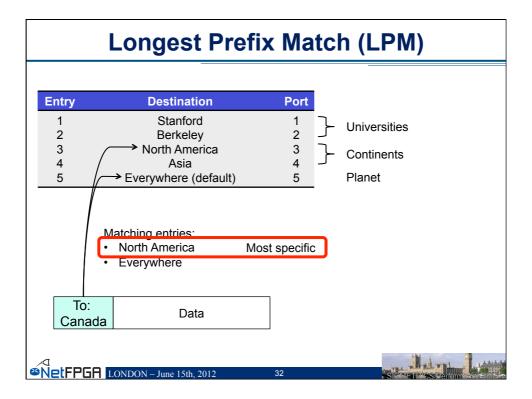

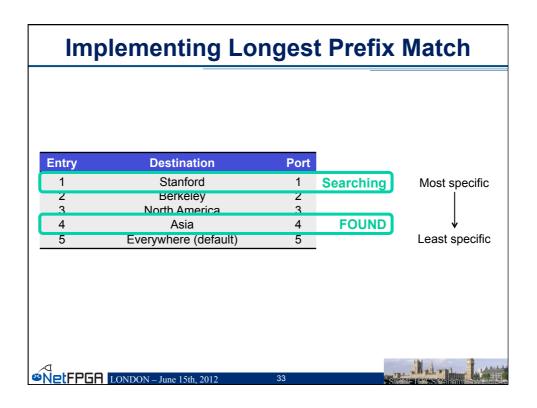

| Longest Prefix Match (LPM)     |                                                                             |                               |            |                                      |  |

|--------------------------------|-----------------------------------------------------------------------------|-------------------------------|------------|--------------------------------------|--|

| Entry<br>1<br>2<br>3<br>4<br>5 | Destination<br>Cambridge<br>Oxford<br>Europe<br>USA<br>Everywhere (default) | Port<br>1<br>2<br>3<br>4<br>5 | <br>}<br>} | Universities<br>Continents<br>Planet |  |

|                                | Matching entries:<br>• Europe<br>• Everywhere                               | Most specific                 |            |                                      |  |

| To:<br>Fran                    | Data                                                                        |                               |            |                                      |  |

|                                | LONDON – June 15th, 2012                                                    | 27                            |            |                                      |  |

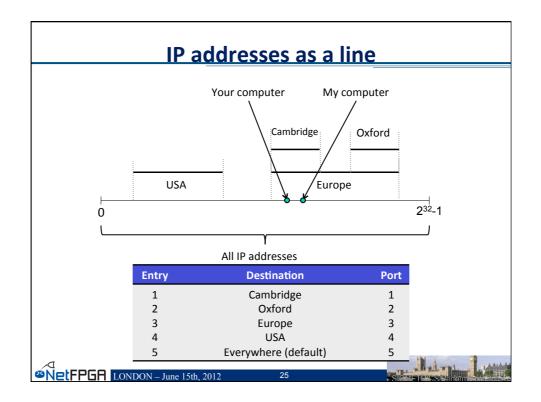

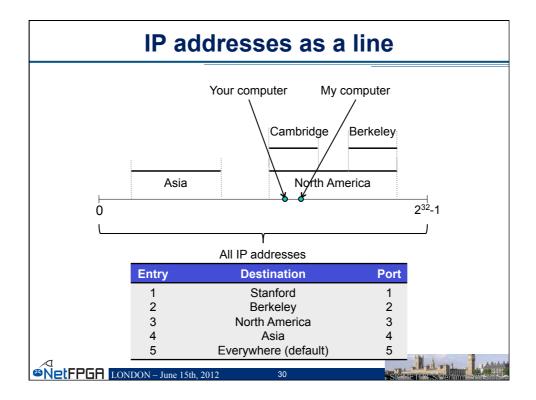

|                 | Forwarding tables                                                                                  |                   |             |         |              |  |  |

|-----------------|----------------------------------------------------------------------------------------------------|-------------------|-------------|---------|--------------|--|--|

|                 | $\boxed{\text{IP address}} 32 \text{ bits wide} \rightarrow \sim 4 \text{ billion unique address}$ |                   |             |         |              |  |  |

|                 | <b>Naïve approach:</b><br>One entry per address                                                    |                   |             |         |              |  |  |

|                 | Entry                                                                                              | Destination       | Port        |         |              |  |  |

|                 | 1                                                                                                  | 0.0.0.0           | 1           |         |              |  |  |

|                 | 2                                                                                                  | 0.0.0.1           | 2           | -~4 bil | lion entries |  |  |

|                 | :<br>2 <sup>32</sup>                                                                               | 255.255.255.255   | :<br>12     |         |              |  |  |

|                 | Improved approach:<br>Group entries to reduce table size                                           |                   |             |         |              |  |  |

|                 | Entry                                                                                              | Destinat          | ion         | Port    |              |  |  |

|                 | 1                                                                                                  | 0.0.0.0 - 127.25  |             | 1       |              |  |  |

|                 | 2                                                                                                  | 128.0.0.1 – 128.2 | 255.255.255 | 2       |              |  |  |

|                 | 50                                                                                                 | 248.0.0.0 – 255.2 | 255.255.255 | :<br>12 |              |  |  |

| <sup>Q</sup> Ne | NetFPGR LONDON – June 15th, 2012 29                                                                |                   |             |         |              |  |  |

## 13/06/2012

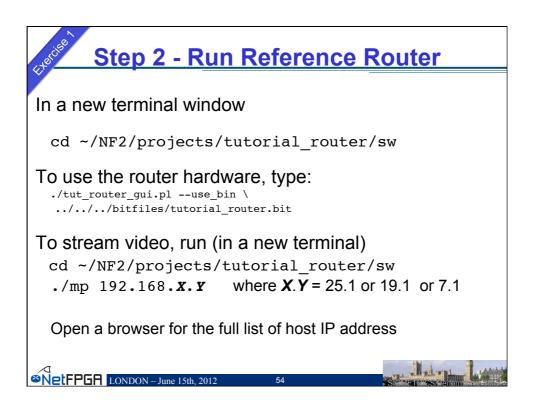

| step 1 -                                                       | Build the Hard                                                                                                                                                     | ware                |  |  |  |  |

|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--|--|--|--|

| Close all windows                                              |                                                                                                                                                                    |                     |  |  |  |  |

| Start terminal, cd to "NF2/projects/<br>tutorial_router/synth" |                                                                                                                                                                    |                     |  |  |  |  |

| Run "make clean"                                               |                                                                                                                                                                    |                     |  |  |  |  |

| Start synthesis with "make"                                    | foot©nf-test9:~/NF2/projects/tutorial_route     Elle Edt View Terminal Tabs Help     [root@nf-test9 ~]# cd NF2/projects/tutorial_t     [root@nf-test9 synth]# make |                     |  |  |  |  |

|                                                                | 15th, 2012 53                                                                                                                                                      | SIGNED SCHOOL STATE |  |  |  |  |

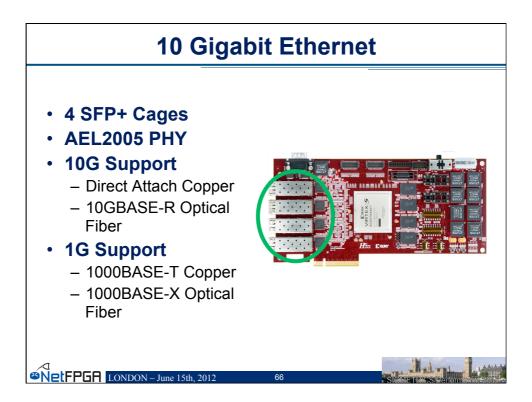

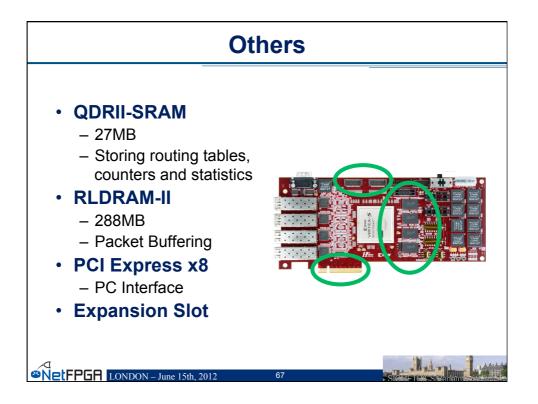

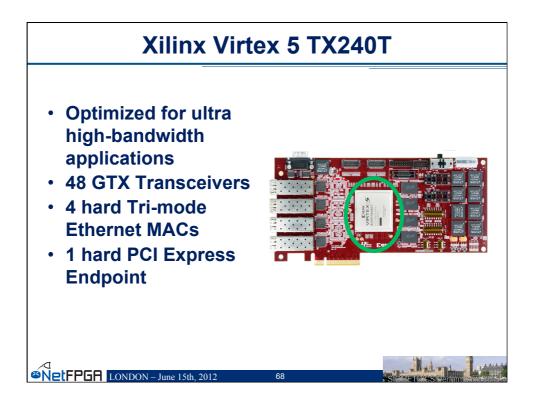

|       | Comparison                          |                                      |  |  |  |  |

|-------|-------------------------------------|--------------------------------------|--|--|--|--|

|       |                                     |                                      |  |  |  |  |

|       | NetFPGA 1G                          | NetFPGA 10G                          |  |  |  |  |

|       | 4 x 1Gbps Ethernet Ports            | 4 x 10Gbps SFP+                      |  |  |  |  |

|       | 4.5 MB ZBT SRAM<br>64 MB DDR2 SDRAM | 27 MB QDRII-SRAM<br>288 MB RLDRAM-II |  |  |  |  |

|       | PCI                                 | PCI Express x8                       |  |  |  |  |

|       | Virtex II-Pro 50                    | Virtex 5 TX240T                      |  |  |  |  |

|       |                                     |                                      |  |  |  |  |

| øNetF | PGA LONDON – June 15th, 2012        | 65 SIGNET SPECIM                     |  |  |  |  |

| <ul> <li>GitHub-powered User Community</li> <li>MicroBlaze SW PC SW</li> <li>Xilinx EDK</li> <li>Reference Designs Att4 IPs</li> <li>Software (embedded and PC)</li> <li>Public Repository (GitHub)</li> <li>Public Wiki (GitHub)</li> <li>Registration for access is required – but available without limit Integration for access is required – but available without limit</li> </ul> | Beyond Hardware                                                 |                                                                                                                                                                                                                   |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                          | MicroBlaze SW PC SW<br>Xilinx EDK<br>Reference Designs AXI4 IPs | <ul> <li>Xilinx EDK based IDE</li> <li>Reference designs with<br/>ARM AXI4</li> <li>Software (embedded and<br/>PC)</li> <li><i>Public</i> Repository<br/>(GitHub)</li> <li><i>Public</i> Wiki (GitHub)</li> </ul> |  |  |  |

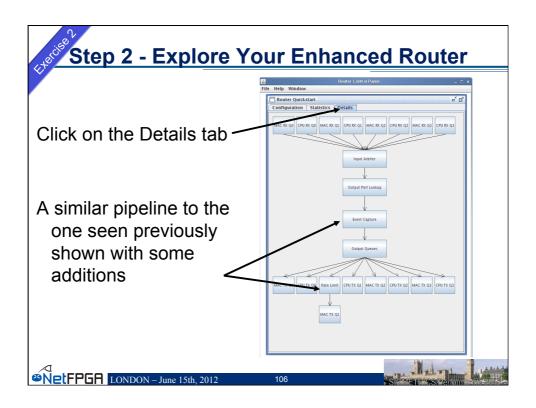

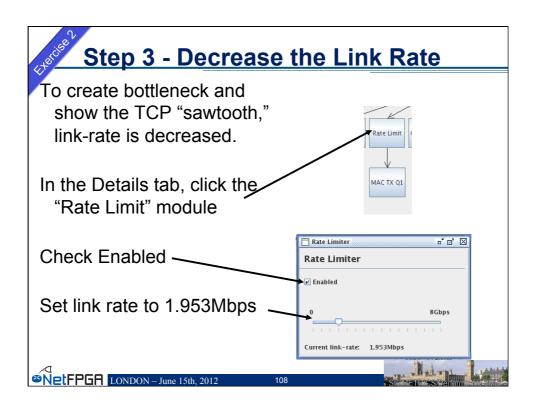

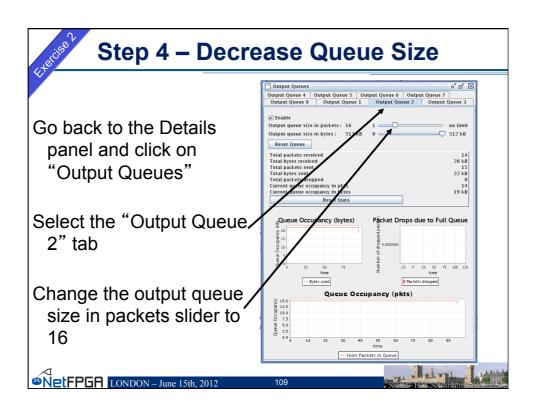

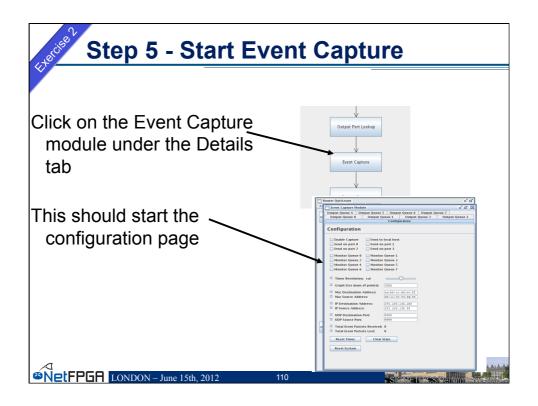

| Step 1 - Run You                  | r Enhanced Router                                                                                                                                                                                    |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ×                                 | v root©nf-test9:~/NF2/projects/tutorial_router/sw C X<br>Elle Edit View Terminal Tabs Help                                                                                                           |

| Start terminal and cd to          | [root@nf-test9 -]# cd NF2/projects/tutorial_router/sw/ ▲<br>[root@nf-test9 sw]# ./tut_adv_router.pl]                                                                                                 |

| NF2/projects/                     | Renter Connorband S                                                                                                                                                                                  |

| tutorial_router/sw/               | Tototre Quidstant n° D'<br>Configuration Statistics Details                                                                                                                                          |

| NB:ADV                            | Reset to Defaults       Output queres size in bytes:       S123.8       Output queres size in packets:       no limit       Output queres size in packets:       Notify:       Manufic Configuration |

| ./tut_adv_router_gui.pl -use_bin\ | Hierface HAC Address IP address                                                                                                                                                                      |

| //bitfiles/tutorial_router.bit    | AND TAME         Reserve firsts         Add fairs         #           New Hey P Addr         New Hey NAC Addr         *                                                                              |

| A familiar GUI should start       |                                                                                                                                                                                                      |

|                                   | Sectory Table         Jammer Entry         Add Entry           Salare #         Salare Hask         Herd Hag #         Opport/Yers                                                                   |

| SetFPGA LONDON – June 15th, 2012  | 105                                                                                                                                                                                                  |

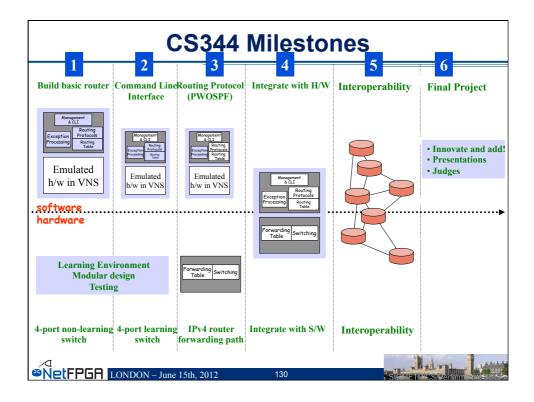

|         | Typical NetFPGA Course Plan |                              |                          |  |  |  |  |

|---------|-----------------------------|------------------------------|--------------------------|--|--|--|--|

| Week    | Software                    | Hardware                     | Deliver                  |  |  |  |  |

| 1       | Verify Software Tools       | Verify CAD Tools             | Write Design<br>Document |  |  |  |  |

| 2       | Build Software Router       | Build Non-Learning<br>Switch | Run Software Router      |  |  |  |  |

| 3       | Cmd. Line Interface         | Build Learning Switch        | Run Basic Switch         |  |  |  |  |

| 4       | Router Protocols            | Output Queues                | Run Learning Switch      |  |  |  |  |

| 5       | Implement Protocol          | Forwarding Path              | Interface SW & HW        |  |  |  |  |

| 6       | Control Hardware            | Hardware Registers           | HW/SW Test               |  |  |  |  |

| 7       | Interoperate Sc             | Router Submission            |                          |  |  |  |  |

| 8       | Plan New Ac                 | Project Design Plan          |                          |  |  |  |  |

| 9       | Show new Advanced Feature   |                              | Demonstration            |  |  |  |  |

| NetFPGf | LONDON – June 15th, 2012    | 131                          | SIGNET ROSPerform        |  |  |  |  |

|                           | <ul> <li>http://netfpga.org/foswiki/bin/vie</li> </ul>                                                                                       |                                 |                          |                                                |                                  | PSIRP NetFPGA Q                |  |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------|------------------------------------------------|----------------------------------|--------------------------------|--|

|                           | de CLWiki(ro) pfact je-S CoNet C/C++<br>→ 🖓 🌝 🚰 Share + 💼 + 🚵 Translate +                                                                    |                                 |                          |                                                | nicks baby CL(owa) Online IP CID | R / VLS Inktorni's Wild Ride » |  |

| ter Laboratory - Course ( | 0 Untitled) O                                                                                                                                | Martin La                       | ibrecque h               | tomepage 💿 🛛 🖪 A Class Apart: Abo              | at the Siebel 🔘 🦨 ProjectTable   | < NetSPGA/OneGi 🔘 🛨 🛒          |  |

|                           |                                                                                                                                              | -                               | lications                | Events News Wiki Foru                          | me About                         | Ô                              |  |

|                           | NetFPGA <sup>Ho</sup>                                                                                                                        | пе Арр                          | lications                | Events News Wiki Ford                          | ins About                        |                                |  |

|                           |                                                                                                                                              |                                 |                          |                                                |                                  |                                |  |

| 🔒 Log In or Register      | You are here: Foswiki > NetFPGA/One                                                                                                          | Gig Web > 1                     | ProjectTable (i          | 02 Aug 2011, Main.GianniAntichi)               |                                  | Edit Attach                    |  |

|                           | Project Table                                                                                                                                |                                 |                          |                                                |                                  |                                |  |

| Learn                     | <ul> <li>We encourse you to Contribute</li> </ul>                                                                                            | veur Project                    | to the NetFPC            | A Community                                    |                                  |                                |  |

| Learn More<br>Get Started | <ul> <li>We encourage you to <u>Contribute</u></li> <li>This table provides a quick refer</li> <li>You can add or modify informat</li> </ul> | tence of projection directly or | ets that run on          | the NetFPGA                                    |                                  |                                |  |

| Users Guide               | <ul> <li>If the eslir button does not appear</li> </ul>                                                                                      | r on your page                  | e, click Log h           | a~<br>n'                                       |                                  |                                |  |

| License                   | Project (Title & Summary)                                                                                                                    | Base                            | Status                   | Organization                                   | Documentation                    |                                |  |

| Develop<br>Develop        |                                                                                                                                              | Version                         |                          |                                                |                                  |                                |  |

| Developers Guide          | IPv4 Reference Router<br>Quad-Port Gigabit NIC                                                                                               | 2.1.1                           | Punctional<br>Punctional |                                                | Quide<br>Guide                   |                                |  |

| Report Bugs<br>Contribute | Ethernet Switch                                                                                                                              | 2.1.1                           | Functional               |                                                | Wiki                             |                                |  |

| Community                 | Buffer Monitoring System                                                                                                                     | 2.1.1                           | Functional               |                                                | Quide                            |                                |  |

| Projects                  | Hardware-Accelerated Linux Router<br>DRAM-Router                                                                                             | 2.1.1 2.1.1                     |                          | Stanford University<br>Stanford University     | Quide<br>Wiki                    |                                |  |

| Forums<br>Events          | DRAM-Queue Test                                                                                                                              | 2.1.1                           | Parctional               |                                                | Wiki                             |                                |  |

| Publications              | Packet Generator                                                                                                                             | 2.1.1                           | Functional               | Stanford University                            | Wiki                             |                                |  |

| Teolhox                   | OpenFlow Switch                                                                                                                              | 2.2.0                           | Functional               |                                                | Wiki                             |                                |  |

| Create New Topic          | NetFlow Probe                                                                                                                                | 1.2                             |                          | Beno University<br>Stanford University         | Wiki<br>Wiki and Paper           |                                |  |

| Index<br>Q. Search        | Fast Reroute & Multipath Router                                                                                                              | 2.0                             |                          | Stanford University                            | Wiki                             |                                |  |

| Changes                   | NetThreads                                                                                                                                   | 1.2.5                           |                          | University of Toronto                          | Wiki                             |                                |  |

| Notifications<br>RSS Feed | NetThreads-RE<br>NetTM                                                                                                                       | 2.0                             |                          | University of Toronto                          | Wiki                             |                                |  |

| Statistics                | NetTM<br>Precise Traffic Generator                                                                                                           | 2.0                             |                          | University of Toronto<br>University of Toronto | Wiki                             |                                |  |

| ✤ Preferences             | URL Extraction                                                                                                                               | 2.0                             | Functional               | Univ. of New South Wales                       | Wiki                             |                                |  |

| Webs                      | zFilter Sprouter (Pub/Sub)                                                                                                                   | 1.2                             | Functional               |                                                | Wiki                             |                                |  |

| NetFPGA<br>OneGie         | Windows Driver<br>RED                                                                                                                        | 2.0                             |                          | Microsoft Research<br>Stanford University      | Wiki<br>Wiki                     |                                |  |

| TenGig                    | RED<br>Open Network Lab                                                                                                                      | 2.0                             |                          | Stanford University<br>Washington University   | Wiki                             |                                |  |

| System                    | DFA                                                                                                                                          | 2.0                             | Functional               | UMass Lowell                                   | Wiki                             |                                |  |

|                           | G/PaX                                                                                                                                        | 2.2                             | Functional               |                                                | Wiki                             |                                |  |

|                           | RCP Router                                                                                                                                   | 2.0                             | Functional               | Stanford University                            | Wiki                             |                                |  |

| Networked FPGAs in Research                                           |

|-----------------------------------------------------------------------|

| 1. OpenFlow                                                           |

| <u>http://OpenFlowSwitch.org/</u>                                     |

| 2. Buffer Sizing                                                      |

| Reduce buffer size & measure buffer occupancy                         |

| 3. RCP: Congestion Control                                            |

| <ul> <li>New module for parsing and overwriting new packet</li> </ul> |

| <ul> <li>New software to calculate explicit rates</li> </ul>          |

| 4. Deep Packet Inspection (FPX)                                       |

| TCP/IP Flow Reconstruction                                            |

| Regular Expression Matching                                           |

| Bloom Filters                                                         |

| 5. Packet Monitoring (ICSI)                                           |

| Network Shunt                                                         |

| 6. Precise Time Protocol (PTP)                                        |

| <ul> <li>Synchronization among Routers</li> </ul>                     |

|                                                                       |

| Conception Provide August 2012 150 Signal August 2012                 |

## Thoughts for (Prospective) Contributors Build Modular components Describe shared registers (as per 2.0 release) Consider how modules would be used in larger systems Define functionality clearly Through regression tests With repeatable results Disseminate projects Post open-source code Document projects on Web, Wiki, and Blog Expand the community of developers Answer questions in the Discussion Forum Collaborate with your peers to build new applications

| Group Discussion                                     |         |

|------------------------------------------------------|---------|

| <ul> <li>Your plans for using the NetFPGA</li> </ul> |         |

| – Teaching                                           |         |

| – Research                                           |         |

| – Other                                              |         |

| <ul> <li>Resources needed for your class</li> </ul>  |         |

| – Source code                                        |         |

| – Courseware                                         |         |

| – Examples                                           |         |

| <ul> <li>Your plans to contribute</li> </ul>         |         |

| – Expertise                                          |         |

| – Capabilities                                       |         |

| – Collaboration Opportunities                        | 14.1.44 |

| NetFPGA LONDON – June 15th, 2012 161                 |         |