# Capable VMs

23 Apr 24 - CHERITech '24

Jacob Bramley, Andrei Lasc Duncan Lowthe Dejice Jacob,

Jerer Jerer aurie Tratt om Wallis

Engineering and Physical Sciences Research Council **Virtual machines** (VMs, also known as managed language runtimes) are ubiquitous components in the modern software stack. They power the web, running in client-side browsers, server-side applications, and smartphone apps. In any ranking of popular programming languages, at least half of the top ten languages run on VMs (e.g. Python, Java, C#, JavaScript, PHP).

A key problem is that **VM security** has traditionally been a secondary concern relative to performance. Industrial strength VMs have large, complex code-bases, and large numbers of hand-crafted optimizations. Not only are they beyond any one person's ability to understand, but security has tended to be treated reactively: mature, widely used VMs such as HotSpot (the standard Java VM) regularly have 50-100 CVEs per year.

The **CapableVMs** project hypothesises that **CHERI** hardware-enforced **capabilities** are the first realistic technique to **make VM security proactive**.

lots of low-level platform-specific systems code

intensive allocation and garbage collection

runtime code generation

multiple interacting dynamic components

lots of low-level platform-specific systems code

multiple interacting dynamic components

intensive allocation and garbage collection

lots of low-level platform-specific systems code

multiple interacting dynamic components

intensive allocation and garbage collection

### 1. Low-level system-specific code

- CHERIfication

- Specific porting process

- Measure proportion of LoC alterered

- KDE: 0.026%

- higher for systems code

- 0.18% for MicroPython

- 1% for snmalloc

#### **Cherifying Linux: A Practical View on using CHERI** Kui Wang Vincent Ahlrichs Jan-Erik Ekberg Dmitry Kasatkin Lukas Auer jan.erik.ekberg@huawei.com Huawei Technologie

1 Introduction

#### Morello MicroPython: A Python Interpreter for CHERI

#### Duncan Lowther University of Glasgow Glasgow, United Kingdom

Dejice Jacob University of Glasgow Glasgow, United Kingdom duncan.lowther@glasgow.ac.uk dejice.jacob@glasgow.ac.uk

#### Abstract

Arm Morello is a prototype system that supports CHERI hardware capabilities for improving runtime security. As Morello becomes more widely available, there is a growing effort to port open source code projects to this novel platform. Although high-level applications generally need minimal code refactoring for CHERI compatibility, low-level systems code bases require significant modification to comply with the stringent memory safety constraints that are dynamically enforced by Morello. In this paper, we describe our work on porting the MicroPython interpreter to Morello with the CheriBSD OS. Our key contribution is to present a set of generic lessons for adapting managed runtime execution environments to CHERI, including (1) a characterization of necessary source code changes, (2) an evaluation of runtime performance of the interpreter on Morello, and (3) a demonstration of pragmatic memory safety bug detection. Although MicroPython is a lightweight interpreter, mostly written in C, we believe that the changes we have implemented and the lessons we have learned are more widely applicable. To the best of our knowledge, this is the first published description of meaningful experience for scripting language runtime engineering with CHERI and Morello.

#### Jeremy Singer

University of Glasgow Glasgow, United Kingdom jeremy.singer@glasgow.ac.uk

In 2021, Arm released a prototype platform code-named 'Morello' [2, 9] which realizes the CHERI hardware capability concept [22, 25] in an industrial strength microprocessor. A *capability* is a double-width 'fat' pointer that includes metadata for address bounds and access permissions. Additionally, CHERI capabilities have an out-of-band tag to ensure pointer validity. The premise of hardware capabilities is that entire classes of memory vulnerabilities can be eliminated, including spatial bugs (i.e. out-of-bounds reads and writes) and temporal bugs (i.e. use-after-free bugs) [12].

In this paper, we describe our experience and lessons learned during a full port of the MicroPython framework to Morello. We modify the C source code of MicroPython in order to provide runtime awareness of CHERI capabilities. There were two logical stages to this work: firstly the MicroPython code was refactored to eliminate compiler errors and warnings, as described in Section 3; secondly memory safety enforcement of capabilities was leveraged to generate tight bounds on runtime allocations, as described in Section 4. In Section 5, we analyse test coverage for MicroPython on the Morello CheriBSD platform, which has almost identical results to the AArch64 FreeBSD platform. Section 6 characvise

import dodgylib

tiny1 = bytearray(3)

tiny2 = bytearray(12)

| #  | setup   | 'Oh | ' raw       | st | ring       |

|----|---------|-----|-------------|----|------------|

| ti | lny1[0] | = ( | 0x4f        | #  | 0          |

| tj | lny1[1] | = ( | <b>0x68</b> | #  | h          |

| tj | lny1[2] | = ( | 00x0        | #  | <b>\</b> 0 |

| # setup             | 'Hello'              | raw string  |

|---------------------|----------------------|-------------|

| <pre>tiny2[0]</pre> | = 0x48               | # H         |

| <pre>tiny2[1]</pre> | = 0x65               | # e         |

| <pre>tiny2[2]</pre> | = 0x6c               | # 1         |

| <pre>tiny2[3]</pre> | = 0x6c               | # l         |

| <pre>tiny2[4]</pre> | = 0x6f               | # O         |

| <pre>tiny2[5]</pre> | $= 0 \mathbf{x} 0 0$ | <b>#</b> ∖0 |

print(tiny1.decode('utf-8'))

dodgylib.dodgy(tiny1)

print(tiny2.decode('utf-8'))

root@amarena:~ #

./micropython-hybrid

exploit.py

Oh HACK!!

```

import uctypes as uct

def dodgy(x):

ptr = uct.addressof(x)

unsafe =

uct.bytearray at(ptr, 2000)

i = 0

while unsafe[i] != 0x65 or

unsafe[i+1] != 0x6c:

i += 1

if i > 2000:

break

unsafe[i] = 0x41

unsafe[i+1] = 0x43

unsafe[i+2] = 0x4b

unsafe[i+3] = 0x21

unsafe[i+4] = 0x21

unsafe[i+5] = 0x00

return

```

print(tiny1.decode('utf-8'))

dodgylib.dodgy(tiny1)

print(tiny2.decode('utf-8'))

root@amarena:~ #

./micropython-purecap

exploit.py

Oh

Tn-address\_space\_securi

In-address space security exception (core dumped)

#### **븿CVE-2023-7158 Detail**

#### Description

A vulnerability was found in MicroPython up to 1.21.0. It has been classified

as critical. Affected is the function slice\_indices of the file objslice.c. The

manipulation leads to heap-based buffer ove the attack remotely. The exploit has been dis be used. Upgrading to version 1.22.0 is able t recommended to upgrade the affected comp vulnerability is VDB-249180.

#### **头CVE-2023-7152 Detail**

#### Description

A vulnerability, which was classified as critical, has been found in MicroPython 1.21.0/1.22.0-preview. Affected by this issue is the function poll\_set\_add\_fd of the file extmod/modselect.c. The manipulation leads to use after free. The exploit has been disclosed to the public and may be used. The patch is identified as 8b24aa36ba978eafc6114b6798b47b7bfecdca26. It is recommended to apply

a patch to fix this issue. VDB-249158 is the identifier assigned to this vulnerability.

### Other findings from MicroPython

- Pointer size assumptions

- don't affect correctness only

- they also have an impact on performance

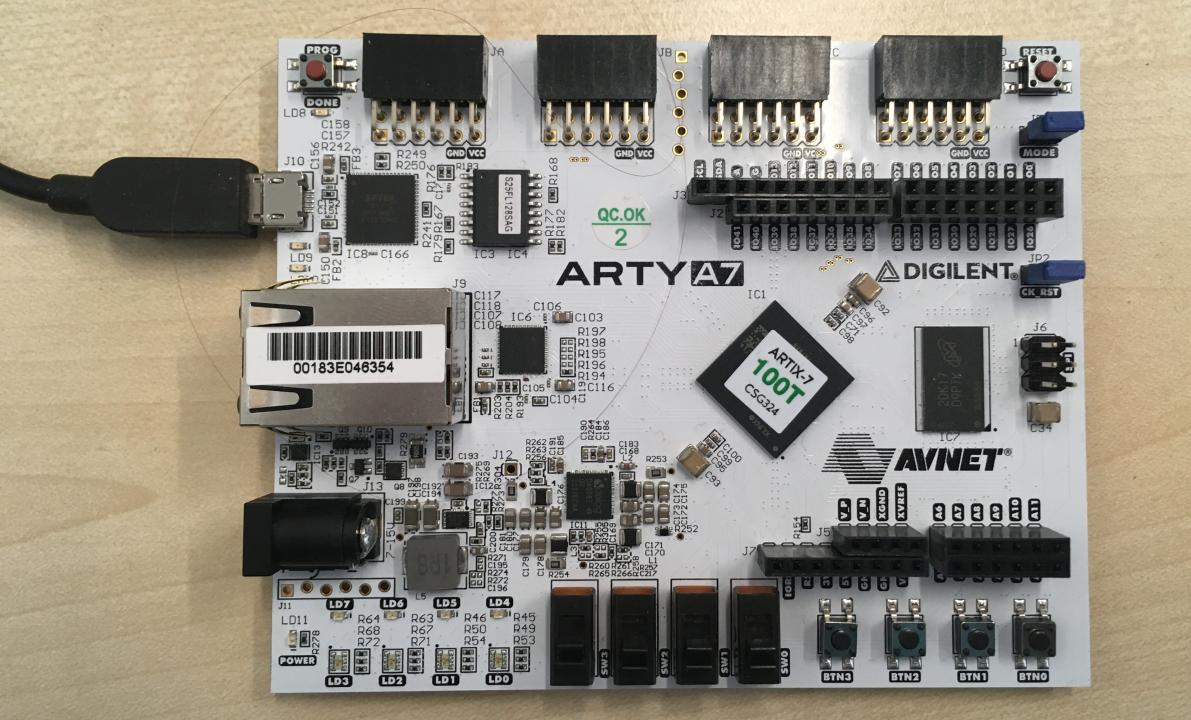

- Porting to a variety of platforms

- Morello: github.com/glasgowPLI/micropython

- working on CHERIoT RISC-V lbex core

lots of low-level platform-specific systems code

wultiple interacting dynamic components

intensive allocation and garbage collection

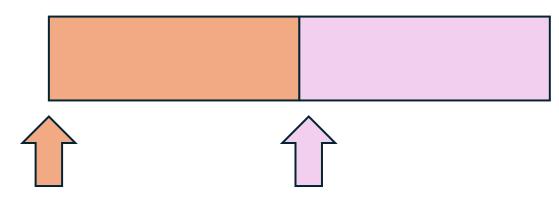

### 2. Multiple interacting components

- compartmentalization (c18n) is **lightweight isolation**

- hybrid code enables DDC-based isolation

- need a compartment switcher

- need a libc per compartment

- need clever tricks to handle dynamic loading

- overhead how small should each compartment be?

- compartment per *function*

- compartment per *shared object*

- alternative compartment boundaries?

#### Alternative c18n strategy

- For purecap MicroPython code

- We isolate at FFI boundaries

- e.g. calls to external C libraries

- (work in progress)

ua

lots of low-level platform-specific systems code

multiple interacting dynamic components

intensive allocation and garbage collection

### 3. Malloc and GC

Complications include:

- finding and tracing the root set

- scanning the full heap

- moving objects

- We have studied **BDWGC**

- Morello & RISC-V: github.com/capablevms/bdwgc

### Observations about purecap GC

- Can't afford to lose capability tags

- conservative -> precise

- overhead reduction!

- issue with sealed caps in userspace code

- issue with coalescing

```

int main() {

int i, size, *buffer;

```

srand(SEED);

```

for (i=0; i<NUM_ALLOCS; i++) {

size = rand() % 1024;

// printf("alloc buffer size %d\n", size);

buffer = (int *)malloc(size * sizeof(int));</pre>

```

// confuse conservative collector?

savebuffer[i%(NUM\_ALLOCS>>5)] = (long int)buffer;

}

return 0;

lots of low-level platform-specific systems code

multiple interacting dynamic components

intensive allocation and garbage collection

### 4. Runtime code generation

- Several baseline interpreters ported to Morello purecap: WARDuino, MicroPython, JSC

- Some investigations on runtime code generation: JSC (& v8)

- This is work-in-progress

## Summary

• Our Capable VMs project has demonstrated that

#### CHERI does provide defence-in-depth against VM-based exploits

Challenges include:

- 1. how to quantify additional **defence**?

- 2. how to measure **performance**?

- 3. how to encourage **adoption**?