# A better x86 memory model: x86-TSO (extended version)

Scott Owens Susmit Sarkar Peter Sewell

University of Cambridge

http://www.cl.cam.ac.uk/users/pes20/weakmemory

March 25, 2009 *Revision* : 1746

#### Abstract

Real multiprocessors do not provide the sequentially consistent memory that is assumed by most work on semantics and verification. Instead, they have relaxed memory models, typically described in ambiguous prose, which lead to widespread confusion. These are prime targets for mechanized formalization. In previous work we produced a rigorous x86-CC model, formalizing the Intel and AMD architecture specifications of the time, but those turned out to be unsound with respect to actual hardware, as well as arguably too weak to program above. We discuss these issues and present a new x86-TSO model that suffers from neither problem, formalized in HOL4. We believe it is sound with respect to real processors, reflects better the vendor's intentions, and is also better suited for programming. We give two equivalent definitions of x86-TSO: an intuitive operational model based on local write buffers, and an axiomatic total store ordering model, similar to that of the SPARCv8. Both are adapted to handle x86-specific features. We have implemented the axiomatic model in our memevents tool, which calculates the set of all valid executions of test programs, and, for greater confidence, verify the witnesses of such executions directly, with code extracted from a third, more algorithmic, equivalent version of the definition.

## Contents

| 1        | Introduction                                                                                                                                                                                                                                                       | <b>2</b>       |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 2        | Many Memory Models           2.1         pre-IWP (before Aug. 2007)           2.2         IWP/AMD64-3.14/x86-CC           2.3         Intel SDM rev-29 (Nov. 2008)                                                                                                 | 3              |

| 3        | The x86-TSO Model3.1The x86-TSO Abstract Machine Memory Model3.2The x86-TSO Axiomatic Memory Model3.3The Machine and Axiomatic x86-TSO Models are Equivalent                                                                                                       | 9              |

| 4        | Verified Checker and Results                                                                                                                                                                                                                                       | 12             |

| <b>5</b> | Related Work                                                                                                                                                                                                                                                       | 12             |

| 6        | Conclusion                                                                                                                                                                                                                                                         | 13             |

| Α        | Litmus Tests and DiscussionA.1Load/Store ReorderingA.2Independent Reads of Independent WritesA.3Locked Instructions: Tests iwp2.7/amd7, iwp2.8.a, iwp2.8.b, n8, and n3A.4Fence Instructions: Tests amd5 and amd10A.5The Unsoundness of IWP/AMD3.14/x86-CC: Test n6 | 17<br>18<br>19 |

|              | A.6 The Weakness of Rev-29: Tests n4 and n5               | 20 |  |

|--------------|-----------------------------------------------------------|----|--|

|              | A.7 Interpreting the rev-29 "not reordered with": Test n7 | 21 |  |

|              | A.8 Other Tests                                           | 22 |  |

|              | A.9 Summary of Test Results                               |    |  |

| в            | The IWP and Rev-29 Principles and Litmus Tests            | 25 |  |

|              | B.1 Principles                                            | 25 |  |

|              | B.2 Litmus Tests                                          | 25 |  |

| С            | Well-Formed Event Structures                              | 26 |  |

| D            | Auxiliary Definitions                                     | 27 |  |

|              | D.1 Axiomatic Memory Model                                | 27 |  |

|              | D.2 Abstract Machine Memory Model                         | 28 |  |

| $\mathbf{E}$ | Proof Outlines                                            | 31 |  |

|              | E.1 Event-annotated machine                               | 31 |  |

|              | E.2 Linear valid executions                               | 36 |  |

|              | E.3 Abstract machine model/axiomatic model equivalence    | 38 |  |

|              | E.3.1 Abstract machine validity                           | 38 |  |

|              | E.3.2 Abstract machine completeness                       |    |  |

|              | E.4 Executable checker                                    | 44 |  |

| $\mathbf{F}$ | Change History                                            | 49 |  |

## 1 Introduction

Most previous research on the semantics and verification of concurrent programs assumes sequential consistency: that accesses by multiple threads to a shared memory occur in a global-time linear order. Real multiprocessors, however, incorporate many performance optimisations. These are typically unobservable by single-threaded programs, but some have observable consequences for the behaviour of concurrent code. For example, on standard Intel or AMD x86 processors, given two memory locations x and y (initially holding 0), if two processors proc:0 and proc:1 respectively write 1 to x and y and then read from y and x, as in the program below, it is possible for both to read 0 *in the same execution*.

| iwp2.3.a/amd4                  | proc:0                   | proc:1                   |  |  |

|--------------------------------|--------------------------|--------------------------|--|--|

| poi:0                          | MOV [x]←\$1              | MOV [y]←\$1              |  |  |

| poi:1                          | MOV EAX $\leftarrow$ [y] | MOV EBX $\leftarrow$ [x] |  |  |

| Allow: $0:EAX=0 \land 1:EBX=0$ |                          |                          |  |  |

One can view this as a visible consequence of *write buffering*: each processor effectively has a FIFO buffer of pending memory writes (to avoid the need to block while a write completes), so the reads from y and x can occur before the writes have propagated from the buffers to main memory. Such optimisations destroy the illusion of sequential consistency, making it impossible (at this level of abstraction) to reason in terms of an intuitive notion of global time.

To describe what programmers can rely on, processor vendors document *architectures*. These are loose specifications, claimed to cover a range of past and future actual processors, which should reveal enough for effective programming, but without unduly constraining future processor designs. In practice, however, they are informal prose documents, e.g. the Intel 64 and IA-32 Architectures SDM [2] and AMD64 Architecture Programmer's Manual [1]. Informal prose is a poor medium for loose specification of subtle properties, and, as we shall see in §2, such documents are often ambiguous, are sometimes incomplete (too weak to program above), and are sometimes unsound (with respect to the actual processors). Moreover, one cannot test programs above such a vague specification (one can only run programs on particular actual processors), and one cannot use them as criteria for testing processor implementations.

Architecture specifications are, therefore, prime targets for rigorous mechanised formalisation. In previous work [20] we introduced a rigorous x86-CC model, formalised in HOL4 [11], based on the

informal prose causal-consistency descriptions of the then-current Intel and AMD documentation. Unfortunately those, and hence also x86-CC, turned out to be unsound, forbidding some behaviour which actual processors exhibit.

In this paper we describe a new model, x86-TSO, also formalised in HOL4. To the best of our knowledge, x86-TSO is sound, is strong enough to program above, and is broadly in line with the vendors' intentions. We present two equivalent definitions of the model: an abstract machine, in §3.1, and an axiomatic version, in §3.2. We compensate for the main disadvantage of formalisation, that it can make specifications less widely accessible, by extensively annotating the mathematical definitions. To explore the consequences of the model, we have a hand-coded implementation in our memovents tool, which can explore all possible executions of litmus-test examples such as that above, and for greater confidence we have a verified execution checker extracted from the HOL4 axiomatic definition, in §4. We discuss related work in §5 and conclude in §6.

Further details can be found in the appendices. In Appendix A we discuss a number of litmus tests, comparing their behaviour in the model (as calculated by **memevents**) and on actual processors (as observed with our litmus tool). In Appendix B we reproduce the key "principles" from the informal-prose vendor documentation, for reference. Appendix C makes the notion of well-formed event structure precise, Appendix D collects a number of routine auxiliary definitions used in the definition of our models, and Appendix E gives an overview of the proofs of our results.

## 2 Many Memory Models

We begin by reviewing the informal-prose specifications of recent Intel and AMD documentation. There have been several versions, some differing radically; we contrast them with each other, and with what we know of the behaviour of actual processors.

### 2.1 pre-IWP (before Aug. 2007)

Early revisions of the Intel SDM (e.g. rev-22, Nov. 2006) gave an informal-prose model called 'processor ordering', unsupported by any litmus-test examples. It is hard to give a precise interpretation of this description.

### 2.2 IWP/AMD64-3.14/x86-CC

In August 2007, an Intel White Paper [12] (IWP) gave a somewhat more precise model, with 8 informalprose principles supported by 10 litmus tests. This was incorporated, essentially unchanged, into later revisions of the Intel SDM (including rev.26–28), and AMD gave similar, though not identical, prose and tests [1]. These are essentially causal-consistency models. They allow independent readers to see independent writes (by different processors to different addresses) in different orders, as below (IRIW, see also [5]),

| amd6                                                       | proc:0      | proc:1      | proc:2                   | proc:3                   |  |

|------------------------------------------------------------|-------------|-------------|--------------------------|--------------------------|--|

| poi:0                                                      | MOV [x]←\$1 | MOV [y]←\$1 | MOV EAX $\leftarrow$ [x] | MOV ECX $\leftarrow$ [y] |  |

| poi:1 $MOV EBX \leftarrow [y] MOV EDX \leftarrow [x]$      |             |             |                          |                          |  |

| Final: $2:EAX=1 \land 2:EBX=0 \land 3:ECX=1 \land 3:EDX=0$ |             |             |                          |                          |  |

| cc : Allow; tso : Forbid                                   |             |             |                          |                          |  |

but require that, in some sense, causality is respected: "P5. In a multiprocessor system, memory ordering obeys causality (memory ordering respects transitive visibility)". These were the basis for our x86-CC model, for which a key issue was giving a reasonable interpretation to this "causality". Apart from that, the informal specifications were reasonably unambiguous — but they turned out to have two serious flaws.

First, they are arguably rather weak for programmers. In particular, they admit the IRIW behaviour above but, under reasonable assumptions on the strongest x86 memory barrier, MFENCE, adding MFENCEs would not suffice to recover sequential consistency [20, §2.12]. Here the specifications seem to be much looser than the behaviour of implemented processors: to the best of our knowledge, and following some testing, IRIW is not observable in practice. It appears that some JVM implementations depend on this fact, and would not be correct if one assumed only the IWP/AMD64-3.14/x86-CC architecture [9]. Second, more seriously, they are unsound with respect to current processors. The following n6 example, due to Paul Loewenstein [14], shows a behaviour that is observable (e.g. on an Intel Core 2 duo), but that is disallowed by x86-CC, and by any interpretation we can make of IWP and AMD64-3.14.

| n6                                         | proc:0                     | proc:1      |  |  |

|--------------------------------------------|----------------------------|-------------|--|--|

| poi:0                                      | MOV [x]←\$1                | MOV [y]←\$2 |  |  |

| poi:1                                      | MOV EAX $\leftarrow$ [x]   | MOV [x]←\$2 |  |  |

| poi:2                                      | $MOV \ EBX \leftarrow [y]$ |             |  |  |

| Final: $0:EAX=1 \land 0:EBX=0 \land [x]=1$ |                            |             |  |  |

| cc : Forbid; tso : Allow                   |                            |             |  |  |

To see why this may be allowed by multiprocessors with FIFO write buffers, suppose that first the proc:1 write of [y]=2 is buffered, then proc:0 buffers its write of [x]=1, reads [x]=1 from its own write buffer, and reads [y]=0 from main memory, then proc:1 buffers its [x]=2 write and flushes its buffered [y]=2 and [x]=2 writes to memory, then finally proc:0 flushes its [x]=1 write to memory.

#### 2.3 Intel SDM rev-29 (Nov. 2008)

The most recent x86 vendor specification, at the time of writing, is revision 29 of the Intel SDM (we are told that there will be a future revision of the AMD specification on similar lines). Key extracts are summarised in Appendix B. This is in a similar informal-prose style to previous versions, again supported by litmus tests, but is significantly different to IWP/AMD64-3.14/x86-CC. First, the IRIW final state above is forbidden [Example 7-7, rev-29], and the previous coherence condition: "P6. In a multiprocessor system, stores to the same location have a total order" has been replaced by: "P9. Any two stores are seen in a consistent order by processors other than those performing the stores".

Second, the memory barrier instructions are now included, with "P11. Reads cannot pass LFENCE and MFENCE instructions" and "P12. Writes cannot pass SFENCE and MFENCE instructions".

Third, same-processor writes are now explicitly ordered (we regarded this as implicit in the IWP "P2. Stores are not reordered with other stores"): "P10. Writes by a single processor are observed in the same order by all processors".

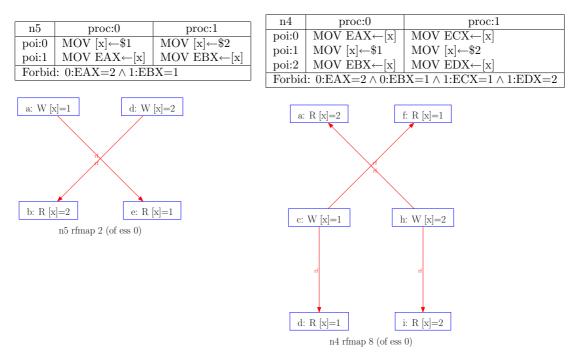

This specification appears to deal with the unsoundness, admitting the n6 behaviour above, but, unfortunately, it is still problematic. The first issue is, again, how to interpret "causality" as used in P5. The second issue is one of weakness: the new P9 says nothing about observations of two stores by those two processors themselves (or by one of those processors and one other). This is illustrated by the following n5 and n4 examples. These final states were not allowed in x86-CC, and we would be surprised if they were allowed by any reasonable implementation (they are not allowed in a pure write-buffer implementation). We have not observed them on actual processors, and programming above a model that permitted them would be problematic. However, rev-29 appears to allow them.

| n5                              | proc:0                   | proc:1                   |  |  |

|---------------------------------|--------------------------|--------------------------|--|--|

| poi:0                           | MOV [x]←\$1              | MOV [x]←\$2              |  |  |

| poi:1                           | MOV EAX $\leftarrow$ [x] | MOV EBX $\leftarrow$ [x] |  |  |

| Forbid: $0:EAX=2 \land 1:EBX=1$ |                          |                          |  |  |

| n4                                    | proc:0                     | proc:1                   |

|---------------------------------------|----------------------------|--------------------------|

| poi:0                                 | MOV EAX $\leftarrow$ [x]   | MOV ECX $\leftarrow$ [x] |

| poi:1                                 | MOV [x]←\$1                | MOV [x]←\$2              |

| poi:2                                 | $MOV \ EBX \leftarrow [x]$ | MOV EDX $\leftarrow$ [x] |

| Forbid: $0:EAX=2 \land 0:EBX=1 \land$ |                            |                          |

| $1:ECX=1 \land 1:EDX=2$               |                            |                          |

Summarising the key litmus-test differences, we have:

|       | IWP/AMD64-3.14/x86-CC | rev-29    | actual processors |

|-------|-----------------------|-----------|-------------------|

| IRIW  | allowed               | forbidden | not observed      |

| n6    | forbidden             | allowed   | observed          |

| n4/n5 | forbidden             | allowed   | not observed      |

There are also many non-differences: tests for which the behaviours coincide in all three cases. The test details can be found in Appendix A. They include the 9 other IWP tests, illustrating that various load and store reorderings other than that shown in iwp2.3.a/amd4 (§1) are not possible; the AMD MFENCE tests amd5 and amd10, and several other tests.

## 3 The x86-TSO Model

Given these problems with the informal specifications, we cannot produce a useful rigorous model by formalising the "principles" they contain (as we attempted with x86-CC [20]). Instead, we have to build a reasonable model that is consistent with the given litmus tests, observable processor behaviour, and with what we know of the needs of programmers and of the vendors intentions.

The fact that write buffering is observable (iwp2.3.a/amd4 and n6) but IRIW is not, together with the other tests that prohibit many other reorderings, strongly suggests that, apart from write buffering, all processors share the same view of memory (in contrast to x86-CC, where each processor had a separate view order). This is broadly similar to the SPARC Total Store Ordering (TSO) memory model [21, 23], which is essentially an axiomatic description of the behaviour of write-buffer multiprocessors. Moreover, while the term "TSO" is not used, informal discussions suggest this matches the intention behind the rev.29 informal specification. Accordingly, we define here a rigorous x86-TSO model.

After some preliminaries, we give two equivalent definitions of x86-TSO. The first, in §3.1, is an abstract machine, with explicit write buffers. The second, in §3.2, is an axiomatic model, defining valid executions in terms of memory orders and reads-from maps. In both, we deal with the x86 CISC instructions with multiple memory accesses, with x86 LOCK'd instructions (CMPXCHG, LOCK;INC, etc.), with potentially non-terminating computations, and with dependencies through registers. Together with our earlier instruction semantics, x86-TSO thus defines a complete semantics of programs.

The intended scope of x86-TSO, as for the x86-CC model, covers typical user code and most kernel code: programs using coherent write-back memory, without exceptions, misaligned or mixed-size accesses, 'non-temporal' operations (e.g. MOVNTI), self-modifying code, or page-table changes.

**Basic Types: Actions, Events, and Event Structures** As in our earlier work, the action of (any particular execution of) a program is abstracted into a set of *events* (with additional data) called an *event structure*. An event represents a read or write of a particular value to a memory address, or to a register, or the execution of a fence. Our earlier work includes a definition of the set of event structures generated by an assembly language program. For any such event structure, the memory model (there x86-CC, here x86-TSO) defines what a *valid execution* is.

In more detail, each machine-code instruction may have multiple events associated with it: events are indexed by an instruction ID *iiid* that identifies which processor the event occurred on and the position in the instruction stream of the instruction it comes from (the *program order index*, or *poi*). Events also have an event ID *eiid* to identify them within an instruction (to permit multiple, otherwise identical, events). An event structure indicates when one of an instruction's events has a dependency on another event of the same instruction with an *intra\_causality* relation, a partial order over the events of each instruction. An event structure also records which events occur together in a locked instruction with *atomicity* data, a set of (disjoint, non-empty) sets of events which must occur atomically together.

Expressing this in HOL, we index processors by a type proc = num, take types address and value to both be the 32-bit words, and take a location to be either a memory address or a register of a particular processor:

location = LOCATION\_REG of proc 'reg

| LOCATION\_MEM of address

The model is parameterised by a type 'reg of x86 registers, which one should think of as an enumeration of the names of ordinary registers EAX, EBX, etc., the instruction pointer EIP, and the status flags. To identify an instance of an instruction in an execution, we specify its processor and its program order index.

iiid =  $\langle proc : proc; poi : num \rangle$

This introduces a type of records with two fields, a *proc* of type **proc** and a program order index *poi* of type **num**. An action is either a read or write of a value at some location, or a barrier:

dirn =  $R \mid W$ barrier = LFENCE | SFENCE | MFENCE action = ACCESS of dirn ('reg location) value | BARRIER of barrier

Finally, an event has an instruction instance id, an event id (of type eiid = num, unique per iiid), and an action:

$event = \langle eiid : eiid; iiid : iiid; action : action \rangle$

and an event structure E comprises a set of processors, a set of events, an intra-instruction causality relation, and a partial equivalence relation (PER) capturing sets of events which must occur atomically, all subject to some well-formedness conditions which we omit here.

$\begin{array}{l} \mathsf{event\_structure} = \{ \begin{array}{l} \mathit{procs}: \mathsf{proc set}; \\ \mathit{events}: ('\mathit{reg} \; \mathsf{event}) \mathsf{set}; \\ \mathit{intra\_causality}: ('\mathit{reg} \; \mathsf{event}) \mathsf{reln}; \\ \mathit{atomicity}: ('\mathit{reg} \; \mathsf{event}) \mathsf{set} \; \mathsf{set} \\ \end{array} \end{array}$

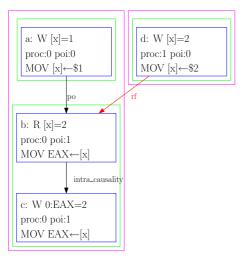

| <b>Example</b> We show a very simple event structure below, for the program: |

|------------------------------------------------------------------------------|

|------------------------------------------------------------------------------|

| tso1  | proc:0                   | proc:1                   |

|-------|--------------------------|--------------------------|

| poi:0 | MOV [x]←\$1              | MOV $[x] \leftarrow \$2$ |

| poi:1 | MOV EAX $\leftarrow$ [x] |                          |

There are four events — the inner (blue) boxes. The event ids are pretty-printed alphabetically, as a,b,c,d, etc. We also show the assembly instruction that gave rise to each event, e.g. MOV  $[x] \leftarrow \$1$ , though that is not formally part of the event structure.

tso1 rfmap 0 (of ess 0)

Note that events contain concrete values: in this particular event structure, there are two writes of x, with values 1 and 2, a read of [x] with value 2, and a write of proc:0's EAX register with value 2. Later we show two valid executions for this program, one for this event structure and one for another (note also that some event structures may not have any valid executions).

In the diagram, the instructions of each processor are clustered together, into the outermost (magenta) boxes, with program order (po) edges between them, and the events of each instruction are clustered together into the intermediate (green) boxes, with intra-causality edges as appropriate — here, in the MOV EAX $\leftarrow$ [x], the write of EAX is dependent on the read of x.

#### 3.1 The x86-TSO Abstract Machine Memory Model

To understand our x86-TSO machine model, consider an idealised x86 multiprocessor system partitioned into two components: its memory and register state (of all its processors combined), and the rest of the system (the other parts of all the processor cores). Our abstract machine is a labelled transition system: a set of states, ranged over by s, and a transition relation  $s \stackrel{l}{\rightarrow} s'$ . An abstract machine state s models the state of the first component, the memory and register state of a multiprocessor system, and the machine interacts with the rest of the system by synchronising on labels l (the interface of the abstract machine), which include register and memory reads and writes. One should think of the machine as operating in parallel with the processor cores (absent their register/memory subsystems), executing their instruction streams in program order; the latter data is provided by an event structure. This partitioning does not correspond directly to the microarchitecture of any realistic x86 implementation, in which memory and registers would be implemented by separate and intricate mechanisms, but it is useful and sufficient for describing the programming model, which is the proper business of an architecture description. It also supports a precise correspondence with our axiomatic memory model. In more detail, the labels l are the values of the HOL type:

label = TAU | EVT of proc ('reg action) | LOCK of proc | UNLOCK of proc

• TAU, for an internal action by the machine;

| Read from memory                                                                                                                                             |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| not_blocked $s \ p \land (s.M \ a = \text{SOME} \ v) \land \text{no_pending} \ (s.B \ p) a$                                                                  |  |  |  |

| $s \xrightarrow{\text{EVT } p \text{ (ACCESS } R \text{ (LOCATION_MEM } a)v)} s$                                                                             |  |  |  |

|                                                                                                                                                              |  |  |  |

| Read from write buffer                                                                                                                                       |  |  |  |

| not_blocked $s \ p \land (\exists b_1 \ b_2.(s.B \ p = b_1 ++[(a, v)] ++b_2) \land \text{no_pending} \ b_1 \ a)$                                             |  |  |  |

| $s \xrightarrow{\text{Evt } p \text{ (Access } R \text{ (Location_mem } a)v)} s$                                                                             |  |  |  |

| Read from register                                                                                                                                           |  |  |  |

| $(s.R \ p \ r = \text{Some} \ v)$                                                                                                                            |  |  |  |

| $s \xrightarrow{\text{Evt } p \text{ (Access } R \text{ (Location_Reg } p r)v)} s$                                                                           |  |  |  |

| 0 / 0                                                                                                                                                        |  |  |  |

| Write to write buffer                                                                                                                                        |  |  |  |

| Τ                                                                                                                                                            |  |  |  |

| $s \xrightarrow{\text{Evt } p \text{ (Access W (Location\_mem a)v)}} s \oplus \langle \!\![B := s.B \oplus (p \mapsto [(a, v)] + + (s.B \ p)) \rangle \!\!]$ |  |  |  |

| Write from write buffer to memory                                                                                                                            |  |  |  |

| not_blocked $s \ p \land (s.B \ p = b + + [(a, v)])$                                                                                                         |  |  |  |

| $s \xrightarrow{\text{TAU}} s \oplus \langle\!\![M := s.M \oplus (a \mapsto \text{Some } v); B := s.B \oplus (p \mapsto b) \rangle\!\!\rangle$               |  |  |  |

| Write to register                                                                                                                                            |  |  |  |

| T                                                                                                                                                            |  |  |  |

| $s \xrightarrow{\text{Evt } p \text{ (Access W (Location_{REG} p r)v)}} s \oplus (R := s.R \oplus (p \mapsto ((s.R p) \oplus (r \mapsto \text{Some } v))))$  |  |  |  |

| Barrier                                                                                                                                                      |  |  |  |

| $(b = \text{MFENCE}) \implies (s.B \ p = [])$                                                                                                                |  |  |  |

| $\frac{(b = \text{MFENCE}) \implies (s.B \ p = [])}{s} \xrightarrow{\text{Evt } p \ (\text{Barrier } b)} s$                                                  |  |  |  |

| Lock                                                                                                                                                         |  |  |  |

| $(s.L = \text{NONE}) \land (s.B \ p = [])$                                                                                                                   |  |  |  |

| $s \xrightarrow{\text{Lock } p} s \oplus (\!\![L := \text{Some } p]\!\!)$                                                                                    |  |  |  |

| Unlock                                                                                                                                                       |  |  |  |

| $(s.L = \text{Some } p) \land (s.B \ p = [])$                                                                                                                |  |  |  |

| $s \xrightarrow{\text{UNLOCK } p} s \oplus \langle\!\![L := \text{NONE}\rangle\!\!\rangle$                                                                   |  |  |  |

Figure 1: The x86-TSO Machine Behaviour

- EVT p a, where a is an action, as defined above (a memory or register read or write, with its value, or a barrier), by processor p;

- LOCK p, indicating the start of a LOCK'd instruction by processor p; or

- UNLOCK p, for the end of a LOCK'd instruction by p.

(Note that there is nothing specific to any particular memory model in this interface.) The states of the x86-TSO machine are records, with fields R, giving a value for each register on each processor; M, giving a value for each shared memory location; B, modelling a write buffer for each processor, as a list of address/value pairs; and L, which is a global lock, either SOME p, if p holds the lock, or NONE. The HOL type is below.

$\begin{aligned} \mathsf{machine\_state} = & \{ \begin{array}{l} R: \mathsf{proc} \to '\mathit{reg} \to \mathsf{value} \ \mathsf{option}; (* \ \mathsf{per-processor} \ \mathsf{registers} \ *) \\ M: \mathsf{address} \to \mathsf{value} \ \mathsf{option}; (* \ \mathsf{main} \ \mathsf{memory} \ *) \\ B: \mathsf{proc} \to (\mathsf{address}\#\mathsf{value})\mathsf{list}; (* \ \mathsf{per-processor} \ \mathsf{write} \ \mathsf{buffers} \ *) \\ L: \mathsf{proc} \ \mathsf{option}(* \ \mathsf{which} \ \mathsf{processor} \ \mathsf{holds} \ \mathsf{the} \ \mathsf{lock} \ *) \\ \end{aligned} \end{aligned}$

The behaviour of the x86-TSO machine, the transition relation  $s \xrightarrow{l} s'$ , is defined by the rules in Fig. 1. The rules use two auxiliary definitions: processor p is not blocked in machine state s if either it holds the lock or no processor does; and there are no pending writes in a buffer b for address a if there are no (a, v) pairs in b. Restating the rules informally:

- 1. p can read v from memory at address a if p is not blocked, has no buffered writes to a, and the memory does contain v at a;

- 2. p can read v from its write buffer for address a if p is not blocked and has v as the newest write to a in its buffer;

- 3. p can read the stored value v from its register r at any time;

- 4. p can write v to its write buffer for address a at any time;

- 5. if p is not blocked, it can silently dequeue the oldest write from its write buffer to memory;

- 6. p can write value v to one of its registers r at any time;

- 7. if *p*'s write buffer is empty, it can execute an MFENCE (so an MFENCE cannot proceed until all writes have been dequeued, modelling buffer flushing); LFENCE and SFENCE can occur at any time, making them no-ops;

- 8. if the lock is not held, and p's write buffer is empty, it can begin a LOCK'd instruction; and

- 9. if p holds the lock, and its write buffer is empty, it can end a LOCK'd instruction.

We emphasise that this is an *abstract* machine: we are concerned with its extensional behaviour, the (completed, finite or infinite) traces of labelled transitions it can perform (which should include the behaviour of real implementations), not with its internal states and the transition rules. The machine should provide a good model for programmers, but may bear little resemblance to the internal structure of implementations. Indeed, a realistic design would certainly not implement LOCK'd instructions with a global lock, and would have many other optimisations — the force of the x86-TSO model is that none of those have *programmer-visible* effects, except perhaps via performance observations.

One can imagine several variants of the machine with different degrees of locking. We conjecture that one could additionally make the read-register, write-register, write-buffer, and barrier transitions dependent on a not\_blocked premise to arrive at a stricter, but observationally equivalent, machine, that might be simpler for programmers to reason with. However, the additions would make the proof of equivalence to the axiomatic memory model more difficult. We also conjecture that removing the not\_blocked premise from the read-memory transition, and removing the requirement that the buffer is empty on a Lock label, would give a more liberal, but equivalent, machine. Again the equivalence proof would be more difficult. Should either of these variant machines become useful, we anticipate being able to prove them equivalent by working solely on the machines. We relate the machine to event structures in two steps, which we summarise here (the HOL details can be found on-line [22] and are summarised in Appendix E). First, we define a more intensional event-machine: we annotate each memory and register location with an event option, recording the most recent write event (if any) to that location, refine write buffers to record lists of events rather than of plain location/value pairs, and annotate labels with the relevant events.

**Theorem 1** The annotation-erasure of the event-machine is exactly the machine presented above. [HOL proof]

Let *path* range over finite or infinite sequences of states and labels  $s_0 \xrightarrow{l_1} s_1 \xrightarrow{l_1} s_1 \cdots$ . We define (okMpath *path*) to hold if *path* is a path through the event-machine, the first state is an initial machine state, with empty write buffers, etc., and a progress condition holds: for each memory write in *path*, the corresponding TAU is eventually performed. Finally, given an event structure E, we say such a *path* is a machine execution corresponding to that event structure if (okEpath E *path*), i.e., if there is a 1:1 correspondence between non-TAU/LOCK/UNLOCK labels of *path* and the events of E, consistent with program order and intra-causality, and atomic sets are properly bracketed by LOCK/UNLOCK pairs.

### 3.2 The x86-TSO Axiomatic Memory Model

Our x86-TSO axiomatic memory model is based on the SPARCv8 memory model specification [21, 23], but adapted to x86 and in the same terms as our earlier x86-CC model. Compared with the SPARCv8 TSO specification, we omit instruction fetches (IF), instruction loads (IL), flushes (F), and stbars (-S). The first three deal exclusively with instruction memory, which we do not model, and the last is useful only under the SPARC PSO memory model. To adapt it to x86 programs, we add register and fence events, generalize to support instructions that give rise to many events (partially ordered by an intra-instruction causality relation), and generalize atomic load/store pairs to locked instructions.

An execution is permitted by our memory model if there exists an *execution witness* X for its event structure E that is a *valid execution*. An execution witness contains a *memory\_order*, an *rfmap*, and an *initial\_state*; the rest of this section defines when these are valid.

execution\_witness =  $\langle [memory_order : ('reg event)reln; rfmap : ('reg event)reln; initial_state : ('reg location <math>\rightarrow$  value option)]

The memory order is a partial order that records the global ordering of memory events. It must be a total order on memory writes, and corresponds to the  $\leq$  relation in SPARCv8, as constrained by the SPARCv8 **Order** condition (in figures, we use the label mo\_non-po\_write\_write for the otherwise-unforced part of this order).

partial\_order  $(\langle X.memory\_order \rangle)$  (mem\_accesses E) linear\_order  $(\langle X.memory\_order \rangle)|_{(mem\_writes E)})$  (mem\_writes E)

The initial state is a partial function from locations to values. Each read event's value must come either from the initial state or from a write event: the rfmap ('reads-from map') records which, containing (ew, er) pairs where the read er reads from the write ew. The  $reads\_from\_map\_candidates$  predicate below ensures that the rfmap only relates such pairs with the same address and value. (The SPARCv8 model does not have an explicit representation of reads-from maps, and does not deal with initial states.)

reads\_from\_map\_candidates  $E \ rfmap =$  $\forall (ew, er) \in rfmap.(er \in reads \ E) \land (ew \in writes \ E) \land$  $(loc \ ew = loc \ er) \land (value_of \ ew = value_of \ er)$

We lift program order from instructions to a relation  $po_{-iico} E$  over events, taking the union of program order of instructions and intra-instruction causality. This corresponds roughly to the ; in SPARCv8. However, *intra\_causality* might not relate some pairs of events in an instruction, so our po\_iico E will not generally be a total order for the events of a processor.

po\_strict E =

$\{(e_1, e_2) \mid (e_1.iiid.proc = e_2.iiid.proc) \land e_1.iiid.poi < e_2.iiid.poi \land e_1 \in E.events \land e_2 \in E.events\}$

$<_{(\text{po_iico }E)} = \text{po_strict }E \cup E.intra_causality$

The *check\_rfmap\_written* below ensures that the rfmap relates a read to the most recent preceding write. For a register read, this is the most recent write in program order. For a memory read, this is the most recent write in memory order among those that precede the read in either memory order or program order (intuitively, the first case is a read of a committed write and the second is a read from the local write buffer). The check\_rfmap\_written and reads\_from\_map\_candidates predicates implement the SPARCv8 Value axiom above the rfmap witness data. The *check\_rfmap\_initial* predicate extends this to handle initial state, ensuring that any read not in the rfmap takes its value from the initial state, and that that read is not preceded by a write in memory order or program order.

previous\_writes  $E \ er <_{order} =$   $\{ew' \mid ew' \in \text{ writes } E \land ew' <_{order} \ er \land (\text{loc } ew' = \text{loc } er)\}$ check\_rfmap\_written  $E \ X =$   $\forall (ew, er) \in (X.rfmap).$  **if**  $ew \in \text{mem}_\text{accesses } E$  **then**   $ew \in \text{maximal\_elements (previous\_writes } E \ er \ (<_{X.memory\_order}) \cup$   $previous\_writes \ E \ er \ (<_{(\text{po\_iico } E)}))$   $(<_{X.memory\_order})$  **else** (\* ew IN reg\_accesses E \*)  $ew \in \text{maximal\_elements (previous\_writes } E \ er \ (<_{(\text{po\_iico } E)}))(<_{(\text{po\_iico } E)})$ check\_rfmap\_initial  $E \ X =$  $\forall er \in (\text{reads } E \ \text{range } X.rfmap).$

$\forall er \in (\text{reads } E \setminus \text{range } X.rfmap).$   $(\exists l.(\text{loc } er = \text{SOME } l) \land (\text{value_of } er = X.initial\_state \ l)) \land$   $(\text{previous\_writes } E \ er \ (<_{X.memory\_order}) \cup$   $\text{previous\_writes } E \ er \ (<_{(\text{po\_iico } E)}) = \{\})$

We now further constrain the memory order, to ensure that it respects the relevant parts of program order, and that the memory accesses of a LOCK'd instruction do occur atomically.

• Program order is included in memory order, for a memory read before a memory access (labelled mo\_po\_read\_access in figures) (SPARCv8's LoadOp):

$\forall er \in (\text{mem\_reads } E). \forall e \in (\text{mem\_accesses } E).$  $er <_{(\text{po\_iico } E)} e \implies er <_{X.memory\_order} e$

• Program order is included in memory order, for a memory write before a memory write (mo\_po\_write\_write) (the SPARCv8 **StoreStore**):

$\forall ew_1 \ ew_2 \in (\text{mem\_writes} \ E). \\ ew_1 <_{(\text{po\_iico} \ E)} ew_2 \implies ew_1 <_{X.memory\_order} ew_2$

• Program order is included in memory order, for a memory write before a memory read, *if* there is an MFENCE between (mo\_po\_mfence). (There is no need to include fence events themselves in the memory ordering.)

$\forall ew \in (\text{mem\_writes } E). \forall er \in (\text{mem\_reads } E). \forall ef \in (\text{mfences } E). \\ (ew <_{(\text{po\_iico } E)} ef \land ef <_{(\text{po\_iico } E)} er) \implies ew <_{X.memory\_order} er$

• Program order is included in memory order, for any two memory accesses where at least one is from a LOCK'd instruction (mo\_po\_access/lock):

$\begin{array}{l} \forall e_1 \ e_2 \in (\text{mem\_accesses} \ E). \forall e_s \in (E. atomicity). \\ ((e_1 \ \in \ e_s \lor e_2 \ \in \ e_s) \land e_1 <_{(\text{po\_ico} \ E)} e_2) \implies e_1 <_{X.memory\_order} e_2 \end{array}$

• The memory accesses of a LOCK'd instruction occur atomically in memory order (mo\_atomicity), i.e., there must be no intervening memory events. Further, all program order relationships between the locked memory accesses and other memory accesses are included in the memory order (this is a generalization of the SPARCv8 **Atomicity** axiom):

$\forall es \in (E.atomicity). \forall e \in (\text{mem\_accesses } E \setminus es). \\ (\forall e' \in (es \cap \text{mem\_accesses } E). e <_{X.memory\_order} e') \lor \\ (\forall e' \in (es \cap \text{mem\_accesses } E). e' <_{X.memory\_order} e)$

To deal properly with infinite executions, we also require that the prefixes of the memory order are all finite, ensuring that there are no limit points, and, to ensure that each write eventually takes effect globally, there must not be an infinite set of reads unrelated to any particular write, all on the same memory location (this formalizes the SPARCv8 **Termination** axiom).

finite\_prefixes  $(<_{X.memory\_order})$  (mem\_accesses E)

$\begin{array}{l} \forall ew \in (\text{mem\_writes } E). \\ \text{finite} \{ er \mid er \in E.events \land (\text{loc } er = \text{loc } ew) \land \\ er \not<_{X.memory\_order} ew \land ew \not<_{X.memory\_order} er \} \end{array}$

A final state of a valid execution takes the last write in memory order for each memory location, together with a maximal write in program order for each register (or the initial state, if there is no such write). This is uniquely defined assuming that no instruction has multiple unrelated writes to the same register — a reasonable property for x86 instructions.

The definition of valid\_execution E X comprising the above conditions is equivalent to one in which  $<_{X.memory\_order}$  is required to be a linear order, not just a partial order (again, the full details are on-line):

#### Theorem 2

- 1. If linear\_valid\_execution E X then valid\_execution E X.

- 2. If valid\_execution E X then there exists an  $\hat{X}$  with a linearisation of X's memory order such that linear\_valid\_execution  $E \hat{X}$ . [HOL proof]

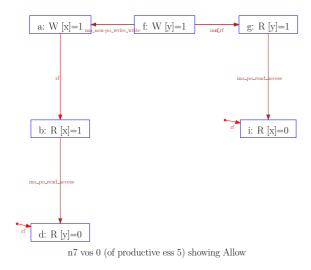

**Interpreting "not reordered with"** Perhaps surprisingly, the above definition does not require that program order is included in memory order for a memory write followed by a read from the same address. The definition does imply that any such read cannot be speculated before the write (by check\_rfmap\_written, as that takes both  $<_{(\text{po_lico } E)}$  and  $<_{X.memory\_order}$  into account). However, if one included a memory order edge, perhaps following a naive interpretation of the rev-29 "P4. Reads may be reordered with older writes to different locations but not with older writes to the same location", then the model would be strictly stronger: the n7 example below would become forbidden, whereas it is allowed on x86-TSO. We conjecture that this would correspond to the (rather strange) machine with the Fig. 1 rules but without the read-from-write-buffer rule, in which any processor would have to flush its write buffer up to (and including) a local write before it can read from it.

| n7    | proc:0                                                     | proc:1      | proc:2                   |  |  |

|-------|------------------------------------------------------------|-------------|--------------------------|--|--|

| poi:0 | MOV [x]←\$1                                                | MOV [y]←\$1 | MOV ECX $\leftarrow$ [y] |  |  |

| poi:1 | MOV EAX $\leftarrow$ [x]                                   |             | MOV EDX $\leftarrow$ [x] |  |  |

| poi:2 | MOV EBX $\leftarrow$ [y]                                   |             |                          |  |  |

| Allow | Allow: $0:EAX=1 \land 0:EBX=0 \land 2:ECX=1 \land 2:EDX=0$ |             |                          |  |  |

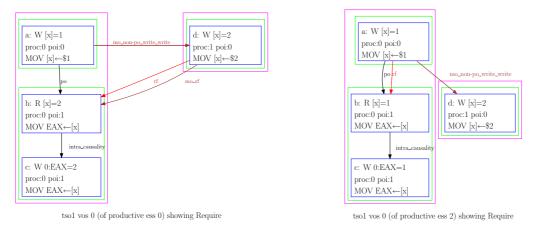

**Examples** We show two valid executions of the previous example program in Fig. 2. In both executions, the proc:0 W x=1 event is before the proc:1 W x=2 event in memory order (the bold mo\_non-po\_write\_write edge). In the first execution, on the left, the proc:0 read of x reads from the most recent write in memory order (the combination of the bold mo\_non-po\_write\_write edge and the mo\_rf edge), which is the proc:1 W x=2. In the second execution, on the right, the proc:0 read of x reads from the most recent write in program order, which is the proc:0 W x=1. This example also illustrates some register events: the MOV EAX $\leftarrow$ [x] instruction gives rise to a memory read of x, followed by (in the intra-instruction causality relation) a register write of EAX.

Figure 2: Example valid execution witnesses (for two different event structures)

#### 3.3 The Machine and Axiomatic x86-TSO Models are Equivalent

To show these two definitions equivalent, given an event-machine *path*, we first build an execution witness path\_to\_X *path*, putting the memory reads and write-buffer flushes (TAUs) in their (linear) order from *path*. Now:

**Theorem 3** For any well-formed event structure E and event-machine path path, if okEpath E path and okMpath path, then path\_to\_X path is a valid execution for E. [HOL proof]

**Theorem 4** For any well-formed event structure E, and valid execution X for E, there exists some event-machine path, such that okEpath E path and okMpath path, in which the memory reads and write-buffer flushes both respect  $<_{X.memory\_order}$ . [hand proof, with some parts in HOL]

## 4 Verified Checker and Results

To explore the consequences of x86-TSO, we implemented the axiomatic model in our memevents tool, which exhaustively explores candidate execution witnesses. For greater confidence, we added to this a verified witness checker: we defined variants of event structures and execution witnesses, using lists instead of sets, wrote algorithmic versions of well\_formed\_event\_structure and valid\_execution, proved these equivalent (in the finite case) to our other definitions, extracted OCaml code from the HOL, and integrated that into memevents. (Obviously, this only provides assurance for positive tests, those with allowed final states.)

The memevents results coincide with our observations on real processors and the vendor specifications, for the 10 IWP tests, the (negated) IRIW test, the two MFENCE tests amd5 and amd10, our n2–n6 and n8, and rwc-fenced. The remaining tests (amd3, n1, n7, and rwc-unfenced) are "allow" tests for which we have not observed the specified final state in practice.

## 5 Related Work

There is an extensive literature on relaxed memory models, but most of it does not address x86, and we are not aware of any previous model that addresses the concerns of §2. We touch here on some of the most closely related work.

There are several surveys of weak memory models, including those by Adve and Gharachorloo [3], by Luchango [16], and by Higham, Kawash, and Verwaal [13]. The latter, in particular, formalises a range of models, including a TSO model, in both operational and axiomatic styles, and proves equivalence results. Their axiomatic TSO model is in a different style to ours, rather closer to the machine behaviour, and idealised rather than x86-specific. Burckhardt and Musuvathi [7, Appendix A] also give operational and axiomatic definitions of a TSO model and prove equivalence, but only for finite executions. Their models treat memory read, memory write and barrier events, but lack register events and locked instructions that force multiple events to happen atomically. Hangel et al. [10] describe the Sun TSOtool, checking the observed behaviour of pseudo-randomly generated programs against a TSO model. Roy et al. [17] describe an efficient algorithm for checking whether an execution lies within an approximation to a TSO model, used in Intel's Random Instruction Test (RIT) generator. Boudol and Petri [6] give an operational model with hierarchical write buffers (thereby permitting IRIW behaviours), and prove sequential consistency for data-race-free (DRF) programs. Burckhardt et al. [8] define an x86 memory model based on IWP [12] (together with two MS CLR models). The mathematical form of their definitions is rather different to ours, using rewrite rules to re-order or eliminate memory accesses in sets of traces. Their model validates the 10 IWP tests and also some instances of IRIW (depending on how parallel compositions are associated), so it will not coincide with x86-TSO or x86-CC. Loewenstein et al. [15] describe a "golden memory model" for SPARC TSO, somewhat closer to a particular implementation microarchitecture than the abstract machine we give in §3.1, that they use for testing implementations. They argue that the additional intensional detail increases the effectiveness of simulation-based verification. Roychoudhury [18] describes a system for exhaustive search of executions in a logic programming system for versions of SPARC TSO and the Java Memory Model. Saraswat et al. [19] also define memory models in terms of local reordering, and prove a DRF theorem, but focus on high-level languages rather than processors. Several groups have used proof tools to tame the intricacies of these models, including Yang et al. [24], using Prolog and SAT solvers to explore an axiomatic Itanium model, and, turning briefly to high-level languages, Aspinall and Sevcik [4], who formalised and identified problems with the Java Memory Model using Isabelle/HOL.

## 6 Conclusion

We have described x86-TSO, a memory model for x86 processors that does not suffer from the ambiguities, weaknesses, or unsoundnesses of earlier models. Its abstract-machine definition should be intuitive for programmers, whereas its equivalent axiomatic definition supports the memevents exhaustive search and permits an easy comparison with related models; the similarity with SPARCv8 suggests x86-TSO is strong enough to program above. Mechanisation in HOL4 revealed a number of subtle points of detail, including some of the well-formed event structure conditions that we depend on (e.g. that instructions have no *internal* data races). We hope this will clarify the semantics of x86 architectures.

Acknowledgements We thank Luc Maranget for his work on memevents, and David Christie, Dave Dice, Doug Lea, Paul Loewenstein, Gil Neiger, and Francesco Zappa Nardelli for their helpful remarks. We acknowledge funding from EPSRC grant EP/F036345.

## A Litmus Tests and Discussion

In this appendix we go through a number of litmus tests, including all those from the Intel IWP [12], the Intel SDM (Rev-29) [2], the AMD64 APM [1], and some others.

Tests are named iwpXXX, for the test numbered XXX from IWP, amdNNN, for the NNN'th test from the AMD64 APM, or nNNN, for other tests. We let x and y range over distinct aligned memory locations. Unless otherwise stated, all tests are considered with respect to an initial state in which those locations and all registers contain 0. We write assembly instructions in Intel syntax (as opposed to the AT&T syntax used by gcc and gas) except that we write an arrow  $\leftarrow$  instead of a comma, to clarify the direction of data flow.

The results of the tests, in x86-CC, x86-TSO, and our observations on actual processors, are summarised in §A.9. In all cases the x86-TSO behaviours are consistent with our observations, though it does permit some behaviours that we have not observed. In other words, this data does not contradict the claim that x86-TSO is sound.

### A.1 Load/Store Reordering

#### Rev-29 Example 7-1. Stores Are Not Reordered with Other Stores.

| iwp2.1/amd1                     | proc:0      | proc:1                      |  |

|---------------------------------|-------------|-----------------------------|--|

| poi:0                           | MOV [x]←\$1 | MOV EAX $\leftarrow$ [y]    |  |

| poi:1                           | MOV [y]←\$1 | $MOV \ EBX {\leftarrow}[x]$ |  |

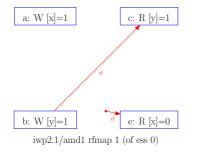

| Forbid: $1:EAX=1 \land 1:EBX=0$ |             |                             |  |

This is Test 2.1 in the Intel White Paper (IWP), and also the first test in the AMD64-3.14. There are two stores on one processor to two different locations, and the other processor loads from those locations in the opposite order. Executions in which the first load reads from the second store, but the second load reads from the initial state, not from the first store, are forbidden. We illustrate such executions below, in a diagram showing the reads-from map over the memory events (eliding register events and the *eiid* and *iiid* data of each memory event). This test also shows that loads are not reordered with other loads.

Rev-29 Example 7-2. Stores Are Not Reordered with Older Loads.

| iwp2.2/amd2                     | proc:0                   | proc:1                   |  |

|---------------------------------|--------------------------|--------------------------|--|

| poi:0                           | $MOV EAX \leftarrow [x]$ | MOV EBX $\leftarrow$ [y] |  |

| poi:1                           | MOV [y]←\$1              | MOV [x]←\$1              |  |

| Forbid: $0:EAX=1 \land 1:EBX=1$ |                          |                          |  |

Here the two processors read a value, from two different locations respectively, and then each stores a value to the other location. Executions as shown below, in which each reads from the write of the other

processor, are forbidden.

Rev-29 Example 7-3. Loads May be Reordered with Older Stores.

| iwp2.3.a/amd4                  | proc:0                   | proc:1                   |  |

|--------------------------------|--------------------------|--------------------------|--|

| poi:0                          | MOV [x]←\$1              | MOV [y]←\$1              |  |

| poi:1                          | MOV EAX $\leftarrow$ [y] | MOV EBX $\leftarrow$ [x] |  |

| Allow: $0:EAX=0 \land 1:EBX=0$ |                          |                          |  |

This test illustrates non-sequentially-consistent behaviour allowed by store buffering, as discussed in §1. Each processor stores to one location and loads from the other location. Both loads are allowed to read from the initial state. We illustrate one such allowed execution below.

| <sup>rf</sup> b: R [y]=0 | rf e: R [x]=0                  |   |

|--------------------------|--------------------------------|---|

| iwp2.3.a/amd4 vos 1 (of  | productive ess 3) showing Allo | w |

Rev-29 Example 7-4. Loads Are not Reordered with Older Stores to the Same Location.

| iwp2.3.b                         | proc:0                   | proc:1                      |

|----------------------------------|--------------------------|-----------------------------|

| poi:0                            | MOV [x]←\$1              | MOV [y]←\$1                 |

| poi:1                            | $MOV EAX \leftarrow [x]$ | $MOV \ EBX {\leftarrow}[y]$ |

| Require: $0:EAX=1 \land 1:EBX=1$ |                          |                             |

This is variant of the previous test in which each load reads from the same location as that processor stored to. Here they are forced to read from the local store. Operationally, loads must read from the local store buffer if it contains a write to the address in question. All executions must satisfy the 'Require' condition; one such is shown below. (The Rev-29 example is identical to the proc:0 part of iwp2.3.b; the proc:1 part adds no more force).

iwp2.3.b vos 1 (of productive ess 0) showing Require

Rev-29 Example 7-5. Intra-Processor Forwarding is Allowed.

| iwp2.4/amd9                    | proc:0                   | proc:1                   |

|--------------------------------|--------------------------|--------------------------|

| poi:0                          | MOV [x]←\$1              | MOV [y]←\$1              |

| poi:1                          | MOV EAX $\leftarrow$ [x] | MOV ECX $\leftarrow$ [y] |

| poi:2                          | $MOV EBX \leftarrow [y]$ | $MOV EDX \leftarrow [x]$ |

| Allow: $0:EBX=0 \land 1:EDX=0$ |                          |                          |

This test is a variant of Example 7-3 (iwp2.3.a/amd4) in which each processor stores to a location *then* reads from that location before reading from the other location. Again, store buffers allow the specified final state, and one such execution is shown below.

iwp2.4/amd9 vos 1 (of productive ess 3) showing Allow

Rev-29 Example 7-6. Stores Are Transitively Visible.

| iwp2.5/amd8                                   | proc:0      | proc:1                   | proc:2                   |

|-----------------------------------------------|-------------|--------------------------|--------------------------|

| poi:0                                         | MOV [x]←\$1 | MOV EAX $\leftarrow$ [x] | MOV EBX $\leftarrow$ [y] |

| poi:1                                         |             | MOV [y]←\$1              | MOV ECX $\leftarrow$ [x] |

| Forbid: $1:EAX=1 \land 2:EBX=1 \land 2:ECX=0$ |             |                          |                          |

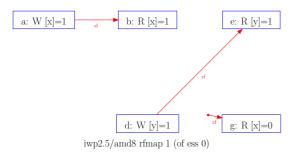

This test shows that a particular transitive chain of causality must be respected. Here proc:1 reads proc:0's write to x, then (in program order) proc:1 writing to y; proc:2 reads from that write of y, then (in program order) proc:1 reads x. That final read is not allowed to be from the initial state. The forbidden reads-from relationship is shown below. The Write-to-Read Causality (WRC) test of Boehm and Adve [5, Fig. 5] is similar to this test, but with fences between the proc:1 and proc:2 pairs of instructions. In x86-TSO the final state is forbidden without requiring such fences.

AMD3.14 Test 3

| amd3                           | proc:0                   | proc:1                   |

|--------------------------------|--------------------------|--------------------------|

| poi:0                          | MOV [x]←\$1              | MOV [y]←\$1              |

| poi:1                          | MOV [x]←\$2              | MOV [y]←\$2              |

| poi:2                          | MOV EAX $\leftarrow$ [y] | MOV EBX $\leftarrow$ [x] |

| Allow: $0:EAX=1 \land 1:EBX=1$ |                          |                          |

This test is another variant of Example 7-3 (iwp2.3.a/amd4) in which each processor stores to a location *then stores again to that location* before reading from the other location. Again, store buffers allow each processor to read from the first write of the other processor, and one such execution is shown below.

amd<br/>3 vos0 (of productive ess4) showing Allow

IWP Test 2.6. Total Order on Stores to the Same Location

| iwp2.6  | proc:0                                                      | proc:1                   | proc:2                      | proc:3                   |  |

|---------|-------------------------------------------------------------|--------------------------|-----------------------------|--------------------------|--|

| poi:0   | MOV [x]←\$1                                                 | MOV $[x] \leftarrow \$2$ | MOV EAX $\leftarrow$ [x]    | MOV ECX $\leftarrow$ [x] |  |

| poi:1   |                                                             |                          | $MOV \ EBX {\leftarrow}[x]$ | $MOV EDX \leftarrow [x]$ |  |

| Forbid: | Forbid: $2:EAX=1 \land 2:EBX=2 \land 3:ECX=2 \land 3:EDX=1$ |                          |                             |                          |  |

This test requires stores to the same location by two processors to be observed in the same order by two other processors. The forbidden reads-from relation is shown below. The test was in IWP, but is no longer present in rev-29.

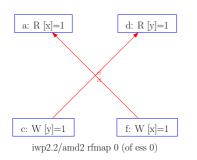

#### A.2 Independent Reads of Independent Writes

The following IRIW example, discussed here in §2.2 and by Boehm and Adve [5], has a final state permitted in AMD64-3.14 (explicitly), in IWP (implicitly), and in x86-CC. Rev-29, however, contains the same example but with the given final state forbidden (rev-29 Example 7-7. Stores Are Seen in a Consistent Order by Other Processors). We have not observed the final state in practice, and it is forbidden in x86-TSO. The reads-from relation required for the given final state is below; in such executions, proc:0 and proc:1 write to two different locations, and proc:2 and proc:3 read from those locations, seeing the writes in opposite orders (proc:2 sees the write to x but not the write to y, reading y from the initial state, whereas proc:3 sees the write to x but reads x from the initial state).

| amd6                                                       | proc:0      | proc:1      | proc:2                   | proc:3                   |

|------------------------------------------------------------|-------------|-------------|--------------------------|--------------------------|

| poi:0                                                      | MOV [x]←\$1 | MOV [y]←\$1 | MOV EAX $\leftarrow$ [x] | MOV ECX $\leftarrow$ [y] |

| poi:1                                                      |             |             | MOV EBX $\leftarrow$ [y] | $MOV EDX \leftarrow [x]$ |

| Final: $2:EAX=1 \land 2:EBX=0 \land 3:ECX=1 \land 3:EDX=0$ |             |             |                          |                          |

| cc : Allow; tso : Forbid                                   |             |             |                          |                          |

### A.3 Locked Instructions: Tests iwp2.7/amd7, iwp2.8.a, iwp2.8.b, n8, and n3

Only the following three IWP litmus tests involve locked instructions, and none of the three forbidden results are allowed in x86-TSO. However, only iwp2.8.a is forbidden by the parts of x86-TSO dealing with locking; the other two are forbidden by the core TSO properties directly (i.e., even if hypothetical non-locked versions of the XCHG instructions were used).

#### Rev-29 Example 7-8. Locked Instructions Have a Total Order.

| iwp2.7/amd7                                            | proc:0                                                      | proc:1       | proc:2                   | proc:3                   |  |

|--------------------------------------------------------|-------------------------------------------------------------|--------------|--------------------------|--------------------------|--|

| poi:0                                                  | XCHG [x]←EAX                                                | XCHG [y]←EBX | MOV ECX $\leftarrow$ [x] | MOV ESI←[y]              |  |

| poi:1                                                  |                                                             |              | MOV EDX $\leftarrow$ [y] | $MOV EDI \leftarrow [x]$ |  |

| Initial state: $0:EAX = 1$ ; $1:EBX = 1$ (elsewhere 0) |                                                             |              |                          |                          |  |

| Forbid: 2:ECX                                          | Forbid: $2:ECX=1 \land 2:EDX=0 \land 3:ESI=1 \land 3:EDI=0$ |              |                          |                          |  |

This is a variant of the IRIW example amd6 but using XCHG instructions (which are implicitly LOCK'd) instead of MOV instructions on proc:0 and proc:1.

#### Rev-29 Example 7-9. Loads Are not Reordered with Locks.

| iwp2.8.a                                               | proc:0                   | proc:1                    |

|--------------------------------------------------------|--------------------------|---------------------------|

| poi:0                                                  | XCHG [x]←EAX             | XCHG $[y] \leftarrow ECX$ |

| poi:1                                                  | MOV EBX $\leftarrow$ [y] | $MOV EDX \leftarrow [x]$  |

| Initial state: $0:EAX = 1$ ; $1:ECX = 1$ (elsewhere 0) |                          |                           |

| Forbid: $0:EBX=0 \land 1:EDX=0$                        |                          |                           |

#### Rev-29 Example 7-10. Stores Are not Reordered with Locks.

| iwp2.8.b                                 | proc:0       | proc:1                   |  |  |

|------------------------------------------|--------------|--------------------------|--|--|

| poi:0                                    | XCHG [x]←EAX | MOV EBX $\leftarrow$ [y] |  |  |

| poi:1                                    | MOV [y]←\$1  | $MOV ECX \leftarrow [x]$ |  |  |

| Initial state: $0:EAX = 1$ (elsewhere 0) |              |                          |  |  |

| Forbid: 1:EBX= $1 \land 1$ :ECX= $0$     |              |                          |  |  |

Test n8. Loads Are not Reordered with Locks — Single-XCHG Variant.

| n8                                                | proc:0                   | proc:1                   |  |

|---------------------------------------------------|--------------------------|--------------------------|--|

| poi:0                                             | XCHG [x]←EAX             | MOV [y]←\$1              |  |

| poi:1                                             | MOV EBX $\leftarrow$ [y] | MOV EDX $\leftarrow$ [x] |  |

| Initial state: $0:EAX = 1; [y] = 1$ (elsewhere 0) |                          |                          |  |

| Allow: $0:EAX=0 \land 1:EDX=0$                    |                          |                          |  |

This test is a variant of iwp2.8.a, but with an unlocked write in place of one of the XCHG instructions. The x86-TSO model allows the result where EBX and EDX are both 0.

Test n3: Independent Locked Instructions and Stores

| n3                                                                                             | proc:0                    | proc:1      | proc:2                   | proc:3                   |

|------------------------------------------------------------------------------------------------|---------------------------|-------------|--------------------------|--------------------------|

| poi:0                                                                                          | XCHG EAX $\leftarrow$ [x] | MOV [y]←\$1 | MOV EBX $\leftarrow$ [y] | MOV ESI←[x]              |

| poi:1                                                                                          |                           |             | MOV ECX $\leftarrow$ [x] | MOV EDI $\leftarrow$ [y] |

| poi:2                                                                                          |                           |             | MOV EDX $\leftarrow$ [x] | MOV $EBP \leftarrow [y]$ |

| Initial state: $0:EAX = 1$ (elsewhere 0)                                                       |                           |             |                          |                          |

| Final: 2:EBX=1 $\land$ 2:ECX=0 $\land$ 2:EDX=1 $\land$ 3:ESI=1 $\land$ 3:EDI=0 $\land$ 3:EBP=1 |                           |             |                          |                          |

| cc : Allow; tso : Forbid                                                                       |                           |             |                          |                          |

IWP left open the question of whether a locked instruction and a store to a different location could be seen in different orders by two other processors. We introduced the n3 test above to cover this case [20]. The given final state was allowed by x86-CC, but is not allowed by x86-TSO (again without the LOCK having anything to do with the reasoning). We have not observed the final state to occur in practice.

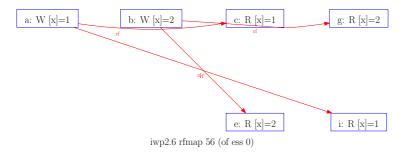

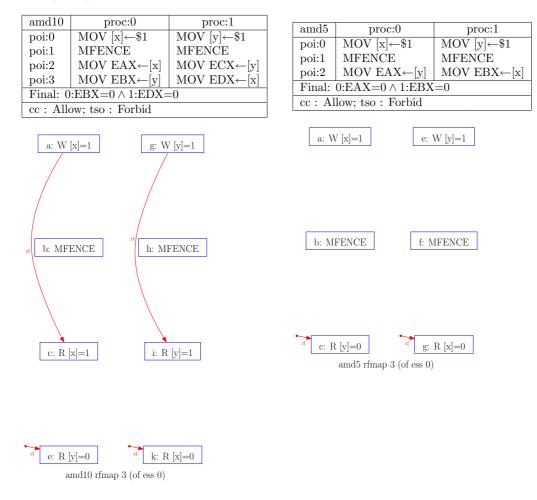

### A.4 Fence Instructions: Tests amd5 and amd10

We handle fences by forcing write-to-read program order dependencies into the memory order. The following amd10 example is very similar to iwp2.8.a, and the forbidden behavior is prohibited by x86-TSO by essentially the same mechanism. Test amd5 below is similar. Our interpretation seems consistent with rev-29 principles P11 and P12.

### A.5 The Unsoundness of IWP/AMD3.14/x86-CC: Test n6

The n6 test below, by Loewenstein, was discussed in §2.2, where we explained how the final state is allowed by write-buffer implementations.

| n6                                         | proc:0                     | proc:1                   |  |  |

|--------------------------------------------|----------------------------|--------------------------|--|--|

| poi:0                                      | MOV [x]←\$1                | MOV $[y] \leftarrow \$2$ |  |  |

| poi:1                                      | MOV EAX $\leftarrow$ [x]   | MOV $[x] \leftarrow \$2$ |  |  |

| poi:2                                      | $MOV \ EBX \leftarrow [y]$ |                          |  |  |

| Final: $0:EAX=1 \land 0:EBX=0 \land [x]=1$ |                            |                          |  |  |

| cc : Forbid; tso : Allow                   |                            |                          |  |  |

The final state is also allowed in x86-TSO, as shown in the execution below.

n6 vos 0 (of productive ess 7) showing Allow

The final state is allowed (as far as we can interpret the principles) in rev-29. The final state is observable on Intel processors: we find witnesses on an Intel Core 2, with our litmus tool. However, the given final state is forbidden in our x86-CC model, and by any interpretation we can make of the IWP or AMD3.14 principles. We have:

- (a, b) in preserved\_program\_order (by IWP P4)

- (b, d) in preserved\_program\_order (by IWP P1)

- (d, f) in the view order of proc:0 (otherwise d could not read value 0)

- (f,g) in preserved\_program\_order (by IWP P2)

- So the view order of proc:0 must be a, b, d, f, g.

- So (a, g) in the write serialization for location x (by IWP P6)

- So the final state must have [x] = 2, not [x] = 1.

#### A.6 The Weakness of Rev-29: Tests n4 and n5

As discussed in §2.3, the following examples were not allowed in x86-CC, nor are they allowed by x86-TSO. We would be surprised if they were allowed by any reasonable implementation, and have not observed them on Intel processors. Programming above a model that permitted them would be problematic. However, the rev-29 principles seem to allow them. In particular, P9 has no force because

it only involves processors other than those performing the two stores.

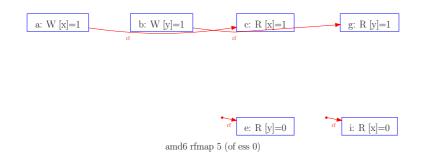

### A.7 Interpreting the rev-29 "not reordered with": Test n7

Key phrases in the vendor documentation (Intel IWP, AMD64-3.14, and Intel SDM rev-29) are not given definite meanings, making it hard use them to justify x86-TSO. Principles P1, P2, P3, P4, and P8 of rev-29 (reproduced in Appendix B) all refer to some events being "not reordered with" others. These principles were also present in IWP/AMD64-3.14, and in x86-CC we interpreted them as giving rise to a preserved-program-order relation, which was included in a transitive happens-before relation, with which each processor's view order had to be consistent. In a TSO-based model, however, one might expect to interpret two events being "not reordered" by requiring that any program order relation between them must also appear in the transitive memory order (as suggested by P5). This seems reasonable, and is what we do, for P1, P2, P3, and P8. However, P4 states READS MAY BE REORDERED WITH OLDER WRITES TO DIFFERENT LOCATIONS BUT NOT WITH OLDER WRITES TO THE SAME LOCATION. There is no problem with the first part, but for the second part, that interpretation would forbid the final state of litmus test n7 below (discussed in §3.2), whereas it is allowed on x86-TSO.

| n7                                                         | proc:0                   | proc:1      | proc:2                   |  |

|------------------------------------------------------------|--------------------------|-------------|--------------------------|--|

| poi:0                                                      | MOV [x]←\$1              | MOV [y]←\$1 | MOV ECX $\leftarrow$ [y] |  |

| poi:1                                                      | MOV EAX $\leftarrow$ [x] |             | MOV EDX $\leftarrow$ [x] |  |

| poi:2                                                      | MOV EBX $\leftarrow$ [y] |             |                          |  |

| Allow: $0:EAX=1 \land 0:EBX=0 \land 2:ECX=1 \land 2:EDX=0$ |                          |             |                          |  |

We illustrate this for the example x86-TSO valid execution below. If the second part of P4 were interpreted to give rise to preserved program order edges appearing in memory order, then there would be a memory order edge from a to b. Read d would then have to read from f, not from the initial state.

There are other valid executions, but not with the given final state.

### A.8 Other Tests

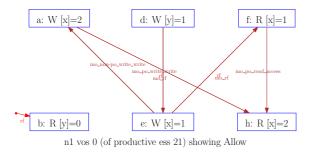

#### Test n1: Reordering of Loads with Older Stores to Different Locations

| n1     | proc:0                                       | proc:1      | proc:2                   |  |  |

|--------|----------------------------------------------|-------------|--------------------------|--|--|

| poi:0  | MOV [x]←\$2                                  | MOV [y]←\$1 | MOV EBX $\leftarrow$ [x] |  |  |

| poi:1  | MOV EAX $\leftarrow$ [y]                     | MOV [x]←\$1 | $MOV ECX \leftarrow [x]$ |  |  |

| Allow: | Allow: $0:EAX=0 \land 2:EBX=1 \land 2:ECX=2$ |             |                          |  |  |

In x86-CC, the allowed final result of iwp2.3.a/amd4 did not require the reordering of loads with older stores to different locations that the test description spoke of. We introduced Test n1 [20] as an example where such reordering was (in x86-CC) essential. The final behaviour is still allowed in x86-TSO, as shown below.

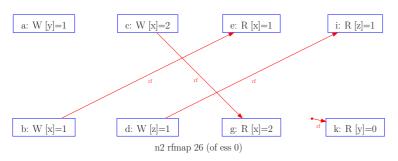

Test n2: Transitive Causality via Preserved Program Order and the Write Serialisation

| n2     | proc:0                                                          | proc:1                   | proc:2                   | proc:3                   |  |  |

|--------|-----------------------------------------------------------------|--------------------------|--------------------------|--------------------------|--|--|

|        |                                                                 |                          | MOV EAX $\leftarrow$ [x] |                          |  |  |