## BOSTON UNIVERSITY

## GRADUATE SCHOOL OF ARTS AND SCIENCES

Dissertation

# TERRIER: AN EMBEDDED OPERATING SYSTEM USING ADVANCED TYPES FOR SAFETY

by

### MATTHEW DANISH

B.S., Carnegie-Mellon University, 2004

Submitted in partial fulfillment of the

requirements for the degree of

Doctor of Philosophy

2015

© 2015 by MATTHEW DANISH All rights reserved

## Approved by

First Reader

Hongwei Xi, Ph.D. Associate Professor of Computer Science

Second Reader

Richard West, Ph.D. Associate Professor of Computer Science

Third Reader

Chris Hawblitzel, Ph.D. Research Scientist

### Acknowledgments

My parents Bonnie and Keith Danish for everything; my primary advisor Hongwei Xi for his infinite patience with my questions; my frequent collaborator Richard West for supporting my foray into systems; my fellow students Likai Liu, Zhiqiang Ren, Ye Li and Mikhail Breslav; and the many other students, staff and faculty at Boston University who have helped me along in countless ways over the years. Without their support, none of this is possible.

# TERRIER: AN EMBEDDED OPERATING SYSTEM USING ADVANCED TYPES FOR SAFETY

### MATTHEW DANISH

Boston University, Graduate School of Arts and Sciences, 2015

Major Professor: Hongwei Xi, Ph.D. Associate Professor of Computer Science

#### ABSTRACT

Operating systems software is fundamental to modern computer systems: all other applications are dependent upon the correct and timely provision of basic system services. At the same time, advances in programming languages and type theory have lead to the creation of functional programming languages with type systems that are designed to combine theorem proving with practical systems programming. The Terrier operating system project focuses on low-level systems programming in the context of a multi-core, real-time, embedded system, while taking advantage of a dependently typed programming language named ATS to improve reliability. Terrier is a new point in the design space for an operating system, one that leans heavily on an associated programming language, ATS, to provide safety that has traditionally been in the scope of hardware protection and kernel privilege. Terrier tries to have far fewer abstractions between program and hardware. The purpose of Terrier is to put programs as much in contact with the real hardware, real memory, and real timing constraints as possible, while still retaining the ability to multiplex programs and provide for a reasonable level of safety through static analysis.

## Contents

| 1 | Intr | roduct | ion                                         | 1  |

|---|------|--------|---------------------------------------------|----|

|   | 1.1  | Opera  | ting system design                          | 3  |

|   |      | 1.1.1  | Programming languages and operating systems | 4  |

|   | 1.2  | Motiv  | ation and structure                         | 5  |

|   |      | 1.2.1  | Processes, programs and tasks               | 8  |

|   |      | 1.2.2  | Asynchronicity and interrupts               | 9  |

|   |      | 1.2.3  | Explicit memory mapping                     | 11 |

|   |      | 1.2.4  | Programming language-based safety           | 13 |

|   |      | 1.2.5  | Scheduling                                  | 16 |

|   | 1.3  | Relate | ed work                                     | 16 |

|   |      | 1.3.1  | Program verification                        | 17 |

|   |      | 1.3.2  | Operating system verification               | 18 |

|   |      | 1.3.3  | Asynchronous communication mechanisms       | 20 |

|   |      | 1.3.4  | Related designs                             | 22 |

|   | 1.4  | Contr  | ibutions                                    | 24 |

|   | 1.5  | A cras | sh course in the ATS programming language   | 25 |

|   |      | 1.5.1  | From types to dependent types               | 25 |

|   |      | 1.5.2  | Call-by-reference                           | 28 |

|   |      | 1.5.3  | Protecting resources with linear types      | 29 |

|   |      | 1.5.4  | Linear and dependent types                  | 31 |

|   |      | 1.5.5  | Linear types that evolve                    | 32 |

|   |      | 1.5.6  | Flat types                                  | 34 |

|   |      | 1.5.7  | Templates                                   | 36 |

|   |      | 1.5.8  | ATS program structure                       | 37 |

| <b>2</b> | The  | Terrie | er Operating System                    | 39 |

|----------|------|--------|----------------------------------------|----|

|          | 2.1  | Platfo | rm support                             | 39 |

|          | 2.2  | The b  | oot process                            | 40 |

|          |      | 2.2.1  | Start-up                               | 40 |

|          |      | 2.2.2  | Early initialization                   | 40 |

|          |      | 2.2.3  | Physical and virtual memory            | 41 |

|          |      | 2.2.4  | Multiprocessor support                 | 41 |

|          | 2.3  | Hardw  | vare support                           | 43 |

|          |      | 2.3.1  | Memory                                 | 43 |

|          |      | 2.3.2  | Timers                                 | 46 |

|          |      | 2.3.3  | Serial port                            | 47 |

|          |      | 2.3.4  | USB                                    | 48 |

|          | 2.4  | Sched  | uling                                  | 49 |

|          |      | 2.4.1  | The process model                      | 49 |

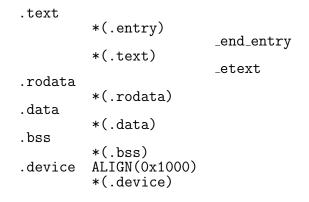

|          |      | 2.4.2  | Program file format                    | 53 |

|          |      | 2.4.3  | Scheduling parameters                  | 54 |

|          |      | 2.4.4  | Mappings                               | 55 |

|          |      | 2.4.5  | Interprocess communication mappings    | 56 |

|          |      | 2.4.6  | Rate-monotonic scheduling (RMS)        | 57 |

|          |      | 2.4.7  | Interrupt handling                     | 60 |

| 3        | Inte | rproce | ess Communication Mechanisms           | 61 |

|          | 3.1  | Introd | uction                                 | 61 |

|          | 3.2  | Interp | rocess communication memory interface  | 61 |

|          | 3.3  | Async  | hronous communication mechanisms       | 62 |

|          | 3.4  | The fo | our-slot mechanism and generalizations | 63 |

|          |      | 3.4.1  | Introduction                           | 63 |

|          |      | 3.4.2  | Definitions                            | 64 |

|          |      |        |                                        |    |

| 3.4.3   | Single-reader mechanism definitions                                                                                                                                                                           | 65                                                                                                                                                                                                                                                                                   |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.4.4   | Single-reader proofs                                                                                                                                                                                          | 65                                                                                                                                                                                                                                                                                   |

| 3.4.5   | Single-reader (expanded)                                                                                                                                                                                      | 69                                                                                                                                                                                                                                                                                   |

| 3.4.6   | Expanded pseudocode                                                                                                                                                                                           | 69                                                                                                                                                                                                                                                                                   |

| 3.4.7   | Linearization points                                                                                                                                                                                          | 69                                                                                                                                                                                                                                                                                   |

| 3.4.8   | Diagrams                                                                                                                                                                                                      | 70                                                                                                                                                                                                                                                                                   |

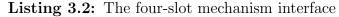

| 3.4.9   | The four-slot mechanism interface                                                                                                                                                                             | 70                                                                                                                                                                                                                                                                                   |

| The m   | nulti-reader mechanism                                                                                                                                                                                        | 70                                                                                                                                                                                                                                                                                   |

| 3.5.1   | Definitions                                                                                                                                                                                                   | 74                                                                                                                                                                                                                                                                                   |

| 3.5.2   | Pseudocode                                                                                                                                                                                                    | 74                                                                                                                                                                                                                                                                                   |

| 3.5.3   | Proofs                                                                                                                                                                                                        | 75                                                                                                                                                                                                                                                                                   |

| 3.5.4   | The multi-reader mechanism interface                                                                                                                                                                          | 78                                                                                                                                                                                                                                                                                   |

| 3.5.5   | Conclusion                                                                                                                                                                                                    | 79                                                                                                                                                                                                                                                                                   |

| The fit | xed-slot mechanism                                                                                                                                                                                            | 79                                                                                                                                                                                                                                                                                   |

| 3.6.1   | High level functional description and example                                                                                                                                                                 | 81                                                                                                                                                                                                                                                                                   |

| 3.6.2   | Pseudo-code                                                                                                                                                                                                   | 83                                                                                                                                                                                                                                                                                   |

| 3.6.3   | Details of implementation                                                                                                                                                                                     | 84                                                                                                                                                                                                                                                                                   |

| 3.6.4   | The fixed-slot mechanism interface                                                                                                                                                                            | 89                                                                                                                                                                                                                                                                                   |

| 3.6.5   | Performance                                                                                                                                                                                                   | 92                                                                                                                                                                                                                                                                                   |

| mory I  | Protection using Types                                                                                                                                                                                        | 97                                                                                                                                                                                                                                                                                   |

| The U   | USB interface                                                                                                                                                                                                 | 97                                                                                                                                                                                                                                                                                   |

| 4.1.1   | An example use of the interface                                                                                                                                                                               | 97                                                                                                                                                                                                                                                                                   |

| 4.1.2   | The provided library interface                                                                                                                                                                                | 101                                                                                                                                                                                                                                                                                  |

| 4.1.3   | Performance                                                                                                                                                                                                   | 111                                                                                                                                                                                                                                                                                  |

| Physic  |                                                                                                                                                                                                               | 118                                                                                                                                                                                                                                                                                  |

|         | 3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8<br>3.4.9<br>The n<br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4<br>3.5.5<br>The fi<br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4<br>3.6.5<br>mory I<br>The U<br>4.1.1<br>4.1.2<br>4.1.3 | 3.4.4       Single-reader proofs         3.4.5       Single-reader (expanded)         3.4.6       Expanded pseudocode         3.4.7       Linearization points         3.4.8       Diagrams         3.4.9       The four-slot mechanism interface         The multi-reader mechanism |

$\mathbf{4}$

| <b>5</b> | Deb | bugging with Types and Logic                                           | 122 |

|----------|-----|------------------------------------------------------------------------|-----|

|          | 5.1 | The fixed-slot mechanism                                               | 122 |

|          |     | 5.1.1 Static types for the fixed-slot mechanism                        | 123 |

|          | 5.2 | Case study: Model-checking a complex entry handler $\ . \ . \ . \ .$ . | 131 |

|          | 5.3 | Case study: Invasive changes to a device driver                        | 138 |

|          |     |                                                                        |     |

| 6        | Con | clusion                                                                | 144 |

| 6        |     | clusion<br>Critiques                                                   |     |

| 6        |     |                                                                        | 144 |

|          | 6.1 | Critiques                                                              | 144 |

## List of Tables

| 1.1 | ATS terminology                                                                  | 14  |

|-----|----------------------------------------------------------------------------------|-----|

| 2.1 | Terrier executable program memory layout                                         | 54  |

| 2.2 | Symbols that Terrier interprets specially                                        | 54  |

| 3.1 | Legend for Figure 3.13                                                           | 82  |

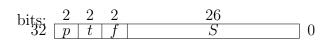

| 3.2 | The bit layout of the 32-bit word                                                | 87  |

| 3.3 | Average cycle counts to run step $R1$ under various scheduling scenarios         | 93  |

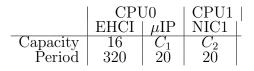

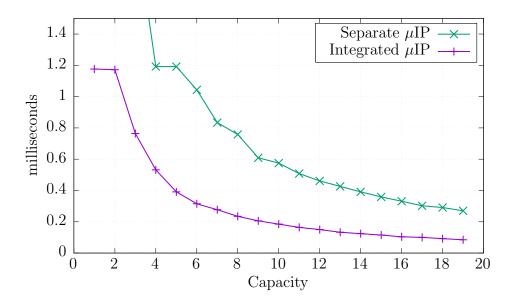

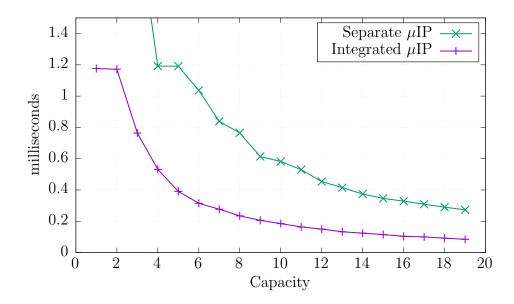

| 3.4 | Basic scheduling setup for the experiments                                       | 94  |

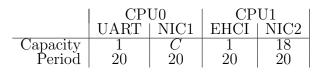

| 4.1 | Basic scheduling setup for the experiments                                       | 112 |

| 5.1 | Meanings ascribed to registers in the ehci entry handler                         | 132 |

| 5.2 | The InitEntry stage                                                              | 133 |

| 5.3 | Check to see if we are returning from IRQ-handling mode                          | 133 |

| 5.4 | Check the IRQ status table                                                       | 134 |

| 5.5 | Switch between the Save, LoadIRQ, or ContextSwitch stages $\ldots \ldots \ldots$ | 134 |

| 5.6 | The Save stage                                                                   | 135 |

| 5.7 | The LoadIRQ stage $\ldots$ $\ldots$                                              | 135 |

| 5.8 | The RestoreSaved stage $\ldots$                                                  | 136 |

| 5.9 | The ContextSwitch stage                                                          | 136 |

## List of Figures

| 1.1  | Goals of operating system designs                                                | 4  |

|------|----------------------------------------------------------------------------------|----|

| 1.2  | Entry handler and interrupts                                                     | 10 |

| 1.3  | Example of interprocess communication                                            | 12 |

| 1.4  | Hardware memory protection independence                                          | 13 |

| 1.5  | Views and types in ATS syntax                                                    | 14 |

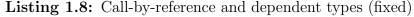

| 1.6  | Type indices link proof and program                                              | 32 |

| 1.7  | Boxed and unboxed values                                                         | 35 |

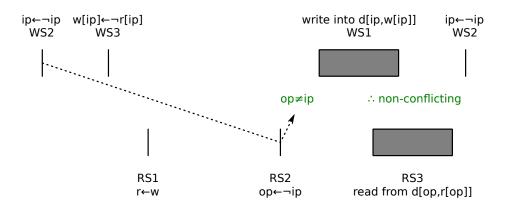

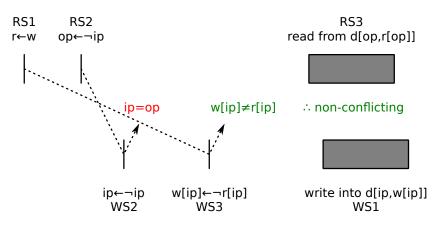

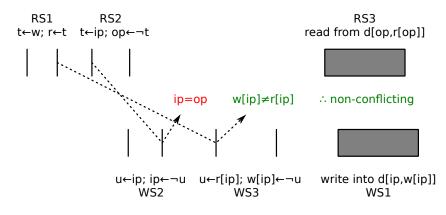

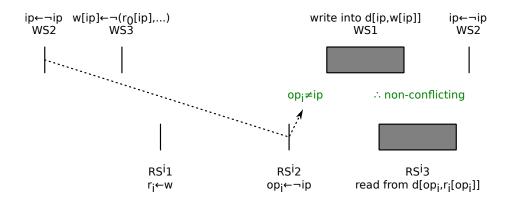

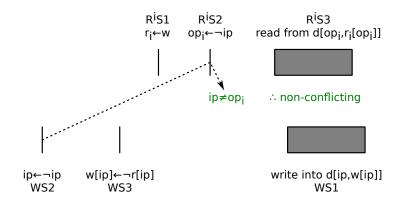

| 3.1  | $W3$ does not occur between $R1$ and completion of $R3$ $\hdots$                 | 66 |

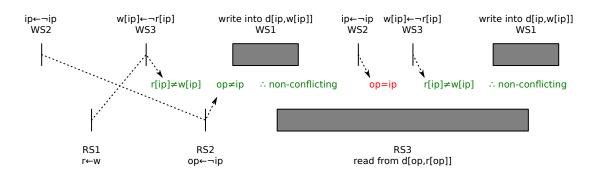

| 3.2  | $W3$ occurs at least once between $R1$ and completion of $R3$ $\ .$              | 66 |

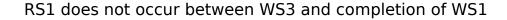

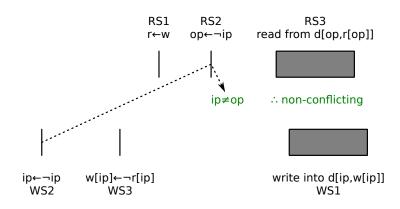

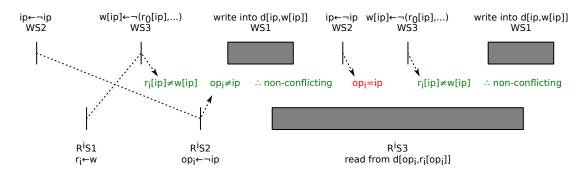

| 3.3  | R1 does not occur between $W3$ and completion of $W1$                            | 67 |

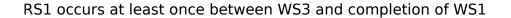

| 3.4  | R1 occurs at least once between $W3$ and completion of $W1,$ as well as          |    |

|      | a case where $op = ip$                                                           | 68 |

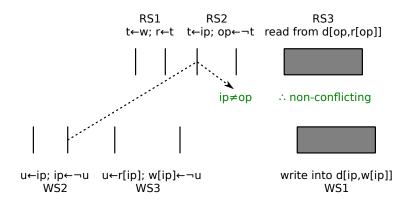

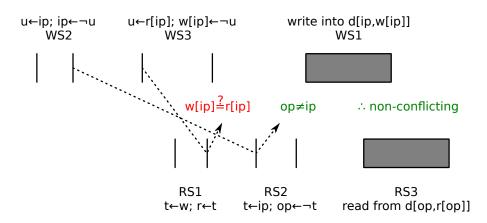

| 3.5  | R1 occurs at least once between $W3$ and completion of $W1,$ as well as          |    |

|      | a case where $op = ip$                                                           | 71 |

| 3.6  | R1 does not occur between $W3$ and completion of $W1$                            | 71 |

| 3.7  | $W3$ does not occur between $R1$ and completion of $R3$ $\hdots$                 | 72 |

| 3.8  | $W3$ occurs at least once between $R1$ and completion of $R3$ $\hdots$           | 72 |

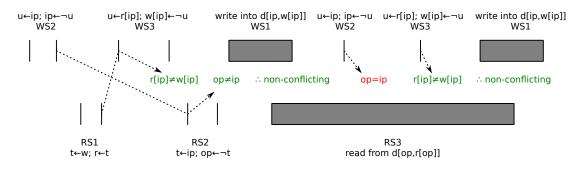

| 3.9  | W3 does not occur between $R^{i_1}$ and completion of $R^{i_3}$                  | 75 |

| 3.10 | W3 occurs at least once between $R^{i}1$ and completion of $R^{i}3$ , as well as |    |

|      | a case where $ip = op_i$                                                         | 76 |

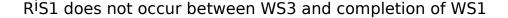

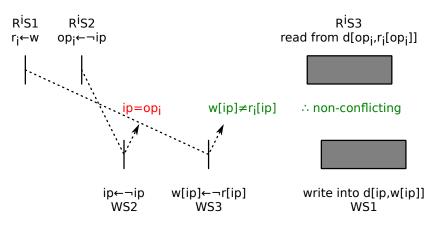

| 3.11 | $R^i 1$ does not occur between $W3$ and completion of $W1$                       | 77 |

| 3.12 | $R^i 1$ occurs at least once between $W3$ and completion of $W1,$ as well as     |    |

|      | a case where $op_i = ip$                                                         | 78 |

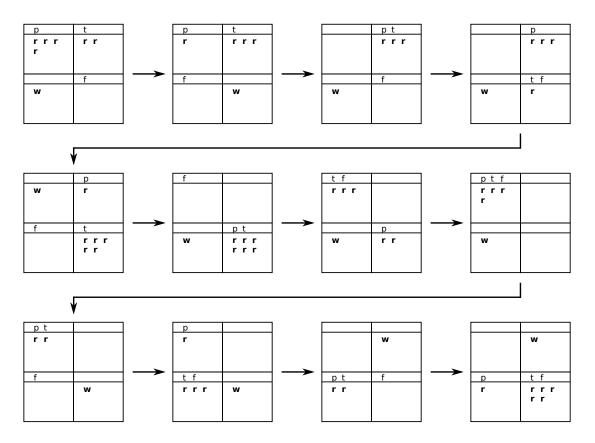

| 3.13                                                                        | Example sequence of steps for a fixed-slot mechanism with four slots                                                                                                                                                                                                                                                                                                                         |                                                                             |

|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

|                                                                             | and six readers                                                                                                                                                                                                                                                                                                                                                                              | 83                                                                          |

| 3.14                                                                        | The shared variable state                                                                                                                                                                                                                                                                                                                                                                    | 84                                                                          |

| 3.15                                                                        | Fixed-slot mechanism pseudo-code: writer                                                                                                                                                                                                                                                                                                                                                     | 84                                                                          |

| 3.16                                                                        | Fixed-slot mechanism pseudo-code: reader                                                                                                                                                                                                                                                                                                                                                     | 85                                                                          |

| 3.17                                                                        | Atomic increment using LDREX/STREX                                                                                                                                                                                                                                                                                                                                                           | 86                                                                          |

| 3.18                                                                        | Assembly pseudo-code for atomic operation $R1$                                                                                                                                                                                                                                                                                                                                               | 88                                                                          |

| 3.19                                                                        | Assembly pseudo-code for atomic operation $R6$                                                                                                                                                                                                                                                                                                                                               | 88                                                                          |

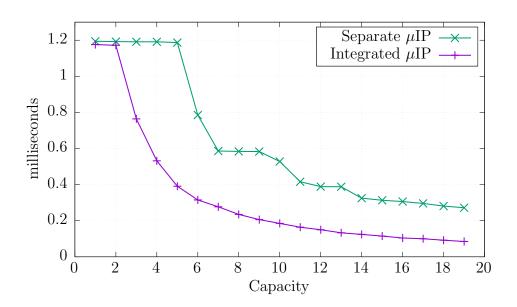

| 3.20                                                                        | Experiment with separate $\mu$ IP process of varying capacity $\ldots$ .                                                                                                                                                                                                                                                                                                                     | 94                                                                          |

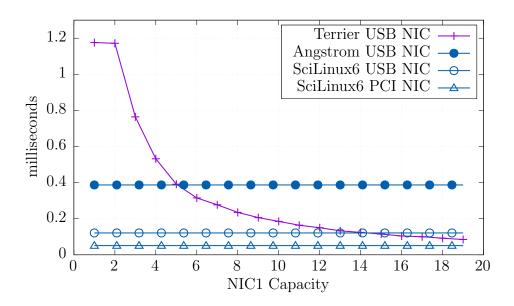

| 3.21                                                                        | Experiment varying capacity of NIC1 with separate $\mu \mathrm{IP}$ process $\ . \ .$                                                                                                                                                                                                                                                                                                        | 95                                                                          |

| 3.22                                                                        | Experiment varying capacity of both NIC1 and separate $\mu \mathrm{IP}$ process                                                                                                                                                                                                                                                                                                              | 95                                                                          |

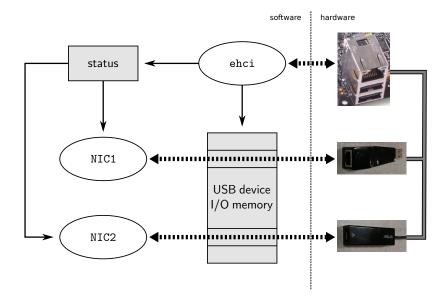

| 4.1                                                                         | The relationships between modules and hardware                                                                                                                                                                                                                                                                                                                                               | 113                                                                         |

|                                                                             |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                             |

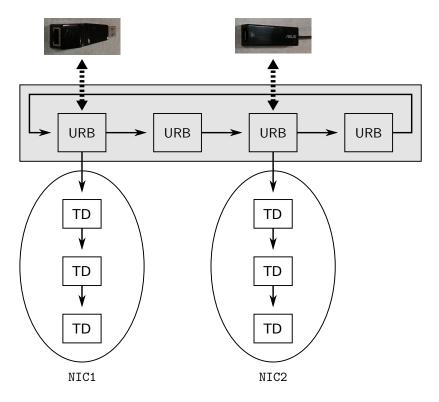

| 4.2                                                                         | URB linked list example                                                                                                                                                                                                                                                                                                                                                                      | 113                                                                         |

| 4.2<br>4.3                                                                  | URB linked list example                                                                                                                                                                                                                                                                                                                                                                      | 113<br>114                                                                  |

|                                                                             | -                                                                                                                                                                                                                                                                                                                                                                                            |                                                                             |

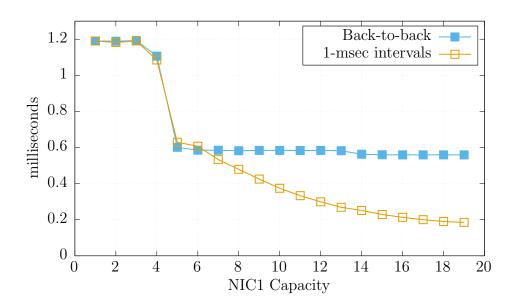

| 4.3                                                                         | Effect of NIC1 capacity on ping roundtrip time using Ethernet switch                                                                                                                                                                                                                                                                                                                         | 114                                                                         |

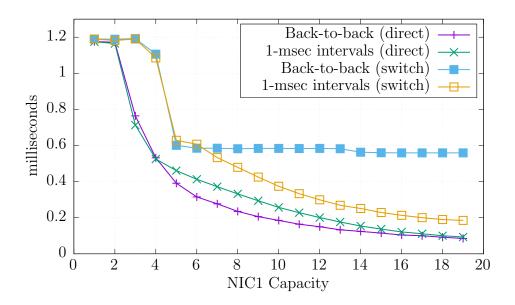

| 4.3<br>4.4                                                                  | Effect of NIC1 capacity on ping roundtrip time using Ethernet switch<br>Effect from type of network connection on ping roundtrip time                                                                                                                                                                                                                                                        | 114<br>115                                                                  |

| <ul><li>4.3</li><li>4.4</li><li>4.5</li></ul>                               | Effect of NIC1 capacity on ping roundtrip time using Ethernet switch<br>Effect from type of network connection on ping roundtrip time<br>Comparison of ping roundtrip time to various Linux scenarios                                                                                                                                                                                        | 114<br>115<br>116                                                           |

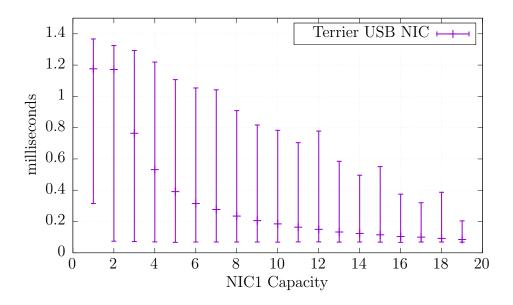

| <ol> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> </ol>              | Effect of NIC1 capacity on ping roundtrip time using Ethernet switch<br>Effect from type of network connection on ping roundtrip time<br>Comparison of ping roundtrip time to various Linux scenarios<br>Distribution of ping response times (min/avg/max)                                                                                                                                   | 114<br>115<br>116                                                           |

| <ol> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> </ol>              | Effect of NIC1 capacity on ping roundtrip time using Ethernet switch<br>Effect from type of network connection on ping roundtrip time<br>Comparison of ping roundtrip time to various Linux scenarios<br>Distribution of ping response times (min/avg/max) Distribution of ping response times in experiment that varies period of                                                           | <ol> <li>114</li> <li>115</li> <li>116</li> <li>117</li> </ol>              |

| <ol> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> </ol> | Effect of NIC1 capacity on ping roundtrip time using Ethernet switch<br>Effect from type of network connection on ping roundtrip time<br>Comparison of ping roundtrip time to various Linux scenarios<br>Distribution of ping response times (min/avg/max)<br>Distribution of ping response times in experiment that varies period of<br>NIC1 while maintaining 90% utilization for capacity | <ol> <li>114</li> <li>115</li> <li>116</li> <li>117</li> <li>118</li> </ol> |

## xii

## List of Abbreviations

| ACM      | <br>Asynchronous Communication Mechanism    |  |  |

|----------|---------------------------------------------|--|--|

| ARM      | <br>Acorn RISC Machine                      |  |  |

| ATS      | <br>Applied Type System                     |  |  |

| CPU      | <br>Central Processing Unit                 |  |  |

| CSP#     | <br>Communicating Sequential Programs–Sharp |  |  |

| EHCI     | <br>Enhanced Host Controller Interface      |  |  |

| GHC      | <br>Glasgow Haskell Compiler                |  |  |

| ICMP     | <br>Internet Control Message Protocol       |  |  |

| I/O      | <br>Input/Output                            |  |  |

| IP       | <br>Internet Protocol                       |  |  |

| IRQ      | <br>Interrupt Request                       |  |  |

| $\mu IP$ | <br>Micro IP                                |  |  |

| PAT      | <br>Process Analysis Toolkit                |  |  |

| PCI      | <br>Peripheral Component Interconnect       |  |  |

| NIC      | <br>Network Interface Card                  |  |  |

| QH       | <br>Queue Head                              |  |  |

| RISC     | <br>Reduced Instruction Set Computing       |  |  |

| RMS      | <br>Rate Monotonic Scheduling               |  |  |

| TCP      | <br>Transmission Control Protocol           |  |  |

| TD       | <br>Transfer Descriptor                     |  |  |

| URB      | <br>USB Request Block                       |  |  |

| USB      | <br>Universal Serial Bus                    |  |  |

### Chapter 1

### Introduction

Recent years have seen a proliferation of small, embedded, electronic devices controlled by computer processors as powerful as the ARM<sup>®</sup>. These devices are now responsible for tasks as varied as flying a plane, talking on a cellphone, or helping to perform surgery. Some of these tasks have severe consequences for a mistake caused by faulty programming or missed deadlines. The best defense against these mistakes is to prevent them from happening in the first place.

The operating systems software is fundamental to modern computer systems, such as these embedded devices: all other applications are dependent upon the correct and timely provision of basic system services. Ideally, the operating system is written with maximum attention to detail and the use of optimal algorithms. In practice, many difficult decisions must be made during the design and implementation of a realistic system.

There are many aspects of operating system development that contribute to this situation: the low-level behavior of hardware can be finicky, the asynchronous combination of system processes may produce unforeseen results, many of the resource-management problems are intractable to solve optimally, the slightest mistake can have profound consequences, and there is little room for any wasteful overhead. To maximize performance and ease of hardware interaction, most operating systems software is written in type-unsafe, low-level memory model programming languages like C or C++. But, this often leads to compromised reliability and safety because of programmer error.

At the same time, advances in programming languages and type theory have lead to the creation of functional programming languages with type systems that are designed to combine theorem proving with practical systems programming. This allows programmers to bring the rigor of mathematical verification to important properties of their processes. I argue that the usage of these kinds of languages, in operating system development, can lead to better assurance that the processes running on an embedded device are correct, responsive, and safe.

The Terrier operating system project focuses on low-level systems programming in the context of a real-time embedded system, while taking advantage of a dependently typed programming language named ATS (Xi, 2004) to improve reliability. The purpose of this project is to identify effective, practical means to create safer, more reliable systems through use of advanced type system features in programming languages. I am also interested in the implications of having expressive programming language tools available, and the effects on plausible system design. For example, the Terrier OS moves much of the responsibility for program safety back out onto the programs themselves, rather than relying strictly on run-time checks or hardware protection mechanisms. For another, the Terrier program model is one in which asynchronous events play a central role in program design. These two shifts in thinking put more burden on the programmer—a burden that will be lightened through language-level assistance—but they also open up more flexibility in potential program design that will enable higher performance, better responsiveness and more naturally-written code in difficult problem domains.

ATS is a programming language with the goal of bringing together formal specification and practical programming. The core of ATS is an ML-like functional programming language that is compiled into C. The type system of ATS combines dependent and linear types to permit sophisticated reasoning about program behavior and the safety of resource usage. The design of ATS provides close coupling of type-safe functional code and low-level C code, allowing the programmer to decide the balance between specification and speed. The ATS compiler can generate code that does not require garbage collection nor any other special run-time support, making it suitable for bare metal programming.

Using ATS, I have generated C code that links into my kernel to provide several critical components. I also encourage the use of ATS to help ensure the safety and correctness of programs that run under the OS. For example, programs that wish to communicate with one another are provided with libraries written in ATS that implement protocols that have been statically checked for safety and correctness. Most of these protocols fall into the category of asynchronous communication mechanisms, which ties into the central role that asynchronous event handling plays in the Terrier OS.

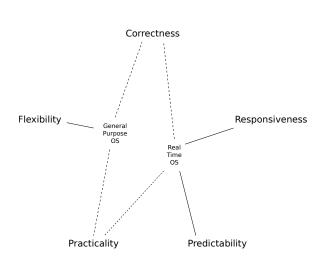

### 1.1 Operating system design

There are several competing goals of operating system design. For example, general purpose operating systems like Linux (Torvalds et al., 2014) might strive for maximum flexibility and practicality. Those systems are used by a wide diversity of people with many different applications. Figure 1.1 compares the goals of a general purpose operating system with those of a real-time operating system. In the latter case, responsiveness and predictability may be held as the most important properties of all.

But in doing so, the real-time operating system becomes less flexible, because it makes extraordinary demands of programs. It may ask for "Worst Case Execution Time" (Wilhelm et al., 2008) profiles, strict static scheduling parameters (Liu and Layland, 1973), priority ceiling protocol cooperation (Sha et al., 1990), or other kinds of information that require extensive analysis. A real-time system is not necessarily a high-performance system either. Some techniques used for high-performance, such as caching, are inherently difficult to predict (Basumallick and Nilsen, 1994) and therefore may be eschewed.

4

Figure 1.1: Goals of operating system designs

Either type of operating system might try to incorporate correctness guarantees in some form. Depending on how strong the assurances are, the amount of effort required could easily skyrocket. Or it could detract from other goals, such as flexibility, for instance, by making it more difficult to support diverse applications or hardware. It could hurt performance, practicality and responsiveness by requiring the use of run-time checks in certain cases. Compromise is necessary to balance these goals.

#### 1.1.1 Programming languages and operating systems

In the same way, compromise is required in the design of programming languages and type systems. Also, many operating systems are intertwined with a particular programming language. In no particular order:

- Unix: C (Ritchie and Thompson, 1974)

- SPIN: Modula-3 (Bershad et al., 1995)

- Singularity: Sing# (Hunt and Larus, 2007)

- seL4: Isabelle, Haskell and C (Klein et al., 2009)

- House: Haskell (Hallgren et al., 2005)

It is sometimes said that types are "partial specifications" for programs. That means that the correctness guarantees of an operating system can be linked to the capability of the type system of the programming language in which it is written.

Some systems use a more powerful type system than others. For example, House is written in Haskell, a reasonably powerful programming language and type system, but it is supported by lifting the run-time environment straight from GHC (Peyton-Jones et al., 2014) and grafting it onto a bare-metal support framework. This means House must defer interrupt handling until known safe points in order to avoid breaking the garbage collector. Another popular system is Unix and C, which has a weak type system, but is popular with performance-oriented programmers.

The system that is being introduced in this text, Terrier, is intended to be a practical, incremental approach to leveraging advanced types while retaining efficiency enough to make it usable for real-time applications.

### **1.2** Motivation and structure

The purpose of most operating systems is to multiplex the hardware, to allow it to be shared between multiple processes and possibly multiple users. The most customary approach to this task is for the kernel to build environments that are an abstraction of the real hardware.

For example, the physical memory address space of most architectures is limited by real constraints, and is often strewn with many kinds of exceptional uses and alternate meanings. On the typical ARM-based architecture, general-purpose memory is restricted to certain ranges of physical addresses, while much of the rest is used for memory-mapped device communication. However, the details of physical addressing are almost always irrelevant to application developers, who just need a place to store their processes and data. So, typically, an operating system devotes significant effort to the construction of the "virtual memory" abstraction: it is the illusion of flat, nearly unlimited, unrestricted and unconflicted memory address space that is provided to each process separately. The traditional operating system uses memory management hardware to give every process its own private address space, which is both a (virtual) resource, and a protection against unauthorized access into other processes' data.

Another way that operating systems abstract a real resource is through scheduling: the CPU can essentially only be working on a single process at a time, but there are many processes that want to make forward progress. Even in computers with multiple CPUs available, there are usually more processes than available processors. The standard way to deal with this problem is to time-share the CPU: each process in turn gets a chance to run, and then when that time-slice elapses, it is put to sleep and the next process is woken up. The exact details of which process is selected and for how long it runs is up to the specifics of the scheduling algorithm. But the common characteristic is that the CPU is rapidly switching between processes and that processes spend significant amounts of real time not running. However, that is not the abstraction that is provided to the application programmer. The traditional kernel is engineered to provide the illusion of continuous process execution that is uninterrupted unless explicitly requested by the application programmer.

There are other abstractions as well: filesystems that organize raw disk sectors into virtual resources such as files and directories, network stacks that multiplex the frame transceiving capabilities of network cards and do high-level routing of data, and a menagerie of other device drivers that make the computer usable in practice. Many of these abstractions are created to help multiplex but also to help protect processes from each other.

A great deal of the work done by the traditional operating system is to create the illusion of nearly limitless space and time for each process to enjoy separately. When application programmers do not care about real time, or real memory constraints, then this approach makes sense. But does it still make sense for real-time applications? Does it make sense to go through the trouble of creating these abstractions and then breaking them for the sake of processes that must have a firm relation to real resources? Does it make sense to put up hardware barriers between two processes when the failure of one means the failure of the other, anyway?

Consider the case of a watchdog process running on an embedded system that is helping to fly an aircraft. It runs at precise periodic intervals to check on the status of the control systems. The programmers of this kind of embedded system have extensively studied the exact behavior of their hardware, have analyzed the worstcase execution time of their various pieces of software, and have spent a tremendous amount of effort to flush out all possible errors before deployment. There is no need for an abstraction of limitless time and space in any of the processes that are running in this system. Instead, what is needed is close tracking of real time, fast communication, minimal overhead, and rapid detection of hardware failures.

The watchdog process is, by nature, not continuously executing, but instead it is event-driven. It interacts with all other processes in the system, but it does not want to impose overhead on them, or any synchronization delays. Correctness of the program is important, but hardware memory protection would interfere with its mission. In a traditional operating system, this kind of program would probably be implemented as a kernel-level process that can see through the various abstractions of the kernel. That is one example of the limitations of a traditional operating system's model. But watchdog processes are hardly the only kind of program that may benefit from a less abstracted application model.

The underlying realization behind Terrier is that there already exists a model for applications that is more natural to the hardware: it is the model on which the kernel itself is built, the one provided by the hardware. Multiplexing is still needed, but, it ought to be possible to provide for that while also exposing an interface to processes that most closely resembles the hardware. Thus, the philosophy behind the design for Terrier's program model:

- Asynchronicity and interrupts

- Explicit memory mapping

- Safety based on programming language features

and some of the derived features:

- Preemptive application-level scheduling

- Delegation of device control

- Flexible, asynchronous interprocess communication

- Ability to operate with or without hardware memory protection

#### 1.2.1 Processes, programs and tasks

This text will use the term "program" to refer to a high-level language file, as well as the idea of a set of machine instructions packaged together as a single unit, intended to be loaded and executed by the kernel. The term "program" can be used to either mean the abstract concept of a program, at a high-level, or the concrete manifestation of said concept: as a string of binary code stored in a file or loaded into memory. The term "process" is similar to program but is typically used in contexts where specific operation of the kernel and the machine is being discussed. Finally, when the term "task" is used to describe a program, it is in a more abstract sense of something that requires CPU time and needs to be scheduled.

A "program model" is the environment and functionality provided by the kernel within which a program must exist and be constructed. A "program point" can either refer to a specific machine instruction within the compiled program, or to location in the high-level language file that corresponds to a programmer's understanding of a specific point in the execution of the program. A "process context" is the state of the processor, including registers, at a given program point.

The kernel loads and manages a set of processes, scheduling them according to their static specifications, as described by Section 2.4.6. The following section goes into more detail about how processes may be interrupted by hardware events, and the way in which control is returned.

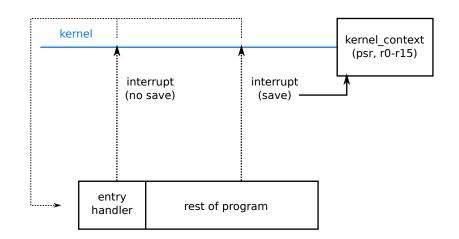

#### **1.2.2** Asynchronicity and interrupts

The Terrier program model allows for the unexpected, sudden transfer of control from the current program point to a designated entry point in the application code. All programs are expected to have program code that forms the *entry handler*, and it should be placed at the designated entry point. The purpose of this code is to handle asynchronous events and to make decisions about what actions to take next. Several common behaviors will be made available as pre-compiled static object files or libraries that may be linked into applications to provide entry handlers, but it will also be possible for an application programmer to custom-design one.

In order to allow rapid resumption of execution, upon interrupt, the kernel captures a snapshot of the interrupted process context (with one exception) and later makes it available to the entry handler. That context will take the form of an array containing the program status register and the sixteen registers of the ARM processor. Restoration of context can be done within a few assembly instructions on the ARM processor in this way.

The kernel will also make available a table of interrupt status bits that reflect the current state of the interrupt controller. This will enable entry handlers to quickly decide whether or not a particular interrupt is of interest.

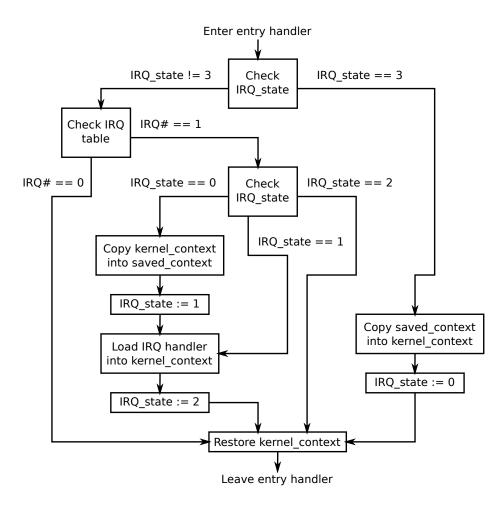

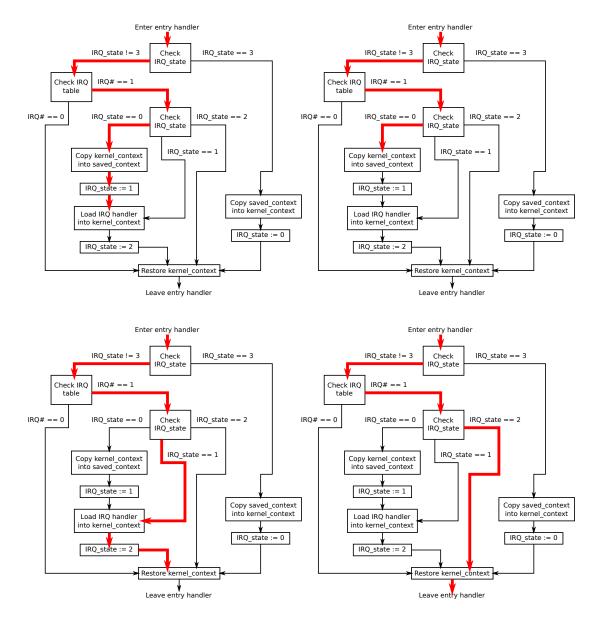

Figure 1.2: Entry handler and interrupts

#### **Reentrancy and restartability**

In order to avoid race conditions and make it possible for this mechanism to work without masking interrupts, the kernel reserves some special behavior for the entry handler. If a program is interrupted while the program counter is within the designated entry handler, as shown in figure 1.2, then the kernel will skip saving the interrupted process context, and will instead preserve the existing saved context. There are two main effects: one, the interruption of an entry handler does not destroy valuable program state before it can be examined, and two, the entry handler must be programmed to be entirely reentrant and restartable (Bershad et al., 1992) at any time. Entry handlers are further discussed in Chapter 2.4.1.

Although it is possible to program such an entry handler by hand, the use of verification techniques such as model-checking are well-suited for the task, and have been investigated, as discussed in Chapter 5.2.

#### Application control of scheduling

One of the consequences of the unusual entry handler design is that it allows a program to gain first-class access to its own contexts, or continuations, in a sense. Therefore, an entry handler can be designed that allows a choice between different process contexts, or even the creation of an abstraction such as "user-level threads" but with support for preemption at any point, unlike typical implementations. This allows an application to manage scheduling within itself if the programmer chooses to use it, for example, to create user-level scheduling hierarchies (Parmer and West, 2008).

#### 1.2.3 Explicit memory mapping

The ARM architecture makes hardware registers available through memory-mapped address space regions. Therefore, application programs will also be able to request explicit memory mappings from the kernel, along with desired attributes, in order to interact with hardware or provide interfaces. The current design has applications compiled with special sections that statically describe the necessary mappings, so that the kernel can analyze and decide which ones to fulfill and how. Dynamic mappings are also anticipated in the future.

#### Delegation of device control

Like a microkernel, most device support is expected to be fulfilled by application programs. Unlike a microkernel, these application programs are given very close control over the hardware. Using explicit memory mapping and access to the interrupt status table, device drivers may be written with minimal kernel interaction.

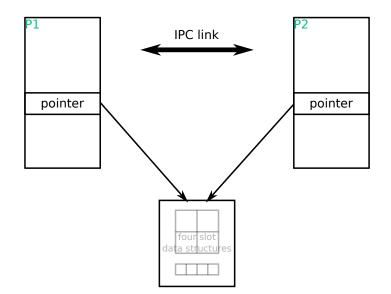

#### Interprocess communication

Communication between programs is mediated by shared memory and therefore falls under the explicit memory mapping regime. In the current design, applications that wish to communicate are expected to statically describe the name of the channel and the method of communication used. The kernel finds pairs of programs, then allocates the necessary physical memory, and creates virtual mappings if necessary, as shown in Figure 1.3. The actual communication between programs is expected to be handled through application libraries, written in ATS, which implement asynchronous

Figure 1.3: Example of interprocess communication

communication mechanisms, without kernel involvement.

The use of asynchronous communication mechanisms avoids the creation of dependencies between two schedulable entities, which avoids the pitfalls of synchronous IPC on fixed-priority real-time scheduling algorithms (Steinberg et al., 2005).

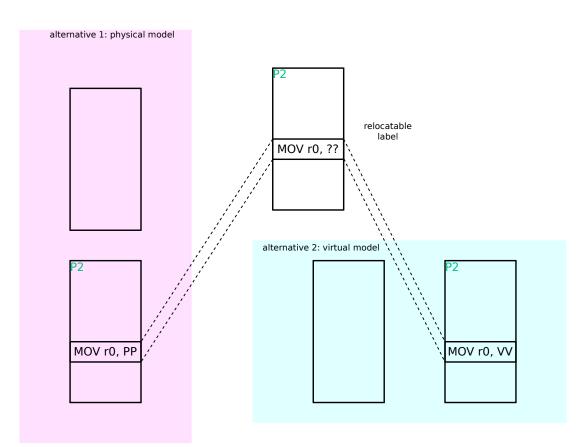

#### Hardware memory protection independence

Hardware memory protection is useful when dealing with unknown applications or during development to find and protect against undesired behaviors. However, it is less useful when all application code is known, or has been checked for safety with other means, and it does impose overhead on performance. Therefore, Terrier has been programmed from the ground up to operate correctly with or without hardware memory protection. It can be disabled prior to boot, currently as a compilation option.

The application programming model is affected by the use or non-use of virtual memory. In a virtual memory environment, all applications are provided the illusion of having the entire memory space to themselves. In a physical memory environment,

Figure 1.4: Hardware memory protection independence

applications are given different segments of memory for their own use and must avoid access outside of their space.

Terrier achieves the flexibility by requiring that all application programs be compiled with relocation sections enabled. Then, at load-time, Terrier rewrites the application binary code so that it fits into either one of the two memory models as shown in Figure 1.4.

### 1.2.4 Programming language-based safety

Terrier shifts much of the responsibility for program safety away from the hardware and kernel onto the application programmer. It also provides a more challenging model for programs. To make up for that, Terrier encourages the use of the ATS func-

|            | Proposition | Type     |

|------------|-------------|----------|

| Linear     | view        | viewtype |

| Non-linear | prop        | type     |

Table 1.1: ATS terminology

tional programming language, which allows the use of dependent and linear types, while allowing the programmer to avoid most or all of the overhead typically associated with high level languages.

#### Types in ATS

ATS has multiple levels of types (i.e. "types" of types) that are necessary in order to have usable, complex types that can describe interesting properties. ATS uses the term *sort* (Xi, 2004) to distinguish "types" of types from types of values. The programmer may quantify at the sort-level in order to describe particular values to index a type. Alternatively, you might say, these are the values upon which a type is "dependent."

ATS also has other dichotomies: proposition vs "real" type, linear vs non-linear. Linear types are also nicknamed *views*, from the common usage of protecting pointers that have a particular "view" of memory. The various ATS names for these concepts are shown in table 1.1.

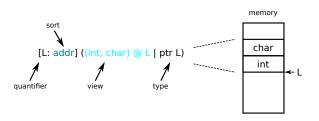

In the example of figure 1.5 the *c* (pronounced: at-view) is a constructor for a view, and it has two parameters: the type of value found in memory ((int, char) in the example), and the address at which it is found (L in the example). The at-view

Figure 1.5: Views and types in ATS syntax

abstractly represents the "view" of that slice of memory found at that address.

#### **Resource** management

One of the biggest tasks in system development is that of resource management. As a result, one of the biggest source of bugs in systems is caused by resource mismanagement. The linear propositions and types provided by ATS are well suited to addressing this problem. In short, a value of a linear type is consumed once and exactly once, avoiding the common errors of memory leak or dangling pointer. In addition, the dependent types of ATS are useful for describing exactly the kind of details that need to be statically checked for safe usage. For example, array bounds length, or contents of a memory region accessible through a particular pointer.

#### Synchronization

Another use of linear types and properties is for synchronization. For example, locks can be considered a kind of resource that must be acquired and released. Linear types can be used to enforce sequencing of steps; they are also useful for locks that must be acquired in a particular order to avoid deadlocking.

#### Avoiding overhead

After compilation, all of the types are stripped away and therefore none of it affects runtime performance.

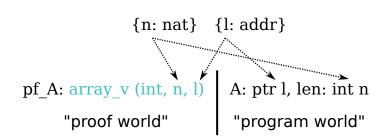

And even though ATS is a high level language, it primarily works with "flat types" that are essentially equivalent to C's data representation. They are types of varying sizes, often referred to as "unboxed types" in other contexts. For example, the low-level implementation of a flat "pair" is just a C struct with two members.

To go along with that, ATS has support for templates as a means of gaining the practical benefits of parametric polymorphism. Like C++, the templates of ATS are generated for each different type, and the names are mangled to co-exist with each

other.

#### 1.2.5 Scheduling

In order to provide guaranteed partitions of processor time to each program, Terrier uses a static priority, rate monotonic (Liu and Layland, 1973) real-time scheduler algorithm. The design shies away from traditional blocking schemes that use systems of queues to wake-up programs when their request is available. Instead, the system programmer is expected to choose parameters for the scheduler that give each program an adequate amount of time to operate, at periodic intervals. Each program will respond to events in turn, when given control of the CPU. Most communication is expected to be conducted asynchronously, so programs will continue to run and execute code after invoking a communication protocol. Programs that must run with significant concurrency to each other are expected to be scheduled on separate CPUs, decoupled by asynchronous communication mechanisms, which helps avoid unnecessary delays.

### 1.3 Related work

Verification of operating system software has been a goal of many researchers and programmers over the decades. In a way, it is reminiscent of the effort by early 20th century mathematicians to find a firm basis for their theories rooted in purely logical reasoning. Since the operating system forms the basis of a computer system, its correctness is vital to the correct operation of all other software running on the system. However there are many challenges: the operating system must manage many different layers of hardware and software together, many different applications and devices that may be independently designed, and it must accomplish all of these feats within a fraction of a millisecond. So while the operating system is a kind of program, it is a very special kind of program that deserves its own consideration.

#### **1.3.1** Program verification

There have been a great many efforts to improve the reliability of programs using programming language techniques. Some are applied to existing languages, like CCured (Necula et al., 2005), which checks memory safety of ordinary C programs by applying a carefully designed strong type system that differentiates between different kinds of pointer use. It inserts run-time checks where memory safety cannot be proven statically, and tracks meta-data about certain pointers in order to implement those run-time safety tests—these are often called "fat" pointers. In a slightly different approach, Cyclone (Jim et al., 2002) is a memory-safe dialect of C. It achieves its goal by restricting the behavior of C programs and then recovering some of that expressiveness by giving the programmer features that: insert NULL-pointer checks, use "fat" pointers when pointer arithmetic is desired, have growable regions as an alternative to classical manual memory management, and more.

TESLA (Anderson et al., 2014) is a tool that allows programmers to annotate their C code with temporal assertions that describe safety properties in a language based on Linear Temporal Logic. The assertions generate code that is used to instrument the program at run-time in order to check the given properties. TESLA is an entirely dynamic analysis tool and therefore imposes a run-time penalty on instrumented programs. In contrast, MUVI (Lu et al., 2007) automatically detects certain classes of concurrency bugs statically using pattern analysis on multi-variable access correlations. It is able to detect when correlated variables are not updated in a consistent way, and when correlated accesses are not protected in the same atomic section. Although useful for finding those two classes of bugs, MUVI cannot verify arbitrarily specified properties in general.

Other efforts have focused on the creation of novel programming languages. BitC (Sridhar et al., 2008) is a language intended to be used for systems programming with

an ML-style type system with effects. It allows precise control of the representation of types in memory while enjoying the advantage of static type inference. Theoremproving is syntactically supported but left to a (yet to be created) plugin or third-party application.

Bedrock (Chlipala, 2011) is a Coq (Herbelin, 2009) library that forms a programming language to address these concerns. It uses a computational approach to verify low level code that allows programmers to express invariants using functional constructs already present in the Coq environment. Bedrock contains a generic machine language syntax for describing program implementations. There are few operations, including: describing registers, memory dereferencing, conditionals, and jumps. On top of this, assertions in separation logic allow a programmer to define pre- and postconditions on functions. Given that ATS and C share the same data representation, it is possible that I could make use of the C code verified by Bedrock when constructing ATS programs.

Dafny (Leino, 2010) is an imperative programming language designed to support the static verification of programs using the Boogie intermediate language (Barnett et al., 2006) and the Z3 SMT solver (De Moura and Bjørner, 2008). The Dafny compiler produces code suitable for the .NET platform.

#### 1.3.2 Operating system verification

With operating system software being fundamental to the correct functioning of the entire machine, many efforts have been directed at trying to verify operating systems. The seL4 project is based on a family of microkernels known as L4 (Klein et al., 2009). In that work, a refinement proof was completed that demonstrates the adherence of a high-performance C implementation to a generated executable specification, created from a prototype written in Haskell, and checked in the Isabelle (Paulson, 1994) theorem proving system. The prototype itself is checked against a high-level design. One difference with my work is that I seek to eliminate the phase of manual translation from high to low level language. Another difference is that, while the seL4 approach can certainly bring many benefits, I feel that the cost associated with it is too high for ordinary use. For example, it may turn out to be intractably difficult to apply this technique to a multiprocessor kernel. That is currently an open problem according to Elphinstone and Heiser (2013).

Singularity (Hunt and Larus, 2007) is a microkernel OS written in a high-level and type-safe language that employs language properties and software isolation to guarantee memory safety and eliminate the need for hardware protection domains in many cases. In particular, it makes use of a form of linear types in optimizing communication channels. Singularity was an inspiration for Terrier, although several goals are different. For instance, Terrier seeks to avoid, as much as possible, the overhead associated with high-level languages. Terrier's design is more explicitly geared towards embedded devices responding to real-time events. And inter-program communication in Terrier is left open enough to accommodate multiple approaches, tailored to the particular application domain.

House (Hallgren et al., 2005) is an operating system project written primarily in the Haskell functional programming language. It takes advantage of a rewrite of the GHC (Peyton-Jones et al., 2014) run-time environment that eliminates the need for OS support, and instead operates directly on top of PS/2-compatible hardware. Then a foreign function interface is used to create a kernel written in Haskell. There is glue code written in C that glosses over some of the trickiness. For example, interrupts are handled by C code that sets flags that the Haskell code can poll at safe points. This avoids potentially corrupting the Haskell heap due to interruptions of the Haskell garbage collector while it is an inconsistent state. SPIN (Bershad et al., 1995) is a pioneering effort along these lines that used the Modula-3 language (Cardelli et al., 1989) to provide a protection model and extensibility. In general, these types of systems do not tackle the problem of high-level language overhead, generally do not handle multiprocessing well if at all, and only offer guarantees as good as their type system can handle.

Verve (Yang and Hawblitzel, 2010) improves on this approach by splitting the system into two parts: a "Nucleus" written in verified assembly language that exports abstractions of the underlying hardware, and a kernel layer on top of that, which provides traditional services. Verve verifies the correctness of the Nucleus, but only verifies the safety of the kernel. Verve is fully mechanically verified for type safety, but it does not support multiple processors, uses a stop-the-world GC, and keeps interrupts disabled during collection, making it unsuitable for real-time applications. The Ironclad Apps framework (Hawblitzel et al., 2014) extends the Verve OS with some advanced features to support end-to-end security, secure hardware, and the Dafny language. Ironclad Apps uses a modified Dafny compiler that outputs BoogieX86 (Hawblitzel and Petrank, 2009) code that can be verified independently and easily translated into machine code.

Both VFiasco (Hohmuth and Tews, 2005) and Verisoft (Alkassar et al., 2008) take a completely different approach to system verification. Verisoft relies upon a custom hardware architecture that has itself been formally verified, and a verified compiler to that instruction set. VFiasco claims that it is better to write the kernel in an unsafe language such as C++ and then mechanically generate theorems from that source code, to be discharged by an external proof engine.

#### **1.3.3** Asynchronous communication mechanisms

Simpson (1990) designed an ACM called the "four-slot mechanism" intended to allow the communication of a piece of reference data from a single writer to a single reader without the use of any mutual exclusion mechanisms nor special atomic operations. The name "four-slot" comes from the memory space requirement: the mechanism requires the use of an array that can hold up to four copies of the reference data. The same paper also described several of the desired properties of such mechanisms, as well as a scheme for categorizing the behavior of certain ACMs. This "four-slot mechanism" was later generalized (Simpson, 1997a) to work with multiple readers and multiple writers, resulting in a " $2 \times nw \times (n_r + 1)$ -slot mechanism", where  $n_w, n_r$  are the number of writers and readers respectively.

The ATS implementation (Danish and Xi, 2014) of Simpson's four-slot mechanism is compact, efficient and shows how expressive types can provide useful assurances at a low-level without intruding into run-time performance of critical code or requiring voluminous quantities of proof-writing.

Simpson (1992) also developed a model-checking technique called "role model analysis" and then applied it to his four-slot mechanism (Simpson, 1997b) to verify properties of coherency and freshness. Henderson and Paynter (2002) created a formal model of the four-slot mechanism in PVS and used it to show that it was atomic under certain assumptions about interleaving. Rushby (2002) used model-checking to verify coherency and freshness in the four-slot mechanism but also found the latter can only be shown if the control registers are assumed to be atomic. By comparison, my approach has been to encode pieces of the desired theorems into the type system, apply it to working code, and then allow the type-checker to verify consistency. If a mistake is made, it will be caught prior to compilation. Or, if the type-checker is satisfied, then the end result is efficient C code that may be compiled and linked and used directly by applications.

Subsequent to Simpson's work, Chen and Burns (1997) collaborated on a "threeslot mechanism" that offered the same features as the "four-slot mechanism" except it is able to operate with a smaller memory requirement. This mechanism was proven to be safe and effective as long as the atomic operation Compare-And-Swap is available from the hardware. This too was later generalized (Chen and Burns, 1998) into an "n+2-slot mechanism" with a single writer and n readers, using the atomic operation **Test-And-Set**. Both Simpson's and Chen's ACMs have a rising memory requirement that scales with the number of programs communicating with each other.

The following year, Chen and Burns (1999) introduced one answer to the scaling space problem: a "timing-based" ACM based on circular buffers. In this approach, the size of the circular buffer is statically configured based on the static rate-monotonic scheduling parameters. For many real-time systems, this is a reasonable approach, although it does require re-analysis any time the static scheduling parameters are changed. By comparison, the fixed-slot mechanism remains in the category of "algorithm-based" solutions, since it does not require foreknowledge of scheduling parameters.

#### 1.3.4 Related designs

First popularized in the 1980s, a microkernel design (Liedtke, 1995) keeps as much kernel functionality as possible out of the hardware-privileged level. Normally in such a design, privileged code is restricted to the minimum necessary to implement hardware memory protection, most basic scheduling, and interprocess communication. Higher level operating system functions are moved out into unprivileged processes or threads, and then granted access to the hardware on a restricted basis. These processes or threads are expected to all coordinate with each other, and with other programs, by using the core interprocess communication mechanisms.