Number 698

# Pulse-based, on-chip interconnect

Simon J. Hollis

September 2007

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500 http://www.cl.cam.ac.uk/

## © 2007 Simon J. Hollis

This technical report is based on a dissertation submitted June 2007 by the author for the degree of Doctor of Philosophy to the University of Cambridge, Queens' College.

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

http://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986

## **Abstract**

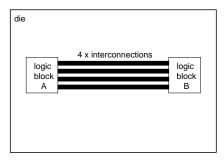

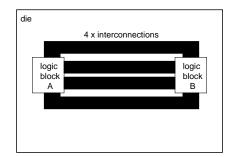

This thesis describes the development of an on-chip point-to-point link, with particular emphasis on the reduction of its global metal area footprint.

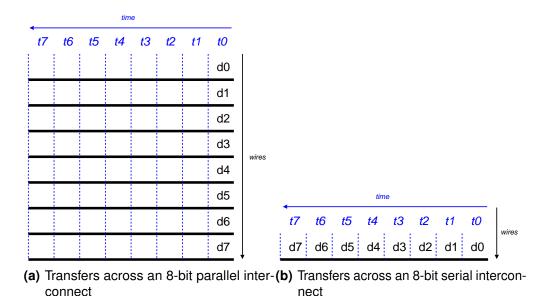

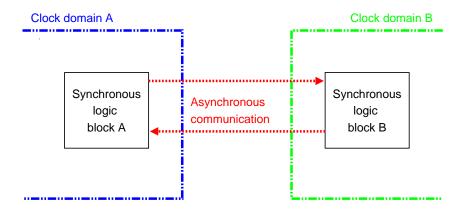

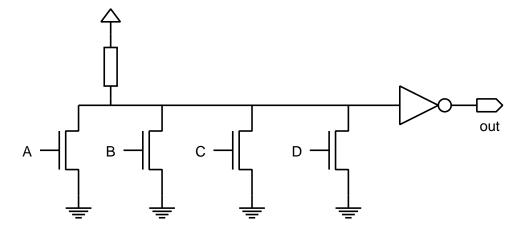

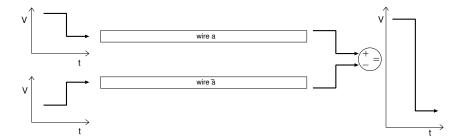

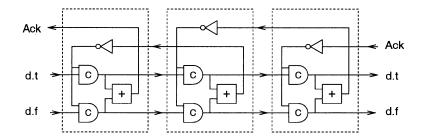

To reduce its metal footprint, the interconnect uses a serial transmission approach. 8-bit data is sent using just two wires, through a pulse-based technique, inspired by the *GasP* interconnect from Sun Microsystems. Data and control signals are transmitted bi-directionally on a wire using this double-edged, pulse-based signalling protocol, and formatted using a variant of dual-rail encoding. These choices enable a reduction in the number of wires needed, an improvement in the acknowledgement overhead of the asynchronous protocol, and the ability to cross clock domains without synchronisation hazards.

New, stateful, repeaters are demonstrated, and results from *spice* simulations of the system show that data can be transferred at over 1Gbit/s, over 1mm of minimum-sized, minimally-spaced metal 5 wiring, on a 180nm (0.18 $\mu$ m) technology. This reduces to only 926Mbit/s, when 10mm of wiring is considered, and represents a channel utilisation of a very attractive 45% of theoretical capacity at this length. Analysis of latencies, energy consumption, and area use are also provided.

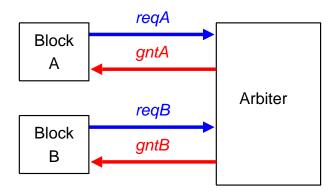

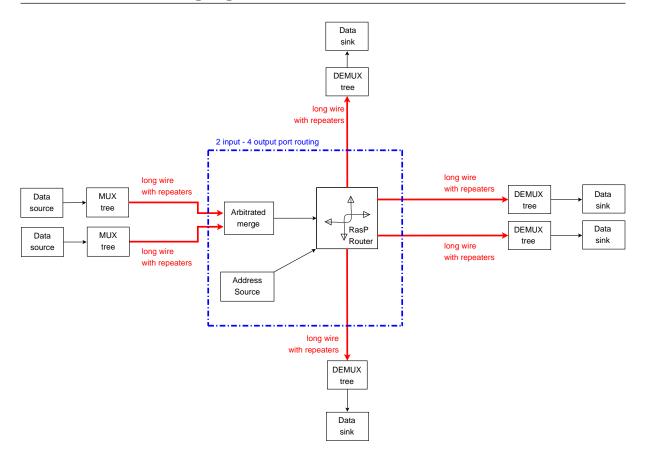

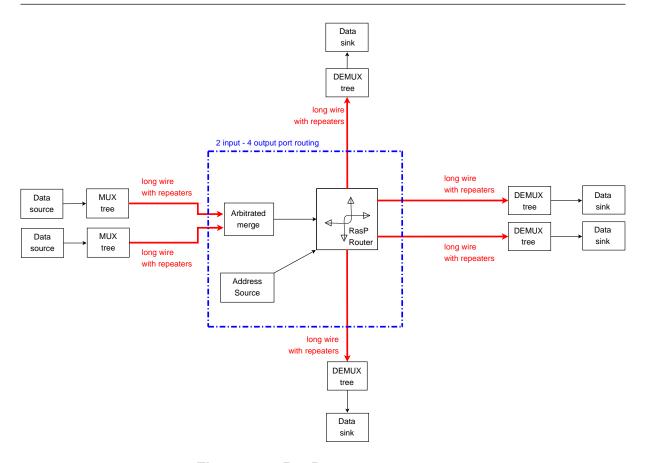

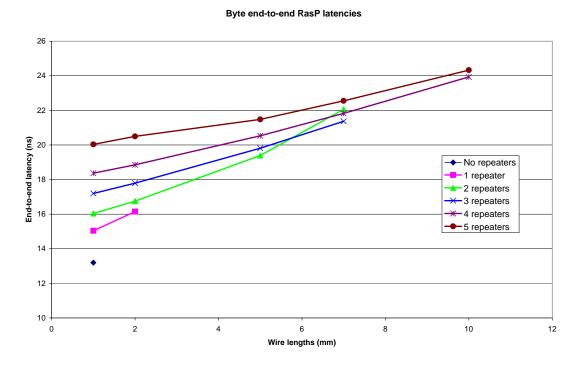

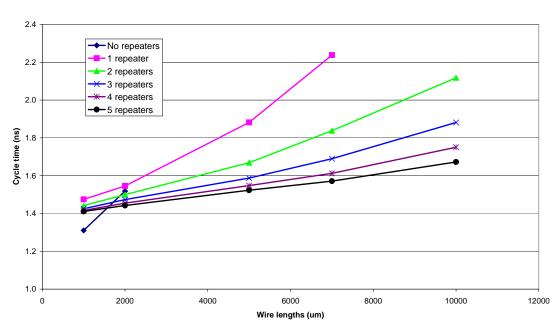

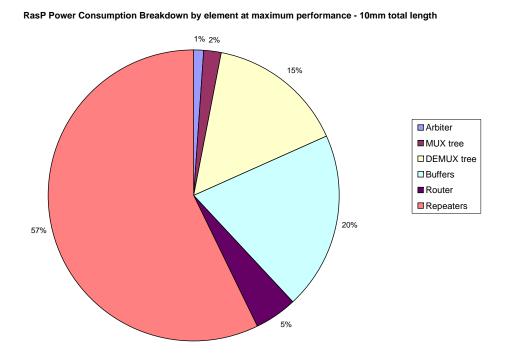

The point-to-point link is then expanded with the invention and demonstration of a router and an arbitrated merge element, to produce a Network-on-Chip (NoC) design, called *RasP*. The full system is then evaluated, and peak throughput is shown to be 763Mbit/s for 1mm of wiring, reducing to 599Mbit/s for 10mm of the narrow metal 5 interconnect.

Finally, RasP is compared in performance with the *Chain* interconnect from the University of Manchester. Results for the metrics of throughput, latency, energy consumption and area footprint show that the two systems perform very similarly—the maximum absolute deviation is under 25% for throughput, latency and area; and the energy-efficiency of RasP is approximately twice that of Chain. Between the two systems, RasP has the smaller latency, energy and area requirements and is shown to be a viable alternative NoC design.

## Acknowledgements

This thesis is dedicated to my parents, without whose help and belief it would have never been written. They have always encouraged me to do what I enjoy, whatever the cost. It is with this credo that I have found my niche in research. I will always thank them.

My eternal gratitude goes to my supervisor, Simon Moore, without whose expertise and help, I would have never got this far. Over the years, Simon has not only provided me with advice and funding, but has never complained when I wanted to go off on a tangent. This thesis is, I hope, proof of the success of such an approach; thank you.

John Whitington and Daniel Greenfield deserve special mention for proof-reading this mighty document, and providing a great deal of corrections (even if we did sometimes disagree about the finer points of grammar).

I also wish to thank my dear friends, Andy, Ash and Mark, who have filled my nights with experiences dear during the three and half years it has taken to prepare this dissertation.

Finally, I wish to express my appreciation to my housemates over the years — you have kept me sane (and frequently fed and watered) along the journey.

# **Contents**

| Co | onter |                                 | 7         |

|----|-------|---------------------------------|-----------|

|    | List  | of Tables                       | 11        |

|    | List  | of Figures                      | 13        |

| 1  | Intr  | oduction                        | 17        |

|    | 1.1   | Overview of the proposed system |           |

|    | 1.2   | Approach                        | 19        |

| 2  | Inte  | erconnect design                | <b>21</b> |

|    | 2.1   | Introduction                    | 21        |

|    | 2.2   | Parallel interconnect design    | 21        |

|    |       | 2.2.1 Performance               | 22        |

|    |       | 2.2.2 Overheads                 | 23        |

|    | 2.3   | Serial interconnect design      | 23        |

|    |       | 2.3.1 Performance               | 25        |

|    |       | 2.3.2 Overheads                 | 25        |

|    | 2.4   | Clock skew                      | 26        |

|    |       | 2.4.1 GALS                      | 26        |

|    | 2.5   | Data encoding                   | 27        |

|    | 2.6   | Summary                         | 29        |

| 3  | Con   | nnectivity of interconnects     | 31        |

|    | 3.1   | Point-to-point links            | 31        |

|    |       | 3.1.1 Uni-directional links     | 32        |

|    |       | 3.1.2 Bi-directional links      | 32        |

|    |       | 3.1.3 Packetisation             | 32        |

|    |       | 3.1.4 Half-duplex links         | 32        |

|    | 3.2   | Point-to-multipoint links       | 33        |

|    | 3.3   | Multipoint-to-point links       |           |

|    | 3.4   | Multipoint-to-multipoint links  |           |

|    |       | 3.4.1 Buses                     |           |

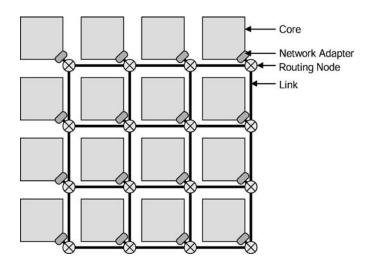

|    |       | 3.4.2 Networks-on-Chip          |           |

|    |       | 3.4.3 Circuit-switched networks |           |

|    | 3.5   | Summary                         | 36        |

#### **Contents**

|   | Phys                                                  | sical characteristics and limitations of interconnects                                                                                                                                                                                                                                                                                                                                                                                                                | <b>37</b>                                                                        |

|---|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|   | 4.1                                                   | Wires                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 37                                                                               |

|   |                                                       | 4.1.1 Wire Resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 38                                                                               |

|   |                                                       | 4.1.2 Wire Capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                | 39                                                                               |

|   |                                                       | 4.1.3 Wire Inductance                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 42                                                                               |

|   | 4.2                                                   | Delay models                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 44                                                                               |

|   |                                                       | 4.2.1 The Elmore delay model                                                                                                                                                                                                                                                                                                                                                                                                                                          | 44                                                                               |

|   |                                                       | 4.2.2 The $\pi$ delay model                                                                                                                                                                                                                                                                                                                                                                                                                                           | 45                                                                               |

|   |                                                       | 4.2.3 First-order RC delay approximation                                                                                                                                                                                                                                                                                                                                                                                                                              | 45                                                                               |

|   |                                                       | 4.2.4 Effects on delay of resistance, capacitance and inductance                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                  |

|   |                                                       | 4.2.5 Trade-offs                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                  |

|   | 4.3                                                   | Signal integrity                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 49                                                                               |

|   |                                                       | 4.3.1 Crosstalk                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

|   | 4.4                                                   | The routing problem                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                  |

|   | 4.5                                                   | Conventional trade-offs in interconnect design                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                  |

|   |                                                       | 4.5.1 Throughput and latency                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                  |

|   |                                                       | 4.5.2 Throughput and space                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                  |

|   |                                                       | 4.5.3 Throughput and power                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                  |

|   | 4.6                                                   | Driving transistors                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                  |

|   | 1.0                                                   | 4.6.1 Models                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                  |

|   |                                                       | 4.6.2 Driving transistor behaviour                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

|   | 4.7                                                   | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

|   | 1.,                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 00                                                                               |

| 5 |                                                       | <b>'1</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 61                                                                               |

|   | 5.1                                                   | Asynchronous logic                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 62                                                                               |

|   |                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

|   |                                                       | 5.1.1 Handshaking                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

|   | 5.2                                                   | 5.1.1 HandshakingThe GasP control system                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |

|   | 5.2                                                   | The GasP control system                                                                                                                                                                                                                                                                                                                                                                                                                                               | 66<br>66                                                                         |

|   | 5.2                                                   | The GasP control system                                                                                                                                                                                                                                                                                                                                                                                                                                               | 66<br>66<br>67                                                                   |

|   | 5.2                                                   | The GasP control system                                                                                                                                                                                                                                                                                                                                                                                                                                               | 66<br>66<br>67                                                                   |

|   |                                                       | The GasP control system                                                                                                                                                                                                                                                                                                                                                                                                                                               | 66<br>66<br>67<br>68                                                             |

|   | 5.3                                                   | The GasP control system                                                                                                                                                                                                                                                                                                                                                                                                                                               | 66<br>66<br>67<br>68<br>69                                                       |

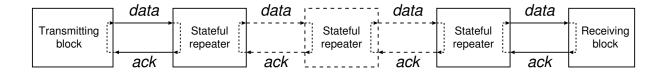

|   | 5.3                                                   | The GasP control system  5.2.1 Micropipelines  5.2.2 GasP and micropipelines  5.2.3 The unsuitability of GasP for area-efficient interconnect  Introduction to my point-to-point interconnect                                                                                                                                                                                                                                                                         | 66<br>66<br>67<br>68<br>69<br>71                                                 |

|   | 5.3                                                   | The GasP control system  5.2.1 Micropipelines  5.2.2 GasP and micropipelines  5.2.3 The unsuitability of GasP for area-efficient interconnect  Introduction to my point-to-point interconnect  Chosen data encoding                                                                                                                                                                                                                                                   | 66<br>67<br>68<br>69<br>71<br>71                                                 |

|   | 5.3                                                   | The GasP control system  5.2.1 Micropipelines  5.2.2 GasP and micropipelines  5.2.3 The unsuitability of GasP for area-efficient interconnect  Introduction to my point-to-point interconnect  Chosen data encoding  5.4.1 Serial transmission                                                                                                                                                                                                                        | 66<br>67<br>68<br>69<br>71<br>71<br>72                                           |

|   | 5.3<br>5.4                                            | The GasP control system  5.2.1 Micropipelines  5.2.2 GasP and micropipelines  5.2.3 The unsuitability of GasP for area-efficient interconnect Introduction to my point-to-point interconnect Chosen data encoding  5.4.1 Serial transmission  5.4.2 Voltage swing                                                                                                                                                                                                     | 66<br>66<br>67<br>68<br>69<br>71<br>71<br>72<br>72                               |

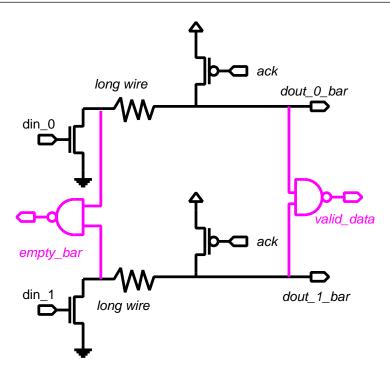

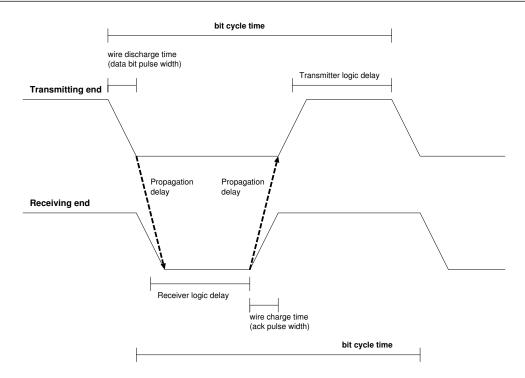

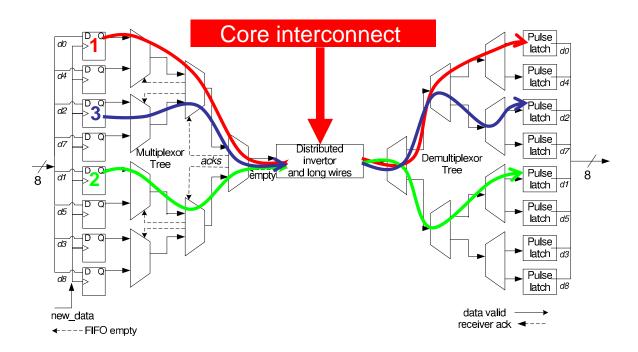

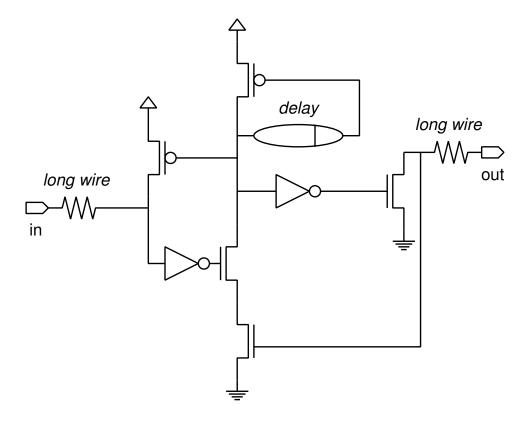

|   | 5.3<br>5.4                                            | The GasP control system  5.2.1 Micropipelines  5.2.2 GasP and micropipelines  5.2.3 The unsuitability of GasP for area-efficient interconnect Introduction to my point-to-point interconnect Chosen data encoding  5.4.1 Serial transmission  5.4.2 Voltage swing The core interconnect (dual distributed inverter structure)                                                                                                                                         | 66<br>67<br>68<br>69<br>71<br>71<br>72<br>72<br>74                               |

|   | 5.3<br>5.4<br>5.5                                     | The GasP control system  5.2.1 Micropipelines  5.2.2 GasP and micropipelines  5.2.3 The unsuitability of GasP for area-efficient interconnect  Introduction to my point-to-point interconnect  Chosen data encoding  5.4.1 Serial transmission  5.4.2 Voltage swing  The core interconnect (dual distributed inverter structure)  5.5.1 Pulse generation                                                                                                              | 66<br>66<br>67<br>68<br>69<br>71<br>71<br>72<br>72<br>74<br>75                   |

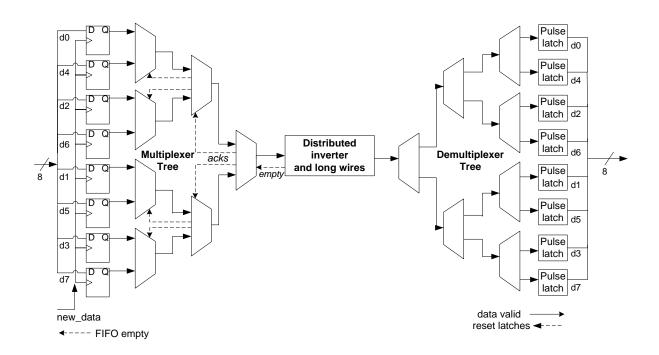

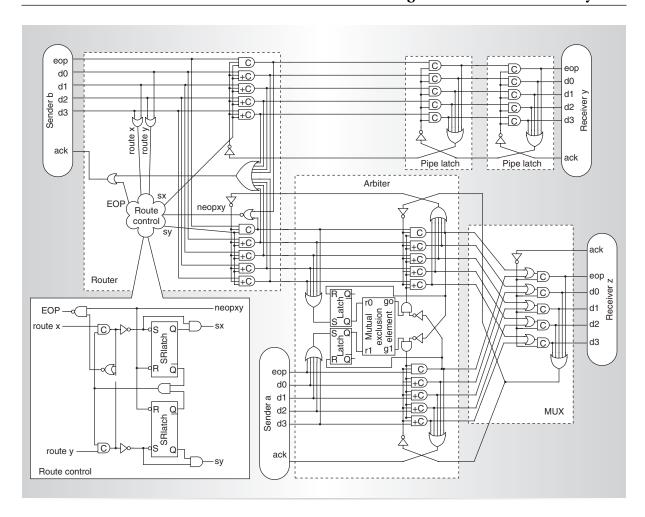

|   | 5.3<br>5.4<br>5.5<br>5.6                              | The GasP control system  5.2.1 Micropipelines  5.2.2 GasP and micropipelines  5.2.3 The unsuitability of GasP for area-efficient interconnect Introduction to my point-to-point interconnect Chosen data encoding  5.4.1 Serial transmission  5.4.2 Voltage swing The core interconnect (dual distributed inverter structure)  5.5.1 Pulse generation Point-to-point interconnect implementation                                                                      | 66<br>67<br>68<br>69<br>71<br>72<br>72<br>74<br>75<br>75                         |

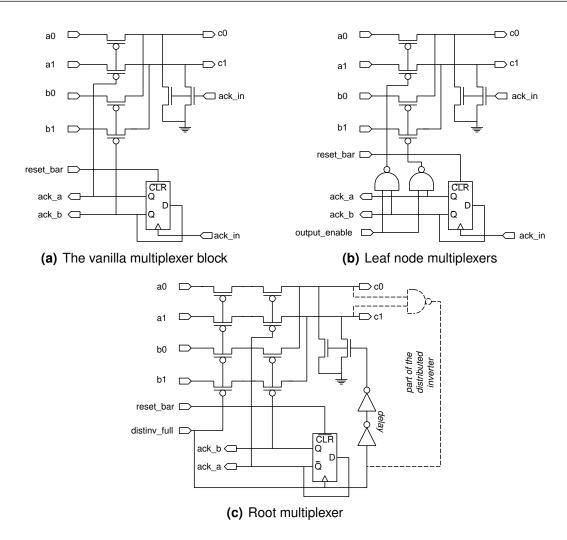

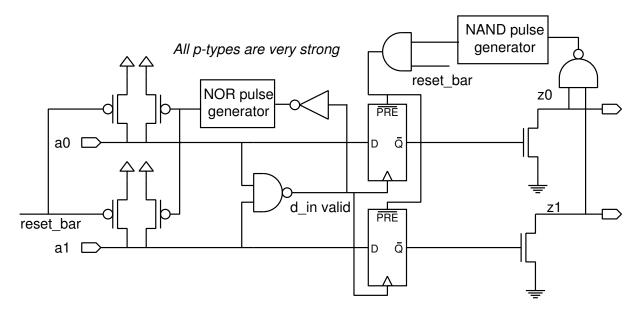

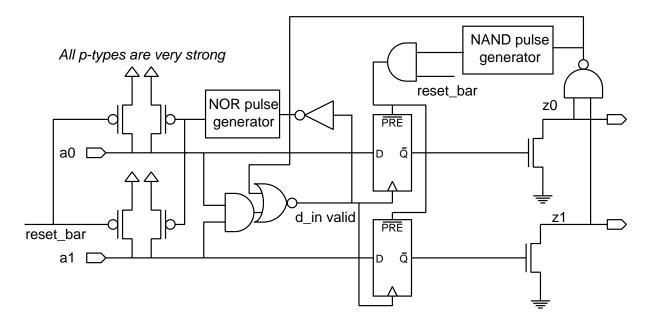

|   | 5.3<br>5.4<br>5.5<br>5.6<br>5.7                       | The GasP control system  5.2.1 Micropipelines  5.2.2 GasP and micropipelines  5.2.3 The unsuitability of GasP for area-efficient interconnect Introduction to my point-to-point interconnect Chosen data encoding  5.4.1 Serial transmission  5.4.2 Voltage swing The core interconnect (dual distributed inverter structure)  5.5.1 Pulse generation Point-to-point interconnect implementation MUXs                                                                 | 66<br>66<br>67<br>68<br>69<br>71<br>72<br>72<br>74<br>75<br>75                   |

|   | 5.3<br>5.4<br>5.5<br>5.6<br>5.7                       | The GasP control system  5.2.1 Micropipelines  5.2.2 GasP and micropipelines  5.2.3 The unsuitability of GasP for area-efficient interconnect Introduction to my point-to-point interconnect Chosen data encoding  5.4.1 Serial transmission  5.4.2 Voltage swing The core interconnect (dual distributed inverter structure)  5.5.1 Pulse generation Point-to-point interconnect implementation  MUXs  5.7.1 State                                                   | 66<br>66<br>67<br>68<br>69<br>71<br>71<br>72<br>72<br>74<br>75<br>75<br>78<br>80 |

|   | 5.3<br>5.4<br>5.5<br>5.6<br>5.7                       | The GasP control system  5.2.1 Micropipelines  5.2.2 GasP and micropipelines  5.2.3 The unsuitability of GasP for area-efficient interconnect Introduction to my point-to-point interconnect Chosen data encoding  5.4.1 Serial transmission  5.4.2 Voltage swing The core interconnect (dual distributed inverter structure)  5.5.1 Pulse generation Point-to-point interconnect implementation MUXs  5.7.1 State  DEMUXs  5.8.1 State                               | 666<br>6768<br>6971<br>7172<br>7274<br>7575<br>7880<br>80                        |

|   | 5.3<br>5.4<br>5.5<br>5.6<br>5.7                       | The GasP control system  5.2.1 Micropipelines  5.2.2 GasP and micropipelines  5.2.3 The unsuitability of GasP for area-efficient interconnect Introduction to my point-to-point interconnect Chosen data encoding  5.4.1 Serial transmission  5.4.2 Voltage swing The core interconnect (dual distributed inverter structure)  5.5.1 Pulse generation Point-to-point interconnect implementation MUXs  5.7.1 State  DEMUXs  5.8.1 State  5.8.2 Operation              | 666<br>6768<br>6971<br>7172<br>7475<br>7578<br>8080<br>81                        |

|   | 5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8                | The GasP control system  5.2.1 Micropipelines  5.2.2 GasP and micropipelines  5.2.3 The unsuitability of GasP for area-efficient interconnect Introduction to my point-to-point interconnect Chosen data encoding  5.4.1 Serial transmission  5.4.2 Voltage swing The core interconnect (dual distributed inverter structure)  5.5.1 Pulse generation Point-to-point interconnect implementation MUXs  5.7.1 State DEMUXs  5.8.1 State  5.8.2 Operation Pulse latches | 666<br>6768<br>6971<br>7172<br>7274<br>7575<br>7880<br>8081<br>8182              |

|   | 5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10 | The GasP control system  5.2.1 Micropipelines  5.2.2 GasP and micropipelines  5.2.3 The unsuitability of GasP for area-efficient interconnect Introduction to my point-to-point interconnect Chosen data encoding  5.4.1 Serial transmission  5.4.2 Voltage swing The core interconnect (dual distributed inverter structure)  5.5.1 Pulse generation Point-to-point interconnect implementation MUXs  5.7.1 State  DEMUXs  5.8.1 State  5.8.2 Operation              | 666<br>6768<br>6971<br>7172<br>7475<br>7578<br>8081<br>8182<br>8484              |

| 5.11.2 Stateful repeater       88         5.11.3 A potential optimisation       90         5.12 Summary       90         5.12 Summary       90         6.1 Introduction       93         6.2 Methodology       93         6.2.1 Wire model       94         6.2.2 Optimal repeater insertion       96         6.2.3 Driving transistor characterisation       97         6.2.4 Output buffer cascading factor       99         6.3 Simulation of correctness       100         6.4 Point-to-point link results       103         6.5 A loop oscillator       103         6.5.1 Additional repeater insertion       105         6.5.2 Comparison to published literature       107         6.6 Basic link evaluation       114         6.7 Pulse widths       114         6.8 Voltage swing       114         6.8.1 Crosstalk       120         6.8.2 Reflections and ringing       122         6.8.3 Effects of inductance       123         6.9 Pulse generator design choice       123         6.10 Evaluation of the flop-based design       125         6.10.1 Throughput       126         6.10.2 Evaluation of the pulse-chopper based design       131         6.12.2 Through                                                                            |   |      | Con                                        | ntents |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|--------------------------------------------|--------|

| 5.11.3 A potential optimisation       90         5.12 Summary       90         6 Evaluation of the area-efficient interconnect       93         6.1 Introduction       93         6.2 Methodology       93         6.2.1 Wire model       94         6.2.2 Optimal repeater insertion       96         6.2.3 Driving transistor characterisation       97         6.2.4 Output buffer cascading factor       99         6.3 Simulation of correctness       100         6.3.1 Test results       100         6.4 Point-to-point link results       103         6.5 Aloop oscillator       103         6.5.1 Additional repeater insertion       105         6.5.2 Comparison to published literature       107         6.6 Basic link evaluation       114         6.7 Pulse widths       114         6.8 Voltage swing       119         6.8.1 Crosstalk       120         6.8.2 Reflections and ringing       122         6.8.3 Effects of inductance       123         6.10 Evaluation of the flop-based design       125         6.10.1 Throughput       126         6.10.2 Latency       127         6.11 Summary of the flop-based design       131         6.12.1 Latency <th></th> <th></th> <th>5.11.2 Stateful repeater</th> <th> 88</th>             |   |      | 5.11.2 Stateful repeater                   | 88     |

| 5.12 Summary       90         6 Evaluation of the area-efficient interconnect       93         6.1 Introduction       93         6.2 Methodology       93         6.2.1 Wire model       94         6.2.2 Optimal repeater insertion       96         6.2.3 Driving transistor characterisation       97         6.2.4 Output buffer cascading factor       99         6.3 Simulation of correctness       100         6.3.1 Test results       100         6.4 Point-to-point link results       103         6.5.1 Additional repeater insertion       105         6.5.2 Comparison to published literature       107         6.6 Basic link evaluation       114         6.7 Pulse widths       114         6.8 Voltage swing       119         6.8.1 Crosstalk       120         6.8.2 Reflections and ringing       122         6.8.3 Effects of inductance       123         6.9 Pulse generator design choice       123         6.10 Evaluation of the flop-based design       125         6.10.1 Throughput       126         6.10.2 Latency       127         6.11 Summary of the flop-based design       131         6.12.2 Throughput       131         6.13.1 Repeater in                                                                            |   |      | •                                          |        |

| 6.1 Introduction       93         6.2 Methodology       93         6.2.1 Wire model       94         6.2.2 Optimal repeater insertion       96         6.2.3 Driving transistor characterisation       97         6.2.4 Output buffer cascading factor       99         6.3 Simulation of correctness       100         6.3.1 Test results       100         6.4 Point-to-point link results       103         6.5 Aloop oscillator       103         6.5.1 Additional repeater insertion       105         6.5.2 Comparison to published literature       107         6.6 Basic link evaluation       114         6.7 Pulse widths       114         6.8 Voltage swing       119         6.8.1 Crosstalk       120         6.8.2 Reflections and ringing       122         6.8.3 Effects of inductance       123         6.9 Pulse generator design choice       123         6.10.1 Throughput       126         6.10.1 Throughput       126         6.10.2 Latency       127         6.11 Summary of the flop-based design       128         6.12 Evaluation of the pulse-chopper based design       131         6.12 Evaluation of the pulse-chopper based design       131         <                                                                        |   | 5.12 |                                            |        |

| 6.2 Methodology       93         6.2.1 Wire model       94         6.2.2 Optimal repeater insertion       96         6.2.3 Driving transistor characterisation       97         6.2.4 Output buffer cascading factor       99         6.3 Simulation of correctness       100         6.3.1 Test results       100         6.4 Point-to-point link results       103         6.5 A loop oscillator       103         6.5.1 Additional repeater insertion       105         6.5.2 Comparison to published literature       107         6.6 Basic link evaluation       114         6.7 Pulse widths       114         6.8 Voltage swing       119         6.8.1 Crostalk       120         6.8.2 Reflections and ringing       122         6.8.3 Effects of inductance       123         6.9 Pulse generator design choice       123         6.10 Evaluation of the flop-based design       125         6.10.1 Throughput       126         6.10.2 Latency       127         6.11 Summary of the flop-based design       131         6.12.1 Latency       131         6.12.2 Throughput       131         6.13.3 Repeater insertion with the chopper-based link       134         6.1                                                                            | 6 | Eval | luation of the area-efficient interconnect | 93     |

| 6.2.1 Wire model       94         6.2.2 Optimal repeater insertion       96         6.2.3 Driving transistor characterisation       97         6.2.4 Output buffer cascading factor       99         6.3 Simulation of correctness       100         6.3.1 Test results       100         6.4 Point-to-point link results       103         6.5 A loop oscillator       103         6.5.1 Additional repeater insertion       105         6.5.2 Comparison to published literature       107         6.6 Basic link evaluation       114         6.7 Pulse widths       114         6.8 Voltage swing       119         6.8.1 Crostalk       120         6.8.2 Reflections and ringing       122         6.8.3 Effects of inductance       123         6.9 Pulse generator design choice       123         6.10 Evaluation of the flop-based design       125         6.10.1 Immary of the flop-based design       126         6.12 Evaluation of the pulse-chopper based design       128         6.12 Evaluation of the flop-based design       131         6.12 Evaluation of the flop-based design       131         6.13 Repeater insertion with the chopper-based link       134         6.13.1 Latency       131                                         |   | 6.1  | Introduction                               | 93     |

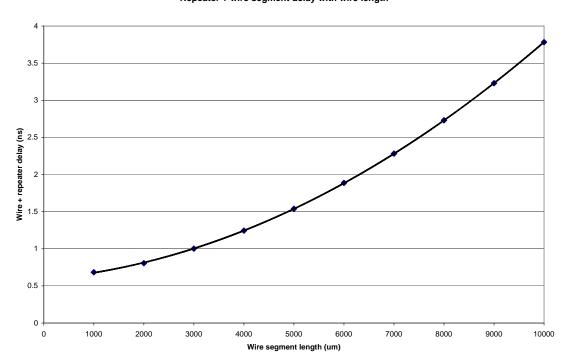

| 6.2.2 Optimal repeater insertion       96         6.2.3 Driving transistor characterisation       97         6.2.4 Output buffer cascading factor       99         6.3 Simulation of correctness       100         6.3.1 Test results       100         6.4 Point-to-point link results       103         6.5 A loop oscillator       103         6.5.1 Additional repeater insertion       105         6.5.2 Comparison to published literature       107         6.6 Basic link evaluation       114         6.7 Pulse widths       114         6.8 Voltage swing       119         6.8.1 Crosstalk       120         6.8.2 Reflections and ringing       122         6.8.3 Effects of inductance       123         6.10 Evaluation of the flop-based design       125         6.10.1 Throughput       126         6.10.2 Latency       127         6.10.3 Energy use       127         6.11 Summary of the flop-based design       131         6.12.2 Throughput       131         6.13.1 Latency       131         6.13.2 Throughput       131         6.13.3 Repeater logic delay       135         6.13.4 Energy       137         6.13.5 Energy use breakdown                                                                                            |   | 6.2  | Methodology                                | 93     |

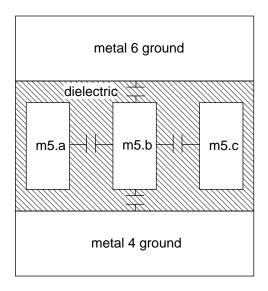

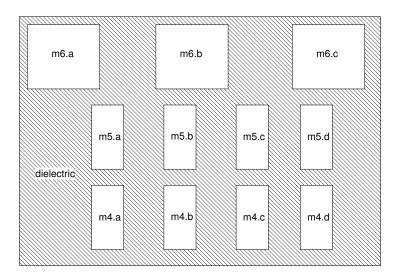

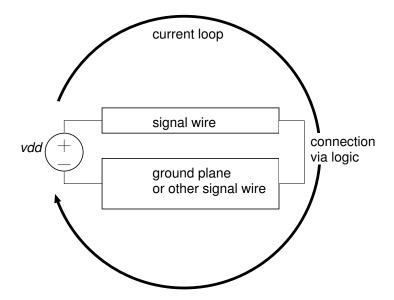

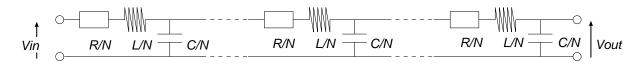

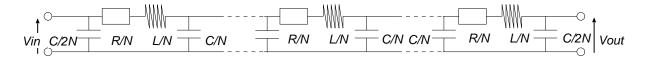

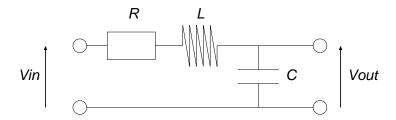

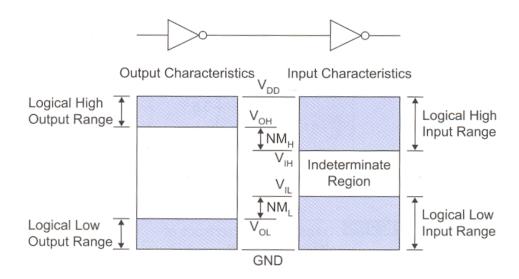

| 6.2.3 Driving transistor characterisation       97         6.2.4 Output buffer cascading factor       99         6.3 Simulation of correctness       100         6.4 Point-to-point link results       103         6.5 A loop oscillator       103         6.5.1 Additional repeater insertion       105         6.5.2 Comparison to published literature       107         6.6 Basic link evaluation       114         6.7 Pulse widths       114         6.8 Voltage swing       119         6.8.1 Crosstalk       120         6.8.2 Reflections and ringing       122         6.8.3 Effects of inductance       123         6.9 Pulse generator design choice       123         6.10 Evaluation of the flop-based design       125         6.10.1 Throughput       126         6.10.2 Latency       127         6.10.3 Energy use       127         6.11 Summary of the flop-based design       128         6.12 Evaluation of the pulse-chopper based design       131         6.12.1 Latency       131         6.13.2 Throughput       131         6.13.1 Eatency       134         6.13.2 Throughput       135         6.13.4 Energy       135         6.13.5 Energy use break                                                                            |   |      | 6.2.1 Wire model                           | 94     |

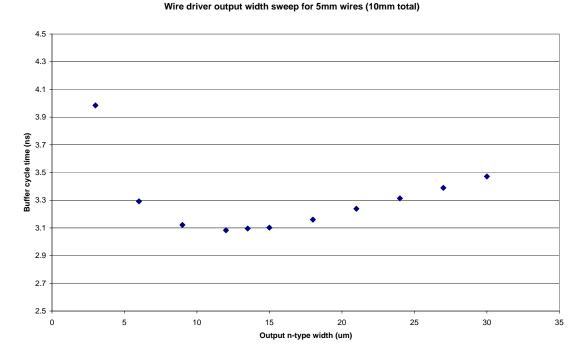

| 6.2.4 Output buffer cascading factor       99         6.3 Simulation of correctness       100         6.3.1 Test results       100         6.4 Point-to-point link results       103         6.5 A loop oscillator       103         6.5.1 Additional repeater insertion       105         6.5.2 Comparison to published literature       107         6.6 Basic link evaluation       114         6.7 Pulse widths       114         6.8 Voltage swing       119         6.8.1 Crosstalk       120         6.8.2 Reflections and ringing       122         6.8.3 Effects of inductance       123         6.9 Pulse generator design choice       123         6.10 Evaluation of the flop-based design       125         6.10.1 Throughput       126         6.10.2 Latency       127         6.10.3 Energy use       127         6.11 Summary of the flop-based design       128         6.12 Evaluation of the pulse-chopper based design       131         6.12.1 Latency       131         6.12.2 Throughput       131         6.13.3 Repeater insertion with the chopper-based link       134         6.13.1 Latency       134         6.13.2 Energy use breakdown       135                                                                                |   |      | 6.2.2 Optimal repeater insertion           | 96     |

| 6.3. Simulation of correctness       100         6.3.1 Test results       100         6.4 Point-to-point link results       103         6.5 A loop oscillator       103         6.5.1 Additional repeater insertion       105         6.5.2 Comparison to published literature       107         6.6 Basic link evaluation       114         6.7 Pulse widths       114         6.8 Voltage swing       119         6.8.1 Crosstalk       120         6.8.2 Reflections and ringing       122         6.8.3 Effects of inductance       123         6.9 Pulse generator design choice       123         6.10 Evaluation of the flop-based design       125         6.10.1 Throughput       126         6.10.2 Latency       127         6.10 Senergy use       127         6.11 Summary of the flop-based design       128         6.12 Evaluation of the pulse-chopper based design       131         6.12.2 Throughput       131         6.13.1 Latency       131         6.13.2 Throughput       135         6.13.3 Repeater insertion with the chopper-based link       134         6.13.5 Energy use breakdown       135         6.13.6 Repeater energies       140         6.1                                                                            |   |      | 6.2.3 Driving transistor characterisation  | 97     |

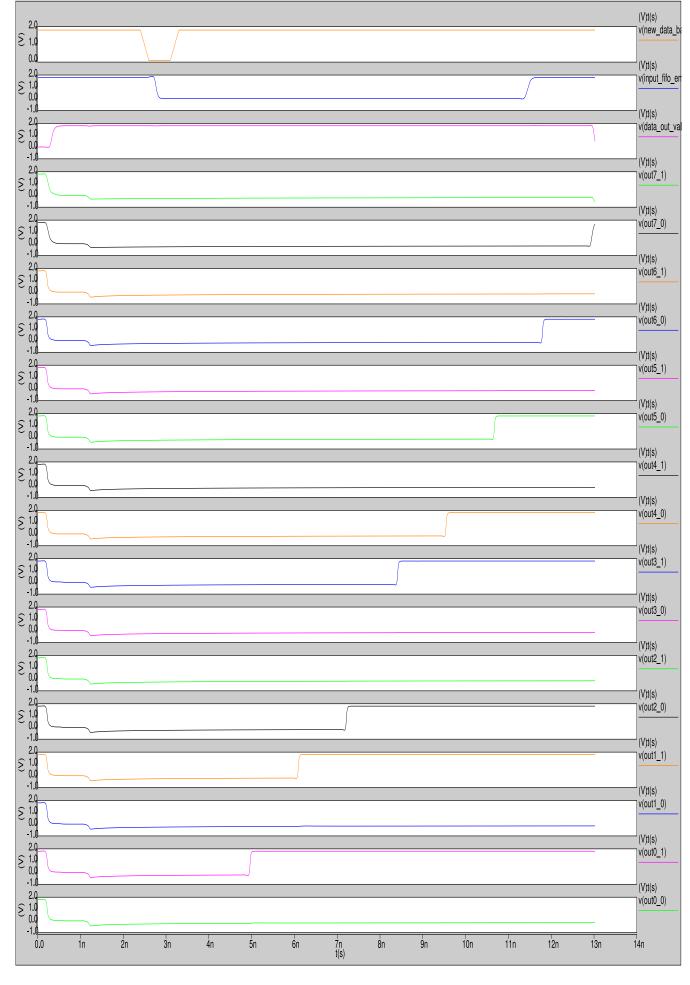

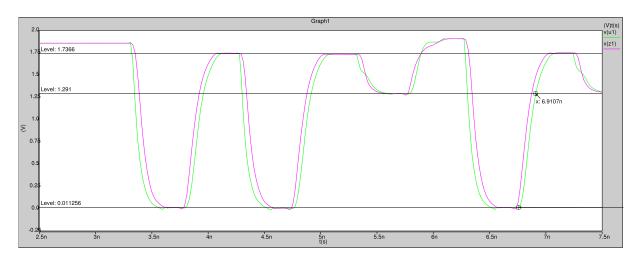

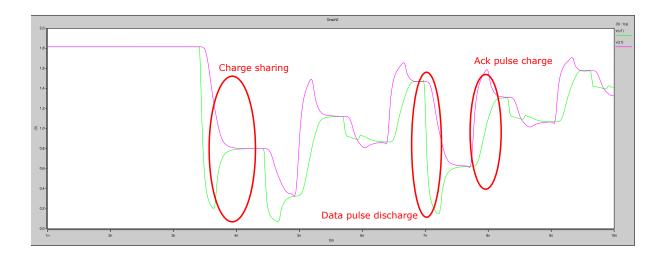

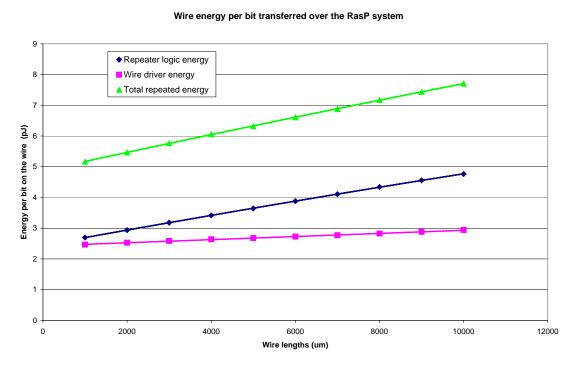

| 6.3.1 Test results       100         6.4 Point-to-point link results       103         6.5 A loop oscillator       103         6.5.1 Additional repeater insertion       105         6.5.2 Comparison to published literature       107         6.6 Basic link evaluation       114         6.7 Pulse widths       114         6.8 Voltage swing       119         6.8.1 Crosstalk       120         6.8.2 Reflections and ringing       122         6.8.2 Reflects of inductance       123         6.9 Pulse generator design choice       123         6.10 Evaluation of the flop-based design       125         6.10.1 Throughput       126         6.10.2 Latency       127         6.10.3 Energy use       127         6.11 Summary of the flop-based design       128         6.12 Evaluation of the pulse-chopper based design       131         6.12.1 Latency       131         6.13.2 Throughput       131         6.13.3 Repeater insertion with the chopper-based link       134         6.13.1 Latency       134         6.13.2 Throughput       135         6.13.4 Energy       135         6.13.5 Energy use breakdown       137         6.13.6 Repeater energies <td></td> <td></td> <td>6.2.4 Output buffer cascading factor</td> <td> 99</td> |   |      | 6.2.4 Output buffer cascading factor       | 99     |

| 6.4 Point-to-point link results       103         6.5 A loop oscillator       103         6.5.1 Additional repeater insertion       105         6.5.2 Comparison to published literature       107         6.6 Basic link evaluation       114         6.7 Pulse widths       114         6.8 Voltage swing       119         6.8.1 Crosstalk       120         6.8.2 Reflections and ringing       122         6.8.3 Effects of inductance       123         6.9 Pulse generator design choice       123         6.10 Evaluation of the flop-based design       125         6.10.1 Throughput       126         6.10.2 Latency       127         6.10.3 Energy use       127         6.11 Summary of the flop-based design       128         6.12.1 Latency       131         6.12.2 Throughput       131         6.13 Repeater insertion with the chopper-based link       134         6.13.1 Latency       134         6.13.2 Throughput       135         6.13.4 Energy       135         6.13.5 Energy use breakdown       137         6.13.6 Repeater energies       140         6.13.7 Logic delays       141         6.16 Omparison to other interconnect designs                                                                                       |   | 6.3  | Simulation of correctness                  | 100    |

| 6.5 A loop oscillator       103         6.5.1 Additional repeater insertion       105         6.5.2 Comparison to published literature       107         6.6 Basic link evaluation       114         6.7 Pulse widths       114         6.8 Voltage swing       119         6.8.1 Crosstalk       120         6.8.2 Reflections and ringing       122         6.8.3 Effects of inductance       123         6.9 Pulse generator design choice       123         6.10 Evaluation of the flop-based design       125         6.10.1 Throughput       126         6.10.2 Latency       127         6.10.3 Energy use       127         6.11 Summary of the flop-based design       128         6.12 Evaluation of the pulse-chopper based design       131         6.12 Evaluation of the pulse-chopper based design       131         6.12.1 Latency       131         6.12.2 Throughput       131         6.13 Repeater insertion with the chopper-based link       134         6.13.1 Energy       135         6.13.2 Energy use breakdown       135         6.13.5 Energy use breakdown       137         6.13.6 Repeater energies       140         6.15.7 Theoretical analysis of interconnect efficiency                                                    |   |      | 6.3.1 Test results                         | 100    |

| 6.5.1 Additional repeater insertion       105         6.5.2 Comparison to published literature       107         6.6 Basic link evaluation       114         6.7 Pulse widths       114         6.8 Voltage swing       119         6.8.1 Crosstalk       120         6.8.2 Reflections and ringing       122         6.8.3 Effects of inductance       123         6.9 Pulse generator design choice       123         6.10 Evaluation of the flop-based design       125         6.10.1 Throughput       126         6.10.2 Latency       127         6.10.3 Energy use       127         6.11 Summary of the flop-based design       131         6.12 Evaluation of the pulse-chopper based design       131         6.12.1 Latency       131         6.12.2 Throughput       131         6.13 Repeater insertion with the chopper-based link       134         6.13.1 Latency       134         6.13.2 Energy use breakdown       135         6.13.4 Energy       137         6.13.6 Repeater energies       140         6.13.7 Logic delays       141         6.14 Area       143         6.16.1 Parallel wires       147                                                                                                                                  |   | 6.4  | Point-to-point link results                | 103    |

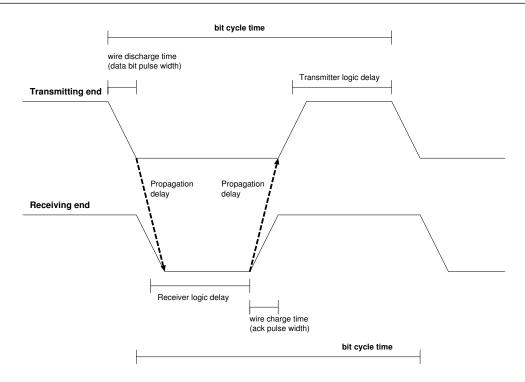

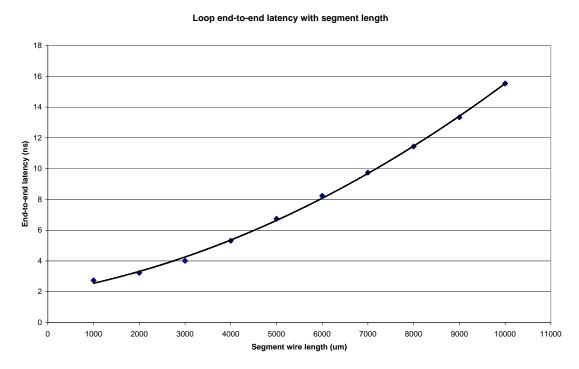

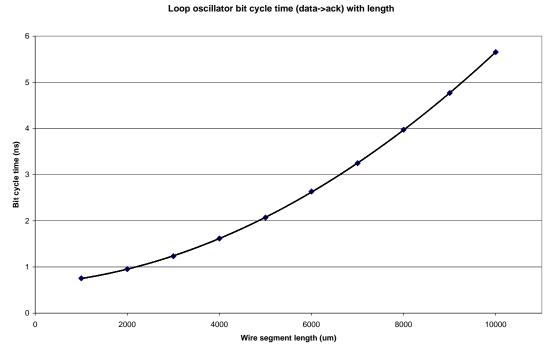

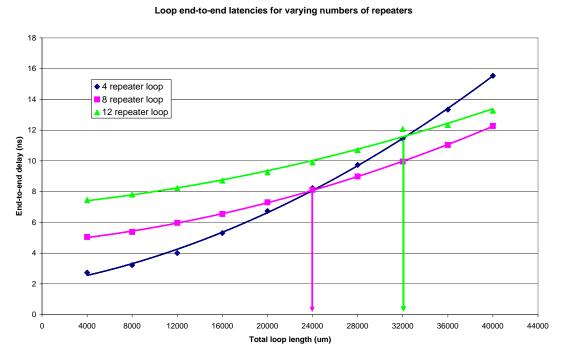

| 6.5.2 Comparison to published literature       107         6.6 Basic link evaluation       114         6.7 Pulse widths       114         6.8 Voltage swing       119         6.8.1 Crosstalk       120         6.8.2 Reflections and ringing       122         6.8.3 Effects of inductance       123         6.9 Pulse generator design choice       123         6.10 Evaluation of the flop-based design       125         6.10.1 Throughput       126         6.10.2 Latency       127         6.10.3 Energy use       127         6.11 Summary of the flop-based design       128         6.12 Evaluation of the pulse-chopper based design       131         6.12.1 Throughput       131         6.13 Repeater insertion with the chopper-based link       134         6.13.1 Latency       134         6.13.2 Throughput       135         6.13.4 Energy       137         6.13.5 Energy use breakdown       137         6.13.6 Repeater energies       140         6.14 Area       143         6.15 Theoretical analysis of interconnect efficiency       144         6.16 Comparison to other interconnect designs       147         6.16.1 Parallel wires       147 <td></td> <td>6.5</td> <td>A loop oscillator</td> <td>103</td>                     |   | 6.5  | A loop oscillator                          | 103    |

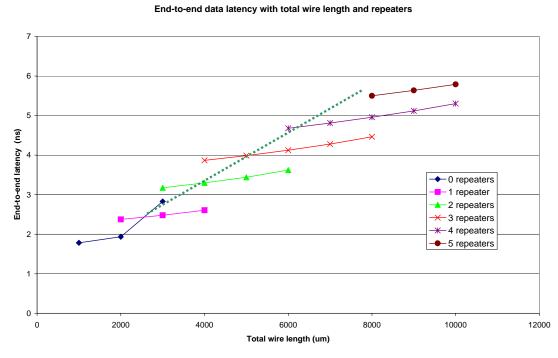

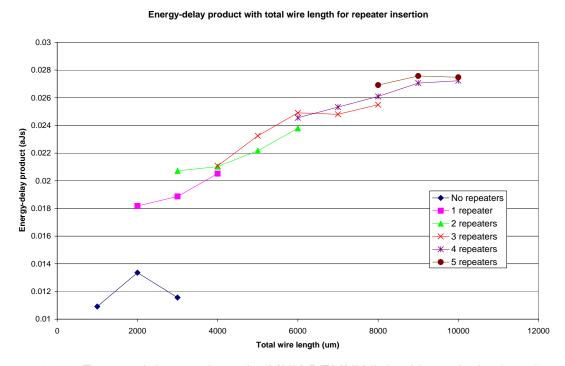

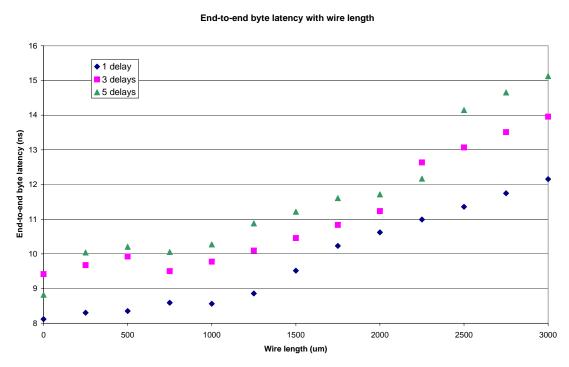

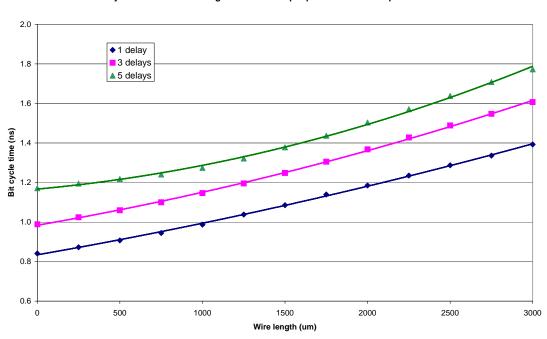

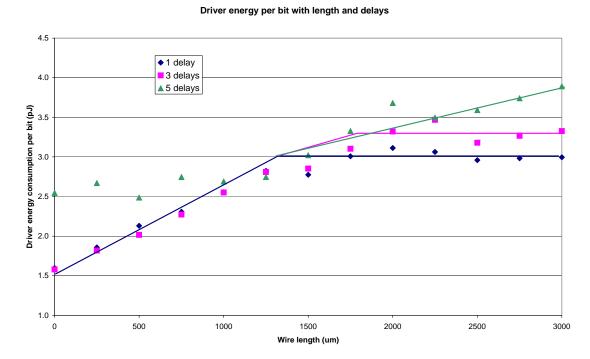

| 6.6       Basic link evaluation       114         6.7       Pulse widths       114         6.8       Voltage swing       119         6.8.1       Crosstalk       120         6.8.2       Reflections and ringing       122         6.8.3       Effects of inductance       123         6.9       Pulse generator design choice       123         6.10       Evaluation of the flop-based design       125         6.10.1       Throughput       126         6.10.2       Latency       127         6.10.3       Energy use       127         6.11       Summary of the flop-based design       128         6.12       Evaluation of the pulse-chopper based design       131         6.12       Evaluation of the pulse-chopper based design       131         6.12       Throughput       131         6.13       Repeater insertion with the chopper-based link       134         6.13.1       Latency       134         6.13.2       Throughput       135         6.13.3       Repeater logic delay       135         6.13.4       Energy       137         6.13.5       Energy use breakdown       137         6.13.6                                                                                                                                        |   |      | 6.5.1 Additional repeater insertion        | 105    |

| 6.7 Pulse widths       114         6.8 Voltage swing       119         6.8.1 Crosstalk       120         6.8.2 Reflections and ringing       122         6.8.3 Effects of inductance       123         6.9 Pulse generator design choice       123         6.10 Evaluation of the flop-based design       125         6.10.1 Throughput       126         6.10.2 Latency       127         6.10 Senergy use       127         6.11 Summary of the flop-based design       128         6.12 Evaluation of the pulse-chopper based design       131         6.12.1 Latency       131         6.13.2 Repeater insertion with the chopper-based link       134         6.13.1 Latency       134         6.13.2 Throughput       135         6.13.4 Energy       135         6.13.5 Energy use breakdown       137         6.13.6 Repeater energies       140         6.13.7 Logic delays       141         6.14 Area       143         6.15 Theoretical analysis of interconnect efficiency       144         6.16 Comparison to other interconnect designs       147         6.16.1 Parallel wires       147                                                                                                                                                       |   |      | 6.5.2 Comparison to published literature   | 107    |

| 6.8 Voltage swing       119         6.8.1 Crosstalk       120         6.8.2 Reflections and ringing       122         6.8.3 Effects of inductance       123         6.9 Pulse generator design choice       123         6.10 Evaluation of the flop-based design       125         6.10.1 Throughput       126         6.10.2 Latency       127         6.10 Summary of the flop-based design       128         6.12 Evaluation of the pulse-chopper based design       131         6.12.1 Latency       131         6.12.2 Throughput       131         6.13 Repeater insertion with the chopper-based link       134         6.13.1 Latency       134         6.13.2 Throughput       135         6.13.4 Energy       135         6.13.5 Energy use breakdown       137         6.13.6 Repeater energies       140         6.13.7 Logic delays       141         6.14 Area       143         6.15 Theoretical analysis of interconnect efficiency       144         6.16 Comparison to other interconnect designs       147         6.16.1 Parallel wires       147                                                                                                                                                                                           |   | 6.6  | Basic link evaluation                      | 114    |

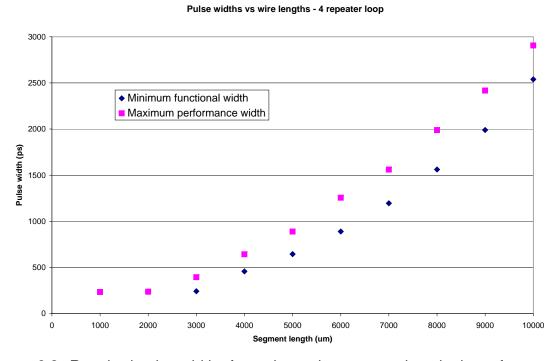

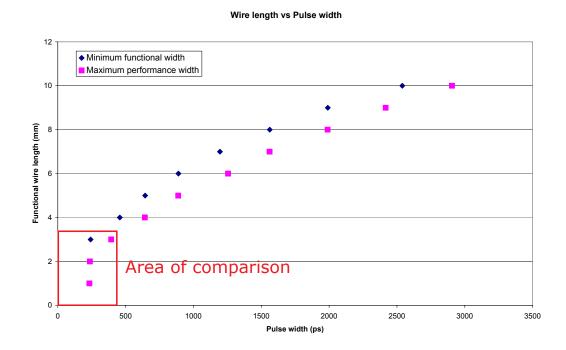

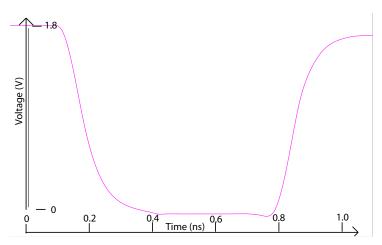

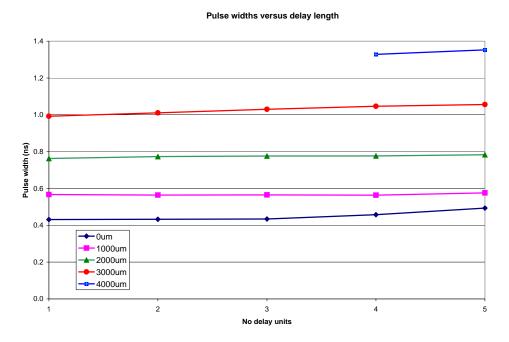

| 6.8.1 Crosstalk       120         6.8.2 Reflections and ringing       122         6.8.3 Effects of inductance       123         6.9 Pulse generator design choice       123         6.10 Evaluation of the flop-based design       125         6.10 I Throughput       126         6.10.2 Latency       127         6.10.3 Energy use       127         6.11 Summary of the flop-based design       128         6.12 Evaluation of the pulse-chopper based design       131         6.12.1 Latency       131         6.12.2 Throughput       131         6.13.1 Latency       134         6.13.2 Throughput       135         6.13.3 Repeater logic delay       135         6.13.4 Energy       135         6.13.5 Energy use breakdown       137         6.13.6 Repeater energies       140         6.13.7 Logic delays       141         6.14 Area       143         6.15 Theoretical analysis of interconnect efficiency       144         6.16 Comparison to other interconnect designs       147         6.16.1 Parallel wires       147                                                                                                                                                                                                                   |   | 6.7  | Pulse widths                               | 114    |

| 6.8.2 Reflections and ringing       122         6.8.3 Effects of inductance       123         6.9 Pulse generator design choice       123         6.10 Evaluation of the flop-based design       125         6.10.1 Throughput       126         6.10.2 Latency       127         6.10.3 Energy use       127         6.11 Summary of the flop-based design       128         6.12 Evaluation of the pulse-chopper based design       131         6.12.1 Latency       131         6.12.2 Throughput       131         6.13 Repeater insertion with the chopper-based link       134         6.13.1 Latency       134         6.13.2 Throughput       135         6.13.3 Repeater logic delay       135         6.13.4 Energy       137         6.13.5 Energy use breakdown       137         6.13.6 Repeater energies       140         6.13.7 Logic delays       141         6.14 Area       143         6.15 Theoretical analysis of interconnect efficiency       144         6.16 Comparison to other interconnect designs       147         6.16.1 Parallel wires       147                                                                                                                                                                               |   | 6.8  | Voltage swing                              | 119    |

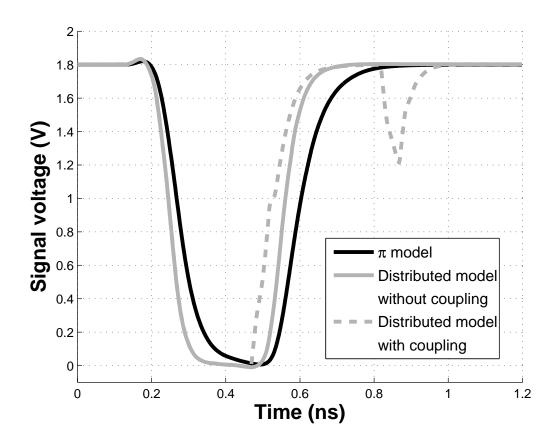

| 6.8.3 Effects of inductance       123         6.9 Pulse generator design choice       123         6.10 Evaluation of the flop-based design       125         6.10.1 Throughput       126         6.10.2 Latency       127         6.10.3 Energy use       127         6.11 Summary of the flop-based design       128         6.12 Evaluation of the pulse-chopper based design       131         6.12.1 Latency       131         6.12.2 Throughput       131         6.13 Repeater insertion with the chopper-based link       134         6.13.1 Latency       134         6.13.2 Throughput       135         6.13.3 Repeater logic delay       135         6.13.4 Energy       137         6.13.5 Energy use breakdown       137         6.13.6 Repeater energies       140         6.13.7 Logic delays       141         6.14 Area       143         6.15 Theoretical analysis of interconnect efficiency       144         6.16 Comparison to other interconnect designs       147         6.16.1 Parallel wires       147                                                                                                                                                                                                                               |   |      |                                            |        |

| 6.9 Pulse generator design choice       123         6.10 Evaluation of the flop-based design       125         6.10.1 Throughput       126         6.10.2 Latency       127         6.10.3 Energy use       127         6.11 Summary of the flop-based design       128         6.12 Evaluation of the pulse-chopper based design       131         6.12.1 Latency       131         6.12.2 Throughput       131         6.13 Repeater insertion with the chopper-based link       134         6.13.1 Latency       134         6.13.2 Throughput       135         6.13.3 Repeater logic delay       135         6.13.4 Energy       137         6.13.5 Energy use breakdown       137         6.13.6 Repeater energies       140         6.13.7 Logic delays       141         6.14 Area       143         6.15 Theoretical analysis of interconnect efficiency       144         6.16 Comparison to other interconnect designs       147         6.16.1 Parallel wires       147                                                                                                                                                                                                                                                                             |   |      |                                            |        |

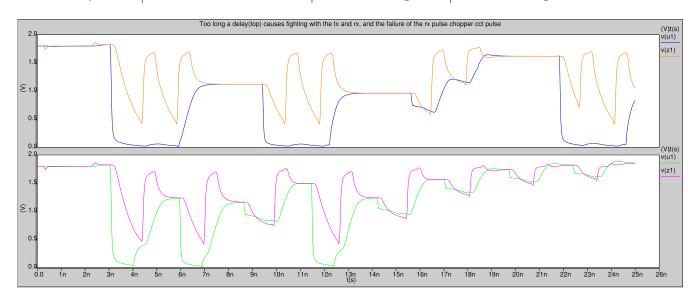

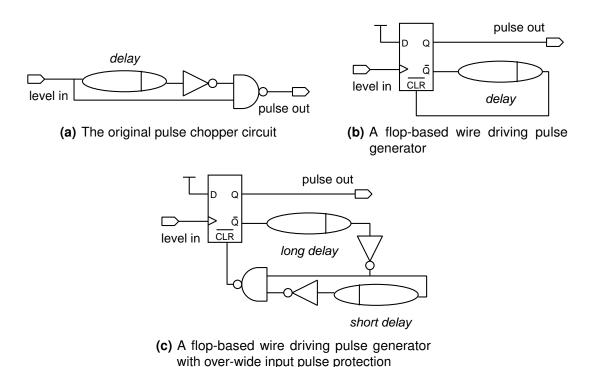

| 6.10 Evaluation of the flop-based design       125         6.10.1 Throughput       126         6.10.2 Latency       127         6.10.3 Energy use       127         6.11 Summary of the flop-based design       128         6.12 Evaluation of the pulse-chopper based design       131         6.12.1 Latency       131         6.12.2 Throughput       131         6.13 Repeater insertion with the chopper-based link       134         6.13.1 Latency       134         6.13.2 Throughput       135         6.13.3 Repeater logic delay       135         6.13.4 Energy       137         6.13.5 Energy use breakdown       137         6.13.6 Repeater energies       140         6.13.7 Logic delays       141         6.14 Area       143         6.15 Theoretical analysis of interconnect efficiency       144         6.16 Comparison to other interconnect designs       147         6.16.1 Parallel wires       147                                                                                                                                                                                                                                                                                                                                 |   |      |                                            |        |

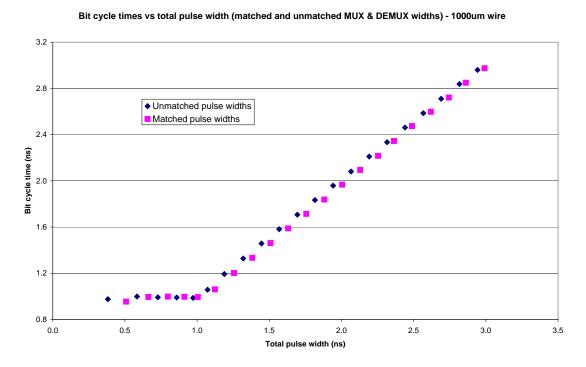

| 6.10.1 Throughput       126         6.10.2 Latency       127         6.10.3 Energy use       127         6.11 Summary of the flop-based design       128         6.12 Evaluation of the pulse-chopper based design       131         6.12.1 Latency       131         6.12.2 Throughput       131         6.13 Repeater insertion with the chopper-based link       134         6.13.1 Latency       134         6.13.2 Throughput       135         6.13.3 Repeater logic delay       135         6.13.4 Energy       137         6.13.5 Energy use breakdown       137         6.13.6 Repeater energies       140         6.13.7 Logic delays       141         6.14 Area       143         6.15 Theoretical analysis of interconnect efficiency       144         6.16 Comparison to other interconnect designs       147         6.16.1 Parallel wires       147                                                                                                                                                                                                                                                                                                                                                                                            |   |      |                                            |        |

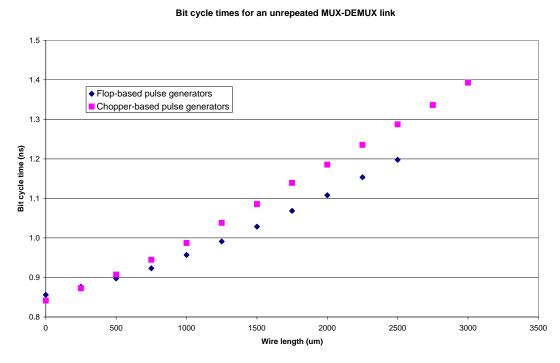

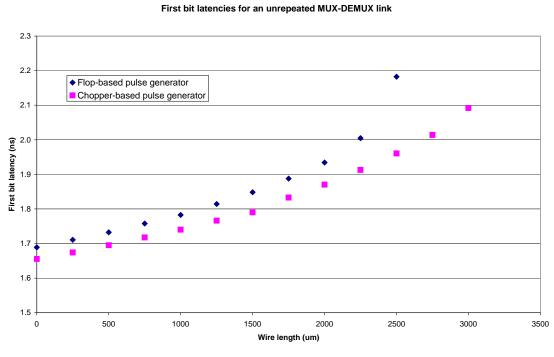

| 6.10.2 Latency       127         6.10.3 Energy use       127         6.11 Summary of the flop-based design       128         6.12 Evaluation of the pulse-chopper based design       131         6.12.1 Latency       131         6.12.2 Throughput       131         6.13 Repeater insertion with the chopper-based link       134         6.13.1 Latency       134         6.13.2 Throughput       135         6.13.3 Repeater logic delay       135         6.13.4 Energy       137         6.13.5 Energy use breakdown       137         6.13.6 Repeater energies       140         6.13.7 Logic delays       141         6.14 Area       143         6.15 Theoretical analysis of interconnect efficiency       144         6.16 Comparison to other interconnect designs       147         6.16.1 Parallel wires       147                                                                                                                                                                                                                                                                                                                                                                                                                                |   | 6.10 |                                            |        |

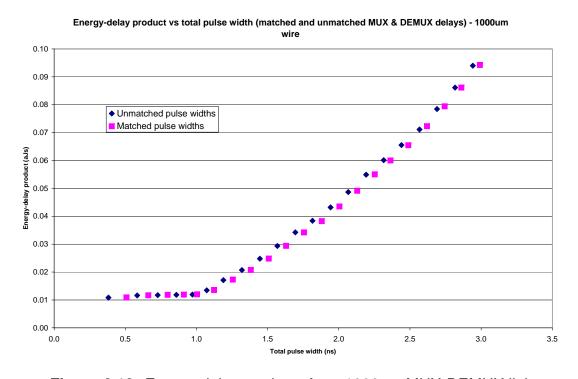

| 6.10.3 Energy use       127         6.11 Summary of the flop-based design       128         6.12 Evaluation of the pulse-chopper based design       131         6.12.1 Latency       131         6.12.2 Throughput       131         6.13 Repeater insertion with the chopper-based link       134         6.13.1 Latency       134         6.13.2 Throughput       135         6.13.3 Repeater logic delay       135         6.13.4 Energy       137         6.13.5 Energy use breakdown       137         6.13.6 Repeater energies       140         6.13.7 Logic delays       141         6.14 Area       143         6.15 Theoretical analysis of interconnect efficiency       144         6.16 Comparison to other interconnect designs       147         6.16.1 Parallel wires       147                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |      | 0 1                                        |        |

| 6.11 Summary of the flop-based design       128         6.12 Evaluation of the pulse-chopper based design       131         6.12.1 Latency       131         6.12.2 Throughput       131         6.13 Repeater insertion with the chopper-based link       134         6.13.1 Latency       134         6.13.2 Throughput       135         6.13.3 Repeater logic delay       135         6.13.4 Energy       137         6.13.5 Energy use breakdown       137         6.13.6 Repeater energies       140         6.13.7 Logic delays       141         6.14 Area       143         6.15 Theoretical analysis of interconnect efficiency       144         6.16 Comparison to other interconnect designs       147         6.16.1 Parallel wires       147                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |      | •                                          |        |

| 6.12 Evaluation of the pulse-chopper based design       131         6.12.1 Latency       131         6.12.2 Throughput       131         6.13 Repeater insertion with the chopper-based link       134         6.13.1 Latency       134         6.13.2 Throughput       135         6.13.3 Repeater logic delay       135         6.13.4 Energy       137         6.13.5 Energy use breakdown       137         6.13.6 Repeater energies       140         6.13.7 Logic delays       141         6.14 Area       143         6.15 Theoretical analysis of interconnect efficiency       144         6.16 Comparison to other interconnect designs       147         6.16.1 Parallel wires       147                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |      |                                            |        |

| 6.12.1 Latency       131         6.12.2 Throughput       131         6.13 Repeater insertion with the chopper-based link       134         6.13.1 Latency       134         6.13.2 Throughput       135         6.13.3 Repeater logic delay       135         6.13.4 Energy       137         6.13.5 Energy use breakdown       137         6.13.6 Repeater energies       140         6.13.7 Logic delays       141         6.14 Area       143         6.15 Theoretical analysis of interconnect efficiency       144         6.16 Comparison to other interconnect designs       147         6.16.1 Parallel wires       147                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |      | , ,                                        |        |

| 6.12.2 Throughput       131         6.13 Repeater insertion with the chopper-based link       134         6.13.1 Latency       134         6.13.2 Throughput       135         6.13.3 Repeater logic delay       135         6.13.4 Energy       137         6.13.5 Energy use breakdown       137         6.13.6 Repeater energies       140         6.13.7 Logic delays       141         6.14 Area       143         6.15 Theoretical analysis of interconnect efficiency       144         6.16 Comparison to other interconnect designs       147         6.16.1 Parallel wires       147                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   | 6.12 |                                            |        |

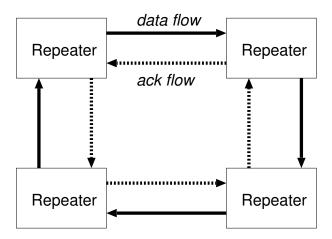

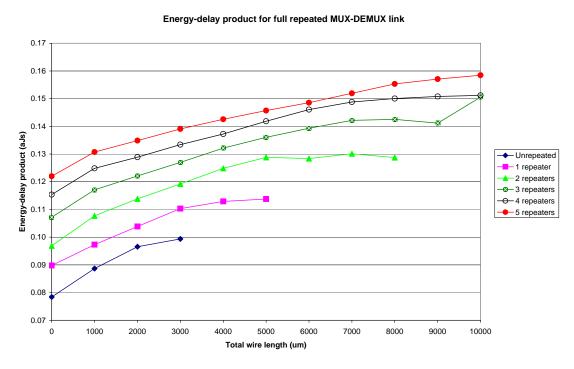

| 6.13 Repeater insertion with the chopper-based link       134         6.13.1 Latency       134         6.13.2 Throughput       135         6.13.3 Repeater logic delay       135         6.13.4 Energy       137         6.13.5 Energy use breakdown       137         6.13.6 Repeater energies       140         6.13.7 Logic delays       141         6.14 Area       143         6.15 Theoretical analysis of interconnect efficiency       144         6.16 Comparison to other interconnect designs       147         6.16.1 Parallel wires       147                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |      |                                            |        |

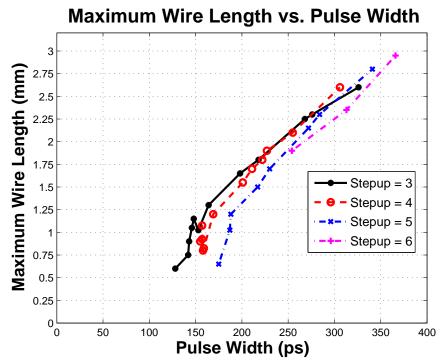

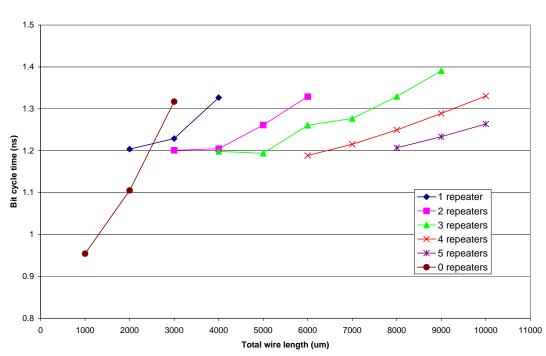

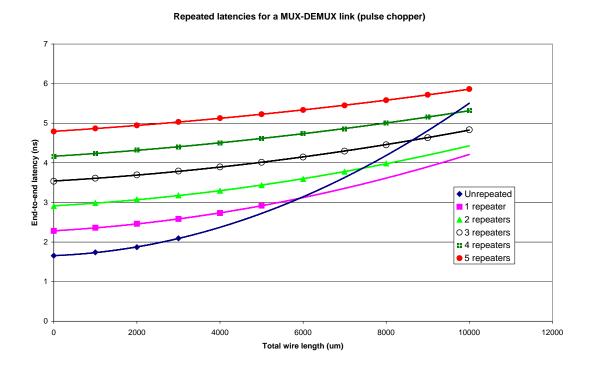

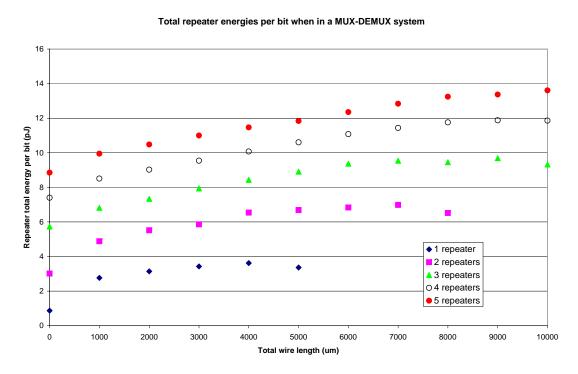

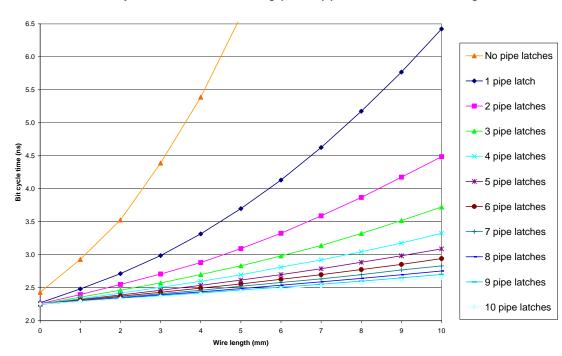

| 6.13.1 Latency       134         6.13.2 Throughput       135         6.13.3 Repeater logic delay       135         6.13.4 Energy       137         6.13.5 Energy use breakdown       137         6.13.6 Repeater energies       140         6.13.7 Logic delays       141         6.14 Area       143         6.15 Theoretical analysis of interconnect efficiency       144         6.16 Comparison to other interconnect designs       147         6.16.1 Parallel wires       147                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   | C 10 | 0 1                                        |        |

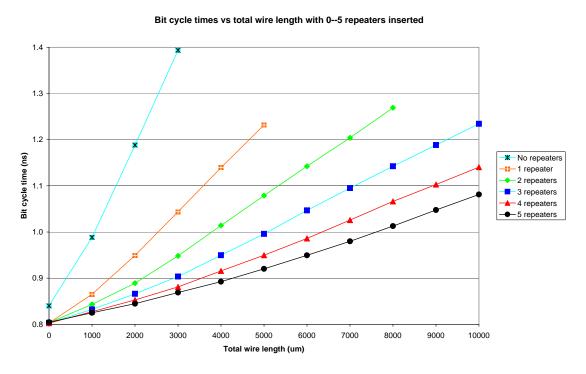

| 6.13.2 Throughput       135         6.13.3 Repeater logic delay       135         6.13.4 Energy       137         6.13.5 Energy use breakdown       137         6.13.6 Repeater energies       140         6.13.7 Logic delays       141         6.14 Area       143         6.15 Theoretical analysis of interconnect efficiency       144         6.16 Comparison to other interconnect designs       147         6.16.1 Parallel wires       147                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | 6.13 |                                            |        |

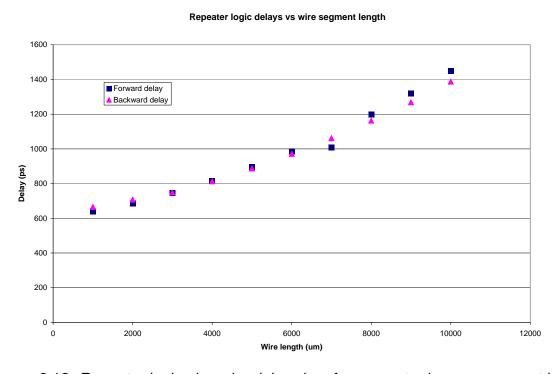

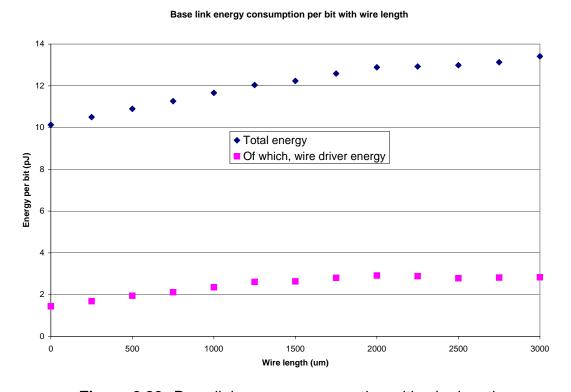

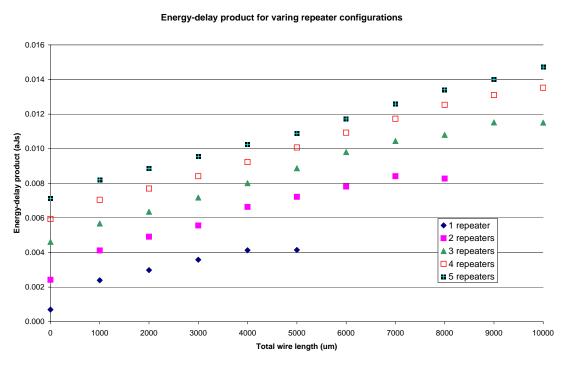

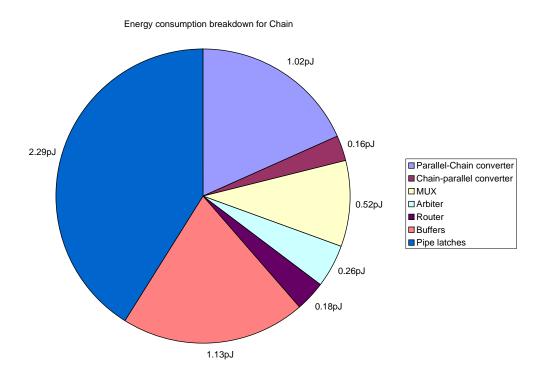

| 6.13.3 Repeater logic delay       135         6.13.4 Energy       137         6.13.5 Energy use breakdown       137         6.13.6 Repeater energies       140         6.13.7 Logic delays       141         6.14 Area       143         6.15 Theoretical analysis of interconnect efficiency       144         6.16 Comparison to other interconnect designs       147         6.16.1 Parallel wires       147                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |      | ·                                          |        |