Technical Report

Number 682

**Computer Laboratory**

# Translating HOL functions to hardware

Juliano Iyoda

April 2007

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500

http://www.cl.cam.ac.uk/

### © 2007 Juliano Iyoda

This technical report is based on a dissertation submitted October 2006 by the author for the degree of Doctor of Philosophy to the University of Cambridge, Hughes Hall.

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

http://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986

# Translating HOL functions to hardware

Juliano Iyoda

#### Abstract

Delivering error-free products is still a major challenge for hardware and software engineers. Due to the increasingly growing complexity of computing systems, there is a demand for higher levels of automation in formal verification.

This dissertation proposes an approach to generate formally verified circuits automatically. The main outcome of our project is a compiler implemented on top of the theorem prover HOL4 which translates a subset of higher-order logic to circuits. The subset of the logic is a first-order tail-recursive functional language. The compiler takes a function fas argument and automatically produces the theorem

#### $\vdash$ C implements f

where C is a circuit and *implements* is a correctness relation between a circuit and a function. We achieve full mechanisation of proofs by defining theorems which are composable. The correctness of a circuit can be mechanically determined by the correctness of its sub-circuits. This technology allows the designer to focus on higher levels of abstraction instead of reasoning and verifying systems at the gate level.

A pretty-printer translates netlists described in higher-order logic to structural Verilog. Our compiler is integrated with Altera tools to run our circuits in FPGAs. Thus the theorem prover is used as an environment for supporting the development process from formal specification to implementation.

Our approach has been tested with fairly substantial case studies. We describe the design and the verification of a multiplier and a simple microcomputer which has shown us that the compiler supports small and medium-sized applications. Although this approach does not scale to industrial-sized applications yet, it is a first step towards the implementation of a new technology that can raise the level of mechanisation in formal verification.

# Acknowledgements

First I want to thank my supervisor Mike Gordon. He was always available to listen and to help. His constant enthusiasm, inspiring advices and encouragement guided me gently towards the conclusion of this dissertation. In particular, his motivation and expertise in HOL helped me to program parts of the compiler faster than I thought possible.

The ARG members have always helped me with whatever problem I had. Special thanks go to Joe Hurd and my office mates Anthony Fox and Hasan Amjad, who have always kindly helped me in my work.

Thanks to Robert Mullins and Simon Moore for helping me in integrating FPGAs and Quartus II with Linux. David Greaves provided me insightful comments on hardware design. Ken Friis Larsen integrated my UART program in C with Moscow ML. Konrad Slind and Scott Owens have been great colleagues who supported this project with enthusiasm and contributed with significant improvements to the compiler.

The good people of the then Portuguese Society introduced me to their culture in their unique entertaining way. It was a pleasure to later join the committee presided by Eliana Lucas.

Thanks to those who changed my life in Cambridge. I couldn't have asked for better friends: Carol Anselmo, Pedro Anselmo Filho, Clint Ballinger, Ronaldo Batista, Marco Cariglia, Raquel Costa, Val Feltrim, Liliana Ferreira, Carol Gasperin, Rodrigo Gribel, Carlos Hotta, Paul Hunter, Daniel Maciel, Ricardo Mendes, Antônio Moura, Chico Prosdocimi, Isabel Ribeiro, Leda Sampson, João Pedro dos Santos, André Sartori, Paula Signorini, Yuri Sobral and Cris Viegas.

Augusto Sampaio was my supervisor during my Masters and has always been a good friend and a true mentor. His constant advice and help in my professional career influenced my decision to come to Cambridge.

My PhD has been financially supported by the CAPES Institute (a foundation attached to the Brazilian Ministry of Education).

And, finally, thanks to my parents for all the support, patience and love.

# Contents

| 1        | Intr                 | roduction 7                                                                                                                                               |

|----------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1.1                  | Mechanised Verification                                                                                                                                   |

|          | 1.2                  | Contributions                                                                                                                                             |

|          | 1.3                  | The structure of this dissertation                                                                                                                        |

| <b>2</b> | Cor                  | npilation 11                                                                                                                                              |

|          | 2.1                  | Introduction                                                                                                                                              |

|          | 2.2                  | A Brief Introduction to HOL                                                                                                                               |

|          | 2.3                  | Hardware Verification in HOL                                                                                                                              |

|          |                      | 2.3.1 Verification $\ldots \ldots \ldots$ |

|          | 2.4                  | Compilation-by-proof in HOL                                                                                                                               |

|          |                      | 2.4.1 The Source Language                                                                                                                                 |

|          |                      | 2.4.2 The Specification                                                                                                                                   |

|          |                      | 2.4.3 Automatic Verification                                                                                                                              |

|          |                      | 2.4.4 The Implementation                                                                                                                                  |

|          | 2.5                  | Summary                                                                                                                                                   |

| 3        | Ont                  | timisations and Synthesis 29                                                                                                                              |

| 0        | 3.1                  | Optimisations                                                                                                                                             |

|          | 3.2                  | Clock Introduction                                                                                                                                        |

|          | 3.3                  | Translating HOL Circuits to Verilog                                                                                                                       |

|          | 3.4                  | A Simple Example                                                                                                                                          |

|          | 3.5                  | Summary                                                                                                                                                   |

| 4        | т:                   | itations and Dashland 40                                                                                                                                  |

| 4        |                      | aitations and Problems       40         Atomic Circuits Not Verified       40                                                                             |

|          | 4.1                  |                                                                                                                                                           |

|          | 4.2                  | Combinational Loops                                                                                                                                       |

|          | 4.3                  | Proof Effort                                                                                                                                              |

|          | 4.4                  | Undefined Values                                                                                                                                          |

|          | 4.5                  | Industrial-scale Specifications                                                                                                                           |

|          | 4.6                  | Summary                                                                                                                                                   |

| <b>5</b> | $\operatorname{Cas}$ | e Studies 46                                                                                                                                              |

|          | 5.1                  | Booth Multiplier                                                                                                                                          |

|          |                      | 5.1.1 The Compilation $\ldots \ldots 47$                                                   |

|          | 5.2                  | The DIY Microcomputer                                                                                                                                     |

|          |                      | 5.2.1 The CPU Design                                                                                                                                      |

|              |                 | 5.2.2 The Microcomputer Design | 54 |  |  |  |

|--------------|-----------------|--------------------------------|----|--|--|--|

|              | 5.3             | Result Analysis                | 56 |  |  |  |

| 6            | Rela            | ated Work                      | 60 |  |  |  |

|              | 6.1             | LAMBDA                         | 60 |  |  |  |

|              | 6.2             | VERITAS <sup>+</sup>           | 60 |  |  |  |

|              | 6.3             | DDD                            | 60 |  |  |  |

|              | 6.4             | Gropius                        | 61 |  |  |  |

|              | 6.5             | Occam Synthesis                | 61 |  |  |  |

|              | 6.6             | Ruby                           | 62 |  |  |  |

|              | 6.7             | Functional Languages           | 62 |  |  |  |

|              |                 | 6.7.1 $\mu$ FP                 | 62 |  |  |  |

|              |                 | 6.7.2 Lava                     | 63 |  |  |  |

|              |                 | 6.7.3 Lustre                   | 63 |  |  |  |

|              |                 | 6.7.4 Hydra                    | 64 |  |  |  |

|              |                 | 6.7.5 Hawk                     | 64 |  |  |  |

|              |                 | 6.7.6 ReFLect                  | 65 |  |  |  |

|              |                 | 6.7.7 SAFL                     | 65 |  |  |  |

|              |                 | 6.7.8 SASL                     | 65 |  |  |  |

|              |                 | 6.7.9 SHard                    | 65 |  |  |  |

|              | 6.8             | Comparative Analysis           | 66 |  |  |  |

|              |                 | 6.8.1 Summary                  | 67 |  |  |  |

| 7            | Con             | clusion                        | 69 |  |  |  |

|              | 7.1             | Lessons Learnt                 | 69 |  |  |  |

|              | 7.2             | Final Remarks                  | 70 |  |  |  |

| $\mathbf{A}$ | The             | DIY Specifications             | 71 |  |  |  |

|              | A.1             | The CPU Design                 | 71 |  |  |  |

|              | A.2             | -                              | 78 |  |  |  |

| Bi           | Bibliography 83 |                                |    |  |  |  |

# Chapter 1 Introduction

The development of reliable systems is still a challenge to hardware and software engineers. Computing systems are increasingly growing in complexity and size, which makes subtle errors more likely to appear. Uncovered bugs in the development phase can cause severe loss of money or, in safety-critical applications, even human life. According to Wired News website, among the History's Worst Bugs are the Intel Pentium floating point division and the Ariane 5 Flight 501 [25]. These failures are estimated to have cost around half a billion US dollars each. Although there is no definitive solution to this problem, *formal methods* is the most rigorous set of techniques which provides high assurance of correctness.

Formal methods refers to techniques and tools based on mathematical logic which ensure the quality and the correctness of a design by representing specifications and implementations in a particular logical system. *Formal verification* is a rigorous deduction in the logic (a theorem) which shows that an implementation meets the specification. *Theorem provers* are software tools which mechanise a logical system and automate (as much as possible) the proof of theorems.

This dissertation proposes an approach for automatic formal verification of hardware. The specification is a subset of higher-order logic and the implementation is a circuit represented in the logic. The theorem prover HOL4 [59] translates the source code into a circuit and automatically proves that it meets the specification. In order to achieve a fully mechanised verification, we develop a technology to compose proofs automatically. We show the feasibility of this method in the development of small and medium-sized applications. Although this technology does not scale to industrial-sized applications yet, this thesis is a proof-of-concept that our approach is a promising first step in improving the degree of mechanisation in hardware verification (on any scale) using theorem provers.

In what follows, we overview how theorem provers help in mechanising hardware verification followed by a description of the contributions of this dissertation and an outline of the structure of the next chapters.

# **1.1** Mechanised Verification

There are two main techniques for mechanising hardware verification. *Model checking* exhaustively verifies that a model of the system satisfies some property. Systems are usually modelled as a finite state machines, which allows model checking to perform fully automatic verification. Another advantage of model checking is the generation of

counterexamples whenever a property does not hold. In contrast to model checking, *theorem proving* can deal with infinite state spaces. A theorem prover mechanises a proof system. Both the system and the properties are expressed inside some logic defined by axioms and inference rules. Theorem provers are able to model complex systems due to the high expressiveness of their logic. The disadvantage of using theorem provers is the need for user guidance in constructing proofs (although in particular domains, full automation is possible).

As our work is on theorem provers applied to hardware verification, we overview previous work using this technology. For an excellent survey on the application of model checking (and theorem provers) to hardware verification, see Kern and Greenstreet [49].

In the classic paper Why higher-order logic is a good formalism for specifying and verifying hardware [27], Gordon shows that specialised hardware description languages and specialised deductive systems are not needed for hardware verification. Formal logic suffices. Higher-order logic is now a well established formalism for specifying and verifying hardware [8, 19, 36, 55]. An advantage of this formalism is that higher-order functions naturally model signals as functions from time (natural numbers) to values, like Booleans. Moreover, it is possible to define additional mathematical theories on top of the logic and use them in hardware modelling. There are different versions of higher-order logic.

The HOL4 system implements Church's simple type theory with polymorphic types. The early experiments with hardware verification described by Gordon [27] were later extended by Melham, who introduced abstraction mechanisms for functional, data and time refinement [55]. Parallel to these developments, the verification of complete processors and micro-architectures were undertaken (e.g., Viper [16] and ARM6 [23]). More recently, Blumenröhr embedded the hardware description language Gropius [8] in HOL. This work is based on pre-proved theorems, which allow the automatic generation of circuits whose sub-modules are formally verified, thus providing a higher degree of mechanisation.

In VERITAS<sup>+</sup> [36], classical non-constructive logic is extended with dependent types and subtypes, thus enhancing its expressiveness and allowing polymorphism. The disadvantage of this extension is the loss of decidable type-checking. Dependent types and subtypes are also features of the PVS [64] prover. Its particular specification language is based on higher-order logic. Although PVS is a general purpose theorem prover, it has been applied to several projects in hardware verification, like the verification of microprocessors (AAMP5), arithmetic circuits and dynamic hardware reconfiguration algorithms [78, 79].

Hardware correctness has also been verified in first-order logic. The Boyer-Moore logic is a first-order, untyped, quantifier free logic of total recursive functions. The Nqthm theorem prover [13], which mechanises the Boyer-Moore logic, has been extensively used in hardware verification. For instance, Hunt et al. applied the prover to verify the correctness of the microprocessors FM8501 and FM9001 [40, 41]. The user has to be familiar with the heuristics employed in the prover in order to be able to guide Nqthm effectively [13]. The theorem prover ACL2 (A Computational Logic for Applicative Common Lisp) is a recoded version of Nqthm which supports a subset of applicative Common Lisp [48]. Like Nqthm, ACL2 has also being used in several projects related to verification of hardware. For instance, ACL2 was used to mechanically check the verification of a complex pipelined microprocessor [70] and to formalise a finite state machine language applied to the verification of a microprocessor [42].

There are several other theorem provers which have been applied to hardware verifica-

#### 1.2. CONTRIBUTIONS

tion. However it is not our intention to cover in detail all the previous work in hardware verification here, but to illustrate how the efforts to tackle industrial-sized applications and to achieve a greater degree of mechanisation using theorem provers evolved. The level of mechanisation, abstraction and the scale of later work [13, 23, 55, 78] have shown a significant improvement in comparison to early verification efforts [27, 36, 40]. Despite the tremendous advances in the mechanisation of hardware verification which produced several impressive cases of industrial-sized verifications, in general the process still requires human input. Hardware proofs in a particular application domain may follow particular patterns of verification and, consequently, benefit from a specific automatic proof technology, but in general theorem provers need user guidance.

In our work we experiment with an approach which minimises (or eliminates) any user guidance in the verification process. As mentioned in the previous section, one of the aims of this project is to evaluate the feasibility of this method to hardware specification and verification. We have chosen to work with the HOL4 system. Although in principle any other higher-order logic theorem prover could be used, hardware verification is intrinsically related to the HOL4 system. It is the application which motivated its creation [29] and which has been vastly explored and has contributed significantly to the system's development.

# **1.2** Contributions

This section lists the main contributions of this dissertation.

• We develop a compiler which takes a function f as argument and *automatically* returns the theorem

#### $\vdash$ C implements f

where C is a generated circuit and *implements* is a correctness relation between implementation and specification (*implements* is formally defined in Section 2.4). Both the circuit C and the function f are represented in HOL. In particular, C is a HOL representation of a netlist. The function f lies in a subset of HOL which constitutes a first-order tail-recursive functional language. The fully automatic verification is based on the principle of compositionality. The correctness of a complex circuit can be mechanically determined by the correctness of its sub-circuits. This is achieved by carefully designing the structure of our theorems.

- As a direct consequence of the automatic verification of circuits with respect to a functional program, the designers do not have to reason and to interactively verify systems at lower levels of abstraction like architectural, register-transfer or gate level. The development process can start from a specification in higher-order logic which is subsequently proved (interactively) to be implemented by a first-order tail-recursive function. This is the lowest level of abstraction the designer has to reason about during verification.

- We tested our approach to evaluate its feasibility. Our experiments and case studies have shown that our technology supports small and medium-sized applications. Typically the compiler takes few hours to verify the correctness of circuits with

approximately 700 components. Chapter 5 presents the verification of a simple microcomputer specified as functional program. We also developed a Booth multiplier specified originally as part of the ARM6 verification project (Section 5.1). Cryptographic algorithms like TEA [82] were verified by Konrad Slind at the University of Utah [76].

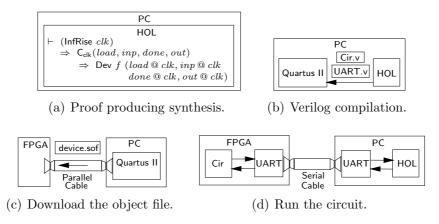

• A fully functional prototype that links HOL4 to an FPGA has been implemented. The complete development process can be carried out from the theorem prover. The HOL netlist is informally translated to structural Verilog, which is compiled and downloaded to an Altera FPGA by the Quartus II tool set.

# **1.3** The structure of this dissertation

In this section we outline the structure of the subsequent chapters.

Chapter 2 introduces the main concepts used in our approach. Initially we illustrate our approach informally using fictitious source and target languages. This is followed by a brief description of HOL and of how hardware is modelled and verified in the logic. We conclude by describing how the concepts introduced informally at the beginning of the chapter are formalised in HOL.

Chapter 3 presents several optimisation techniques and compilation steps for synthesis. The optimisations are basically theorems which state the equivalence between a circuit and its optimised version. We also describe a compilation step that introduces a global clock to the system and the technology used to download the netlist in an FPGA. The last section illustrates the complete verification process step-by-step.

**Chapter 4** reports on the limitations of our approach and describes issues and problems we faced during the development of this project.

**Chapter 5** shows the development of two case studies: an implementation of the Booth multiplier and a simple microcomputer called the DIY microcomputer. We developed two different designs for the DIY. In the first one, only the CPU is modelled in HOL. The second design includes a tiny memory connected to the CPU. We analyse the strengths and weaknesses of our compilation method revealed by the case studies.

In **Chapter 6**, we describe several closely related work. We review projects based on theorem provers and work on hardware synthesis of functional languages. We present a comparative analysis of these approaches based on the abstraction level of the source language and the level of automation of the verification.

Chapter 7 summarises our work and discusses the limitations and contributions of our approach.

Part of Chapter 2 is also described by Gordon et al. [30] and Slind et al. [77]. Chapter 3 and Section 5.1 were also introduced by Slind et al. [76].

10

# Chapter 2 Compilation

This chapter describes the compilation-by-proof approach. Section 2.1 informally describes the automatic verification using simple fictitious languages. Sections 2.2 and 2.3 overview higher-order logic and show how circuits are modelled and verified in the logic. Finally, Section 2.4 presents the source and the target languages and formalises the method introduced informally in Section 2.1.

# 2.1 Introduction

This section introduces the compilation and the verification method based on composable entities. For simplicity, we use fictitious languages in our examples.

Our aim is to develop a compiler which takes a program f and *automatically* produces a theorem

$$\vdash$$

C implements f

where C is a generated circuit and *implements* is a correctness relation between implementation and specification (*implements* is formally defined in Section 2.4).

First we classify the commands or constructors of a language in two kinds: atomic and composite. Atomic commands are those which do not depend on any sub-command to exist. For example, assignments are atomic commands in imperative programming languages. Composite commands are those which are built from sub-commands. Sequential composition and if-then-else are examples of composite commands.

A simple source language is used in this section to illustrate the compilation and the verification method. Its BNF is shown below.

$$p ::= f_1 | f_2 | f_3 | f_4(p_1, p_2) | f_5(p_1, p_2, p_3)$$

The commands  $f_1$ ,  $f_2$  and  $f_3$  are atomic. The composite commands  $f_4$  and  $f_5$  take two and three sub-commands as arguments, respectively. For example,  $f_5(f_4(f_3, f_2), f_1, f_2)$  is a program written in this language.

In order to translate this language into hardware (without verifying it), we define a

corresponding circuit implementation for each language constructor.

Circuits are represented by boxes, reflecting their physical structure.

The compilation is carried out by simply replacing every occurrence of a command in the source code by its corresponding circuit implementation. For example, the compilation of  $f_5(f_4(f_3, f_2), f_1, f_2)$  produces

$$f_5(f_4(f_3, f_2), f_1, f_2) \mapsto \boxed{\begin{array}{c} \mathsf{C}_5 \\ \mathsf{C}_4 \\ \mathsf{C}_3 \\ \mathsf{C}_2 \end{array}} \boxed{\begin{array}{c} \mathsf{C}_1 \\ \mathsf{C}_2 \end{array}}$$

For this method to work, the circuit constructors must have the same interface. This allows every circuit to connect to every other circuit. In the example above, the circuit  $C_5$  is connected to both primitive and composite sub-circuits. This is basically how SAFL [71] translates a functional program to hardware. The key idea is to deal with *composable* circuits.

This method inspired us to develop a similar approach concerning verification. The main challenge is to prove theorems which state the correctness of the circuits and also satisfy the composability property.

First we prove that the atomic circuits are correct.

The next step is to prove that the correctness of composite circuits depends on the correctness of its sub-circuits.

$$\vdash (\boxed{\mathsf{C}_{f}} \text{ implements } f) \land (\boxed{\mathsf{C}_{g}} \text{ implements } g)$$

$$\Rightarrow \boxed{\mathsf{C}_{4}} \boxed{\mathsf{C}_{f}} \boxed{\mathsf{C}_{g}} \text{ implements } f_{4}(f,g)$$

$$\vdash (\boxed{\mathsf{C}_{e}} \text{ implements } e) \land (\boxed{\mathsf{C}_{f}} \text{ implements } f) \land (\boxed{\mathsf{C}_{g}} \text{ implements } g)$$

$$\Rightarrow \boxed{\mathsf{C}_{5}} \boxed{\mathsf{C}_{e}} \boxed{\mathsf{C}_{f}} \boxed{\mathsf{C}_{g}} \text{ implements } f_{5}(e,f,g)$$

#### 2.1. INTRODUCTION

The circuits  $C_e$ ,  $C_f$  and  $C_g$  are implementations of the functions e, f and g, respectively. Note that they are not necessarily atomic. The composability of these theorems comes from the uniform structure of the antecedents and the consequents of the implication "(C implements f)". In addition to that, circuits and commands are also composable. This property allows a proof assistant to build proofs of correctness automatically.

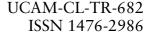

Figure 2.1 shows the compilation-by-proof of the program  $f_5(f_4(f_3, f_2), f_1, f_2)$ . Steps

Figure 2.1: Verification of  $f_5(f_4(f_3, f_2), f_1, f_2)$ .

1, 2 and 3 are the correctness theorems for circuits  $C_3$ ,  $C_2$  and  $C_4$ , respectively. On step 4, the variables  $C_f$  and  $C_g$  of step 3 are specialised with the circuits  $C_3$  and  $C_2$ . Step 5 eliminates the antecedent of step 4 by applying  $\wedge$ -Introduction and *modus ponens* with respect to steps 1 and 2. A similar proof is carried out from steps 6 to 9.

This example shows that we depend solely on  $\wedge$ -Introduction, modus ponens and specialisation of variables in order to verify the correctness of a circuit. The compilation process incrementally constructs the source code on the right-hand side of *implements*. This is easily mechanisable by a theorem proving system like HOL4 and requires no user guidance. Notice that the proof of correctness of each circuit constructor presented above is carried out in a interactive way, but the proof of any particular circuit is done automatically. This idea is not new. Composable theorems have already been used to implement algebraic compilers based on a refinement calculus [12, 69].

This section provided an informal description on how the automatic verification works. Before formalising the concepts presented here, higher-order logic is introduced, followed by an overview of hardware verification in this logic.

## 2.2 A Brief Introduction to HOL

This section briefly introduces the HOL logic [28]. We intend to explain the logical system from the hardware designer point of view. The terms *HOL* and *higher-order logic* are used interchangeably to mean the particular formulation developed by Mike Gordon at the University of Cambridge [26].

HOL is basically a predicate calculus with typed  $\lambda$ -calculus terms.

The predicate calculus of HOL allows variables to range over functions and predicates. For example, Peano's *Mathematical Induction* postulate is naturally formalised in HOL.

$$\vdash \ \forall P. \ P \ 0 \ \land \ (\forall n. \ P \ n \Rightarrow \ P \ (\mathsf{SUC} \ n)) \ \Rightarrow \ (\forall n. \ P \ n)$$

The variable P ranges over predicates. If P holds for 0 and if whenever it holds for a number n, it also holds for its successor (SUC n), then P holds for all natural numbers. Table 2.1 summarises the predicate logic notation.

| Term                       | Description            |

|----------------------------|------------------------|

| Т                          | true                   |

| F                          | false                  |

| $\neg t$                   | not t                  |

| $t_1 \lor t_2$             | $t_1 \text{ or } t_2$  |

| $t_1 \wedge t_2$           | $t_1$ and $t_2$        |

| $t_1 \Rightarrow t_2$      | $t_1$ implies $t_2$    |

| $t_1 = t_2$                | $t_1$ equals $t_2$     |

| $\forall x. t$             | for all $x:t$          |

| $\exists x. t$             | for some $x:t$         |

| $\varepsilon x. t$         | an $x$ such that : $t$ |

| if t then $t_1$ else $t_2$ | conditional            |

Table 2.1: Terms of the HOL logic.

The BNF for the untyped  $\lambda$ -terms is shown below.

$$M ::= c \mid v \mid (M N) \mid \lambda v. M$$

The syntactical variables c and v range over constants and variables, respectively. Function applications have the form  $(M \ N)$  and  $\lambda$ -abstractions are of the form  $\lambda v. M$ . For example,  $(\lambda x. x+1)$  denotes the function that takes a number and returns its successor. The term  $((\lambda x. x+1) \ 5)$  evaluates to 6. Functions can take functions as arguments and return functions as results. For example, the function  $(\lambda n. \lambda m. n+m)$  takes an argument, say 3, and returns a function which takes a number and adds 3 to it:  $(\lambda m. 3+m)$ . Actually, by defining new constants, it is possible to manipulate higher-order functions in a more user-friendly way. For example, it is easy to define the constant add as  $(add \ n \ m = n+m)$ . In Section 2.3 we illustrate how higher-order functions are used to model circuits.

HOL is a typed logic. The version of higher-order logic presented here extends Church's simple type theory [15] with polymorphic types. For example, the equality operator = is a higher-order function of type  $\alpha \rightarrow (\alpha \rightarrow bool)$ . The type of its arguments is not defined *a priori*. Type variables are represented by the Greek letters  $\alpha$ ,  $\beta$ ,  $\gamma$ , etc. The type  $\sigma_1 \rightarrow \sigma_2$

denotes the set of all total functions from values of  $\sigma_1$  to values of  $\sigma_2$ . In the Mathematical Induction postulate presented above, the predicate P is of type  $num \rightarrow bool$ , where num is the type of natural numbers. We can write  $P:num \rightarrow bool$  to explicitly declare its type.

The HOL logic is actually built from a very small set of primitive definitions. The primitive terms are those of the  $\lambda$ -expressions. The primitive constants are equality  $(=: \alpha \rightarrow \alpha \rightarrow bool)$ , implication  $(\Rightarrow: bool \rightarrow bool \rightarrow bool)$  and the choice operator  $(\varepsilon: (\alpha \rightarrow bool) \rightarrow \alpha)$ . The primitive types are bool, ind (set of individuals) and the type operator fun, which is abbreviated to the infix notation  $\rightarrow$ . All other types and constants are introduced in terms of these primitives by rules of definition, which guarantee to preserve the consistency of the system. From the primitive definitions, it is possible to develop a large library of theories like those for natural numbers, sets, lists, groups, etc. One of the first attempts to derive portions of mathematics from logic is described in Principia Mathematica by Russell and Whitehead [83] (but using a different logic).

There are quite a few theorem provers which mechanise HOL.

Isabelle is a generic theorem prover which provides a mechanism (a simple metalogic) to allow different object logics to be represented in it. The Isabelle system already includes several logics like Logic for Computable Functions, classical and intuitionistic first-order logic and Zermelo-Fraenkel set theory. Its specialisation for higher-order logic is called Isabelle/HOL [58].

HOL Light is an implementation of HOL built on top of a smaller and simpler logical core in comparison to previous implementations [37, 38]. Although its logical kernel is implemented in just about 400 lines of OCaml [60], HOL light is powerful enough to be used in large verification projects.

ProofPower [65] is another implementation of HOL. It was originally implemented by International Computers Ltd. (ICL) in collaboration with Program Validation Ltd. and the universities of Kent and Cambridge. Their aim was to develop a tool to support both HOL and the Z notation. In 1993 the first version of ProofPower was released. It was applied to high assurance security systems and safety-critical software. Since 1997, it has being developed by Lemma 1 Ltd.

The system we use in this work is the HOL4 [59]. The HOL4 system is latest version of a series of implementations first released in 1988. The HOL system was the first mechanisation of higher-order logic and was originally developed for hardware verification [28]. All of the systems mentioned above are descendants of the LCF system [56]. They follow many of the design concepts and remarkable ideas created by Robin Milner.

The next section illustrates how higher-order logic can be used to naturally model circuits and how hardware verification benefits from a proof assistant.

# 2.3 Hardware Verification in HOL

There are different ways of specifying the behaviour of a hardware component in higherorder logic. They vary in the level of abstraction and style. This section describes the model developed by Mike Gordon and Tom Melham for sequential circuits [27, 55].

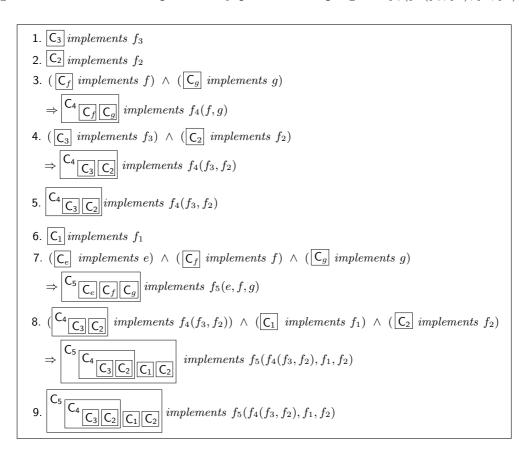

The behaviour of a hardware component is described by a predicate which restricts the observable values on its external wires. The component is regarded as a black box (see Figure 2.2).

Figure 2.2: Hardware component as a black box.

A predicate C, which specifies the behaviour of a component, is defined such that  $C(in_1, in_2, \ldots, in_n, out_1, out_2, \ldots, out_m)$  is true if and only if the wires  $in_1, in_2, \ldots, in_n$ ,  $out_1, out_2$  and  $out_m$  drive observable values.

Wires are modelled as functions from time to some type. They represent the sequence of values that appear on wires. Time is represented by natural numbers (type num) and values are either Booleans (representing a single bit) or words of a given size. A theory of *n*-bit words was formalised in HOL to support the verification of the ARM6 micro-architecture [23].

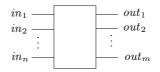

Figure 2.3 shows the specifications of an AND gate and a delay component.

$$in_{1} - out$$

$$in_{2} - out$$

$$\vdash \mathsf{AND}(in_{1}, in_{2}, out) = \forall t. out \ t = (in_{1} \ t) \land (in_{2} \ t)$$

$$inp - \Box \mathsf{EL} - out$$

$$\vdash \mathsf{DEL}(inp, out) = \forall t. out \ (t+1) = inp \ t$$

Figure 2.3: Primitive components in HOL.

Note that the predicates are higher-order. The wires  $in_1$ ,  $in_2$ , inp and out are functions from time to Boolean  $(num \rightarrow bool)$ . The definition of AND states that for all times we observe its external wires, the value of the output is the conjunction of the values of the inputs at that time. The delay component specifies the value of the output in terms of the value of the input at the *previous* time. At time zero, the value of the output is undefined.

The values of the external wires of a single component are restricted by its predicate. In order to specify the behaviour of two components connected together, we simply conjoin their predicates. The new specification restricts all wires of the composite circuit to satisfy the constraints imposed by both sub-circuits. In order to hide internal wires we can simply use the existential quantifier. Figure 2.4 shows the definition of a device which comprises an AND gate connected to a delay component by the internal wire c.

#### 2.3.1 Verification

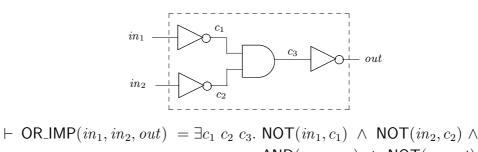

This section describes a simple example that illustrates how we can formally verify properties of a given circuit. The example shows how to verify that a particular circuit built from AND and NOT gates correctly implements an OR-gate.

$\vdash$  AND\_DEL $(in_1, in_2, out) = \exists c. AND(in_1, in_2, c) \land DEL(c, out)$

Figure 2.4: Circuit composition in HOL.

First we define the formal *specification* of the system, i.e. a predicate which specifies the required behaviour of the circuit.

$$\vdash \mathsf{OR\_SPEC}(in_1, in_2, out) = \forall t. out \ t = (in_1 \ t) \ \lor \ (in_2 \ t)$$

The specification states that the value of the output is always the disjunction of the inputs.

After specifying the required behaviour of the system, an *implementation* must be formally defined (see Figure 2.5).

$\mathsf{AND}(c_1, c_2, c_3) \land \mathsf{NOT}(c_3, out)$

Figure 2.5: Is the output the disjunction of the inputs?

The specification of an inverter is similar to the definition of an AND gate showed in the previous section.

$$\vdash$$

NOT $(inp, out) = \forall t. out t = \neg(inp t)$

In order to prove that the circuit  $OR_IMP$  correctly implements the specification  $OR\_SPEC$ , we have to prove that if the values on the external wires  $in_1$ ,  $in_2$  and *out* satisfy the constraints imposed by  $OR\_IMP$ , then they must also satisfy  $OR\_SPEC$ . This notion of correctness is formalised by a logical implication.

$\forall in_1 \ in_2 \ out. \ \mathsf{OR\_IMP}(in_1, in_2, out) \Rightarrow \ \mathsf{OR\_SPEC}(in_1, in_2, out)$

*Proof:* The proof starts by assuming that:

$OR_IMP(in_1, in_2, out)$

Replacing OR\_IMP, AND and NOT by their definitions gives:

$$\exists c_1 \ c_2 \ c_3. \ (\forall t. \ c_1 \ t = \neg(in_1 \ t)) \land \ (\forall t. \ c_2 \ t = \neg(in_2 \ t)) \land \\ (\forall t. \ c_3 \ t = (c_1 \ t) \land \ (c_2 \ t)) \land \ (\forall t. \ out \ t = \neg(c_3 \ t))$$

Now we can move all the equations under the scope of a single  $\forall$  quantifier.

$$\exists c_1 \ c_2 \ c_3. \ \forall t. \ (c_1 \ t = \neg(in_1 \ t)) \ \land \ (c_2 \ t = \neg(in_2 \ t)) \land \\ (c_3 \ t = (c_1 \ t) \ \land \ (c_2 \ t)) \ \land \ (out \ t = \neg(c_3 \ t))$$

Replacing the equation (out  $t = \neg(c_3 t)$ ) with the right-hand sides of  $(c_1 t = ...)$ ,  $(c_2 t = ...)$  and  $(c_3 t = ...)$  gives:

$$\exists c_1 \ c_2 \ c_3. \ \forall t. \ out \ t = \neg(\neg(in_1 \ t) \land \neg(in_2 \ t))$$

De Morgan's Law can now be applied to simplify to:

$\exists c_1 \ c_2 \ c_3. \ \forall t. \ out \ t = (in_1 \ t) \ \lor \ (in_2 \ t)$

Eliminating the existential quantifier and using the definition of OR\_IMP yield:

$OR\_SPEC(in_1, in_2, out)$

Based on the assumption in the first step, we can conclude that

$$OR\_IMP(in_1, in_2, out) \Rightarrow OR\_SPEC(in_1, in_2, out)$$

By generalising the free variables, we prove that

$\forall in_1 \ in_2 \ out. \ \mathsf{OR\_IMP}(in_1, in_2, out) \Rightarrow \ \mathsf{OR\_SPEC}(in_1, in_2, out)$

The theorem above is actually proved in fewer steps using the HOL4 system. For this simple example, very little user-guidance is needed and even a pencil-and-paper proof is easy to prove and check. However this is not the case for more elaborate implementations. For instance, the case studies presented in Chapter 5 manipulate circuits with several hundreds primitive components. This clearly makes manual or even interactive proof long and tedious.

# 2.4 Compilation-by-proof in HOL

This section presents the formalisation in HOL of the concepts introduced in Section 2.1. We use the same principles for hardware modelling and verification presented in the previous section.

#### 2.4.1 The Source Language

Our source language is a subset of HOL which constitutes a tail-recursive first-order functional language.

A function is tail-recursive if its recursive calls are the last operation executed in the body of the function, i.e. there are no operations to be carried out on the results of the recursive calls. For example, the function **mult** below is tail-recursive.

$\vdash$  mult(m, n, acc) = if (m = 0w) then acc else mult(m-1w, n, acc+n)

This function manipulates only 32-bit words (type *word32* in HOL). The terms 0w and 1w represent the numbers 0 and 1, respectively. The function call  $\mathsf{mult}(m, n, 0w)$  returns  $m \times n$ .

A standard definition of **mult** which is not tail-recursive is shown below.

$\vdash$  mult\_standard(m, n) = if (m = 0w) then 0w else  $n + \text{mult_standard}(m - 1w, n)$

Tail-recursive functions are of particular interest in hardware compilation because they eliminate the problem of saving the state of the function before the recursive call. In the example above, as  $\mathsf{mult}(m-1w, n, acc+n)$  is the last operation to be executed, the compiler will simply connect the arguments (m-1w, n, acc+n) back to the hardware component that implements  $\mathsf{mult}$ .

The abstract syntax of our source language is shown below.

$e ::= c \mid x \mid (if \ e_1 \ then \ e_2 \ else \ e_3) \mid f(e_1, \dots, e_{(\#f)})$  $p ::= (f_1(x_1, \dots, x_{(\#f_1)}) = e_1), \ \dots, \ (f_n(x_1, \dots, x_{(\#f_n)}) = e_n)$

An expression is either a constant, a variable, a conditional or a function call. The term #f denotes the arity of f. A program is simply a list of function definitions. A recursive function must have the form:

$$f(x_1,\ldots,x_n) = if e_1 then e_2 else f(e_3)$$

where  $e_1$ ,  $e_2$  and  $e_3$  do not contain a call to f. However, these expressions can contain calls to other (recursive) functions provided that they are *not* mutually recursive.

For example, the function fact below uses the multiplier defined above to compute the factorial of a number (whenever the accumulator acc is initialised to 1w).

$\vdash$  fact(n, acc) = if (n = 0w) then acc else fact $(n-1w, \mathsf{mult}(n, acc, 0w))$

A list containing the function definitions of **mult** and **fact** is an example of a typical program in our source language.

$(\mathsf{mult}(m, n, acc) = if \ (m = 0w) \ then \ acc \ else \ \mathsf{mult}(m-1w, n, acc+n)),$  $(\mathsf{fact}(n, acc) = if \ (n = 0w) \ then \ acc \ else \ \mathsf{fact}(n-1w, \mathsf{mult}(n, acc, 0w)))$

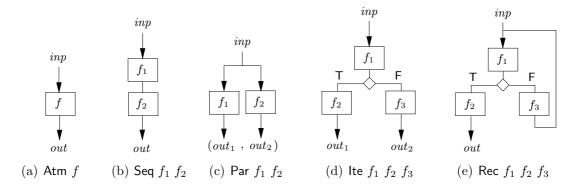

#### The Intermediate Language

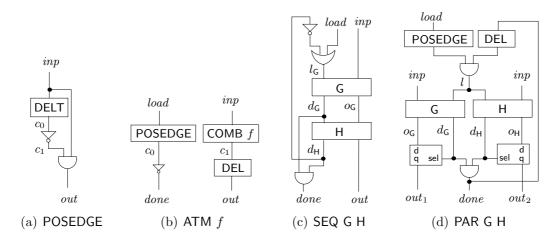

We need to translate the source language into an intermediate form. The compiler transforms the source code to one which contains only *atomic* operators, sequential and parallel compositions, conditional constructors and tail-recursive calls. Atomic operators are the primitive operators of the language, like addition or subtraction. These operators are part of a library and are not built from sub-components (recall the notion of atomic commands given in Section 2.1). The intermediate code is still a functional program, but it reflects the structure of the circuit to be built. The constructors are called Atm (atomic), Seq (sequential), Par (parallel), Ite (if-then-else) and Rec (see Figure 2.6).

Figure 2.6: The intermediate language.

Each box depicted in Figure 2.6 represents a function which is eventually compiled into a hardware block. The constructors are higher-order functions defined as:

The atomic constructor acts as the identity function. It is used to identify the primitive operators. The Seq constructor is a simple function composition. The term (Par  $f_1 f_2$ ) is a function that takes an argument, say v, and produces the pair  $(f_1 v, f_2 v)$ . The conditional constructor represents the usual if-then-else and the constructor Rec implements a tail-recursive function.

HOL4 automatically translates a source program into its intermediate form. For example, the function word2bool transforms a 32-bit word into a Boolean.

$\vdash$  word2bool n = (if (n = 0w) then F else T)

Its intermediate code is shown below.

$$\begin{array}{l} \vdash \mbox{ word2bool} = \mbox{Ite } (\mbox{Seq } (\mbox{Par } (\mbox{Atm } \lambda n. \ n) \\ (\mbox{Atm } \lambda n. \ 0w)) \\ (\mbox{Atm } \lambda n. \ 0w)) \\ (\mbox{Atm } \lambda n. \ F) \\ (\mbox{Atm } \lambda n. \ T) \end{array}$$

The atomic operators which occur in word2bool are the identity function, the equality and constant generators for zero, true and false. The constructor lte takes three arguments. The first is the test of the conditional. The parallel constructor produces the pair (n, 0w), which is subsequently sent to the comparator via the sequential constructor. The remaining arguments of lte are the conditional branches. In the example above, they both generate a Boolean constant. For a slightly more elaborate example, Figure 2.7 shows the intermediate code for the function mult.

```

\label{eq:mult} \begin{split} \vdash \ \mathsf{mult}(m,n,acc) &= if \ (m=0w) \ then \ acc \ else \ \mathsf{mult}(m-1w,n,acc+n) \\ \vdash \ \mathsf{mult} = \mathsf{Rec} \ (\mathsf{Seq} \ (\mathsf{Par} \ (\mathsf{Atm} \ \lambda(m,n,acc). \ m) \\ & (\mathsf{Atm} \ \lambda(m,n,acc). \ 0w)) \\ & (\mathsf{Atm} \ \lambda(x,y). \ x=y)) \\ & (\mathsf{Atm} \ \lambda(m,n,acc). \ acc) \\ & (\mathsf{Par} \ (\mathsf{Seq} \ (\mathsf{Par} \ (\mathsf{Atm} \ \lambda(m,n,acc). \ m) \\ & (\mathsf{Atm} \ \lambda(m,n,acc). \ 1w)) \\ & (\mathsf{Atm} \ \lambda(m,n,acc). \ 1w)) \\ & (\mathsf{Atm} \ \lambda(m,n,acc). \ n) \\ & (\mathsf{Seq} \ (\mathsf{Par} \ (\mathsf{Atm} \ \lambda(m,n,acc). \ acc) \\ & (\mathsf{Atm} \ \lambda(m,n,acc). \ n)) \\ & (\mathsf{Atm} \ \lambda(m,n,acc). \ n)) \\ & (\mathsf{Atm} \ \lambda(x,y). \ x+y)))) \end{split}

```

Figure 2.7: Intermediate code for mult.

#### 2.4.2 The Specification

Section 2.1 presented a correctness relation between a circuit C and a function f.

$\vdash$  C implements f

In this section we formalise the notion of a circuit implementing a function.

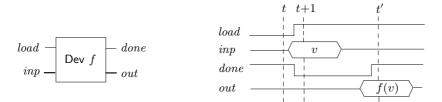

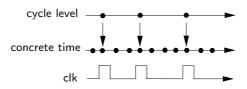

A device is a black box which computes some function f via a four-phase handshaking protocol (see Figure 2.8). Its external wires are *load*, *inp*, *done* and *out*. The wires *load* and *done* are control signals; *done* indicates when the device is available and *load* is used by the environment to trigger the device. Data are received and sent over the *inp* and *out* buses, respectively.

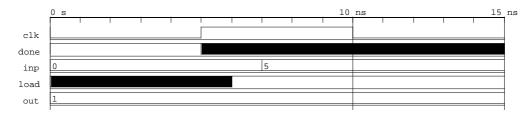

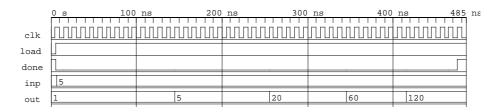

Figure 2.8: Handshaking device.

Figure 2.8 shows a timing diagram of the handshake protocol. At the start of a transaction (say at time t) the device must be outputting T on *done* (to indicate it is ready) and the environment must be asserting F on *load*, i.e. in a state such that a positive edge on *load* can be generated. A transaction is initiated by asserting (at time t+1) the value T on *load*, i.e. *load* has a positive edge at time t+1. This causes the device to read the value, v say, input on *inp* (at time t+1) and to set *done* to F. The device then becomes insensitive to inputs until T is next asserted on *done*, when the computed value f(v) will be output on *out*.

The formal specification of the four-phase handshake protocol is defined by the predicate **Dev** below, which uses the auxiliary predicates **Posedge** and **HoldF**.

A positive edge of a signal is defined as the transition of its value from low to high, i.e. from F to T. There is no positive edge at time zero.

$\vdash$  Posedge s t = if (t=0) then  $\mathsf{F}$  else  $(\neg(s (t-1)) \land (s t))$

The formula (HoldF  $(t_1, t_2) s$ ) says that a signal s holds a low value F during a halfopen interval starting at  $t_1$  to just before  $t_2$ .

$$\vdash \mathsf{HoldF}(t_1, t_2) \ s \ = \ \forall t. \ t_1 \le t < t_2 \ \Rightarrow \ \neg(s \ t)$$

The formula Dev f (load, inp, done, out) specifies the behaviour of the handshaking device computing a function f.

$$\vdash \text{ Dev } f \ (load, inp, done, out) = \\ (\forall t. \ done \ t \ \land \ \text{Posedge} \ load \ (t+1) \\ \Rightarrow \\ \exists t'. \ t' > t+1 \ \land \ \text{HoldF} \ (t+1, t') \ done \ \land \\ done \ t' \ \land \ (out \ t' = f(inp \ (t+1)))) \ \land \\ (\forall t. \ done \ t \ \land \ \neg(\text{Posedge} \ load \ (t+1)) \Rightarrow \ done \ (t+1)) \land \\ (\forall t. \ \neg(done \ t) \ \Rightarrow \ \exists t'. \ t' > t \ \land \ done \ t')$$

The first conjunct in the right-hand side specifies that if the device is available and a positive edge occurs on *load*, then there exists a time t' in future when *done* signals its termination and the output is produced. The value of the output at time t' is the result of applying f to the value of the input at time t+1. The signal *done* holds the value F during the computation. The second conjunct specifies the situation where no call is made on *load* and the device simply remains idle. Finally, the last conjunct states that if the device is busy, it will eventually finish its computation and become idle. This liveness condition prevents a circuit which constantly outputs F on *done* from satisfying any (Dev f).

Now we can formally state the notion of correctness for a circuit implementing a function. A circuit C implements a device which computes the function f if, whenever the values on the external wires *load*, *inp*, *done* and *out* satisfy the constraints imposed by the circuit, then they also satisfy the constraints imposed by (Dev f).

$\vdash \mathsf{C} \text{ implements } f = \\ \forall load \text{ inp done out. } \mathsf{C}(load, inp, done, out) \Rightarrow \mathsf{Dev} f(load, inp, done, out)$

#### 2.4.3 Automatic Verification

As shown in Section 2.1, for each language constructor we have to develop a corresponding circuit constructor and prove its correctness. Let us assume that the circuit constructors ATM, SEQ, PAR, ITE and REC have already been defined (their formal definitions are presented in Section 2.4.4). This section presents the theorems that establish they are correct implementations of the functions Atm, Seq, Par, Ite and Rec.

In order to verify circuits automatically, our theorems must have the same composable structure of the theorems shown in Section 2.1. We prove the following theorems in the HOL4 system.

$\vdash \forall f. (ATM f) implements (Atm f)$   $\vdash \forall G H g h.$   $(G implements g) \land (H implements h)$   $\Rightarrow (SEQ G H) implements (Seq g h)$   $\vdash \forall G H g h.$   $(G implements g) \land (H implements h)$   $\Rightarrow (PAR G H) implements (Par g h)$   $\vdash \forall E G H e g h.$   $(E implements e) \land (G implements g) \land (H implements h)$   $\Rightarrow (ITE E G H) implements (Ite e g h)$   $\vdash \forall E G H e g h.$  Total(e, g, h)  $\Rightarrow (E implements e) \land (G implements g) \land (H implements h)$   $\Rightarrow (REC E G H) implements (Rec e g h)$

Notice that ATM is a parameterised circuit which takes a *function* as argument. For example, the circuit (ATM  $(\lambda(x, y), x+y)$ ) implements the primitive operator  $(\lambda(x, y), x+y)$ . The circuits SEQ, PAR, ITE and REC take *sub-circuits* as arguments. We do not show the proofs here. They are straightforward and are similar to the proof of correctness of the circuit OR\_IMP (Section 2.3.1), but they are much longer and tedious to read. These proofs are available in the **examples** directory of the HOL4 CVS repository [81]. The first theorem is the base case of the compilation. The ATM circuit implements handshaking devices that compute the primitive operator f. The theorems for SEQ, PAR and ITE state that if their sub-circuits are correct, then the composite circuit is correct.

The theorem for REC has a pre-condition: the correctness of the circuit (REC E G H) can only be established if the function (Rec e g h) terminates. This is necessary because functions in HOL are total. Termination is characterised by the predicate Total.

$$\vdash \mathsf{Total}(e, g, h) = \exists (variant : \alpha \to num). \\ (\forall inp. \neg (e \ inp) \Rightarrow variant(h \ inp) < variant(inp))$$

Intuitively, this predicate is based on the fact that if the arguments of a function can be related by a well-founded relation, then the function terminates. The predicate states that if the input is not in the base case, then the recursive call will compute over a new input  $(h \ inp)$  which is smaller in some sense than the current input inp.

In principle, the restriction of proving termination eliminates the possibility of an automatic verification. The theorem for REC has lost the pure structure of a composable theorem. However, one of the facilities provided by the HOL4 system is the TFL package [74], which mechanises the proof of termination with little user guidance — the user must provide only a proper variant.

For example, the compilation of the recursive function **mult** is done by calling the function hwDefine.

```

hwDefine '(mult(m:word32,n:word32,acc:word32) =

if m=0w then acc else mult(m-1w,n,acc+n)) measuring (w2n o FST)'

```

The function mult is defined for 32-bit words. The variant is given by the function composition (w2n  $\circ$  FST), which takes the first element of the tuple (m, n, acc) and transforms a word into a natural number (the totality is defined in terms of the < relation for natural numbers)<sup>1</sup>. This variant isolates the variable m, which is a key variable for TFL to prove the termination of mult. The function hwDefine automatically returns the theorem below.

This theorem states that the circuit (REC (SEQ...) (ATM...) (PAR...)) implements a handshaking device which computes the function mult. The proof is done essentially in the same way of the proof shown in Figure 2.1.

### 2.4.4 The Implementation

This section describes our target language. Following the approach described in Section 2.1, we define circuits which implement each constructor of the intermediate language.

The circuits introduced in this section are defined in terms of the following primitive components.

- $\vdash \mathsf{AND}(in_1, in_2, out) = \forall t. out \ t = (in_1 \ t \ \land \ in_2 \ t)$

- $\vdash \mathsf{OR}(in_1, in_2, out) = \forall t. out \ t = (in_1 \ t \ \lor \ in_2 \ t)$

- $\vdash$  NOT  $(inp, out) = \forall t. out t = \neg(inp t)$

- $\vdash$  MUX(sw, in<sub>1</sub>, in<sub>2</sub>, out) =  $\forall t. out \ t = if \ (sw \ t) \ then \ (in_1 \ t) \ else \ (in_2 \ t)$

- $\vdash$  DEL (*inp*, *out*) =  $\forall t$ . *out* (t+1) = *inp* t

- $\vdash$  DELT (*inp*, *out*) = (*out* 0 = T)  $\land \forall t. out (t+1) = inp t$

- $\vdash$  COMB  $f(inp, out) = \forall t. out t = f(inp t)$

The components AND, OR, NOT and MUX are defined in a standard way. We introduce two sequential components: DEL and DELT. The delays DEL and DELT output the value of the current input one time-unit later. The only difference between them is that DELT outputs T at time zero. The component (COMB f) is a combinational circuit which

24

$<sup>^{1}</sup>$ In the most recent version of the compiler, we can omit the measuring function in some cases. For instance, mult can be defined by:

hwDefine 'mult(m:num,n:num,acc:num) = if m=0 then acc else mult(m-1,n,acc+n)'

This facility is available to variables of type : num, but we still have to extend it to words.

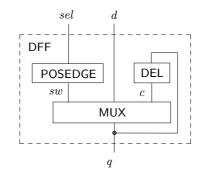

Figure 2.9: The implementation of DFF\_SPEC.

applies the function f to the input. This component is used to implement the primitive operators of the language. Note that COMB is a parameterised circuit. A real circuit is only synthesisable after applying COMB to some function, e.g. COMB ( $\lambda(x, y)$ . (x = y)). This indicates that ( $\lambda(x, y)$ . x = y) is a primitive operator of the language.

Before presenting the implementations of the intermediate language constructors, we introduce two auxiliary circuits.

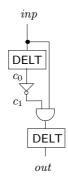

The circuit **POSEDGE** detects a positive edge on the input (see Figure 2.10(a) on page 26).

$$\vdash$$

POSEDGE $(inp, out) = \exists c_0 \ c_1. \ \mathsf{DELT}(inp, c_0) \land \mathsf{NOT}(c_0, c_1) \land \mathsf{AND}(c_1, inp, out)$

The specification DFF\_SPEC describes a device which outputs the value of the input whenever there is a positive edge on the signal *sel*.

$$\vdash \mathsf{DFF\_SPEC}(d, sel, q) = \\ \forall t. \ q \ (t+1) = if \ (\mathsf{Posedge} \ sel \ (t+1)) \ then \ (d \ (t+1)) \ else \ (q \ t)$$

One possible implementation of DFF\_SPEC is defined below (see Figure 2.9).

$$\vdash$$

DFF $(d, sel, q) = \exists c \ sw. \ \mathsf{POSEDGE}(sel, sw) \land \mathsf{DEL}(q, c) \land \mathsf{MUX}(sw, d, c, q)$

It is easy to prove that the circuit DFF is an implementation of the DFF\_SPEC.

$$\vdash$$

DFF(d, sel, q)  $\Rightarrow$  DFF\_SPEC(d, sel, q)

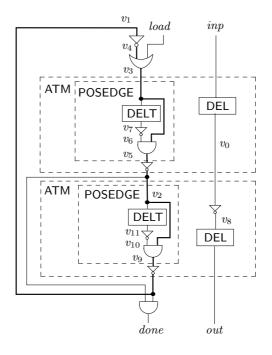

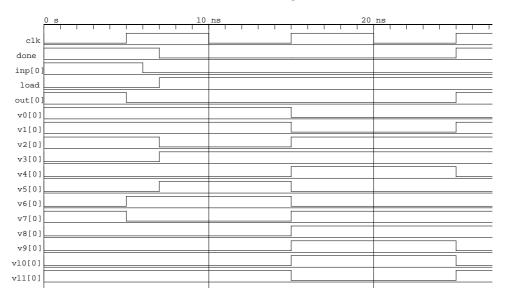

Recall that the language constructors Atm, Seq, Par, Ite and Rec presented in Section 2.4.1 are *functions* which perform general computations like sequential execution or recursion. As shown in Section 2.4.2, a circuit implements a function f if it behaves like a handshaking device that computes f. Therefore, we develop, for each language constructor, a corresponding circuit which implements the functionality of the constructor over a handshaking interface. Figures 2.10 and 2.11 show these handshaking circuits, where the local wires l, i, d and o represent the external wires *load*, *inp*, *done* and *out* of a sub-circuit. The *circuits* ATM, SEQ, PAR, ITE and REC implement the *functions* Atm, Seq, Par, Ite and Rec, respectively.

In what follows, we describe the behaviour of these five circuits. All of them satisfy the properties shown in Section 2.4.3.

Figure 2.10: Implementation of composite devices.

ATM

$$\vdash \mathsf{ATM} f (load, inp, done, out) = \\ \exists c_0 \ c_1. \ \mathsf{POSEDGE}(load, c_0) \land \ \mathsf{NOT}(c_0, done) \land \\ \mathsf{COMB} \ f (inp, c_1) \land \ \mathsf{DEL}(c_1, out)$$

We assume that the primitive operators are combinational. The atomic constructor encapsulates the combinational circuit (COMB f) inside a handshaking interface, where f is a primitive operator of the language. The computation of an atomic circuit takes exactly one time-unit. As soon as a positive edge on *load* is detected, *done* outputs F and DEL stores the value of f applied to the current value of *inp*. At the next observable time, the circuit is ready again and *out* returns valid data.

SEQ

$$\begin{array}{l} \vdash \ \mathsf{SEQ} \ \mathsf{G} \ \mathsf{H} \ (load, inp, done, out) = \\ \exists c_0 \ l_{\mathsf{G}} \ d_{\mathsf{G}} \ o_{\mathsf{G}} \ d_{\mathsf{H}}. \\ \mathsf{NOT}(d_{\mathsf{H}}, c_0) \ \land \ \mathsf{OR}(c_0, load, l_{\mathsf{G}}) \ \land \ \mathsf{G}(l_{\mathsf{G}}, inp, d_{\mathsf{G}}, o_{\mathsf{G}}) \ \land \\ \mathsf{H}(d_{\mathsf{G}}, o_{\mathsf{G}}, d_{\mathsf{H}}, out) \ \land \ \mathsf{AND}(d_{\mathsf{G}}, d_{\mathsf{H}}, done) \end{array}$$

The circuit SEQ takes two sub-circuits G and H and connect them in sequence. For the handshaking protocol of the entire circuit to work, the sub-circuits must also be handshaking circuits. If the sequential computation is not finished, the circuit ignores any calls on *load* (see the OR-gate in Figure 2.10(c)). Actually, all handshaking circuits have this behaviour.

PAR

$$\vdash \mathsf{PAR} \mathsf{G} \mathsf{H} (load, inp, done, out) = \\ \exists c_0 \ c_1 \ l \ d_{\mathsf{G}} \ o_{\mathsf{G}} \ d_{\mathsf{H}} \ o_{\mathsf{H}}. \\ \mathsf{POSEDGE}(load, c_0) \land \mathsf{DEL}(done, c_1) \land \mathsf{AND}(c_0, c_1, l) \land \\ \mathsf{G}(l, inp, d_{\mathsf{G}}, o_{\mathsf{G}}) \land \mathsf{H}(l, inp, d_{\mathsf{H}}, o_{\mathsf{H}}) \land \\ \mathsf{DFF}(o_{\mathsf{G}}, d_{\mathsf{G}}, out_1) \land \mathsf{DFF}(o_{\mathsf{H}}, d_{\mathsf{H}}, out_2) \land \\ \mathsf{AND}(d_{\mathsf{G}}, d_{\mathsf{H}}, done) \land (out = \lambda t. (out_1 \ t, out_2 \ t)) \end{cases}$$

The parallel circuit triggers both of its sub-circuits  $\mathsf{G}$  and  $\mathsf{H}$  at the same time (see the wire

*l* in Figure 2.10(d)). The computation finishes when both sub-circuits finish. In order to output valid results from both sub-circuits, their outputs are stored in DFFs, which are triggered by the positive edge that occurs on  $d_{\rm G}$  and  $d_{\rm H}$  when the circuits G and H finish their computation.

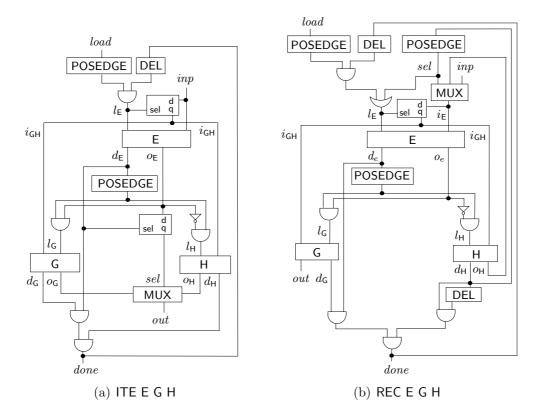

ITE

$\vdash \mathsf{ITE} \mathsf{E} \mathsf{F} \mathsf{G} (load, inp, done, out) = \\ \exists c_0 \ c_1 \ c_2 \ c_3 \ c_4 \ l_{\mathsf{E}} \ i_{\mathsf{GH}} \ d_{\mathsf{E}} \ o_{\mathsf{E}} \ l_{\mathsf{G}} \ l_{\mathsf{H}} \ d_{\mathsf{G}} \ o_{\mathsf{G}} \ o_{\mathsf{H}} \ d_{\mathsf{H}} \ sel. \\ \mathsf{POSEDGE}(load, c_0) \ \land \ \mathsf{DEL}(done, c_1) \ \land \ \mathsf{AND}(c_0, c_1, l_{\mathsf{E}}) \ \land \\ \mathsf{E}(l_{\mathsf{E}}, inp, d_{\mathsf{E}}, o_{\mathsf{E}}) \ \land \ \mathsf{POSEDGE}(d_{\mathsf{E}}, c_2) \ \land \ \mathsf{DFF}(o_{\mathsf{E}}, d_{\mathsf{E}}, sel) \ \land \\ \mathsf{DFF}(inp, l_{\mathsf{E}}, i_{\mathsf{GH}}) \ \land \ \mathsf{AND}(c_2, o_{\mathsf{E}}, l_{\mathsf{G}}) \ \land \ \mathsf{NOT}(o_{\mathsf{E}}, c_3) \ \land \\ \mathsf{AND}(c_2, c_3, l_{\mathsf{H}}) \ \land \ \mathsf{G}(l_{\mathsf{G}}, i_{\mathsf{GH}}, d_{\mathsf{G}}, o_{\mathsf{G}}) \ \land \ \mathsf{H}(l_{\mathsf{H}}, i_{\mathsf{GH}}, d_{\mathsf{H}}, o_{\mathsf{H}}) \ \land \\ \mathsf{MUX}(sel, o_{\mathsf{G}}, o_{\mathsf{H}}, out) \ \land \ \mathsf{AND}(d_{\mathsf{G}}, d_{\mathsf{E}}, c_4) \ \land \ \mathsf{AND}(c_4, d_{\mathsf{H}}, done) \\ \end{cases}$

The *if-then-else* circuit ITE takes three sub-circuits E, G and H as arguments. The circuit E tests the condition and the circuits G and H compute the conditional branches. The result of the test is stored in a DFF connected to a multiplexer (Figure 2.11(a)).

Figure 2.11: The conditional and the recursive constructors.

$\vdash \mathsf{REC} \mathsf{E} \mathsf{F} \mathsf{G} (load, inp, done, out) = \\ \exists c_0 \ c_1 \ c_2 \ c_3 \ c_4 \ c_5 \ c_6 \ c_7 \ sel \ l_{\mathsf{E}} \ i_{\mathsf{E}} \ i_{\mathsf{GH}} \ d_{\mathsf{E}} \ o_{\mathsf{E}} \ l_{\mathsf{G}} \ l_{\mathsf{H}} \ d_{\mathsf{G}} \ d_{\mathsf{H}} \ o_{\mathsf{H}}. \\ \mathsf{POSEDGE}(load, c_0) \land \mathsf{DEL}(done, c_1) \land \mathsf{AND}(c_0, c_1, c_2) \land \\ \mathsf{OR}(c_2, sel, l_{\mathsf{E}}) \land \mathsf{POSEDGE}(d_{\mathsf{H}}, sel) \land \mathsf{MUX}(sel, o_{\mathsf{H}}, inp, i_{\mathsf{E}}) \land \\ \mathsf{DFF}(i_{\mathsf{E}}, l_{\mathsf{E}}, i_{\mathsf{GH}}) \land \mathsf{E}(l_{\mathsf{E}}, i_{\mathsf{E}}, d_{\mathsf{E}}, o_{\mathsf{E}}) \land \mathsf{POSEDGE}(d_{\mathsf{E}}, c_3) \land \\ \mathsf{AND}(c_3, o_{\mathsf{E}}, l_{\mathsf{G}}) \land \mathsf{NOT}(o_{\mathsf{E}}, c_4) \land \mathsf{AND}(c_4, c_3, l_{\mathsf{H}}) \land \mathsf{G}(l_{\mathsf{G}}, i_{\mathsf{GH}}, d_{\mathsf{G}}, out) \land \\ \mathsf{H}(l_{\mathsf{H}}, i_{\mathsf{GH}}, d_{\mathsf{H}}, o_{\mathsf{H}}) \land \mathsf{DEL}(d_{\mathsf{H}}, c_5) \land \mathsf{AND}(d_{\mathsf{H}}, c_5, c_7) \land \mathsf{AND}(d_{\mathsf{G}}, d_{\mathsf{E}}, c_6) \land \\ \\ \mathsf{AND}(c_6, c_7, done) \end{aligned}$

The recursive function is very similar to the conditional one. It also takes three circuits E, G and H as arguments. The only difference is that it connects the output of H to the input of E to implement the tail-recursion. A delay is connected to the *done* signal of H in order to distinguish a recursive call from the complete termination of the computation (Figure 2.11(b)).

# 2.5 Summary

This chapter presented the main ideas related to the compilation-by-proof method. We started by introducing the notion of automatic verification via composable theorems, followed by the introduction of higher-order logic and hardware verification.

Then, the source language was presented together with an intermediate language, which is the one manipulated by the compiler. This language structures the source code in terms of the composable functions Atm, Seq, Par, Ite and Rec.

For each of these constructors, we defined five circuit constructors which implement them: ATM, SEQ, PAR, ITE and REC.

The notion of correctness for circuits implementing functions is given via the concept of a handshaking device which computes a function. We showed that each circuit constructor is correct, provided that their sub-circuits are correct. As usual in verification tasks, proofs of correctness are not mathematically challenging, but rather long and tedious. Our proofs take nearly 3,000 lines of ML [81] and took several months of work.

As the main aim of this chapter is to introduce the principles and concepts involved in our compilation, we have not addressed issues like clocked circuits generation or optimisations. These steps are presented in the next chapter.

REC

# Chapter 3 Optimisations and Synthesis

Chapter 2 focused on the fundamental concepts underlying our compiler. However in order to deal with more realistic designs, we implement optimisations and integrate HOL4 with external tools for FPGAs. This chapter describes these features.

The optimisations aim to reduce the size of a circuit and its execution time. Section 3.1 presents four optimisations introduced to the compiler.

In order to run our circuit, we transform it into a clocked synchronous circuit, translate it to Verilog and download it to an FPGA. Section 3.2 describes how to introduce a clock signal using time refinement. The translation of clocked circuits to Verilog and the integration of HOL4 to an FPGA are presented in Section 3.3. The last section shows a simple example which illustrates all the steps of the compilation.

# 3.1 Optimisations

In what follows we introduce four optimisations: the circuits PRECEDE and FOLLOW, the extension of the primitive constructors, *whole program compaction* and let-expressions.

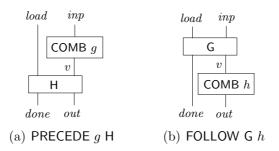

#### PRECEDE and FOLLOW

In the last chapter we defined handshaking circuits for every constructor of the language. In particular, the atomic constructors implement a handshaking interface to encapsulate a combinational circuit<sup>1</sup>. We can eliminate some of these internal handshakes by directly connecting a combinational part to another circuit.

We create two circuit constructors which connects a combinational component in sequence to another circuit without introducing a handshake. These constructors are introduced during the compilation of  $(Seq \ g \ h)$ , where g or h is combinational.

$\vdash \mathsf{PRECEDE} \ g \ \mathsf{H} \ (load, inp, done, out) = \\ \exists v. \ \mathsf{COMB} \ g \ (inp, v) \ \land \ \mathsf{H}(load, v, done, out)$

$\vdash \mathsf{FOLLOW} \mathsf{G} h(load, inp, done, out) = \\ \exists v. \mathsf{G}(load, inp, done, v) \land \mathsf{COMB} h(v, out)$

The circuit (PRECEDE g H) connects the combinational circuit (COMB g) to the *input*

<sup>&</sup>lt;sup>1</sup>Combinational circuits are those whose output is a function of the present input only.

of circuit H, while (FOLLOW G h) connects (COMB h) to the *output* of circuit G (see Figure 3.1).

Figure 3.1: PRECEDE and FOLLOW.

In order to include these constructors in the compilation, we have to prove their correctness:

$$\vdash (\mathsf{H} \text{ implements } h) \Rightarrow ((\mathsf{PRECEDE} g \mathsf{H}) \text{ implements } (\mathsf{Seq} g h)) \\ \vdash (\mathsf{G} \text{ implements } g) \Rightarrow ((\mathsf{FOLLOW} \mathsf{G} h) \text{ implements } (\mathsf{Seq} g h))$$

This technique is applied when either g or h in (Seq g h) is combinational. If both are combinational, then the following optimisation is more effective.

#### Extending the primitive operators

The same principle of eliminating handshakes which motivated the creation of PRECEDE and FOLLOW can be applied to the constructors Seq, Par and Ite. If we include these constructors in the library of the *primitive operators* of the language, the compiler eliminates their handshakes provided that their arguments are primitive operators (or are built from primitive operators only). If they are not combinational, the compiler generates the usual handshake circuits SEQ, PAR and ITE. See below the transformations performed by the compiler assuming that e, g and h are primitive operators of the language or can be recursively reduced to a netlist of primitive operators only.

The sequential composition is transformed into two combinational circuits in series.

$$\vdash \mathsf{COMB} (\mathsf{Seq} g h) (inp, out) = \\ \exists c. \mathsf{COMB} g (inp, c) \land \mathsf{COMB} h (c, out)$$

The parallel composition is broken into two different combinational components.

$\vdash \mathsf{COMB} (\mathsf{Par} \ g \ h) \ (inp, out_1 \diamond out_2) = \\ \mathsf{COMB} \ g \ (inp, out_1) \ \land \ \mathsf{COMB} \ h \ (inp, out_2)$

Note that the output of (COMB (Par g h)) is a concatenation of two signals, namely  $out_1$  and  $out_2$ . We concatenate signals by using the operator  $\diamond$ .

$$\vdash s_1 \diamond s_2 = (\lambda t. (s_1 t, s_2 t))$$

The conditional operator is implemented by a multiplexer.

$$\vdash \begin{array}{l} \mathsf{COMB} (\mathsf{lte} \ e \ g \ h) \ (inp, out) \ = \\ \exists c_0 \ c_1 \ c_2. \ \mathsf{COMB} \ e \ (inp, c_0) \ \land \ \mathsf{COMB} \ g \ (inp, c_1) \ \land \\ \mathsf{COMB} \ h \ (inp, c_2) \ \land \ \mathsf{MUX}(c_0, c_1, c_2, out) \end{array}$$

#### 3.1. OPTIMISATIONS

These optimisations connect as many combinational components as possible in order to reduce the amount of handshakes. In addition to the transformations presented above, the process of reducing a circuit to a netlist of primitive operators makes use of auxiliary transformations.

For example, assuming that  $(\lambda n. n)$  and  $(\lambda n. 1w)$  are defined as primitive operators, the compiler generates the following simplifications.

$\vdash \mathsf{COMB} (\lambda n. n) (inp, out) = (inp = out) \\ \vdash \mathsf{COMB} (\lambda n. 1w) (inp, out) = \mathsf{CONSTANT} 1w out$

where **CONSTANT** is a primitive hardware component defined as

$\vdash \mathsf{CONSTANT} \ v \ out \ = \ \forall t. \ out \ t = v$

#### Whole program compaction

A source program is a list of functions. Any optimisation like the ones performed above is restricted to the scope of a function.

Whole program compaction or inline expansion replaces every function call by the body of the function. This produces a monolithic source program defined by a single function, namely the function main. This pre-compilation is performed before any optimisation step.

The optimisations can now have a global view of the program. For example, we are now able to introduce PRECEDE and FOLLOW between circuits that were initially allocated to different functions. Without whole program compaction these circuits had to necessarily communicate via a handshake.

#### Let-expressions

This is an idea by Scott Owens from the University of Utah. In our compilation, whenever we have the same function being called more than once, several instances of its corresponding circuit are generated for each call. Although this approach produces a fast circuit (as no hardware block is shared and no arbiter is needed), it also produces a large circuit.

One solution that can give more flexibility to the compiler is the introduction of let-expressions. A let-expression has the form (let  $v = e_1$  in  $e_2$ ) where v is a variable structure, i.e. it is either a single variable or, recursively, a non-empty tuple of "varstructs" (e.g. (x, (m, n), y)). How a let-expression is implemented as a circuit is shown below.

$$\vdash (\lambda inp. \text{ let } v = (f_1 \ inp) \text{ in } (f_2 \ (inp, v))) = \text{Seq } (\text{Par } (\lambda x. \ x) \ f_1) \ f_2$$

The designer can replace several calls to the same function by a single call. For example, the program below shows how three calls to the function inc are replaced by a single call using the variable y, thus preventing three circuit implementations of inc from being generated.

$$\vdash \text{ inc } n = n+1w$$

$$\vdash \text{ main } n = \text{ let } y = (\text{inc } n) \text{ in } (y+y+y)$$

We can still optimise the compilation of let-expressions. In the expression (let  $v = e_1$  in  $e_2$ ), if  $e_1$  is combinational, then the expression is synthesised into a circuit consisting of  $e_1$  driving wires corresponding to v that are inputs to the circuit corresponding to  $e_2$ . If  $e_1$  is not combinational, the usual compilation in terms of Seq and Par takes place. In the example above, if inc is not declared combinational, then main is compiled to a circuit with 30 components (10 of which are registers) and 28 variables, but if inc is declared to be combinational, then main compiles to a circuit with 7 variables and 9 components (2 of which are registers).

#### Results

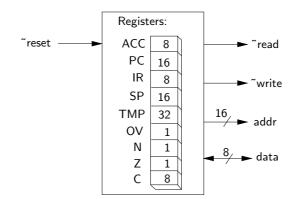

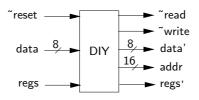

The optimisations presented above address two issues: the elimination of handshakes and the elimination of circuit duplication. The handshake elimination can sometimes produce aggressive optimisations in the sense that almost all handshakes are eliminated. The only exception is for handshakes that appear in the circuit REC. The optimisations reduce the size of the circuit and, by eliminating handshakes, minimise the clock ticks per computation. However there is a trade-off here as they also generate long combinational paths and eventually force the clock to slow down (the next section shows how the clock signal is introduced).

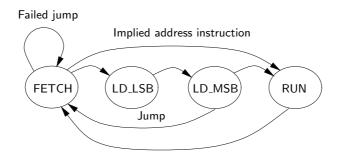

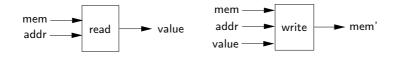

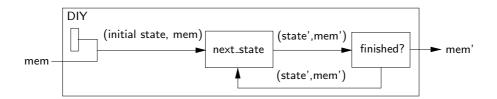

The user has control over most of the optimisations. Whole program compaction can be applied by using an alternative compiler called inlineCompile. A let-expression is just an extra language feature available to the user, and the primitive constructors of the language can be defined by the user, although the compiler initialises a default library which includes Seq, Par and Ite.