Technical Report

Number 660

**Computer Laboratory**

# Static program analysis based on virtual register renaming

Jeremy Singer

February 2006

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500

http://www.cl.cam.ac.uk/

#### © 2006 Jeremy Singer

This technical report is based on a dissertation submitted March 2005 by the author for the degree of Doctor of Philosophy to the University of Cambridge, Christ's College.

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

http://www.cl.cam.ac.uk/TechReports/

ISSN 1476-2986

#### Abstract

Static single assignment form (SSA) is a popular program intermediate representation (IR) for static analysis. SSA programs differ from equivalent control flow graph (CFG) programs only in the names of virtual registers, which are systematically transformed to comply with the naming convention of SSA. Static single information form (SSI) is a recently proposed extension of SSA that enforces a greater degree of systematic virtual register renaming than SSA. This dissertation develops the principles, properties, and practice of SSI construction and data flow analysis. Further, it shows that SSA and SSI are two members of a larger family of related IRs, which are termed virtual register renaming schemes (VRRSs). SSA and SSI analyses can be generalized to operate on any VRRS family member. Analysis properties such as accuracy and efficiency depend on the underlying VRRS.

This dissertation makes four significant contributions to the field of static analysis research.

First, it develops the SSI representation. Although SSI was introduced five years ago, it has not yet received widespread recognition as an interesting IR in its own right. This dissertation presents a new SSI definition and an optimistic construction algorithm. It also sets SSI in context among the broad range of IRs for static analysis.

Second, it demonstrates how to reformulate existing data flow analyses using new sparse SSI-based techniques. Examples include liveness analysis, sparse type inference and program slicing. It presents algorithms, together with empirical results of these algorithms when implemented within a research compiler framework.

Third, it provides the only major comparative evaluation of the merits of SSI for data flow analysis. Several qualitative and quantitative studies in this dissertation compare SSI with other similar IRs.

Last, it identifies the family of VRRSs, which are all CFGs with different virtual register naming conventions. Many extant IRs are classified as VRRSs. Several new IRs are presented, based on a consideration of previously unspecified members of the VRRS family. General analyses can operate on any family member. The required level of accuracy or efficiency can be selected by working in terms of the appropriate family member.

# Contents

| 1        | Intr | troduction 8                                                                                                                                               |   |  |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|

|          | 1.1  | About this Chapter                                                                                                                                         | 3 |  |

|          |      | 1.1.1 Objectives                                                                                                                                           | 3 |  |

|          |      | 1.1.2 Outline                                                                                                                                              | 3 |  |

|          |      | 1.1.3 Contributions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                | 3 |  |

|          | 1.2  | What is Static Analysis?                                                                                                                                   | ) |  |

|          | 1.3  | Motivation                                                                                                                                                 | ) |  |

|          |      | 1.3.1 Current Trends                                                                                                                                       | ) |  |

|          |      | 1.3.2 Discussion of Proebsting's Law 11                                                                                                                    | L |  |

|          | 1.4  | About this Dissertation                                                                                                                                    | 3 |  |

|          |      | 1.4.1 Objectives                                                                                                                                           | 3 |  |

|          |      | 1.4.2 Outline                                                                                                                                              | 3 |  |

|          |      | 1.4.3 Contributions $\ldots \ldots 14$                          | 1 |  |

| <b>2</b> | Bac  | kground 16                                                                                                                                                 | 3 |  |

|          | 2.1  | About this Chapter                                                                                                                                         |   |  |

|          |      | 2.1.1 Objectives $\ldots \ldots \ldots$    | 3 |  |

|          |      | 2.1.2 Outline                                                                                                                                              | 3 |  |

|          |      | 2.1.3 Contributions $\ldots \ldots \ldots$ | 3 |  |

|          | 2.2  | IR Taxonomy 17                                                                                                                                             | 7 |  |

|          | 2.3  | Sequential IRs                                                                                                                                             | 7 |  |

|          | 2.4  | Tree-Based IRs                                                                                                                                             | 3 |  |

|          | 2.5  | Early Graph-Based IRs                                                                                                                                      | 3 |  |

|          |      | 2.5.1 Control Flow Graph                                                                                                                                   | 3 |  |

|          |      | 2.5.2 Data Dependence Graph                                                                                                                                | ) |  |

|          | 2.6  | Recent Graph-Based IRs                                                                                                                                     | ) |  |

|          |      | 2.6.1 Augmented CFG                                                                                                                                        | ) |  |

|          |      | 2.6.2 Augmented DDG                                                                                                                                        | 2 |  |

|          | 2.7  | Complete Combination of Augmented CFG and Augmented DDG 24                                                                                                 | 1 |  |

|          | 2.8  | Alternative Classifications                                                                                                                                | 5 |  |

|          |      | 2.8.1 Sparseness                                                                                                                                           | 5 |  |

|          |      | 2.8.2 Live Range Splitting                                                                                                                                 | 5 |  |

|          |      | 2.8.3 Virtual Register Renaming                                                                                                                            | 3 |  |

|          |      | 2.8.4 Discussion                                                                                                                                           |   |  |

|          | 2.9  | IRs in this Dissertation                                                                                                                                   |   |  |

|          | 2.10 | Concluding Remarks                                                                                                                                         |   |  |

| 3 | Stat | tic Sin         | gle Information Form            | <b>29</b> |

|---|------|-----------------|---------------------------------|-----------|

|   | 3.1  | About           | t this Chapter                  | . 29      |

|   |      | 3.1.1           | Objectives                      | . 29      |

|   |      | 3.1.2           | Outline                         | . 29      |

|   |      | 3.1.3           | Contributions                   |           |

|   | 3.2  | Introd          | luction to SSI                  |           |

|   | 3.3  |                 | tion of SSI                     |           |

|   |      | 3.3.1           | Preliminary Remarks             |           |

|   |      | 3.3.2           | Actual Definition               |           |

|   |      | 3.3.3           | Comparison with Ananian         |           |

|   | 3.4  |                 | erties of SSI                   |           |

|   | 0.1  | 3.4.1           | Bounding the Blow-Up            |           |

|   |      | 3.4.2           | Pruning SSI                     |           |

|   | 3.5  |                 | ructing SSI                     |           |

|   | 0.0  | 3.5.1           | Pessimistic Construction        |           |

|   |      | 3.5.2           | Optimistic Construction         |           |

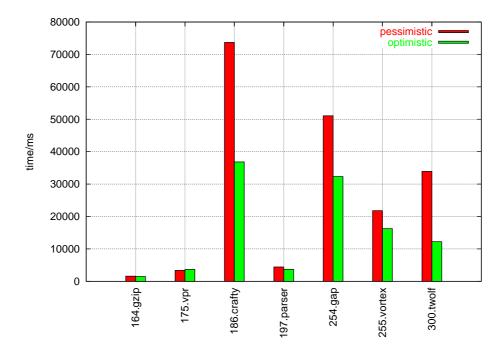

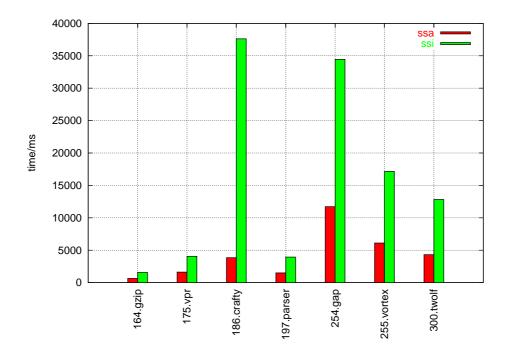

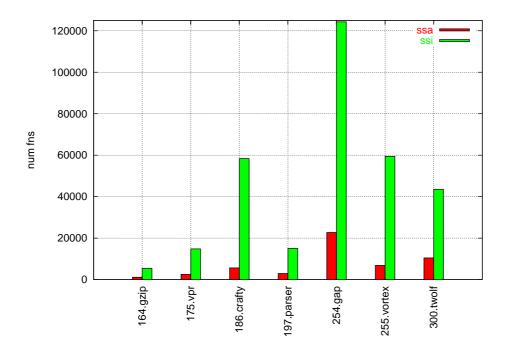

|   |      | 3.5.2           | Empirical Comparison            |           |

|   | 3.6  |                 | ed Work                         |           |

|   | 5.0  | 3.6.1           | Similar IRs                     |           |

|   |      | 3.6.2           | SSA and Construction Algorithms |           |

|   | 3.7  |                 | e Work                          |           |

|   | 3.8  |                 | uding Remarks                   |           |

|   | 0.0  | Conci           |                                 | . 52      |

| 4 | Dat  | a Flow          | v Analysis                      | 54        |

|   | 4.1  |                 | t this Chapter                  | . 54      |

|   |      | 4.1.1           | Objectives                      |           |

|   |      | 4.1.2           | Outline                         |           |

|   |      | 4.1.3           | Contributions                   | -         |

|   | 4.2  | Classi          | fication of Analysis Techniques |           |

|   |      | 4.2.1           | Fundamentals                    |           |

|   |      | 4.2.2           | Procedurality                   |           |

|   |      | 4.2.3           | Directionality                  |           |

|   |      | 4.2.4           | Intermediate Representation     |           |

|   |      | 4.2.5           | Flow-Sensitivity                |           |

|   |      | 4.2.6           | Context-Sensitivity             |           |

|   |      | 4.2.7           | Sparseness                      |           |

|   |      | 4.2.8           | Performance                     |           |

|   | 4.3  |                 | ant Propagation                 |           |

|   | 1.0  | 4.3.1           | Problem                         |           |

|   |      | 4.3.2           | Analysis Techniques             |           |

|   |      | 4.3.3           | Implementation Details          |           |

|   |      | 4.3.4           | Empirical Results               |           |

|   |      | 4.3.4<br>4.3.5  | Discussion                      |           |

|   |      | 4.3.6           | Related Work                    |           |

|   | 4.4  | 4.5.0<br>Livene |                                 |           |

|   | 4.4  |                 | Problem                         |           |

|   |      | <b>I.I.</b>     | 1 10010111                      | . 00      |

|   |            | 4.4.2          | Analysis Techniques                | 66        |

|---|------------|----------------|------------------------------------|-----------|

|   |            | 4.4.3          | Implementation Details             | 67        |

|   |            | 4.4.4          | Empirical Results                  | 68        |

|   |            | 4.4.5          | Discussion                         | 69        |

|   |            | 4.4.6          | Related Work                       | 70        |

|   | 4.5        | Type I         | Inference                          | 72        |

|   |            | 4.5.1          | Problem                            | 72        |

|   |            | 4.5.2          | Analysis Techniques                | 72        |

|   |            | 4.5.3          | Implementation Details             | 78        |

|   |            | 4.5.4          | Empirical Results                  | 78        |

|   |            | 4.5.5          | Discussion                         | 78        |

|   |            | 4.5.6          | Related Work                       | 79        |

|   | 4.6        | System         | natic Renaming                     | 80        |

|   | -          | 4.6.1          | Achieving Maximum Accuracy         | 80        |

|   |            | 4.6.2          | Maximum Accuracy Property          | 81        |

|   |            | 4.6.3          | Live Range Splitting Limit         | 81        |

|   |            | 4.6.4          | Matching IRs to Analyses           | 82        |

|   | 4.7        |                | lding Remarks                      | 83        |

|   |            |                | 0                                  |           |

| 5 | Slici      | 0              |                                    | 85        |

|   | 5.1        | About          | this Chapter                       | 85        |

|   |            | 5.1.1          | Objectives                         | 85        |

|   |            | 5.1.2          | Outline                            | 85        |

|   |            | 5.1.3          | Contributions                      | 86        |

|   | 5.2        | What i         | is Program Slicing?                | 86        |

|   | 5.3        | Interm         | ediate Representations for Slicing | 88        |

|   | 5.4        | CFG S          | Slicing                            | 88        |

|   | 5.5        | SSI Sli        | icing                              | 94        |

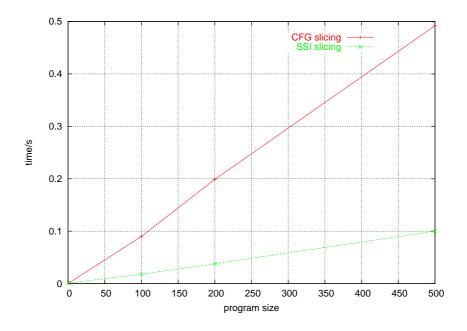

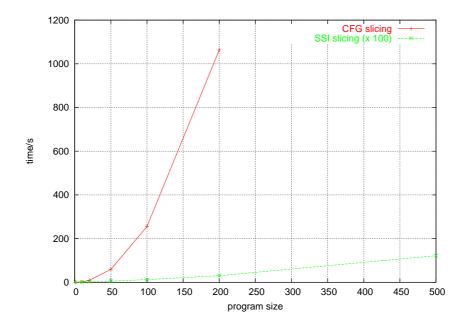

|   | 5.6        |                | ical Comparison                    | 96        |

|   | 5.7        |                | d Work                             |           |

|   |            |                | Dead Code Elimination and Slicing  |           |

|   |            |                | PDG versus SSI                     |           |

|   | 5.8        | Some 1         | Problems with SSI Slicing          |           |

|   |            | 5.8.1          | Too Little Control Dependence      | 105       |

|   |            | 5.8.2          | 1                                  | 107       |

|   | 5.9        | Possibl        | le Extensions                      | 115       |

|   | 5.10       | Conclu         | ıding Remarks                      | 116       |

| 6 | Into       | rnrogo         | edural Extensions                  | 18        |

| U | 6.1        | -              |                                    | 10<br>118 |

|   | 0.1        | 6.1.1          | Objectives                         |           |

|   |            | 6.1.1<br>6.1.2 | Objectives                         |           |

|   |            | 6.1.2          | Contributions                      |           |

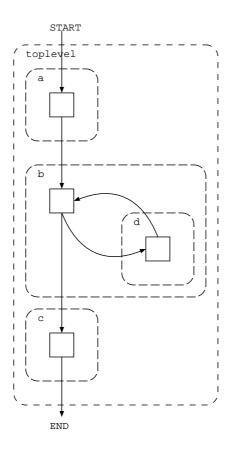

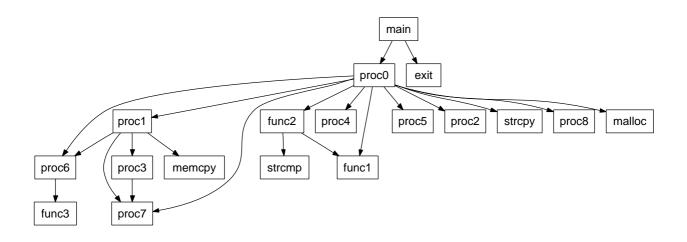

|   | 6.2        |                | lures                              |           |

|   | 0.2<br>6.3 |                |                                    |           |

|   | 0.0        |                | raph Approaches                    |           |

|   |            | 6.3.1<br>6.3.2 | Supergraphs                        |           |

|   |            | 0.0.2          |                                    | LZJ       |

|    | 6.4                          | Control Flow Refactoring Approaches         | 124         |  |

|----|------------------------------|---------------------------------------------|-------------|--|

|    |                              | 6.4.1 Deproceduralization                   | 126         |  |

|    |                              | 6.4.2 Functionalization                     | 129         |  |

|    |                              | 6.4.3 Empirical Comparison                  | 138         |  |

|    | 6.5                          | Concluding Remarks                          | 139         |  |

| 7  | Rev                          | ond SSI 1                                   | L <b>40</b> |  |

| •  | <b>D</b> c <b>y</b> .<br>7.1 | About this Chapter                          | -           |  |

|    |                              | 7.1.1 Objectives                            |             |  |

|    |                              | 7.1.2 Outline                               |             |  |

|    |                              | 7.1.3 Contributions                         |             |  |

|    | 7.2                          | SSA Extensions                              |             |  |

|    | •                            | 7.2.1 General Extensions                    |             |  |

|    |                              | 7.2.2 Feature-Specific Extensions           |             |  |

|    | 7.3                          | Family of Virtual Register Renaming Schemes |             |  |

|    |                              | 7.3.1 Attributes                            |             |  |

|    |                              | 7.3.2 Transformation Process                | 157         |  |

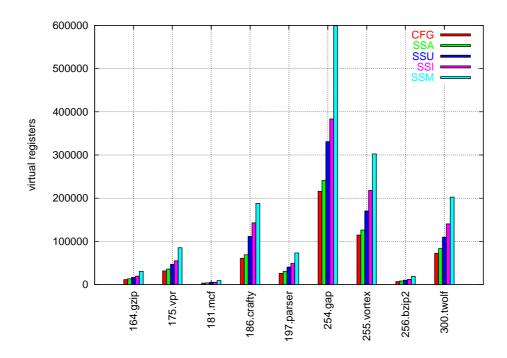

|    | 7.4                          | Empirical Study                             | 158         |  |

|    |                              | 7.4.1 Methodology                           | 158         |  |

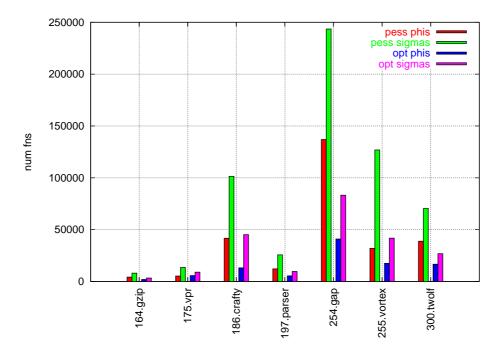

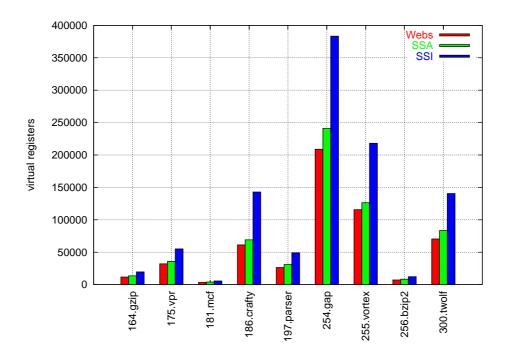

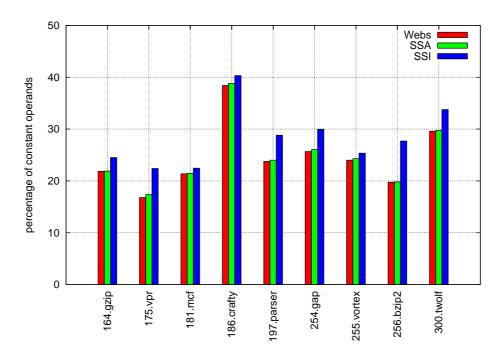

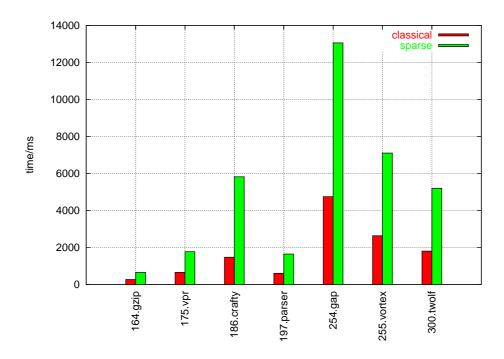

|    |                              | 7.4.2 Namespace Explosion                   | 159         |  |

|    | 7.5                          | Related Work                                | 160         |  |

|    |                              | 7.5.1 VRRS Frameworks                       | 160         |  |

|    |                              | 7.5.2 VRRS Specification Languages          | 161         |  |

|    | 7.6                          | Concluding Remarks                          | 161         |  |

| 8  | Con                          | clusions 1                                  | 63          |  |

|    | 8.1                          | Summary                                     | 163         |  |

|    | 8.2                          | Future Work                                 | 164         |  |

|    | 8.3                          | Final Remarks                               | 164         |  |

| A  | Glos                         | ssary 1                                     | 65          |  |

| Bi | Bibliography 168             |                                             |             |  |

# Chapter 1 Introduction

*Plug-and-play* intermediate representations enable greater flexibility in data flow analysis. This *plug-and-play* concept may be implemented for sparse data flow analysis frameworks by varying the degree of virtual register renaming in the intermediate representation.

# 1.1 About this Chapter

# 1.1.1 Objectives

This chapter has three primary goals.

- 1. It introduces the main themes of program analysis and defines relevant terms which will be used throughout this dissertation.

- 2. It shows that static analysis research is still necessary in the light of recent computer architecture and programming language developments.

- 3. It sets out the background context in which the thesis is to be developed and understood.

# 1.1.2 Outline

Section 1.2 defines what is meant by *static analysis*, which is the broad subject of this dissertation. Static and dynamic analysis are briefly contrasted. Section 1.3 argues that static analysis is more relevant than ever before, in the current computational climate. Finally Section 1.4 outlines the contents of this dissertation.

# 1.1.3 Contributions

Apart from general introductory material, there is one key point in this chapter. Section 1.3.2 gives a balanced and informed discussion of Proebsting's law, which is a contentious issue at present. We reach a different conclusion to Proebsting.

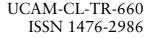

Figure 1.1: An overview of static and dynamic analysis and their interaction

# 1.2 What is Static Analysis?

The overall aim of program analysis is to identify and inspect the behaviour of subject programs. Program analysis techniques are classified as either *static* or *dynamic*. Static analysis occurs at compile time. Its objective is to predict how the analysed program will behave at runtime. In contrast, dynamic analysis occurs at runtime. Its objective is to report how the analysed program is behaving during runtime. Static analysis inspects a representation derived from the analysed program's source code. In contrast, dynamic analysis inspects a representation focuses entirely on static analysis, although some of the techniques may also be applicable to dynamic analysis. Figure 1.1 presents a high-level view of the differences between static and dynamic analysis as outlined above. It also depicts the ways in which static and dynamic analysis may interact. Results from static analysis can be provided as 'ahead-of-time calculated data flow facts' (hints) for dynamic analysis. Results from dynamic analysis can be used to anticipate 'likely runtime behaviour' (feedback) for static analysis. These trends are becoming increasingly apparent, as Section 1.3 explains.

Note that many systems for dynamic analysis, such as Valgrind [Net04], have tunable accuracy. The level of detail recorded in the program execution trace can be altered freely but systematically within a uniform framework. The work of this dissertation is directed toward providing the same kind of systematically tunable accuracy within a static analysis framework. This is accomplished by varying the amount of detail expressed in the program representation.

Formally, static analysis is able "to predict safe and computable approximations to the set of values and behaviours arising when the program is executed" [NNH99]. *Safe* results ensure that the analysis always errs on the side of caution, so it possibly overestimates what 'may' happen at runtime and underestimates what 'must' happen at runtime. *Computable* results ensure that the analysis always terminates eventually.

Aho et al [ASU86] provide the classic presentation of static analysis. More recent treatments are available according to taste. Muchnick [Muc97] is extremely detailed, Appel [App98a] is simple and concise, whereas Nielson et al [NNH99] are particularly formal.

# 1.3 Motivation

This section discusses the necessity for ongoing static analysis research. Section 1.3.1 examines the urgent need in the present circumstances. Section 1.3.2 refutes the suggestions that static analysis is stagnant and should be abandoned.

#### 1.3.1 Current Trends

There has never been a greater need for accurate and efficient static analysis than for optimizing compilers at the beginning of the 21st century. This section lists some compelling reasons.

- 1. Rumour suggests that the next generation of the industry standard compiler and systems performance benchmark suite, SPEC CPU 2005, will not permit feedback directed optimization techniques for the production of baseline performance measurements.<sup>1</sup> Feedback directed optimizations are presently permitted for SPEC CPU 2000 baseline measurements [Spe00b]. It appears that next generation compilers will be judged primarily on their static analysis capability, without the aid of additional information gleaned by feedback-directed techniques that incorporate dynamic analysis.

- 2. Despite the first point, there is an increasing level of synergy between static and dynamic analysis [Ern03]. This is largely fuelled by the growing popularity of just-in-time (JIT) compilation technology, for systems such as Java and .NET. Statically generated annotations (hints) may be inserted into the platform independent byte-code by the source to bytecode compiler. These hints enable the JIT compiler to optimize effectively at runtime. Azevedo et al [ANH99] describe such a system. Information revealed by a hint is normally too time-consuming for the JIT compiler to discover by itself at runtime. In this way, static analysis information may be used to improve the results of dynamic analysis. This is in contrast to feedback-directed optimization (outlined in the first point) in which dynamic analysis information is used to improve the results of static analysis.

- 3. The greatest incentive for high quality static analysis is the acceleration of hardware and software complexity. As both high-level source languages and low-level target languages become increasingly complicated, compilers must shoulder a growing burden of responsibility to handle the complex high-level source features, and to exploit

<sup>&</sup>lt;sup>1</sup>This information was personally communicated by Vivek Sarkar, Senior Manager of the Programming Technologies department at the IBM T. J. Watson Research Centre. I pursued the matter with several members of the SPEC CPU committee, but they were unable to confirm or deny the rumour.

the complex low-level target features. These issues are developed further in the next section.

#### 1.3.2 Discussion of Proebsting's Law

The popular interpretation of Moore's law [Moo65] is that microprocessor performance doubles every 18 months. Proebsting's law [Pro98] is a parody of Moore's law. Proebsting postulates that optimizing compiler technology improvements enable typical program performance to double every 18 years. The original basis for this claim was that optimizing compiler technology was approximately 36 years old (in 1998), and a typical C program for Intel's x86 architecture ran four times faster when compiled at maximum optimization level than when compiled without any optimization. Scott [Sco01] gives a more rigorous empirical justification of Proebsting's law. Similar observations hold for Java JIT compilation with the IBM Jikes RVM system [AAB+00]. Empirical data embedded in the source code (the VM\_CompilerDNA cost/benefit model for adaptive optimization on x86) shows that programs are expected to execute 5.5 times faster when compiled using the aggressive optimizing compiler instead of the baseline non-optimizing compiler.

This potentially depressing observation has led some faint-hearted static analysis researchers (including Proebsting himself!) to suggest that static analysis research has stagnated, and should be abandoned in favour of more fashionable avenues of programming language research, such as programmer productivity. However, Proebsting's conclusion is flawed for the reasons listed below. Actually, research into optimizing compilation and static analysis is more vital than ever before.

#### Speed is no Longer the Only Goal

Compiler analyses and optimizations are not always intended to improve the speed of output executable code. An increasing trend has been to optimize code for execution in resource-constrained environments [KG03]. Such optimizations may be intended to reduce executable code size, runtime memory footprint, or runtime power consumption, for instance. In these cases, the standard static analysis techniques are applicable, in order to acquire the data flow information necessary for optimization.

#### Complicated Technology Needs (and Breeds) Complicated Compilers

It can be argued that compiler developers do well to keep up with the rate of microprocessor speed advances, rather than fall behind! In order to advance processor speeds in accordance with Moore's law, major 'under-the-hood' architectural changes have taken place. The processors of today are very different from processors of 36 years ago! For example, compare the Intel Pentium 4 of 2004 with the DEC PDP-10 of 1968. The Pentium 4 manual [Int04] comprises 4 volumes, with 2282 pages in all. In contrast, the DECsystem-10 processor manual [DEC82] has only 514 pages. This comparison hardly begins to indicate the quantum leap of complexity in processor design over 36 years. A Pentium 4 processor has the following features:

- three levels of high speed memory cache,

- deeply pipelined execution system,

- branch prediction,

- hardware register renaming,

- out-of-order speculative execution system,

- superscalar instruction issue,

- hyperthreading capability.

It is obvious that modern compilers are targeting very different kinds of hardware, for which code generation is much more complicated. There are two more issues that increase the requirement for even more complex static analysis.

- 1. In a bid to increase processor speeds by cutting complexity, recent 'very long instruction word' and 'explicitly parallel instruction computing' architectures offload the responsibility for extracting parallel computations from the hardware at runtime onto the compiler at compile time. In effect, these architectures have the same powerful features as the Pentium class listed above, but none of the inbuilt hardware mechanisms for dependence resolution and conflict avoidance.

- 2. As processor clock speeds increase, memory latency becomes a greater problem. The optimizing compiler faces increasing pressure to produce code with good memory access performance, which again requires extremely accurate static analysis.

On a different level, increasingly complex high-level programming languages require increasingly complex static analysis support. The trend in software engineering has been to develop code using more high-level programming languages. Recent control flow features include exception handling, virtual method calling and multi-threading. Recent data flow features include objects and genericity. Compilers have to analyse much more complicated high-level programs than 36 years ago! Hence a 2004 C++ compiler is much more complicated than a 1968 BCPL compiler. Despite this increased complexity, users expect compiled code to be more efficient than ever before. Thus static analysis research is necessary for the efficient compilation of new generations of high-level constructs.

#### Static Analysis is Everywhere

Static analysis techniques that were originally deployed in optimizing compiler technology have now been transferred to other areas of computer systems. For instance, some compiler innovations have been incorporated directly into recent microprocessor hardware. A few examples are listed below.

• The technique of virtual register renaming has been popularized by static single assignment form (SSA) [CFR<sup>+</sup>91]. However, Cooper and Torczon [CT04] mention that register renaming had been used for static analysis prior to SSA. Register renaming is now performed directly in hardware to avoid unnecessary data dependences in out-of-order and superscalar processors. (Note that the major theme of this dissertation is concerned with virtual register renaming for static analysis!)

- Data dependence analysis has always been an essential element of any static analysis tools. However in addition, dynamic data dependence analysis is now commonly performed directly in hardware to support out-of-order and superscalar execution, which require the extraction of instruction level parallelism on-the-fly.

- The static technique of if-conversion [AKPW83] transforms control dependences into data dependences. This is now supported directly in hardware by many architectures, using predicate registers and conditional execution of all instructions.

In addition, many static analysis techniques invented originally for optimizing compilers are also used in program verification tools. These include the Microsoft SLAM project [BR02] and Metacompilation [HCXE02]. Such systems use static analysis (often combined with other techniques) to detect violations of specified or inferred protocols in program source code. Returning for a moment to the theme of static and dynamic analysis synergy, several verification systems use dynamic analysis to detect likely invariant candidates, then use static analysis to determine whether these candidates are genuine invariants [HL02, ECGN01].

Therefore static analysis is not limited to the compiler as it analyses and generates executable code. Static analysis principles are also used by the hardware on which the code is executed, and the verifiers with which the code is debugged.

# **1.4** About this Dissertation

#### 1.4.1 Objectives

This dissertation has two primary objectives.

- 1. It aims to demonstrate that static single information form (SSI) is a viable alternative to SSA and CFG (control flow graph) IRs for static analysis. The key point to demonstrate is the existence of a trade-off between accuracy and efficiency, dependent on the subject IR for static analysis. The analysis client has to decide where the balance lies before choosing the appropriate IR.

- 2. It aims to show that SSI and SSA are two members of a larger family of related IRs. This family requires exploration and formalization. The final result should be a sliding scale of IRs; with high accuracy but low efficiency analyses at one end of the scale, and low accuracy but high efficiency analyses at the other end. SSA and SSI must be somewhere in the middle of this scale.

#### 1.4.2 Outline

Chapters 1 and 2 provide background material relating to static analysis and intermediate representations. After this, the dissertation falls into two main divisions.

The first part (Chapters 3–6) provides evidence in support of the first objective. Chapter 3 defines SSI, describes how to compute SSI from CFG, and contrasts SSI with both CFG and SSA. Chapter 4 demonstrates how to use SSI for several standard data flow analyses. The results clearly show that SSI enables more accurate analysis results than

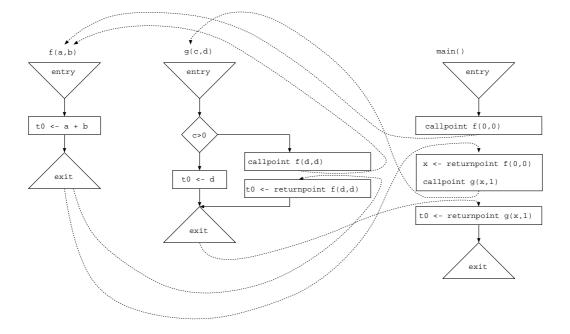

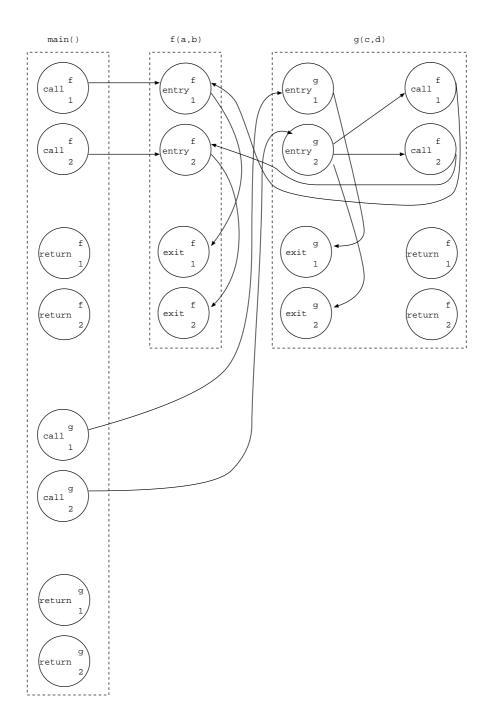

SSA. Chapter 5 demonstrates how to use SSI for program slicing. SSI-based slicing gives greater efficiency over CFG-based slicing, and the same level of accuracy. Chapter 6 discusses extending the scope of SSI from single-procedure to whole-program. It shows that SSI can be used in four different ways to perform interprocedural analysis. In some of these approaches, SSI is a straight replacement for CFG or SSA. In other approaches, SSI has special properties that enable different kinds of interprocedural analysis altogether.

The second part of this dissertation (Chapter 7) presents the relevant material to support the second objective. It reviews and classifies various existing SSA extensions, then presents the family of *virtual register renaming schemes* to which SSA and SSI belong, together with many other IRs. Note that Chapter 7 is a natural development of the theme that is first introduced in Chapter 4, regarding the trade-off between accuracy and efficiency for data flow analysis, based on the selected IR for that analysis.

Finally Chapter 8 concludes.

#### 1.4.3 Contributions

This dissertation makes four significant contributions to the field of static analysis research. These are listed below. Chapters 3–6 deal with the first three contributions. Chapter 7 deals with the fourth contribution.

- 1. It develops the SSI IR. Although SSI was introduced five years ago [Ana99], it has not yet received widespread recognition as an interesting IR in its own right. This dissertation presents a new SSI definition, construction algorithm and a number of applications. It also sets SSI in context among the broad range of compiler IRs.

- 2. It demonstrates how to perform existing static analyses using new, SSI-based techniques. Examples include live variables analysis, sparse type inference and program slicing.

- 3. It provides the first large-scale empirical evaluation of the merits of SSI for data flow analysis. Several studies in this dissertation compare SSI with SSA, CFG, and other existing IRs.

- 4. It identifies a family of virtual register renaming schemes, which are all CFG-like IRs. It shows how generic analyses can operate on any member of the family. The required level of accuracy or efficiency can be selected by working in terms of the appropriate IR family member.

These contributions back up the underlying thesis of this dissertation, which is repeated below for emphasis.

*Plug-and-play* intermediate representations enable greater flexibility in data flow analysis. This *plug-and-play* concept may be implemented for sparse data flow analysis frameworks by varying the degree of virtual register renaming in the intermediate representation.

#### A Note on Terminology

A few explanations of terminology are necessary at this stage, in order to clarify the above thesis. A *virtual register* is an abstract location that can hold a single scalar value. Virtual registers are introduced by a compiler when it generates intermediate code. They represent placeholders for physical registers or memory locations, by which they are replaced at code generation time.

When the thesis refers to *plug-and-play*, this is at the abstract level of data flow analysis algorithm rather than at the coal-face of actual implementation code. *Flexibility* mean varying levels of accuracy and efficiency, in this dissertation. Other parameters are possible however.

Many other terms are defined in the glossary at the end of the dissertation. Common acronyms are also expanded in the glossary.

# Chapter 2

# Background

This chapter presents a brief history of static analysis. It concentrates on the IRs in general rather than any particular analysis or transformation.

# 2.1 About this Chapter

#### 2.1.1 Objectives

This chapter aims to review the field of IRs for static analysis. Over the last 50 years, many IRs have been developed and deployed in compilers. Since the research area is so large, the study must be a high-level overview. It will focus on a few IRs that are particularly relevant to modern static analysis systems. This chapter will briefly discuss the concept of *virtual register renaming*, which is the main theme of the dissertation.

#### 2.1.2 Outline

Section 2.2 outlines the IR taxonomy. Sections 2.3 to 2.7 go through different taxonomy domains in detail. The order of presentation is from simplest to most complex IR, which (perhaps unsurprisingly) is also chronological. Section 2.8 describes several alternative methods for classifying IRs, including the important concepts of sparseness, live range splitting and virtual register renaming. Section 2.9 lists the different IRs that are covered in this dissertation, principally in their relation to static single information form. Finally Section 2.10 concludes.

#### 2.1.3 Contributions

There are two key contribution in this chapter.

- 1. It presents a new taxonomic division of IRs. This is necessary in order to specify precisely the family of IRs that this dissertation will investigate.

- 2. It clarifies the relationship between live range splitting and virtual register renaming.

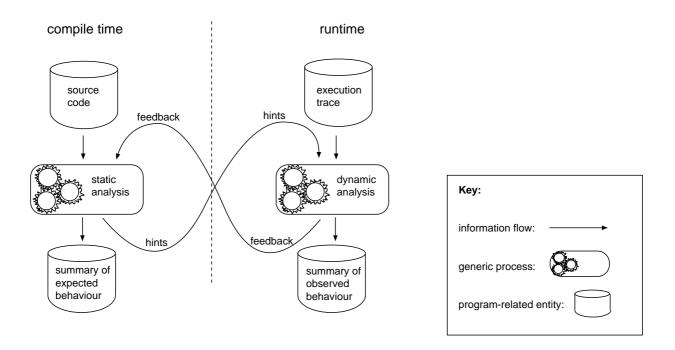

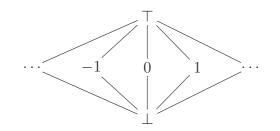

Figure 2.1: Taxonomy of IRs, region of interest is circled

# 2.2 IR Taxonomy

Figure 2.1 presents the IR taxonomy. The top-level division is based on a measure of the explicitly modelled relationships between program entities. These relationships will probably correspond to pointers in the underlying data structures. So, the top-level divides IRs into three domains (sequential, tree-based and graph-based). Subsequent sections describe each of these domains, in chronological order of their invention. Only the graph-based domain is expanded further in Figure 2.1, since the other domains are irrelevant for this dissertation. The circled region of the taxonomy indicates the taxonomic class of the IRs investigated in this dissertation.

Note that a graph-based IR may have an underlying sequential model of the program. For instance, control flow graphs often consist of basic blocks of sequential machine instructions. Thus, an IR may combine elements from different branches of the taxonomy. Analyses and transformations on this kind of hybrid IR should maintain consistency between these diverse elements at all times.

## 2.3 Sequential IRs

Assembly language was devised in the 1950's. This is the first sequential IR. In general, there is a one-to-one mapping between assembly language opcodes and machine instructions. This kind of IR is extremely low-level. Control flow is specified by a program counter register. Data flow is specified by value movement between physical machine locations.

Abstract assembly language for virtual machines is used in many low-level analyses. There are several different varieties. The most popular sequential IRs are stack-based and three-address code. Early examples of stack-based IRs include Pascal P-code [Nel79] and BCPL OCode [RWS79]. Java JVM code has sparked a recent revival in this area. Three-address code is epitomized by Muchnick's MIR [Muc97] and Cooper and Torczon's ILOC [CT04]. The GCC RTL IR is another good example.

Code generators perform peephole optimizations on sequential IRs and then macro-

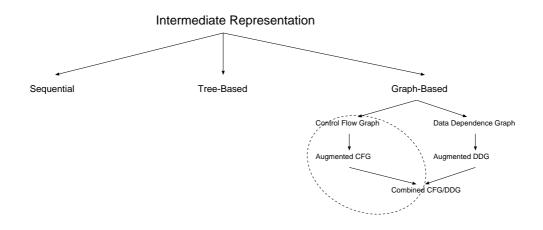

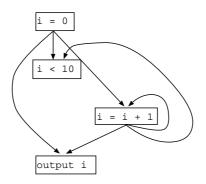

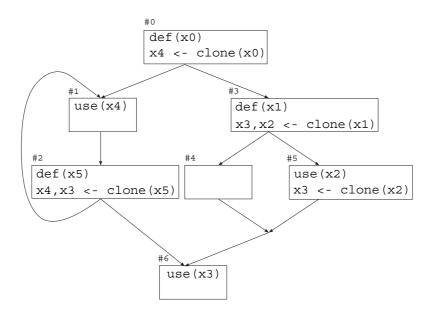

Figure 2.2: Example CFG program

expand each instruction into actual machine code.

# 2.4 Tree-Based IRs

Most early compilers were extremely simple. These date from the 1960's. The input programs were written in basic high-level languages such as Fortran and COBOL. Such compilers operate in a syntax-directed fashion, parsing source code to produce abstract syntax trees (ASTs). Basic tree-rewriting optimizations are performed, before the ASTs are transformed into the target assembly or machine code. However, ASTs provide no scope for more powerful global data flow analysis [Sch73]. (Note that global analysis is now referred to as *intraprocedural* analysis.) A richer IR is required for such more complex kinds of analysis. Generally, modern compilers generate ASTs from source code, then use this information to construct a graph-based IR, as described in the next section.

# 2.5 Early Graph-Based IRs

In the 1970's, as computing technology became more powerful, larger memory and faster processing speeds enabled more complex kinds of IRs. A typical compiler from this era transforms ASTs into a graph-based representation, which is then employed as the standard IR for further analysis and transformation, culminating in code generation.

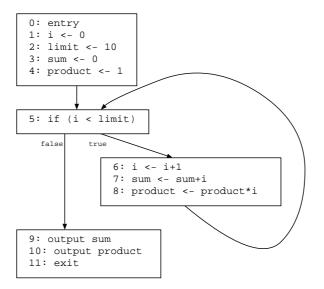

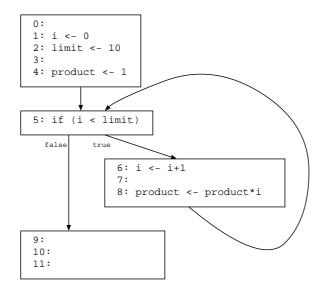

#### 2.5.1 Control Flow Graph

The most widely used graph-based IR is the control flow graph (CFG). CFG is the basis for almost all classical data flow analysis techniques. (In the context of static analysis, the classical age runs from 1970–1990.) The classical description of CFG is given by Aho et al [ASU86]. Nielson et al [NNH99] present a more rigorous overview. Figure 2.2 shows an example CFG program. Formally, a CFG  $G = (N, E, n_{entry}, n_{exit})$  with  $n_{entry}, n_{exit} \in N$  and  $E \subseteq N \times N$ . N is the set of nodes in G.  $n_{entry}$  is the distinguished entry node for G. It has no predecessors.  $n_{exit}$  is the distinguished exit node for G. It has no successors. CFG is an intraprocedural representation, so  $n_{entry}$  corresponds to the unique procedure entry point and  $n_{exit}$  corresponds to the unique procedure exit point. Each node is a basic block. A *basic block* is a sequence of consecutive computational instructions,  $i_1, \ldots, i_m$  with the property that every instruction  $i_j$  has a unique successor instruction  $i_{j+1}$  for  $1 \leq j < m$ and every instruction  $i_k$  has a unique predecessor instruction  $i_{k-1}$  for  $1 < k \leq m$ . Note that in the simplest case, each instruction can map to a unique basic block. This dissertation assumes that the computational instructions are low-level machine instructions, operating in terms of virtual registers and abstract memory locations. This is similar to the sequential IRs outlined in Section 2.3. E is the set of directed edges in the CFG. An edge  $e = (n_i, n_j)$  indicates that control may flow directly from the last instruction of  $n_i$ to the first instruction of  $n_j$  during program execution.

This dissertation imposes the standard CFG reachability constraint: For all nodes  $n \in N$ , there exists a control flow path from  $n_{\text{entry}}$  to n; for all nodes  $n \in N$ , there exists a control flow path from n to  $n_{\text{exit}}$ . An arbitrary CFG can be rewritten to this standard form using two techniques.

- 1. Unreachable code elimination removes nodes that are not on a control flow path from  $n_{\text{entry}}$ .

- 2. Insertion of 'impossible' loop exit edges breaks infinite loops that are not on a control flow path to  $n_{\text{exit}}$ . Such impossible edges may be required for data flow analysis, even if the relevant loops will never terminate at runtime [HS02].

There is a vast body of literature dealing with static analysis of CFG. CFG is the standard IR used in monotone data flow frameworks, which for many years has been the prevalent compiler technique for analysis and optimization. Refer to the bibliographic notes at the end of Chapter 10 in the Dragon book [ASU86] for more details.

CFG is an executable representation, since it contains enough information to permit execution by simple interpretation. It follows that code generation from CFG is straightforward. Each node corresponds to a basic block of code, and each edge corresponds to a jump (program counter update) to a new block of code.

#### 2.5.2 Data Dependence Graph

The data dependence graph (DDG) is sometimes also known as the data flow graph. DDG is based on an entirely different model of computation from CFG, in that it is data flow oriented, rather than control flow oriented. DDG has been widely investigated in the static analysis research community [AK02].

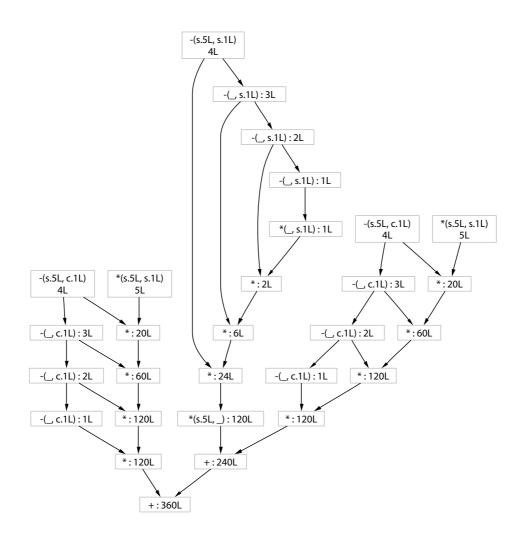

DDG represents the flow of values from their creation (definition site) to their consumption (use site). Figure 2.3 shows an example DDG program. This is the DDG version of the CFG program in Figure 2.2.

Formally, a DDG G = (N, E) where  $E \subseteq N \times N$ . N is the set of nodes in the DDG. A DDG node generally corresponds to a single instruction from a CFG basic block. Sometimes, DDG nodes may represent more primitive operations and operands. E is the set of directed edges in the DDG. Each edge  $(n_i, n_k)$  connects a value creation

Figure 2.3: Example DDG program

to a value consumption. A DDG edge generally corresponds to a virtual register use in a CFG basic block.

DDG specifies certain constraints on the ordering of operations at runtime as dictated by the data flow behaviour of a program. However DDG does not fully capture the control flow of a program. Thus it is not an executable representation as it stands. It is possible to convert control flow information into data dependence information (using if-conversion [AKPW83]). Nevertheless it is still necessary to linearize the DDG code back into sequential control flow oriented code at the code generation phase.

DDG is commonly used in compilers for instruction scheduling tasks such as loop reordering, auto-parallelization, and code generation for a pipelined architecture or a multiple issue architecture. Actually, most optimizing compiler transformations require dependence information [BGS94].

## 2.6 Recent Graph-Based IRs

Since the late 1980's, newly developed IRs have had a hybrid form, incorporating elements of both CFG and DDG. This section classifies these hybrid IRs into either augmented CFG or augmented DDG. This is a new division proposed in this dissertation, but it should seem intuitively appealing.

#### 2.6.1 Augmented CFG

Many more recent IRs resemble CFG with varying quantities of supplementary data dependence information. The first such IR was CFG supplemented by def-use chains [ASU86], which are edges that directly connect virtual register definitions to virtual register uses. A *def-use chain* connects a single definition d of virtual register x to all points  $u_i$  that use x, such that each  $u_i$  is reached by d. A definition d of virtual register x reaches a point p if there is a control flow path from d to p, such that x is not redefined along that path. A *use-def chain* is the dual of a def-use chain. A use-def chain connects a single use u of virtual register x to all reaching definition sites  $d_i$  that define x.

#### Dependence Flow Graph

The dependence flow graph (DFG) [PBJ<sup>+</sup>91, JP93] is an improved version of def-use chaining. DFG has explicit control flow edges, and explicit def-use edges, but def-use edges are factored at control flow split and merge points, which reduces the expense of def-use chaining. Later chapters describe different aspects of DFG in further detail.

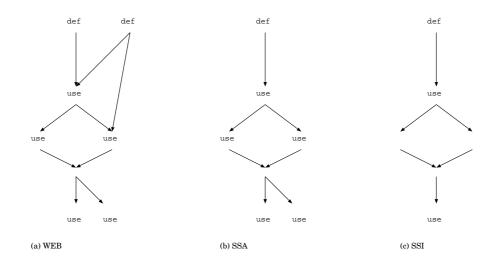

#### WEB

Def-use-use-def-webs form (WEB) is another extension of def-use chaining. Muchnick [Muc97] describes WEB, and shows how it can be useful for register allocation by graph colouring. A *def-use-use-def-web* is the maximal union of def-use chains that share a common use, i.e. def-use chains  $c_1$  and  $c_2$  are in the same web if they both contain a common use, or if there is another chain  $c_3$  that contains a use in common with  $c_2$  and  $c_3$  is in the same web as  $c_1$ . Rather than constructing explicit WEB data structures, WEB information can be made implicit in the CFG by *renaming* virtual registers so that they have a common name if and only if they belong to the same web. The Sable Java static analysis suite [QHV00] uses WEB in its Jimple IR.

#### Static Single Assignment Form

The most popular augmented CFG IR is static single assignment form (SSA) [CFR<sup>+</sup>91]. SSA encodes data dependence information in the names of virtual registers. Thus, SSA is a CFG with def-use relationships encoded in the virtual register naming convention, like WEB. In a similar way to DFG, def-use chains are factored at control flow merge points (but not split points) to avoid expense [SGW94]. The underlying principles of SSA are developed and extended throughout this dissertation, so it is important to clarify SSA fully in this section.

SSA is CFG with an extra constraint: Each virtual register must have a unique (hence single) definition point (hence assignment) in the program text (hence static). For a SSA program to be valid, each unique definition of a virtual register v must dominate all uses of v. Informally, this means that every virtual register must be defined before it can be used. The concept of dominance is defined formally in Section 3.3.

Two steps are required to transform an arbitrary CFG program so that it satisfies the SSA property:

- 1. insert pseudo-definitions at control flow merge points in CFG where multiple definitions for a single virtual register will converge, and

- 2. rename virtual registers so that each definition creates a new name.

Section 3.6.2 provides more information about typical SSA construction algorithms.

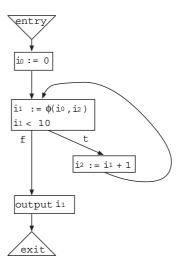

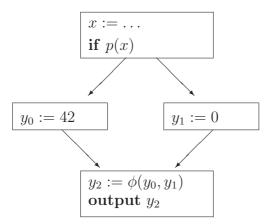

SSA pseudo-definitions are called  $\phi$ -functions. They always occur at the start of basic blocks. If a basic block *b* has *n* control flow predecessors, then a  $\phi$ -function *p* belonging to *b* will have *n* source operands. Generally, *p* takes the value of its *i*th source operand when control flows to basic block *b* from *b*'s *i*th predecessor block. Because of this dependence on control flow information,  $\phi$ -functions are not referentially transparent, or directly interpretable. Some additional representation of control flow information is

Figure 2.4: Example SSA program

necessary to support redundancy elimination of  $\phi$ -functions [TP95], or SSA interpretation [vWF04].

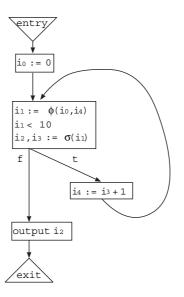

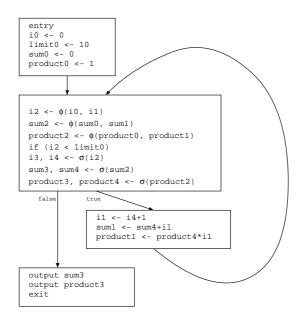

Figure 2.4 shows an example SSA program. This is the SSA version of the CFG program in Figure 2.2.

The seminal description of SSA is by Cytron et al [CFR<sup>+</sup>91]. They state that SSA concepts originated in the early work of Shapiro and Saint [SS70]. SSA is the basis for many optimizations, including constant propagation [WZ91], value numbering [RWZ88], and partial redundancy elimination [KCL<sup>+</sup>99].

Many modern compilers use SSA as their primary IR for static analysis. These include GNU's GCC [Nov03] and Harvard's Machine SUIF [Hol01]. Some JIT compilers also use SSA for heavyweight on-the-fly analysis and optimizations, including Sun's Java HotSpot [Sun99] and IBM's Java Jikes RVM [AAB+00].

SSA is sometimes referred to as 'factored use-def chains' representation [SGW94]. This is because uses can only be reached by one definition in SSA. If a use was reached by more than one definition in the original CFG program, then those multiple reaching definitions are factored into one definition at a  $\phi$ -function in the SSA program. Each SSA use-def chain is a fragment of a use-def chain from the original program. SSA  $\phi$ -functions mark where an original use-def chain has been split. Thus a WEB program can be constructed from a SSA program by renaming virtual registers such that for each  $\phi$ -function  $r_0 \leftarrow \phi(r_1, \ldots, r_n)$  in the SSA program, all occurrences of  $r_0, r_1, \ldots, r_n$  must be replaced by a fresh virtual register name r in the new WEB program; also all  $\phi$ -functions must be removed.

#### 2.6.2 Augmented DDG

#### Program Dependence Graph

The most notable augmented DDG representation is the program dependence graph (PDG) [FOW87]. PDG represents a program as a graph in which nodes are instructions, and directed edges represent dependences between instructions. There are two different

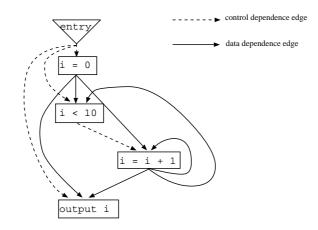

Figure 2.5: Example PDG program

types of edge: data dependence and control dependence. Data dependence edges are the same as edges in the original DDG. Actually, there are three different varieties of data dependence edge, as Section 5.7.2 explains in detail. DDG edges correspond to PDG flow dependence edges. Control dependence edges represent essential control flow ordering information. A control dependence edge  $(n_1, n_2)$  indicates that the execution of  $n_2$  depends on the outcome of  $n_1$ , so  $n_1$  must be executed before a decision can be made about whether to execute  $n_2$ . Parallelism is exposed in the PDG, since the only constraints on code ordering are indicated by the dependence edges. Unlike CFG, there are no artificial control flow constraints imposed by the need for a total ordering on instructions.

PDG is generally constructed from a program in CFG form. Data dependence edges are calculated using standard data flow analysis to determine reaching definitions information. Control dependence edges are calculated using dominance information. Figure 2.5 shows an example PDG program. This is the PDG version of the CFG program in Figure 2.2.

Ferrante et al define PDG, give an algorithm for its construction and discuss several applications [FOW87]. Cartwright and Felleisen develop a formal PDG semantics [CF89]. Ramalingam and Reps have a similar semantic formalism [RR89]. There are several PDG-based compilers (for instance, *pdgcc* [NP94]) developed for research purposes, but PDG does not seem to have been adopted by the mainstream compiler community. The primary PDG application at present is program slicing, which Chapter 5 describes in detail.

#### **Program Dependence Web**

The program dependence web (PDW) [BMO90] is presented as an extension to PDG that can be directly interpreted. PDW also incorporates single-assignment ideas from SSA, by representing program instructions in gated single assignment form (GSA). GSA is similar to SSA, except that each pseudo-definition function that merges multiple incoming definitions is *gated*, i.e. it has an extra argument that specifies which of the source operands should be assigned to the destination operand. This simplifies the presentation of control dependence, and enables efficient PDW interpretation and code generation. GSA is also developing as a distinct IR from PDW [Hav93, TP95].

#### Value Dependence Graph

The value dependence graph (VDG) [WCES94] is a functional IR that expresses computation solely as value flow. CFG-based IRs are statement based and name all values. PDG and PDW do the same. In contrast, a VDG program only specifies the flow of values through a computation. There is no superfluous information concerning names, or the order in which values are computed. (In effect, VDG edges correspond to uses of CFG virtual register names.) VDG has a demand-based semantics, so a value is only computed if it is needed by another computation.

The value state dependence graph (VSDG) [JM03] combines VDG and GSA. VSDG also has state dependence edges, to enforce sequentialized computation. These can be used to express store dependencies (ordering of writes to memory) as well as loop termination dependencies (to ensure that a non-terminating loop can cause the program to loop forever, even when the final result is not data dependent on any values computed by the loop). In addition, state dependence edges can be used to model artificial constraints on control flow. Thus it is possible to create a CFG-like total ordering on operations in the program.

# 2.7 Complete Combination of Augmented CFG and Augmented DDG

The augmented CFG IRs in Section 2.6.1 add data dependence information to CFG. The augmented DDG IRs in Section 2.6.2 add control flow information to DDG. At this point, an obvious question arises: Is there a least upper bound (lub) for these hybrid IRs? If so, what this lub IR? There appear to be three distinct relations between nodes, where nodes are either instructions or values.

- 1. The *control flow* relation, epitomized by CFG edges.

- 2. The *data dependence* relation, epitomized by DDG edges.

- 3. The *control dependence* relation, epitomized by PDG control dependence edges.

Note that control dependence information is distinct from control flow information. While it is true that control dependence can be computed from a knowledge of the control flow relation, this computation is expensive, therefore it may be best to factor this computation into the IR construction costs.

So, the lub IR must encapsulate all three kinds of relation between nodes. *Static single information form* (SSI) is such an IR. Chapter 3 introduces SSI properly. SSI encodes control flow explicitly using edges, in the same way as SSA and CFG. So at first sight it appears that SSI is simply another augmented CFG IR. SSI also encodes data dependence implicitly in its virtual register naming convention, in the same way as SSA. However SSI also encodes control dependence implicitly in its virtual register naming convention. Chapter 5 gives full details of this encoding. So, SSI is one instance of this lub. Most of this dissertation focuses on the the characteristics of SSI, and SSI-based analysis.

# 2.8 Alternative Classifications

The top-level division for the taxonomy presented in Section 2.2 may seem arbitrary. It is similar to the scheme suggested by Cooper and Torczon [CT04]. However, there are many other classifiers for IRs. This section briefly reviews several alternative classifiers and shows how they relate to the IRs in this dissertation.

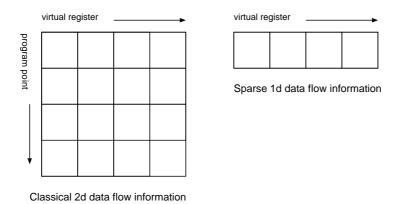

#### 2.8.1 Sparseness

In recent years, *sparse* IRs have become popular in the static analysis community. Broadly speaking, a sparse IR connects data flow information creation sites (generally referred to as definitions, since most sparse analyses are forward, virtual register based analyses) directly to data flow information consumption sites (generally referred to as uses). Analysis of sparse IRs is therefore extremely efficient, since analyses only compute data flow information exactly when it is needed and save it exactly where it is needed. This is very different to the dense, or *classical*, data flow analysis techniques described by Aho et al [ASU86].

Ruf [Ruf95b] distinguishes between analysis-specific and general sparse IRs

- Analysis-specific sparse IRs are specialized to handle only one particular data flow analysis. They do not retain the full semantics of the original program, rather they only represent sufficient information to model the particular data flow properties under consideration. The sparse evaluation graph [CCF91] is an example analysis-specific sparse IR.

- General sparse IRs completely describe a program's behaviour, since they retain the full semantics of a program's execution. Any data flow analysis can be applied to a general sparse IR. WEB SSA and SSI are all examples of general sparse IRs.

This dissertation focuses on general sparse IRs.

## 2.8.2 Live Range Splitting

A virtual register v is *live* at entry to node n if there is a control flow path from n to some other node which uses v, and there is no definition of v along that path. A virtual register v is live along edge e if v is live at entry to the destination node of e. Let G be the subgraph<sup>1</sup> ( $V_L, E_L$ ) of CFG nodes and edges where v is live. Then each connected component within G comprises a distinct *live range* of v. The notion of live range does not appear to be clearly defined in the literature. Whenever this dissertation refers to a live range, it conforms to the above definition.

Live range splitting [CH90] enables reasoning about virtual registers at a finer granularity than would be possible if the original high-level names were retained. Both register allocation and data flow analysis can be improved by this method. Briggs' empirical study shows that register allocation can be ameliorated since a greater degree of live range splitting enables better packing of registers during the colouring phase [Bri92]. Disjoint live

<sup>&</sup>lt;sup>1</sup> Technically G is not a graph since  $E_L \not\subseteq V_L \times V_L$ , but G becomes a graph by forming the closure:  $(V_L \cup source(E_L), E_L)$ , where  $source(E_L) = \{v_1 | (v_1, v_2) \in E_L\}$ . Note that Alan Mycroft helped me to formulate this definition.

ranges of the same variable have different names in the normalized form, and thus each can be allocated a different physical register. This reduces the range over which a single virtual register has to map onto a fixed physical register, easing register pressure. However, reduced register pressure is achieved at the cost of using a larger number of virtual registers during allocation. An increased number of virtual registers degrades the efficiency of the allocation process.

Live range splitting is also beneficial for sparse data flow analysis. Sparse data flow analysis generally associates information with a particular live range, rather than with a particular CFG node. Empirical results in this dissertation show that a greater degree of live range splitting enables a finer granularity of analysis precision. In a sense, this is a generalization of Briggs' observation for register allocation. We generalize 'register colour' to generic data flow information. However, Section 4.6.1 argues that for every data flow analysis, there is 'saturation point' in live range splitting. Beyond this point, further live range splitting cannot improve the accuracy of sparse analysis.

Note that the process of live range splitting is generally carried out by *virtual register* renaming. The next section examines this topic in some detail.

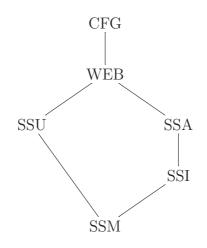

#### 2.8.3 Virtual Register Renaming

The concept of virtual register renaming is most important in this dissertation. WEB, SSA and SSI are examples of virtual register renaming schemes (VRRSs), with particular constraints to satisfy. However there are many other VRRSs belonging to the same family. These are all augmented CFG IRs, with extra information encoded in the virtual register naming convention. Specific pseudo-definitions (like SSA  $\phi$ -functions) may be required with different properties to handle the idiosyncrasies of each particular VRRS.

If live ranges are modelled so that each live range has a distinct virtual register name, then virtual register renaming enables two kinds of live range splitting. First, virtual registers may be renamed so that each definition is an initial point of a live range. This prevents definitions of the form  $v \leftarrow f(v)$ , that would extend the duration of the live range of v. (WEB performs only this kind of live range splitting.) Second, an existing live range may be split into two or more subranges by inserting an appropriate pseudo-definition (effectively one or more virtual register clone operations) at a point within the existing live range. (SSA and SSI perform both kinds of live range splitting.) WEB, SSA and SSI IRs all have a one-to-one mapping between virtual register names and live ranges. Thus sparse data flow analysis for these IRs associates information with each virtual register.

#### 2.8.4 Discussion

This section classifies the different IRs in terms of the shapes of live ranges enforced. WEB allows multiple definitions and multiple uses in a single live range. So a WEB live range may have multiple initial points in the CFG and multiple terminal points. SSA restricts live ranges to a single definition, but multiple uses are allowed. So a SSA live range must have a single initial point and may have multiple terminal points. SSI restricts live ranges to a single definition, and a linear sequence of uses such that if the definition is executed, all the uses will be executed as well. So a SSI live range looks like a single-entry-single-exit region [JPP93] in the CFG, with the single initial point being the definition, and the

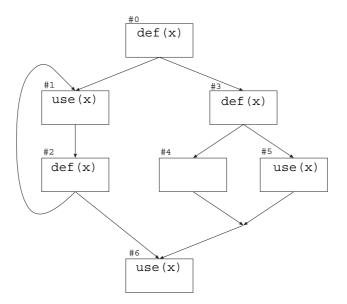

Figure 2.6: Example live ranges in each sparse IR

single terminal point being the last use. Figure 2.6 shows an example live range in each sparse IR.

With reference to the alternative classifiers outlined above, this dissertation concentrates on general sparse IRs that perform live range splitting via virtual register renaming. Data flow analysis on these IRs achieves sparseness by associating data flow information with live ranges (equivalently, virtual register names, since each name encapsulates a static single live range).

# 2.9 IRs in this Dissertation

This dissertation explores augmented CFG IRs, particularly those that encode additional information by virtual register naming conventions like SSA. The first part of the dissertation (Chapters 3–6) concentrates on *static single information form* (SSI), which is an extension of SSA. The second part of the dissertation (Chapter 7) shows that both SSA and SSI are instances of a more general family of virtual register renaming schemes (VRRSs).

There is no single 'related work' section, comparing SSI with existing IRs. Instead, each chapter compares SSI with relevant IRs at that point. A full list of comparisons is given below.

| SSI versus                 | Chapter(s) |

|----------------------------|------------|

| SSA                        | 3, 4       |

| CFG                        | 3, 4, 5    |

| WEB                        | 4          |

| PDG                        | 5          |

| DFG                        | 3, 5       |

| continuation passing style | 6          |

| all VRRSs                  | 7          |

# 2.10 Concluding Remarks

To avoid unnecessary complication, this chapter has concentrated on the character of the actual IRs used for static analysis, rather than the details of any particular analysis. Other parts of this dissertation adopt the same policy, most notably Chapter 6. In a sense, each IR determines the style of analysis that can be performed on that IR. The details should be in the IR itself, and the actual analysis simply leverages the information provided by the IR. As Raymond says [Ray99], "Smart data structures and dumb code works a lot better than the other way around."

Nevertheless, a static analysis is characterized by more than the IR in isolation. A *data flow framework* specifies all the factors that might affect the accuracy and efficiency of an analysis. This dissertation seeks to avoid lengthy discussion of the framework details except where absolutely necessary. A crucial point is now stated, which will be most relevant when we consider the family of related IRs in Chapters 4 and 7: For a given analysis (such as constant propagation), apart from changing IR, if the other parameters in the data flow framework are unaltered, then analysis performance depends completely on the expressivity of each particular IR. The analysis is parameterized on the IR alone, so that a single analysis can operate on multiple similar IRs, such as WEB SSA and SSI.

The next chapter reviews SSI in exhaustive detail.

# Chapter 3

# Static Single Information Form

Static single information form is an augmented CFG IR, which is similar to SSA. Static single information form may be constructed efficiently from CFG.

# 3.1 About this Chapter

# 3.1.1 Objectives

Static single information form (SSI) is a recently proposed IR for data flow analysis of imperative programming languages. It was introduced by Ananian in 1999 [Ana99]. This chapter reviews the basic concepts of SSI. However SSI has not been widely adopted so far by the static analysis community. This chapter aims to tackle this issue by providing:

- 1. a new definition of SSI that is more concise than the original definition, and

- 2. a new construction algorithm for SSI that is shown to be more efficient for real-world programs than the original algorithm, and

- 3. a detailed comparison of SSI and its more popular relative, SSA.

## 3.1.2 Outline

Section 3.2 informally introduces SSI, and reviews its history. Section 3.3 presents a new and concise definition of SSI. Section 3.4 discusses the properties of SSI. Section 3.5 compares two algorithms for SSI construction. Sections 3.6 and 3.7 highlight related work and future work respectively. Finally Section 3.8 concludes.

# 3.1.3 Contributions

This chapter makes three key contributions.

- 1. Section 3.3 gives a new and succinct definition of SSI.

- 2. Section 3.5.2 presents a new algorithm for the efficient construction of SSI programs from CFG programs.

3. This chapter compares the properties of SSA and SSI in a comprehensive and methodical fashion. Section 3.2 gives a qualitative comparison, and Section 3.6 gives a quantitative comparison. There has been no such previous study.

# 3.2 Introduction to SSI

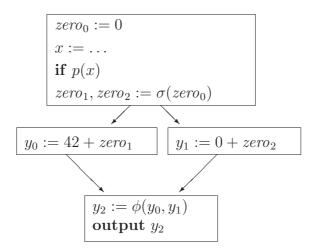

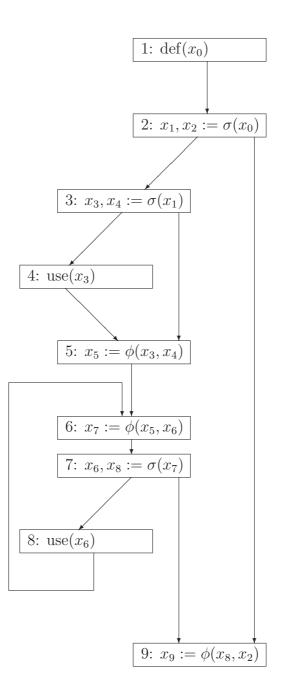

SSI requires each virtual register to have a unique definition point in the program text. This is achieved by virtual register renaming, in the same way as SSA. (This dissertation follows the convention that renamed virtual registers have the same name as originally named virtual registers, with an additional integer subscript. This follows the standard presentation given in most SSA research.) However the SSI constraint generally enforces more renaming than the SSA constraint, since virtual registers used in different arms of a conditional branch must have distinct names in SSI. Thus new virtual register names are introduced at the program points given below.

- assignment statements: As in SSA, a virtual register can only be assigned a value at one point in the program text. This ensures the desirable analytical property of *referential transparency*, where the value of virtual register v does not depend upon the program point at which v is used. (This is similar to the notion of flow-insensitive data flow information introduced in Chapter 4.)

- control flow merge points: As in SSA, the single assignment property means that multiple reaching definitions at a control flow merge point must be factored into a single definition by a  $\phi$ -function.

- control flow split points: Unlike SSA, a virtual register that is used in one or more arms of the control flow split is assigned a new name for each arm of the split. Multiple upwardly exposed uses at a control flow split point must be factored into a single use by a  $\sigma$ -function.

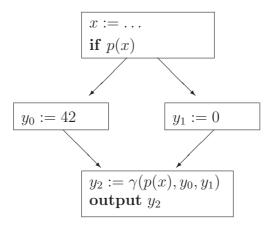

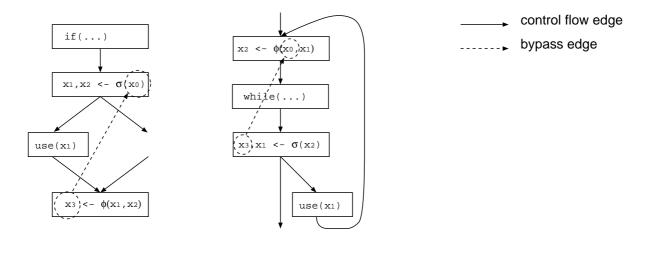

The  $\sigma$ -function is the dual of the  $\phi$ -function. Figure 3.1 compares their properties.

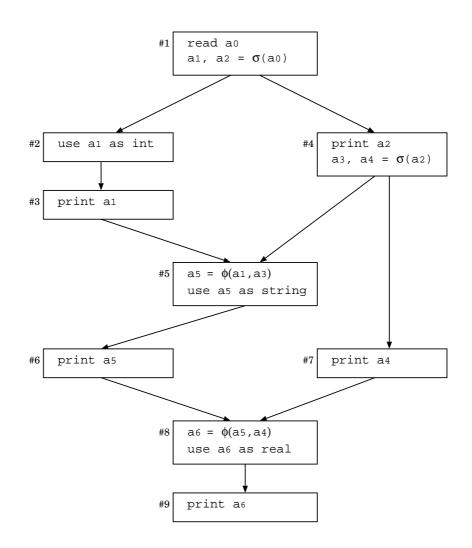

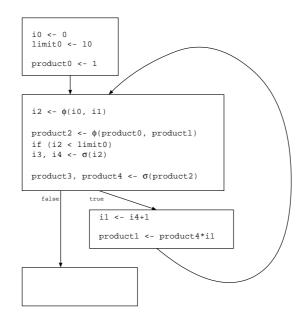

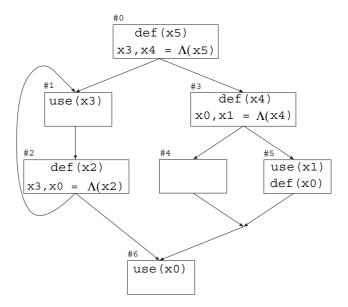

Figure 3.2 shows an example SSI program. This is the SSI version of the CFG program in Figure 2.2. Note that there is a  $\sigma$ -function for *i*, since the value of *i* is used in the loop body. There are three important features of SSI that are emphasized in this section. These properties follow naturally from the formal definition of SSI in Section 3.3, but it is helpful to build up an intuitive, informal understanding at this early stage.

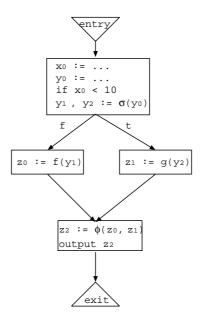

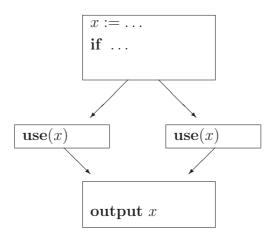

- 1. A  $\sigma$ -function is required for a virtual register v used in a conditional context, even when v is not mentioned in the predicate that governs that conditional context. Virtual register y in Figure 3.3 illustrates this point.

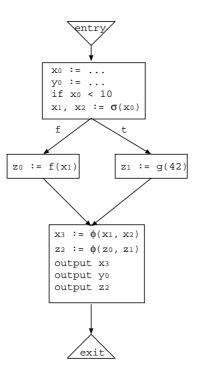

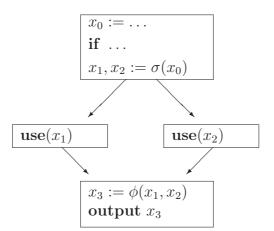

- 2. If a virtual register v is defined before a control flow split point, and v is used after the corresponding control flow merge point, but not used in the conditional context, then the original name can be retained after the control flow merge point, and no  $\phi$ or  $\sigma$ -function is required. Virtual register y in Figure 3.4 illustrates this point. This property of SSI is known as single-entry-single-exit region bypassing. See Sections 3.5.1 and 5.8.2 for further details.

| $\phi$ -function                                                                                                                        | $\sigma$ -function                                                                                                                             |  |

|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| inserted at control flow                                                                                                                | inserted at control flow split                                                                                                                 |  |

| merge points                                                                                                                            | points                                                                                                                                         |  |

| single destination operand                                                                                                              | <i>n</i> destination operands,<br>where <i>n</i> is the number<br>of successors to the basic<br>block that contains this<br>$\sigma$ -function |  |

| $n$ source operands, where $n$ is the number of predecessors to the basic block that contains this $\phi$ -function.                    | single source operand                                                                                                                          |  |

| takes the value of one of its<br>source operands (dependent<br>on control flow) and assigns<br>this value to the destination<br>operand | takes the value of its source<br>operand and assigns this<br>value to one of the desti-<br>nation operands (dependent<br>on control flow)      |  |

Figure 3.1: Differences between  $\phi$ - and  $\sigma$ -functions

3. If a virtual register v is defined before a control flow split point, and used in the subsequent conditional context, then obviously a  $\sigma$ -function for v is necessary at the control flow split point. However, a  $\sigma$ -function must be the last use of its source operand virtual register name. So the original virtual register name cannot be mentioned after the corresponding control flow merge point. A  $\phi$ -function is required to introduce a new virtual register name. Virtual register x in Figure 3.4 illustrates this point. In effect,  $\sigma$ - and  $\phi$ - functions kill their source operands. This can be useful for some data flow analyses, as Chapter 4 explains in detail.

Ananian [Ana99] introduces SSI by giving a formal definition, a pessimistic construction algorithm and an operational semantics. This chapter presents a more concise definition and an optimistic construction algorithm. The empirical evidence presented in this chapter shows that the optimistic construction algorithm performs better than the pessimistic construction algorithm, and also that SSI is similar to SSA in terms of IR size and construction time. This evidence raises the credibility of SSI as a viable IR for static analysis.

SSI is employed in a wide range of existing analyses and optimizations. Examples are given below.

- sparse conditional constant propagation [Ana99]