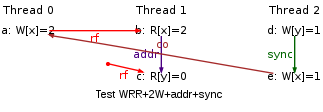

Run WRR+2W+addr+sync in model, using ppcmem

PPC WRR+2W+addr+sync

"Rfe DpAddrdR Fre SyncdWW Wse"

Cycle=Rfe DpAddrdR Fre SyncdWW Wse

{

0:r2=x;

1:r2=x; 1:r5=y;

2:r2=y; 2:r4=x;

}

P0 | P1 | P2 ;

li r1,2 | lwz r1,0(r2) | li r1,1 ;

stw r1,0(r2) | xor r3,r1,r1 | stw r1,0(r2) ;

| lwzx r4,r3,r5 | sync ;

| | li r3,1 ;

| | stw r3,0(r4) ;

exists

(x=2 /\ 1:r1=2 /\ 1:r4=0)