An overview of Jaroslav Ševčík's trace-set transformation semantics from "Safe Optimisations for Shared-Memory Concurrent Programs" (PLDI'11)

Jean Pichon

24th of September 2014

Replacement memory model for Java, for which common subexpression elimination is sound (and other typical optimisations too).

N.B. This is not the case for the current Java Memory Model.

Starting from the "naive" trace-set, the semantics is given by the closure of the trace-set under reorderings and optimisations.

Reordering and elimination of memory actions *one by one* on *thread-local* trace-sets.

#### Trace-sets

#### Thread

$\mathbf{y} =_{\mathtt{NA}} \mathbf{x}_{\mathtt{NA}}$

has naive trace-set (the prefix-closure of)

$\{ R_{NA} \times O \quad W_{NA} y O, \quad R_{NA} \times 1 \quad W_{NA} y 1, \quad \ldots \}$

(one for each value in the domain of x).

# Reordering

Reorder two adjacent memory actions in a (thread-local) trace.

Example: thread  $x =_{NA} 1$ ;  $y =_{NA} 2$ has naive trace-set (the prefix closure of) { $W_{NA} x 1 W_{NA} y 2$ }.

Now, because the two writes in the trace  $W_{NA} \ge 1$   $W_{NA} \ge 2$  are 1) at two different locations,

2) not volatile,

3) non-dependent (here, because they are writes)<sup>1</sup>, they can be reordered:

$$W_{NA} \ge 1$$

$W_{NA} \ge 2$   $\rightarrow$   $W_{NA} \ge 2$   $W_{NA} \ge 1$

Note: therefore,  $y =_{NA} 2$ ;  $x =_{NA} 1$  is a valid "optimisation".

<sup>1</sup>see later

# Roach motel reordering

Roach motel reordering is a design goal of Java<sup>2</sup>.

Non-atomic actions can be moved after a lock or volatile read:

$$t_1 \hspace{0.1 cm} \mathbb{W}_{ ext{NA}} \hspace{0.1 cm} ext{x} \hspace{0.1 cm} 1 \hspace{0.1 cm} \mathbb{L} \hspace{0.1 cm} \ell \hspace{0.1 cm} t_2

ightarrow t_1 \hspace{0.1 cm} \mathbb{L} \hspace{0.1 cm} \ell \hspace{0.1 cm} \mathbb{W}_{ ext{NA}} \hspace{0.1 cm} ext{x} \hspace{0.1 cm} 1 \hspace{0.1 cm} t_2$$

but not the other way around!

Symmetrically, non-atomic actions can be moved before an unlock or volatile write:

$$t_1 \ \mathrm{U}\,\ell \ \mathrm{W}_{\mathrm{NA}}\,\mathrm{x}\,\mathbf{1} \ t_2

ightarrow t_1 \ \mathrm{W}_{\mathrm{NA}}\,\mathrm{x}\,\mathbf{1} \ \mathrm{U}\,\ell \ t_2$$

$^2 to the best of my knowledge, it is not done by any compiler, at least for C — please tell me if I'm wrong, I would really like to know!$

# Optimisations: release/acquire pairs

**Definition**: A *release/acquire pair*<sup>3</sup> is the pair (in that order) of a volatile write and a volatile read (not necessarily to the same location), or of an unlock and lock (not necessarily of the same lock).

<sup>3</sup>nothing to do with C11's release/acquire

# Peephole optimisations: RaR, WaR, RaW, OWE

We can define elimination of redundant read after read, redundant write after read, redundant read after write, and overwritten write.

For example, read after read:

...and overwritten write:

### Irrelevant read elimination

If the trace-set contains all the traces of the form  $t_1 \quad R_{NA} \ge v \quad t_2$ , for all values v in the domain of x, then that read is *irrelevant*, and can be removed, to yield trace  $t_1 \quad t_2$ .

For example, thread

$$z =_{NA} 1; y =_{NA} x_{NA} * 0$$

has (naive) trace-set

$\{ W_{NA} z 1 \ R_{NA} x 0 \ W_{NA} y 0, \ W_{NA} z 1 \ R_{NA} x 1 \ W_{NA} y 0, \ \ldots \}$

so it also has optimised trace

$$W_{NA} \ge 1 \quad W_{NA} \ge 0$$

# Dependencies: LB vs. LB+datas

How to check for dependency: the inverse image (by the transformation) of the prefixes of the transformed trace have to be in the trace-set.

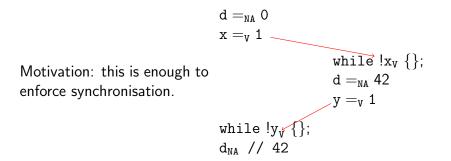

LB is allowed to return 42/42 for non-volatile:  $x_{NA}$ ;  $y =_{NA} 42$  has naive trace-set (the prefix-closure of)

$\{R_{NA} \ge 0 \ W_{NA} \ge 42, \ R_{NA} \ge 42 \ W_{NA} \ge 42\}$

so the closure also contains, by IRE,  $W_{NA} y 42$ , so it also contains  $W_{NA} y 42$   $R_{NA} x 0$  and  $W_{NA} y 42$   $R_{NA} x 42$ . LB+datas is not allowed to return 42/42:

$\{R_{NA} \ge 0 \ W_{NA} \ge 0, \ R_{NA} \ge 42 \ W_{NA} \ge 42\}$

# Conclusion

Advantages:

- Clean (I didn't explain the subtleties of the technical setup, but the ideas were there)

- DRF-SC theorem

- Validates common subexpression elimination and other expected optimisations

- ► Validates C++'s 29.3p9 weak no-OOTA (I think)

- Proof of soundness for typical optimisations on the source

- Cheap to implement on TSO: non-atomic reads and writes can be mapped to plain reads and writes, because all TSO behaviour is accepted by the model

Disadvantages:

- Only considers thread-local optimisations

- $\blacktriangleright$  Unknown implementation cost on  $\mathrm{POWER}/\mathsf{ARM}$

This page intentionally left blank.