#### Lecture Notes for

# Systems Design

# Some Lectures to Part 1A

Easter Term 1996.

Revised slightly 2004.

© D.J. Greaves 95, 96.

(djg@cl.cam.ac.uk)

University of Cambridge Computer Laboratory New Museums Site Pembroke Street Cambridge CB2 3QG

# Contents

| Ι | Hardware Structure of a Computer                                    | 7   |  |  |  |  |  |  |  |

|---|---------------------------------------------------------------------|-----|--|--|--|--|--|--|--|

| 1 | Components of a simple computer                                     | 8   |  |  |  |  |  |  |  |

|   | 1.0.1 Processor Registers                                           | 8   |  |  |  |  |  |  |  |

|   | 1.0.2 Flags Register                                                | 9   |  |  |  |  |  |  |  |

| 2 | Processor Operation                                                 | 11  |  |  |  |  |  |  |  |

|   | 2.1 Fetch-Execute Cycle                                             | 11  |  |  |  |  |  |  |  |

|   | 2.2 Stacks and Subroutines                                          | 11  |  |  |  |  |  |  |  |

|   | 2.3 Interrupts                                                      | 13  |  |  |  |  |  |  |  |

| 3 | Data Representation                                                 | 14  |  |  |  |  |  |  |  |

|   | 3.1 Hexadecimal Representation                                      | 14  |  |  |  |  |  |  |  |

|   | 3.2 Representing Unsigned Integers                                  | 14  |  |  |  |  |  |  |  |

|   | 3.3 Representing Signed Integers                                    | 14  |  |  |  |  |  |  |  |

|   | 3.3.1 $$ Some Examples of Signed and Unsigned Integer Arithmetic $$ | 14  |  |  |  |  |  |  |  |

|   | 3.4 Representing Floating Point Numbers                             | 16  |  |  |  |  |  |  |  |

|   | 3.5 Representing Text                                               | 16  |  |  |  |  |  |  |  |

|   | 3.6 Representing Data Structures                                    | 17  |  |  |  |  |  |  |  |

|   | 3.7 Representing Machine Instructions                               | 18  |  |  |  |  |  |  |  |

|   | 3.7.1 Addressing Modes                                              | 18  |  |  |  |  |  |  |  |

|   | 3.7.2 Example Instruction Set                                       | 19  |  |  |  |  |  |  |  |

| 4 | Caches                                                              | 22  |  |  |  |  |  |  |  |

|   | 4.1 A note on Cache Implementation                                  | 22  |  |  |  |  |  |  |  |

|   | 4.2 Example of Cache Speedup                                        | 22  |  |  |  |  |  |  |  |

|   | 4.3 Instruction and Data Caches                                     | 22  |  |  |  |  |  |  |  |

| 5 | Virtual Memory Translation Hardware                                 |     |  |  |  |  |  |  |  |

|   | 5.1 VM unit implementation                                          | 25  |  |  |  |  |  |  |  |

|   | 5.2 Paging                                                          | 25  |  |  |  |  |  |  |  |

| 6 | Coprocessing                                                        | 27  |  |  |  |  |  |  |  |

| 7 | Input and Output                                                    | 28  |  |  |  |  |  |  |  |

|   | 7.1 Input and Output Cycles                                         | 28  |  |  |  |  |  |  |  |

|   | 7.2 Example: A UART for a serial port                               |     |  |  |  |  |  |  |  |

|   | 7.2.1 UART Programming Procedure                                    | 30  |  |  |  |  |  |  |  |

|   | 7.3 Keyboard and Mouse Interfaces                                   | 30  |  |  |  |  |  |  |  |

|   | 7.4 Memory-mapped display                                           |     |  |  |  |  |  |  |  |

|   | 7.5 Intelligent Devices                                             | 31  |  |  |  |  |  |  |  |

| 8 | Disks, Controllers and Filing Systems                               | 32  |  |  |  |  |  |  |  |

|   | 8.1 Disk Drive Controller                                           | 32  |  |  |  |  |  |  |  |

|   | 8.2 Data arrangement on disk                                        | 33  |  |  |  |  |  |  |  |

|   | 83 Evample: MSDOS File Organisation                                 | 3.4 |  |  |  |  |  |  |  |

|    | 8.3.1 Sequential Read and Write Algorithms                      | 35        |

|----|-----------------------------------------------------------------|-----------|

| 9  | System Busses                                                   | 37        |

|    | 9.1 The Processor Bus                                           | 37        |

|    | 9.2 The Memory Bus                                              | 37        |

|    | 9.3 Peripheral and IO Busses                                    | 37        |

|    | 9.3.1 IO Bus Examples                                           | 39        |

|    | 9.3.2 Peripheral Bus Example - SCSI                             | 39        |

|    | 9.4 The Local Area Network                                      | 40        |

|    | 9.5 Supercomputers                                              | 41        |

| IJ | Resident Software                                               | 42        |

| 10 | System Software, Resident Software and others                   | 43        |

| 11 | Loading the first program - booting                             | 44        |

|    | 11.0.1 Example Diagnostics                                      | 44        |

| 10 | Kernel and Shell                                                | 46        |

| 12 | 12.1 A note on a Basic Input Output System                      | 46        |

|    | 12.2 Command Line Interpreter or Shell                          | 46        |

|    | 12.2 Command time interpreter of Shell                          | 40        |

| 13 | Window Systems                                                  | 48        |

|    | 13.1 Virtual Terminal Windows                                   | 48        |

|    | 13.2 General Windows                                            | 48        |

|    | 13.3 Directory view (ICON) program                              | 48        |

| 14 | System Resources                                                | 49        |

|    | 14.1 What does a program expect to see when loaded in ?         | 49        |

|    | 14.2 Storage Allocation - Dynamic and Static                    | 49        |

|    | 14.2.1 Static Storage                                           | 49        |

|    | 14.2.2 Dynamic Storage                                          | 49        |

|    | 14.2.3 Examples of Dynamic Storage in ML                        | 50        |

| 15 | Protection and Sharing                                          | <b>52</b> |

|    | 15.1 Instruction Classes                                        | 52        |

|    | 15.1.1 Normal Instructions                                      | 52        |

|    | 15.1.2 Privileged Instructions                                  | 52        |

|    | 15.1.3 Emulated Instructions                                    | 52        |

|    | 15.2 System calls to the OS Kernel - The TRAP                   | 53        |

| 16 | Multiprocessing                                                 | 54        |

|    | 16.1 Notes on Process, Processor and Thread                     | 54        |

|    | 16.2 Context Swap                                               | 54        |

|    | 16.3 Three states of a user process as managed by the Scheduler | 55        |

|    |                                                                 |           |

|    | 16.4 Memory Maps                                                | 55        |

| 17 | Input and Output                                                | 57        |

|    | 17.1 The Device Driver                                          | 57        |

|    | 17.1.1 The interface between the device driver and the kernel   | 57        |

|    | 17.1.2 Block and Character devices                              | 59        |

|    | 17.2 Evamples                                                   | 50        |

|     | 17.2.1 Example: Terminal Input and Output                      | 59         |

|-----|----------------------------------------------------------------|------------|

|     | 17.2.2 Printer Output                                          | 59         |

|     | 17.2.3 Disk Access and Filing again                            | 59         |

|     | 17.2.4 Typical functions for file open, read, write and delete | 60         |

|     | 17.2.5 Network input and output                                | 60         |

| 18  | Interprocess Communication                                     | 61         |

|     | 18.1 Communication Paradigms                                   | 61         |

|     | 18.1.1 File Communication                                      | 61         |

|     | 18.1.2 Signals                                                 | 61         |

|     | 18.1.3 Bytestream Communication                                | 61         |

|     | 18.1.4 Datagram Communication                                  | 61         |

|     | 18.1.5 Communication through Remote Procedure Call (RPC)       | 62         |

|     | 18.1.6 Communication through Shared Memory Objects             | 62         |

|     | 18.2 A note on Reliability                                     | 62         |

|     | 18.3 A transport protocol for a bytestream                     | 62         |

| II. | I Software Tools                                               | 63         |

| 19  | Program Preparation Methods                                    | 66         |

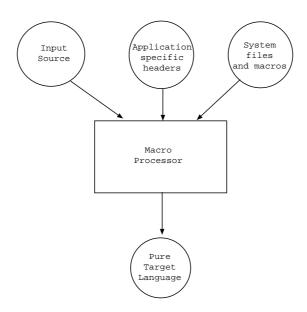

| 20  | Preprocessing and Macro Expansion                              | 67         |

|     | 20.1 Schema Consistency                                        | 67         |

| 21  | Program Compilation                                            | 69         |

| 22  | Assembly Language Again                                        | 71         |

|     | 22.1 The Structure of Assembly Language                        | 71         |

|     | 22.2 Example: Assembly on an Motorola 6800                     | 72         |

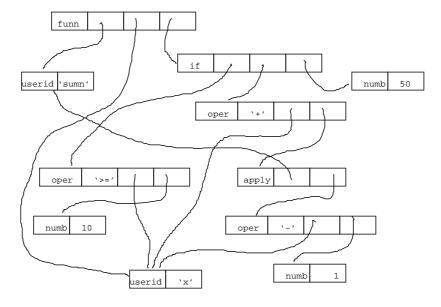

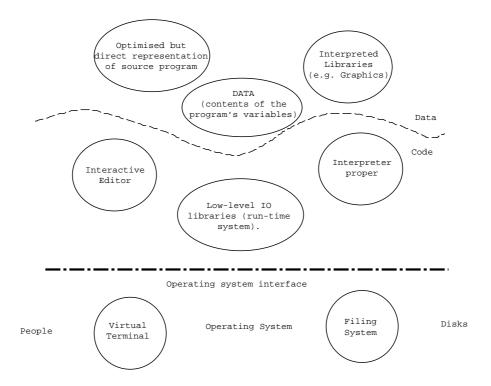

| 23  | Interpreted Software                                           | 74         |

| 24  | Loading and Execution by Hardware                              | <b>7</b> 6 |

|     | 24.0.1 Absolute and Relocatable Addressing                     | 76         |

| 25  | Modular Compilation                                            | 77         |

| 20  | 25.1 Benefits of a Modular Approach to Programming             | 77         |

|     |                                                                |            |

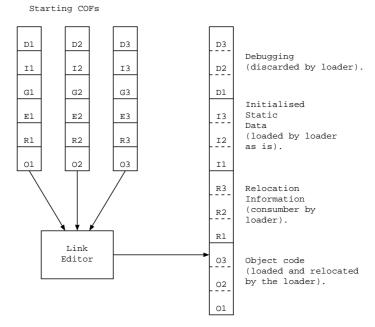

|     | 25.2 Common object format (COF)                                | 77         |

|     | 25.2 Common object format (COF)                                | 77<br>78   |

|     | 25.2 Common object format (COF)                                |            |

|     | 25.2 Common object format (COF)                                | 78         |

| 26  | 25.2 Common object format (COF)                                | 78<br>79   |

# Preface

This course, System Design, is a general introduction to the hardware and software architectural design of modern computer systems, including time-sharing workstations and mainframes, personal computers and imbedded microcontrollers. It is divided into three main parts:

- 1. DATA REP AND MACHINE HARDWARE

- 2. RESIDENT SOFTWARE

- 3. SOFTWARE TOOLS

but the material in each section is actually quite highly interdependent. Many of the ideas are repeated in more than one section.

For those of you who have done the hardware course already, you should see how the first parts of this course build on the larger blocks introduced in hardware, such as multiplexors and tri-state busses. For those who will do hardware next year, do not worry, no hardware knowledge is assumed or required. System Design course material is useful background for the part 1B courses on operating systems, concurrency, processor architecture, assembly language programming and compilation. The System Design lectures will follow these printed notes closely. These notes are not supposed to be a substitute for reading some of the recommended books.

These notes are available online on the departmental 'Teaching' pages, along with any extra slides that I might use in the lectures. Anyone in the department may print a copy for their own use, but copyright belongs to DJ Greaves.

Please email comments on these notes and the course to djg@cl.cam.ac.uk or fill out a lectures appraisal form, available from M Levitt or on the Web.

#### Acronyms used in these notes

ALU - Arithmetic logic unit

$\mathbf{API}\,$  - application program interface

$\mathbf{ASCII}\,$  - American standard code for information interchange

$\mathbf{ATM}\,$  - Asynchronous Transfer Mode

**BIOS** - The Basic Input Output System

CLI - command line interpreter

$\mathbf{COF}\,$  - common object format

CPU - Central Processor Unit

$\mathbf{CRC}$  - Cyclic redundancy check

DRAM - dynamic random access memory

${\bf IAR}\,$  - instruction address register (same as PC)

IDE - a 16 bit disk drive IO bus

${\bf IO}\,$  - input and output

$\mathbf{LAN}$  - local area network

$\mathbf{MAC}\,$  - media access control

$\mathbf{MUX}$  - multiplexor of two or more inputs

**OS** - operating system

${f PC}$  - program counter

PCMCIA - Personal Computer Memory Card Interface Association

PROM - user programmable read only memory

RAM - random access memory

$\mathbf{RTL}$  - register transfer level

RISC - Reduced instruction set computer

${f ROM}$  - read only memory

RS latch - a latch with set and reset inputs

RS232 - a serial communications standard

$\mathbf{SCSI}$  - small computer system interface

SIMD - Single instruction, multiple data processor

MIMD - Multiple instruction, multiple data processor

${f TLB}$  - translation lookaside buffer

**UART** - universal asynchronous receiver and transmitter

VM - Virtual memory

Please send me email if I use acronyms which are not on this list.

#### Recommended Reading

These first three books start with hardware and work upwards through system architecture in the manner of this System Design course.

M H Lewin Logic Design and Computer Organisation. Addison Wesley

V C Hamachar Computer Organisation. McGraw Hill

R D Downing and F W D Woodhams - Computers, from logic to architecture.

Four books about system software:

Maddix and Morgan - Systems software: An introduction to language processors and operating systems. A general book.

A Tanenbaum - Structured Computer Organisation. A book from the preparatory reading list covering many basic topics in computer structure and software approaches.

L L Beck - Systems software, an introduction to systems programming. 2nd Edition. A practical book with a less academic approach than usual.

A Tanenbaum - Operating system design and implementation. Another of Tanenbaum's very readable books, this one going from operating systems basics through to at least part 1B level.

Two more advanced books:

Pereson and Silberschatz - Operating systems concepts. Addison Wesley, 1983. Another part 1B level book, but very readable when you are ready for it.

M J Bach - *The design of the Unix operating System*. This advanced book presents simplified implementations of part of the Unix operating system in the C language.

# Part I

# Hardware Structure of a Computer

# 1 Components of a simple computer

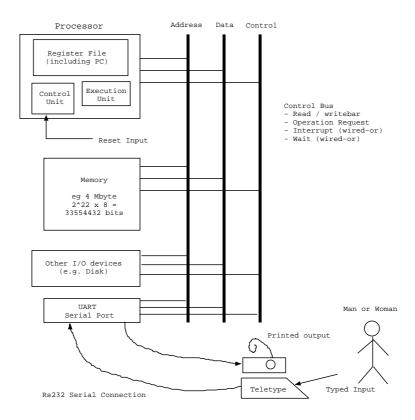

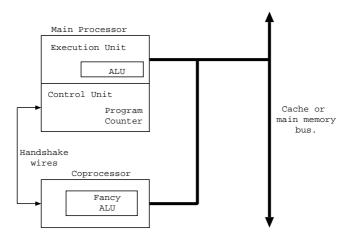

Figure 1.1 shows the architecture of a general purpose Von Neumann computer. Program and data share the same memory, which is connected to a processor unit using busses. The processor contains registers, including the program counter register.

Input and output devices are also connected to the bus. In this simple computer, the only I/O device is a universal asynchronous receiver and transmitter (UART). This provides access to the most basic of text devices, the *Teletype* serial terminal.

The idea of a teletype for input and output, with its two simplex communication channels (input and output) underlies much of systems software, even today. A personal computer running a terminal emulator such as xterm or the the one invoked with the COMMAND program under Windows is identical in function to the ASCII Teletype's used in early timesharing.

With a bus, one device is always the *bus master*. In this simple computer, the only bus master is the processor, meaning that the processor always drives the address bus and control wires. The data bus is bi-directional, being driven by the processor during a write cycle and by the addressed *slave* device during a read cycle. We will now look at all of these components in greater detail.

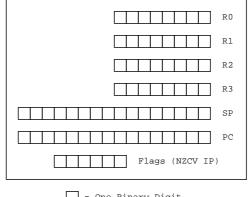

#### 1.0.1 Processor Registers

The processor contains a number of registers available to the programmer. Registers are general purpose or special purpose. General purpose registers are used for fast access, temporary storage of variables. They have names such as

```

R0, R1, R2, R3, R4, R5, R6, R7 ...

or

AX, BX, CX, DX, BP, SI, SP, DI (Intel family)

or

A, B, C, D, E, H, L, IX, IY (Z80)

```

Special purpose registers typically include:

- a program counter (PC), which points to the current instruction

- a flags register, containing P I N Z V C

- a stack pointer register, which points to the last storage location in use in the stack.

In some architectures, any general register can be a program counter or stack pointer, but in most systems, special registers are used so that the hardware data paths may be optimised.

The registers inside the processor generally have the same width as the data bus and this is known as the processor's *word size*. A modern general purpose computer typically has a 32 bit wide data bus and the same width address bus.

A byte-addressed computer gives each byte in address space its own address. I.e. incrementing the address by one moves you 8 bits along the memory array. Many computers in the past have been word-addressed.

When a data bus size larger than 8 bits is used, the computer may still be byte-addressed, but several bytes will be returned on each read cycle to external memory. The processor

Figure 1.1: Simple Von Neumann Computer Architecture

may require all of the bytes immediately, for instance if doing a word addition, or it may store them temporarily in a bus interface register or cache memory in the hope they will be useful shortly.

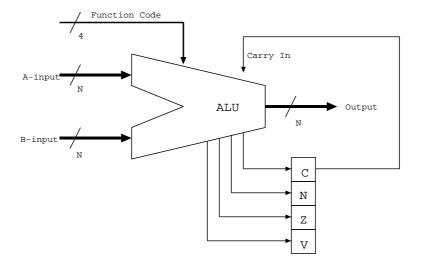

#### 1.0.2 Flags Register

The processor flags register is a collection of single bit flags. Most processors have the following: Z N C V P I. The first four of these are used mainly with conditional branches (section 3.7.2), and the last two are used to support systems software.

- **Z Zero Flag.** This flag is updated after every update to a register. If the register was loaded with zero (all bits zero) the Z flag is set, else clear.

- N Negative Flag. This flag is updated after every update to a register. If the register was loaded with a value were the most significant bit was a one, N is set, else N is cleared.

- C Carry Flag. This flag is updated after every update to a register. If the update was a result generated in the ALU and the carry output from the ALU was a one, C is set, else C is cleared. The carry output from the ALU is the carry generated in the addition (or borrow in subtraction) from the most significant bit.

- V Overflow Flag. This flag is updated after every update to a register. If the update was a result generated in the ALU and the overflow output from the ALU was a one, V is set, else V is cleared. The overflow output from the ALU is the exclusive-or of the carry into and out of the most significant bit. It may be seen that overflow will be asserted if the data being operated on by the ALU is in two's complement form (section 3.3) and the result of the operation lies outside the representable value range. V is not useful for unsigned operations use C instead.

Figure 1.2: Usual configuration of flags with an ALU

- I Interrupt Enable Flag. This flag may be set and cleared by privileged instructions only. When set, the processor will respond to interrupts on its interrupt input(s), otherwise it will ignore them. This flag is set by systems software during critical regions of code where system data structures are transiently in an inconsistent state and so should not be viewed by other software, such as interrupt routines. It is not possible to experience an unexpected context switch while this flag is set (section 16.2). External hardware generally queues interrupts such that even if they occur while I is clear, they will persist until interrupts are again enabled (I set).

- P Privilege Flag When P is set, the full instruction set of the computer may be used and all of the memory map and register set of the processor may be accessed (section 15.1). When clear, a restricted subset of instructions may be executed which can only read or modify the general user registers and user memory space. An internal interrupt is generated, known as a privilege violation exception, if a privileged instruction is attempted when the flag is clear. This flag is set by reset, interrupt and system call instructions. Cleared by a privileged instruction of processor-specific type (such as RTI described in section 2.2).

# 2 Processor Operation

### 2.1 Fetch-Execute Cycle

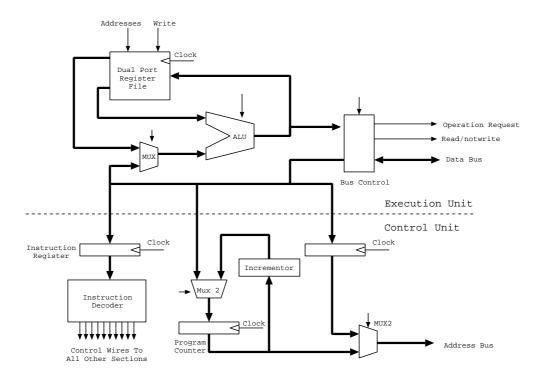

The Control Unit performs the fetch-execute cycle.

- 1. Processor Reset. When the computer is switched on, a timer asserts the reset input to the processor for half a second or so. The reset input causes the program counter to be loaded with a fixed value, such as zero. A program must already be loaded at this address typically a ROM is mapped here. When the reset input is deasserted, we proceed to normal operation, in step 2. Computers with a reset switch drive the reset input from the logical OR of the power on reset and the reset signal from the switch. enabling the computer to be reset without powering off and on again.

- 2. In this step we check for external interrupts. If (any of) the interrupt signal(s) to the processor is(are) active, save the program counter using a special purpose register (e.g. push it on the stack), set the privilege flag and load the program counter with a fixed value, or a value depending on the type of interrupt.

- 3. Fetch an instruction from memory at the address pointed to by the program counter. If the instruction spreads over several memory locations, fetch the rest of the instruction, incrementing the program counter as needed.

- 4. Obey the instruction (using the ALU if needed).

- 5. If the instruction was a jump, then the program counter will have been loaded with the next instruction's address during step 4, so go to step 2.

- 6. Else, increment the program counter to point to the next instruction and go to step 2.

Figure 2.1 shows the data paths of a Von Neumann style processor. It is clear from the structure that the instructions and data both arrive into the processor on the single data bus and that there is only one address bus - hence it a Von Neumann machine.

The data paths for saving the PC as a subroutine return address and for making indexed (calculated) data access are not shown. These paths require exchange of addresses between the control unit and the execution unit. Also there is no provision for calculating program counter relative addresses or interrupts.

#### 2.2 Stacks and Subroutines

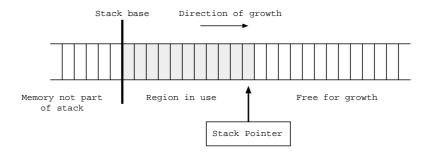

Most processors provide instructions for implementation of LIFO (last-in first-out) stacks. A register in the processor serves as a stack pointer, pointing to the item on the top of the stack. Two operations are needed for a stack - push and pop.

#### PUSH:

- 1. Advance pointer to free space

- 2. Store item at address pointed to by pointer.

#### POP:

- 1. Fetch item from address pointed to.

- 2. Retreat pointer to new top item.

A subroutine call instruction, often called JSR (jump to subroutine), takes an operand which is the address of the subroutine. It stores the program counter (which will be pointing to the

Figure 2.1: Block diagram of a simple microprocessor

${\rm Figure}~2.2:$  Example of a stack with a number of locations in use

| Class | Source or cause                       |

|-------|---------------------------------------|

| 1     | UART interrupt                        |

| 1     | Real-time clock interrupt             |

| 1     | etc                                   |

| 2     | Illegal instruction (bad opcode)      |

| 2     | Illegal address of operand            |

| 2     | Emulation of missing coprocessor      |

| 2     | VM translation fault (page paged out) |

| 2     | Privilege violation                   |

| 3     | Trap (system call)                    |

Table 2.1: Examples of interrupts.

instruction after the JSR) on the stack and then jumps to the operand address (i.e. loads it in the PC). A subroutine return instruction, often called RTS (return from subroutine), is found at the end of a subroutine. It takes no operands and simply pops the stack top value into the program counter, causing execution to resume at the point after the subroutine was called. Such subroutines can be recursive. A subroutine may keep other data, such as local variables, on the stack, provided it pops it off again before returning.

On a processor with a 32 bit program counter, the items stored on the subroutine return address stack will be 32 bit program counter values, so the advance and retreat operations are just add and subtracts of 4 on a byte-addressed machine.

A variant of the RTS instruction is RTI (return from interrupt). As well as doing an RTS, RTI pops an extra word off the stack and loads it in to the flags register. This is a convenient way to clear the privilege flag after a system call and to restore the other flags. System calls are described in section 15.2.

RTI is privileged.

#### 2.3 Interrupts

Interrupts are unexpected, hardware driven deviations from the flow of control prescribed by the current program. It is normal for the interrupting software to save the exact state of the user registers at the time of the interrupt, so that the execution can continue at the point of the interrupt, at some later time. Hence the name, interrupt.

There are three main classes of interrupt:

- 1. An external device requests service by asserting an interrupt line which feeds into the processor. An example is the UART, which interrupts each time a new character has arrived in its internal registers or when ready for a new character to send.

- 2. While obeying the instruction in step 4 above, an error of some kind is detected. An example is a reference to non-existent memory or the loading of a bit pattern from memory in step 3 which is not a valid instruction.

- 3. The software interrupt, or service call, which is described in section 15.2 is also generally handled using similar processing steps, although it is not an unexpected interrupt as the above examples are.

The cause of the error in interrupt class 2 can often be fixed by the operatin system kernel (for instance correcting a page fault - section 5.2) and so when the kernel returns from the interrupt, the program counter should be wound back to restart the instruction. On the other hand, the class 1 interrupts are handled by the processor after the successful completion of an instruction, so on interrupt return, the next instruction should be executed.

The word *exception* is often used for an interrupt which occurs owing to an error.

# 3 Data Representation

Memory can hold any binary bit pattern, but is typically used to hold the following: signed and unsigned integers, floating-point numbers, ASCII text, machine instructions and complex structures such as a stack or composite records of pointers and simpler objects.

Let us look at examples of these and assume a 32 bit machine unles otherwise stated. When the word size is 32 bits, there are  $2^{32}$  different combinations.

## 3.1 Hexadecimal Representation

From time to time, hexadecimal representation is a convenient way to express numbers. Hexadecimal is easier to read than binary, but easy to convert to and from binary. Numbers starting '0x' are in hexadecimal. A hexadecimal digit is one of 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F and represents a four bit binary field. For example, one thousand decimal can be converted to hexadecimal 0x3E8 by first converting it to binary and then grouping the coefficients in fours.

```

1000 \text{ decimal} \\ = 512 + 256 + 128 + 64 + 32 + 8 \\ = 1.512 + 1.256 + 1.128 + 1.64 + 1.32 + 0.16 + 1.8 + 0.4 + 0.2 + 0.1 \\ = 1 1 1 1 1 0 1 0 0 0 \text{ binary} \\ = 0011\_1110\_1000 \\ = 0x3E8

```

The underscore may be placed in a number to help its readability.

#### 3.2 Representing Unsigned Integers

Unsigned Integers may be held in four adjacent bytes in standard binary coding, ranging from zero to  $2^{32} - 1$ .

#### 3.3 Representing Signed Integers

Two's complement form uses the most significant bit as a sign bit. If it is clear, a positive number is represented and the value is equivalent to the identical unsigned binary bit pattern. With a 32 bit word, positive values from zero to  $2^{31} - 1$  can be stored.

Negative two's complement values are represented by the bit pattern which when added to the equivalent unsigned positive number in a normal binary adder results in zero. This pattern can be obtained by inverting all of the bits of the positive representation and then adding one. Values from -1 to  $-2^{31}$  are possible.

Signed integers are normally held in two's complement form since, from the above definition, the representation of the positive integers is unchanged and the arithmetic logic required for addition and subtraction is the same as for unsigned binary integers.

For example, minus 2 as an 8 bit two's complement number is binary  $1111_{-}1110 = 0$ xFE.

## 3.3.1 Some Examples of Signed and Unsigned Integer Arithmetic

Here are 8 Examples of Signed and Unsigned Operations in a 5 bit field:

1. Addition - Unsigned - No carry

2. Addition - Unsigned - With carry

```

11110 30

+ 00111 7

------ Carry indicates answer is 32 too small

1 00101 5 37 cannot be held in 5 bits

```

3. Subtraction - Unsigned - No Borrow

```

11110 30

+ 11001 -7 Add two's complement to effect subtraction

------

1 10111 23 Correct answer, carry of one indicates no borrowing

----- needed.

```

4. Subtraction - Unsigned - With Borrow

```

00111 7

+ 00010 -30 Add two's complement to effect subtraction

-----

0 01001 9 Carry zero implies a borrow of 32 was needed.

```

5. Addition - Signed - No overflow

6. Addition - Signed - With overflow

```

01010 10

+ 00111 7

------ 17 cannot be held in 5 bit two's complement

0 10001 -15 Carry into and out of msb different.

```

7. Subtraction - Signed - No overflow

8. Subtraction - Signed - With overflow

| Decimal<br>Value | <br> | Expo | onent |      |      | Mant: | issa |      |      | Hex representation |

|------------------|------|------|-------|------|------|-------|------|------|------|--------------------|

| 0                | 0    | 000  | 0000  | 0000 | 0000 | 0000  | 0000 | 0000 | 0000 | 0x0000_0000        |

| 1                | 0    | 000  | 0001  | 1000 | 0000 | 0000  | 0000 | 0000 | 0000 | 0x0180_0000        |

| -1               | 1    | 000  | 0001  | 1000 | 0000 | 0000  | 0000 | 0000 | 0000 | 0x8180_0000        |

| 2                | 0    | 000  | 0010  | 1000 | 0000 | 0000  | 0000 | 0000 | 0000 | 0x0280_0000        |

| 2.5              | 0    | 000  | 0010  | 1010 | 0000 | 0000  | 0000 | 0000 | 0000 | 0x02A0_0000        |

| 0.25             | 0    | 111  | 1111  | 1000 | 0000 | 0000  | 0000 | 0000 | 0000 | 0x7F80_0000        |

Table 3.1: Floating Point Representation Example (32 bit)

In overflow cases the sign of the result is always wrong (i.e. the N bit is inverted, so that's why we exclusive-or N with V in the conditional branches).

#### 3.4 Representing Floating Point Numbers

Floating point numbers are represented using three fields, a mantissa, a sign flag and an exponent packed into the 32 bit word. The exponent is generally to the base two. The exponent can be in two's complement to allow numbers smaller than  $\pm 1/2$ ..

For example, a 32 bit word may use the most significant bit as the sign, the next seven bits as the exponent (-64 to +63) and the next 24 bits as the mantissa with the first mantissa bit having significance 0.5.

Some examples Note that bit 23 is set for all numbers except zero and numbers very close to zero. This is the *normal form* for them and generally offers greatest precision, although many numbers may be accurately represented not in normal form.

A 24 bit mantissa gives  $24 \times log_{10}(2) = 7$  decimal digits of precision. The maximum value is approximately  $2^{63}$  which is 9.2E18 and the smallest value is about  $2^{-64}$  which is 5.4E-20.

Most processors (or floating point coprocessors) have a special set of instructions and special registers to process and hold floating point numbers.

Many processors also support extended precision floating point, which uses two words per number. The first byte of the additional word is not used, but the remaining three provide another 24 bits of mantissa, doubling the precision to about 14 decimal digits.

Always remember that floating point numbers are only an approximation to real numbers they secretly have discrete values while deluding you into thinking them continuous.

The illustrated representation is not quite the Standard IEEE system used in most of today's systems. The IEEE system is slightly more advanced, using the concept of a 'hidden bit'.

#### 3.5 Representing Text

Text may be represented using the American Standard Code for Information Interchange (ASCII) coding. Seven bits are used, giving 128 possible codes. Codes from 0 to 31 are non-printing control characters, such as warning bell, backspace and carriage return.

One byte in memory is normally used for one ASCII character, so four are stored in each 32 bit word. Processors where the word size is greater than one provide special instructions

#### ASCII Character Set

|   |       | 2  | 3 | 4 | 5 | 6 | 7     |

|---|-------|----|---|---|---|---|-------|

| 0 | <br>I | sp | 0 | @ | P | ΄ | <br>р |

| 1 | -     | !  | 1 | Α | Q | a | q     |

| 2 | -     | 11 | 2 | В | R | b | r     |

| 3 | -     | #  | 3 | C | S | С | s     |

| 4 | -     | \$ | 4 | D | Т | d | t     |

| 5 | -     | %  | 5 | E | U | е | u     |

| 6 | -     | &  | 6 | F | V | f | v     |

| 7 | -     | ,  | 7 | G | W | g | W     |

| 8 | -     | (  | 8 | H | X | h | x     |

| 9 | -     | )  | 9 | I | Y | i | У     |

| Α | -     | *  | : | J | Z | j | z     |

| В | -     | +  | ; | K | [ | k | {     |

| С | -     | ,  | < | L | \ | 1 | - 1   |

| D | -     | -  | = | M | ] | m | }     |

| E | -     |    | > | N | ^ | n | ~     |

| F | Ι     | /  | ? | 0 | - | 0 | del   |

The ASCII code for a particular character is 16 times the number at the top plus the number down the side.

Table 3.2: ASCI Character Set

| Address | Value | Comment                    |

|---------|-------|----------------------------|

| 0xF30   | 2     | Constructor tag for a leaf |

| 0xF34   | 8     | Integer 8                  |

|         |       |                            |

|         |       |                            |

| 0xF3C   | 1     | Constructor tag for a node |

| 0xF40   | 6     | Integer 6                  |

| 0xF44   | 7     | Integer 7                  |

| 0xF48   | 0xF30 | Address of inner node      |

|         |       |                            |

|         |       |                            |

| 0x1000  | 1     | Constructor tag for a node |

| 0x1004  | 4     | Integer 4                  |

| 0x1008  | 5     | Integer 5                  |

| 0x100C  | 0xF3C | Address of inner node      |

Figure 3.1: Pointer structure stored in memory

for access to individual bytes in memory to ease text handling. The frequent need to handle text on a computer has been a major influence in causing modern processors to use byte addressing.

### 3.6 Representing Data Structures

A pointer is a data value which is the address of some further data. These may be stored in memory. Consider the ML datatype

This could be stored as shown if figure 3.1. Note that the ML system has allocated constructor tag numbers to each instance of a rec so that it can tell whether it is a node (tag=1) or a leaf(tag=2). The inner nodes were allocated first, so are likely to be stored at a lower address, as shown.

Here is a selection of the 18 machine instructions for the EDSAC computer [From Wilkes and Renwick, 1949].

- A n  $\,$  Add the number in storage location n to the accumulator register.

- $\mbox{\ensuremath{\mathtt{H}}}$  n  $\,\,$  Transfer the number in storage location n into the multiplier register.

- E n If the number in the accumulator is greater than or equal to zero, execute next the order [instruction] which stands in storage location n; otherwise proceed serially.

- In Read the next row of holes on the tape and place the resulting five digits in the least significant places of storage location n.

- Z Stop the machine and ring the warning bell.

These instructions are here represented in a symbolic form, using a one character symbol for each instruction. Each instruction also has a binary representation, which is the machine instruction code placed in memory for evaluation by the processor.

Figure 3.2: Some of the instructions available on the EDSAC computer.

#### 3.7 Representing Machine Instructions

Processors vary in the number of bytes used for an instruction, but most modern RISC processors use 4 bytes for each instruction. An example RISC processor is the ARM device developed in Cambridge. Older processors, such as the Motorola 68000 (used in Macs) and the Intel family used in PCs have variable length instructions. Instructions vary from one to tens of bytes long.

Most processors contain at least the following basic instructions

```

ADD, SUBTRACT, LOAD, STORE, JUMP, JSR, RTS, TRAP, XOR, AND, OR, ROTATE, COMPARE, HALT, NOP

```

but the size and style of instruction sets varies wildly. Each instruction can be used with one or more *addressing modes*. The addressing modes provide a set of different ways of specifying the operands. The operands are the arguments to or result from the instruction.

The processor designer invents the instruction set, addressing mode set, number of registers etc. He allocates an 'opcode' for each instruction and an encoding into memory for each instruction and its addressing mode.

#### 3.7.1 Addressing Modes

In general, processors offer combinations of the following addressing modes:

Register a field specifies a register number

Absolute a field is the memory address of the operand

PC relative a field is an offset from the instruction

Immediate a field is the operand (read only)

**Register indirect** a field specifies a register which contains the address of the operand.

**Indexed** a field is an offset to be added to a specified register to generate the address of the operand.

= One Binary Digit

Figure 3.3: A user programming model for an 8 bit processor with 16 bit address space.

| Instruction | Opcode | Modes       |

|-------------|--------|-------------|

|             |        |             |

| ADD         | 1      | RA, RO-R, I |

| SUBTRACT    | 2      | RA, RO-R, I |

| LOAD        | 3      | RA, RO-R, I |

| STORE       | 4      | RA, RO-R    |

| JUMP        | 5      | JC          |

| RTS         | 6      | none        |

| JSR         | 7      | A           |

| etc         |        |             |

|             |        |             |

Table 3.3: Part of instruction set for example processor

Memory Indirect a field is an absolute address of the first of a number of bytes in memory which hold the actual operand address.

By 'field' I mean a set of bits in the instruction.

#### 3.7.2 Example Instruction Set

Here we develop and present a subset of the instruction set of a simple, fictional 8 bit processor. This example processor is typical in style to the first generation 8 bit processors, such as the Z80, 6502 and 6800.

We will have four 8-bit general registers in the processor (needing two bits to address a register), a 65536 location address space (needing two bytes to specify an address), and variable length instructions. We will also need a 16 bit program counter and a flags register and a stack pointer register. This gives us the user programming model shown in figure 3.3.

For instance, the instruction set might start as shown in table 3.3: where the opcode is stored in the top four bits of the first byte of each instruction. The addressing mode set might include those shown in table 3.4.

For the instructions which can take a variety of addressing modes, bits in the instruction must specify which mode is in use. A table is required to allocate these:

| Mode | M1 | МО |

|------|----|----|

|      |    |    |

| RA   | 0  | 0  |

| RO-R | 0  | 1  |

| I    | 1  | 0  |

| Mode | Meaning                                                                                                                                                                      |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A    | One 16 bit address follows in the next two bytes                                                                                                                             |

| RA   | One register and one memory location where the register is in the bottom two bits of the first byte and a 16 bit address is in the next two bytes following the instruction. |

| RO-R | The low two bits give a register for the source operand. Register zero is implied as the destination operand.                                                                |

| I    | The operand is in the next byte.                                                                                                                                             |

| JC   | A condition (cc) in the bottom four bits of<br>the first byte and a 16 bit address in the<br>next two locations.                                                             |

|      |                                                                                                                                                                              |

Table 3.4: Addressing modes for example procsessor

-----

The processor must always be able to tell how long the instruction is going to be from the bytes read so far, and so how many bytes to read in total. This depends on the addressing mode. We can put the mode in the first byte between the opcode and the register number, giving the following format

```

B7 B6 B5 B4 B3 B2 B1 B0 <---opcode---> M1 M0 <-reg->

```

The values of cc in the conditional branch are typically used in a manner similar to figure 3.4. giving us this format

```

B7 B6 B5 B4 B3 B2 B1 B0 <---opcode---> cc3 cc2 cc1 cc0.

```

Examples of use - I will do some examples in the lectures.

```

cc Condition

0 Branch always

1 Branch never (NOP)

2 Branch if N (ie if N is a one)

3 Branch if "N (ie if N is a zero)

4 Branch if V

5 Branch if ~V

6 Branch if Z

7

Branch if ~Z

8 Branch if C

Branch if ~C

Α

Branch if ~Z & ~C

В

Branch if ~(~Z & ~C)

Branch if N != V

D

Branch if N == V

E Branch if ^{\sim}Z and N == V

F Branch if ~(~Z and N == V)

```

Figure 3.4: Table of branch conditions

# 4 Caches

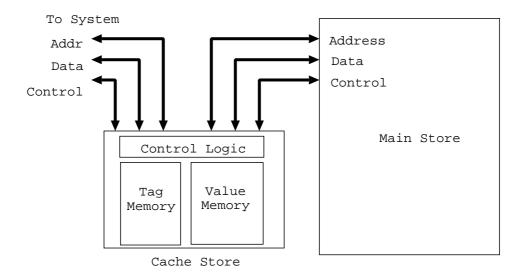

A cache memory is a small, fast store used to enhance the performance of a larger, slower store. The cache contains data recently retrieved from (or written to) the slower store with the hope that the information will be needed again.

Caches are widely used in systems

- Main processor cache of main memory

- VM unit cache of translations (VM mappings)

- Operating system cache of recently accessed disk pages

- Paging of physical memory under a VM system

- Distributed system cache of directory enquiries.

The hit ratio of a cache is the ratio of data retrievals that can be supplied by the cache to the total number of retrievals over some averaging interval.

Caches can be used to improve performance both for reading and writing. A write-through cache updates the main store when data is written, giving no performance gain for writing, but a copy-back cache keeps track of which entries are 'dirty' meaning that they have been updated but the write to main store has not yet occurred. The cache writes dirty entries out to main store when the main store would otherwise be idle.

## 4.1 A note on Cache Implementation

Implementation of caches and associative stores has been widely studied. Internally, a cache may be directly mapped, fully associative or set-associative. A directly mapped cache has only one place in the cache memory where an item from main store may be cached, meaning there is only one item to check to determine a cache hit and no doubt about where to cache new data. This has quite low performance in general, but is fast. A fully associative cache, on the other hand, has no restrictions on where in the cache an item is cached, meaning that every location needs to be examined before a hit can be determined. This is slow if done in software and complex when done in hardware, but generally has the highest hit ratio. A set-associative cache has a set of locations used for each item in main store, with a typical set size of four. Only the small number of entries in the set need to be checked to determine a hit. This clearly gives a compromise in performance and complexity and is widely used.

#### 4.2 Example of Cache Speedup

Consider a cache with a hit ratio of about 90 percent and built from technology which operates 15 times faster than the main store. If the system speed without the cache is 1, then the system speed with the cache is

$$1/[(0.1 \times 1/1) + (0.9 \times 1/15)] = 6.25$$

In general, if the hit ratio of a cache is much less than about 0.9 the benefit of the cache starts to be small.

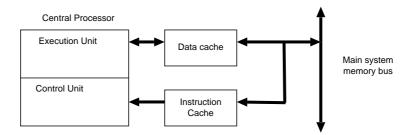

#### 4.3 Instruction and Data Caches

Modern VLSI (very large scale intergration) is able to fit a microprocessor and a significant amount of cache memory onto a single silicon chip, about 1 cm on a side.

${\bf Figure}~4.1:~\textbf{Hardware Cache Generic Arrangement}$

${\bf Figure}~4.2:~\textbf{Instruction and Data Caches}$

It is common to divide the memory into two separate caches, one for instructions and one for data. The advantage of this is that they can be accessed in parallel, doubling performance. While data (operands) for the current instruction are being transferred between the processor and the data cache, in parallel the next instruction can be loaded from the instruction cache.

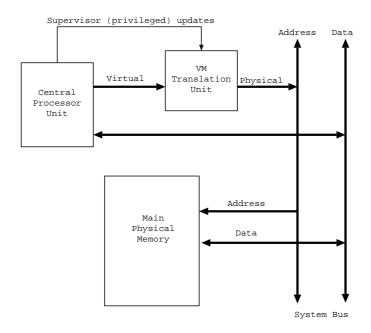

# 5 Virtual Memory Translation Hardware

Most modern general purpose computers have virtual memory translation hardware and this is often on the microprocessor chip, along with the CPU. The VM unit contains tables which can only be modified by the CPU when the privilege flag is set.

Figure 5.1 shows that a virtual memory system is created by feeding the address generated by the processor (the *virtual address*) through a memory translation unit to give the actual memory address to be used (the *physical address*). For any virtual address, the address translator produces either a physical address, which enables the instruction to proceed, or else a translation fault interrupt to the processor. Therefore, each time the processor tries to touch any memory which is not physically mapped, it gets such an interrupt, and systems software then either considers this a real error, or else reconfigures real memory, reprograms the address translator accordingly, and returns execution to the point of the instruction which failed, so that it may be run more successfully.

The instructions which modify the address translator mapping are privileged.

Virtual memory systems have several benefits:

- A program can use more memory than physically exists using paging.

- Separate processes will use separate programmings of the translation hardware, giving them isolation from each other, or controlled sharing.

- It is possible to have more memory than the processor can address.

- Address space becomes cheap, so that if you have to start a data structure at an arbitrary address (e.g. the base of a stack) then this can be in the middle of virtual address space, rather than in the middle of (expensive) real address space.

A VM system clearly has an overhead in translating every address generated by the processor. The delay through a translation unit will add a small percentage of time to each cycle. This penalty is normally outweighed by the above benefits of VM. (If the processor has caches which operate on virtual addresses, then only cache misses need to be translated, which is a help.)

## 5.1 VM unit implementation

Most translation units simply contain an associative memory which maps the input address to the output address. The low 12 or so address bits are not normally mapped, resulting in the concept of memory *pages*, inside which, the logical offset is equal to the physical offset. The associative memory is known as the *translation lookaside buffer* or TLB for short.

#### 5.2 Paging

An operating system can supply more virtual memory than there is physical real memory if it *pages* memory onto a backing store, such as a disk. To do this, pages of memory which have not been used for a while are copied onto the disk and then become free for allocation as more fresh memory is required. The copying can be done while the computer is idle or when the computer runs out of empty memory and more is needed.

Fresh memory is needed when the program addresses memory in a page which has never been allocated. This is detected by the operating system through a page fault interrupt. Alternatively, a page fault occurs when the program access memory which has been used before and is now paged out to disk. The processor must again find 'fresh' memory, but this

Figure 5.1: Virtual Memory Basic Architecture

time must first read back the copied out data before returning to the faulting instruction for another go.

It is important not to page-out the paging-in software.

# 6 Coprocessing

A coprocessor is a hardware unit which attaches closely to a main processor and contains its own registers and a specialised ALU. The coprocessor ALU is able to perform operations outside those supported directly by the ALU on the main processor. When a coprocessor is not fitted to a computer, the operations it would have performed must instead be performed using multiple general purpose instructions on the main processor, which is slower.

Coprocessors are often used for:

- Floating point arithmetic

- Graphical operations (area fill, curve draw etc)

- Encryption/decryption

- CRC calculation.

Instruction opcodes for the coprocessor are generally reserved within the instruction set of the main processor. When the coprocessor is absent, execution of one of these opcodes causes an exception (interrupt) to enable emulation software to run. When the coprocessor is present its instructions are essentially NOPs (no operations) to the main processor.

In some architectures, it is possible to use the main processor's addressing modes and operand address generation function for loads and stores to the registers in the coprocessor. For a load, the coprocessor just 'snoops' on the data bus. For a store, the main processor must make sure its databus is disabled (high impedance) so that the coprocessor can yield its register's contents onto the bus.

Figure 6.1: Coprocessor Typical Configuration

# 7 Input and Output

Input and output from the computer is via hardware devices connected to the bus known as peripherals. Typical peripherals are

- Universal asynchronous receiver transmitter (UART) (Better known as a serial port)

- Floppy disk controller

- IDE or SCSI bus controller for CD roms, hard disks etc.

- Keyboard

- Real-time clock

- Non-volatile memory

- Floppy disk controller

- Parallel port (for Centronix compatible printer)

- Network interface

#### 7.1 Input and Output Cycles

The processor can interact with these peripherals through three main mechanisms:

- 1a. Programmed memory mapped IO

- **1b.** IO space instructions

- 2. Interrupts

- 3. Direct memory access

We will look at these in turn. In most systems, all three mechanisms are used.

- 1a. Programmed memory mapped IO In memory mapped IO a small set of (uncached) locations in address space (outside main memory) is allocated to a peripheral with one location per register inside the peripheral. The peripherals are then accessed using the same instructions as used for access to main memory: ie load and store instructions. Unlike memory, the data found in the locations which are actually peripheral registers tend to change from one read cycle to the next. Storing the same value twice in one of the registers is also a potentially sensible operation, since the store might be of an ASCII character and each store operation may result in the character being printed on the printer.

- 1b. IO space instructions Older computers, especially those with limited address space, had special READ and WRITE instructions which performed the same functions as LOAD and STORE for memory mapped IO, generating identical bus cycles, except that an additional signal from the processor was asserted to indicate to the address space decoders that an IO space decode was required.

- 2. Interrupts The interrupt is a means for the peripheral to inform the processor that it is ready for attention. Without an interrupt, the processor would have to periodically poll the peripheral with a programmed IO instruction which is a wasteful effort.

Figure 7.1: **UART Logic Symbol**

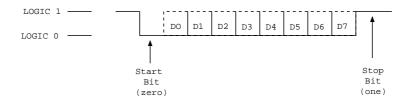

Figure 7.2: **RS232 transmission format**

3. Direct memory access (DMA) Direct memory access is where the processor temporarily gives up control of the bus (i.e. being bus master) and allows the peripheral to take control. The peripheral generates addresses and control signals to transfer data to or from the memory directly. DMA is normally faster for bulk data transfer than programmed IO since every bus cycle carries useful data. Programmed IO is slower because it requires each data word to be read from device/memory and then written to memory/device via a processor register with instruction fetch cycles in between.

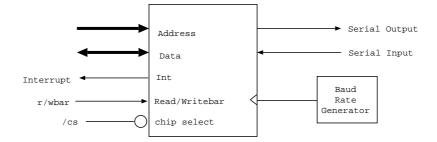

#### 7.2 Example: A UART for a serial port

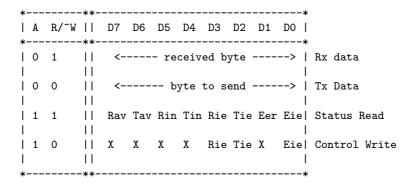

A simple UART (universal asynchronous receiver and transmitter) may be addressed through two registers, a data register and a control/status register. A byte written to the data register is serialised by the UART and leaves the computer. Serial data which arrives may be read by the processor through the data register. The control/status register has status flags which change by themselves and control bits which retain the values written there by the processor.

A minimal interface model could be as follows (only one address line is needed if there are just two locations within the device):

The status bits have the following meanings:

Rav - a one if a received byte is available.

Figure 7.3: Programming model for an example UART

- Tav a one if the transmit register is empty and so available for the next transmission

- Rin the interrupt line is asserted because the receive register is non-empty and Rie is set.

- Tin the interrupt line is asserted because the transmit register is empty and Tie is asserted.

- Eer an error of some sort has occurred since this register was last read.

The control bits are all interrupt enables. If set by the processor, then the interrupt output from the uart will be active when the interrupting event occurs.

A number of errors can occur, even with such a simple device. We have three over-run/underrun cases:

- 1. Processor reads data register when Rav zero

- 2. Data arrives when Rav is set because the processor has not read out the last byte yet.

- 3. Processor writes to data register when Tav zero because it has not waited for the last byte to be serialised.

Other errors can occur on the receive side if the stop bit is missing or if the UART detects the input data changing in what it thinks is the middle of a bit cell.

The error flag in this simple UART is not really much use because there is no cause indicator register. Real UARTs have multiple error flags and also allow the programmer to enable automatic insertion and checking of a parity bit between the last data bit and the stop bit.

Note that an enhanced version of the UART could insert a FIFO memory in series with its transmit and receive streams without modifying the programming interface model. This would reduce the chance of overrun or underrun and can reduce the number of interrupts to the processor.

#### 7.2.1 UART Programming Procedure

Typically the system will keep input and output circular buffers for data received but not yet processed and data generated but not yet transmitted. Overall this calls for three sections of code to be written:

wrch a routine to queue a byte for output

rdch a routine to read an input byte

**uisr** the interrupt service routine.

#### 7.3 Keyboard and Mouse Interfaces

Most keyboards and mice these days have a serial link to the system unit. A circuit very like a UART is required for their interface.

Keyboards normally generate *scan codes* rather than ASCII directly. A code is generated each time each key is pressed or released. In this way, different alphabets and layouts can be supported merely by changing the system software and keytops. Codes are generated when a key is released, since for shift and control keys, the computer needs to know when the key was released.

Mice generate a code each time a button is pressed or released and each time they cross a line in their quantisation grid. The cross code is one of four, indicating one of the four possible directions of crossing.

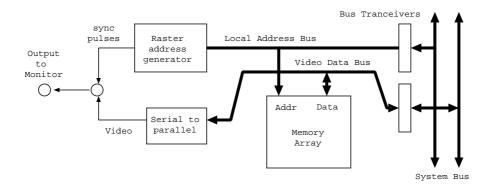

Figure 7.4: Memory Mapped Display Controller Block Diagram

#### 7.4 Memory-mapped display

A memory-mapped display looks like a normal region of RAM to the processor. A pixel-mapped monochrome display where each pixel is either on or off needs one bit per pixel. If it is 1024 pixels by 650 pixels then the memory region needed is

$$1024 \times 650/8 \text{ bytes} = 83200 \text{ bytes}.$$

Displays which have colour or greyscales require more bits per pixel. Normally the lowest byte in memory corresponds to the top left corner of the screen and the ordering is left-to-right, top-to-bottom. The bits making up each each byte are either used msb first or lsb first to make up eight horizontal pixels.

Systems software is provided which takes a stream of ASCII bytes and renders them using a font table (or character generator table). The software typically also provides a cursor and interprets the non-printing control characters to move the cursor.

#### 7.5 Intelligent Devices

Sometimes an I/O device will help in the data processing. Examples are graphical display devices which accept high-level commands for drawing circles or shading polygons and network interface devices which do scatter/gather of blocks of memory chained together by the main processor or perform retransmission in the case of an error. These intelligent devices process in parallel with the main host processor, thereby freeing it up.

Some devices today contain processors yet retain their older dumb interface to the host processor. This gives backwards compatibility. Examples are disk drives which perform internal caching and read-ahead of data blocks, without telling the host processor, and even a large class of PC keyboards which send a convoluted sequence of numeric-shift down and up strokes each side of a press of the cursor key press in order to emulate early PC keyboards which did not have dedicated cursor keys.

# 8 Disks, Controllers and Filing Systems

Disk drives record data serially on a rotating magnetic medium in concentric tracks. On a hard disk drive there are multiple platters, whereas on a floppy there is just the single plastic disk (one platter). Each platter has two surfaces each with its own read/write head. The set of tracks across the platters which can be accessed without moving the head assembly are known as a *cylinder*.

The sector is the basic unit of reading or writing and typically contains between 128 and 2048 bytes.

A note on sectoring: Disks are either hard or soft sectored. This refers to the method of knowing which sector is which around a track. A hard-sectored disk uses a physical index mark on the hub which causes sector pulses to be sent to the controller as the disk rotates, with a special double pulse, once per rotation, to identify sector 0. With a soft-sectored disk, the sectors consist of two parts, a header containing the address, put there when the disk is formatted, and then the sector data region which is updated each time the sector is written. Under hard-sectoring, the controller counts pulses from the double pulse to the required sector, whereas with soft-sectoring, the controller reads each sector header as it passes.

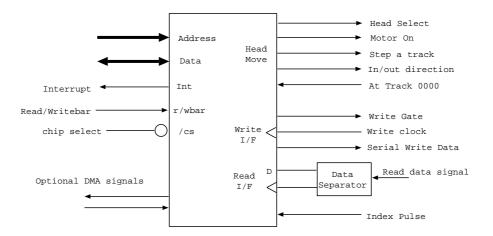

#### 8.1 Disk Drive Controller

A disk controller sits on the processor bus and generates control signals for the disk drive. Hard disks and floppy disks are similar in most respects, as the typical parameters in figure 8.1 shows.

The functions of a disk controller are:

- Generate pulses for moving the head in or out

- Generate head select value

- Scan sector headers (or count index pulses)

- Convert data to/from serial format for the head.

- Generate/check a CRC (cyclic redundancy check) for each sector.

| Parameter         | Hard Drive | Floppy | Drive  |

|-------------------|------------|--------|--------|

|                   |            |        |        |

| Number of platte  | rs 4       | 1      |        |

| Number of heads   | 8          | 2      |        |

| Rotation speed    | 3600       | 300    | rpm    |

| Bit rate (MFM)    | 10000      | 250    | kbps   |

| Bits per track    | 166        | 50     | kbits  |

| Bytes per track   | 20         | 6      | kbyte  |

| Sector size       | 1024       | 512    | bytes  |

| Sectors per track | k 18       | 9      |        |

| Cylinders         | 500        | 80     |        |

| Capacity          | 72000      | 737    | kbytes |

| Seek one track    |            |        | ms     |

| Seek full width   |            |        | ms     |

|                   |            |        |        |

Figure 8.1: Disk Drive Example Parameters

Figure 8.2: A Disk Controller

Disk drive timing is slow then fast: there may be milliseconds of delay between the desire to access a sector and the head being in the correct place, but once there, the data is read or written from/to the disk surface at full rotational speed. The following sequence of processor to controller interactions is typically used to overcome this:

- 1. Processor writes a command to the controller using programmed IO. The command is either a read or a write and contains the head, track and sector number.

- 2. The controller generates pulses to move the head assembly to the correct cylinder, waits for the correct sector to come under the head, then issues a DMA request.

- 3. The processor gives up the bus and the memory system sinks or sources the required sector's worth of data, then relinquishes the bus.

- 4. The controller generates an interrupt so that the processor may read a status register in the controller telling the outcome of the operation (e.g. CRC error) and then issue the next controller command.

A note on imbedded disk caches: Many modern disk controllers have a built-in track memory buffer RAM. The processor may access this RAM at its own speed, removing the real-time requirement to transfer data from main processor store to/from the disk. Disk drives for PCs typically have multiple such buffers, arranged to provide caching, in order to increase performance when using the primitive systems software on a basic PC, but it is always more expensive to invest in specialised RAM subsystems than using part of the main system memory. The Linux OS can use all 'unused' system memory as a disk cache.

#### 8.2 Data arrangement on disk

In a typical operating system, a disk will contain files and directories and each file will consist of an ordered finite sequence of bytes. The filing system has conventions which map these objects onto the array of sectors provided by the disk. The disk must also explicitly, or implicitly, represent a free sector list.

A simple *serial* file system keeps files in consecutive sectors, but this leads to free space fragmentation over a period of time. The fragmentation problem occurs when the medium (disk) is quite old and has had many files created and then deleted. The effect is that sometimes a new file cannot be writtent to the disk beacuse, although there is sufficient free space, it is fragmented into small chunks, with no chunk large enough. *Compaction* is the name of the process of copying things around so that the free space is coalesced.

A sequential file system links arbitrary sectors into a chain and so overcomes the 'hard' fragmentation problem of not being able to write a new file, but there is a 'soft' fragmentation

problem which can result in low performance as files weave over the medium in ever more twisty chains.

A random access file system can be built on a sequential file system. For random access to an offset within a file it is necessary to have stored, or on-the-fly generate, an index which maps offsets within the file to a sector number and byte within the sector.

#### 8.3 Example: MSDOS File Organisation

In MSDOS, a disk is first logically divided into four sections with the following typical sizes.

- 1. The boot block. 1 sector.

- **2a.** The file allocation table (FAT) 3 sectors.

- **2b.** A copy of the FAT 3 sectors.

- **3.** The root directory 5 sectors.

- 4. The dynamically allocated remainder

The boot block is on cylinder 0, head 0, sector 1 for all disk types and encodes a description of the disk parameters including sides, tracks, sectors per track and bytes per sector. This establishes a logical to physical mapping function, such that given any integer in the range 1 to the number of sectors on the disk, the track, side and sector number can be calculated. The rest of the filing system can then simply deal with logical sector numbers. The mapping is structured so that a small change in logical sector number results in a small displacement on the disk surface, so that serial allocation of sector numbers as a file is written does not cause the head to scurry all over the disk. The boot block also gives the FAT size and the sector number of the first sector in the root directory.

The file allocation table (FAT) is an array indexed by a logical sector number where each entry is also a logic sector number. There are two copies of it in order to reduce the possibility of loss. They are (should be) always the same. The FAT is used to stitch sectors together into a chain (linked list), since given a sector number, the FAT can give the successor number. Two special values are used: one to represent that a sector is not in use and one for the last sector of a chain.

The directory consists of a number of 32 byte fixed-length records. Each may hold a file or subdirectory name. The bytes are used as follows:

```

0-7

File name

8-10

Filename extension

Attribute flags

1=Read only, 2=Hidden, 4=System file, 8=Volume label

16=subdirectory, 32=Archived flag

Reserved

12-21

22-23

Time of modification

24-25

Date of modification

26 - 27

Starting logical sector number

28-31 File size in bytes

```

Byte 0 can also hold a non-printing ASCII code to represent the directory slot status:

```

00=never used slot

E5=erased slot (was in use once).

```

Here is an example directory listing.

```

HTCORE

CV

8:57:52 18-july-1994

6005

(cluster=52, sector=115)

LINKCTL

CV

8:57:56 18-july-1994 6373

(cluster=58, sector=127)

С

14:52:48 18-july-1994 34078 (cluster=265, sector=541)

TAB

11:38:56 18-july-1994 29630 (cluster=312, sector=635)

GAVINS

CV

20:20:28 23-oct-1994 7473 (cluster=351, sector=713)

VPI.US

```

```

VERIOUT C 20:20:8 23-oct-1994 4643 (cluster=348, sector=707) SYSDES N 17:18:48 15-april-1995 2581 (cluster=371, sector=753) Displayed total 358987 bytes. 354304 bytes free.

```

And here is the hexadecimal and ASCII display of part of the sector containing it:

```

48 54 43 4F 52 45 20 20 43 56 20 00 00 00 00 00

HTCORE CV ....

00 00 00 00 00 00 3A 47 F2 1C 34 00 75 17 00 00

....:G..4.u...

4C 49 4E 4B 43 54 4C 20 43 56 20 00 00 00 00 00

LINKCTL CV ....

00 00 00 00 00 00 3C 47 F2 1C 3A 00 E5 18 00 00

......<G..:....

54 41 42 20 20 20 20 20 43 20 20 20 00 00 00 00

TAB

C ....

00 00 00 00 00 00 98 76 F2 1C 09 01 1E 85 00 00

. . . . . . . v . . . . . . . .

GAVINS CV ....

47 41 56 49 4E 53 20 20 43 56 20 20 00 00 00 00

00 00 00 00 00 00 DC 5C F2 1C 38 01 BE 73 00 00

....\..8..s..

56 50 40 55 53 20 20 20 43 20 20 00 00 00 00 00

VPLUS C ....

....W._.1...

00 00 00 00 00 00 8E A2 57 1D 5F 01 31 1D 00 00

56 45 52 49 4F 55 54 20 43 20 20 00 00 00 00 00

VERIOUT C .....

00 00 00 00 00 00 84 A2 57 1D 5C 01 23 12 00 00

.......W.\.#...

53 59 53 44 45 53 20 20 4E 20 20 20 00 00 00 00

SYSDES N ....

00 00 00 00 00 00 58 8A 8F 1E 73 01 15 0A 00 00

.....X...s....

. . . . . . . . . . . . . . . . .

. . . . . . . . . . . . . . . .

```

#### 8.3.1 Sequential Read and Write Algorithms

Most operating systems offer sequential, byte-orientated read and write access to files. We need two sets of three subroutines available for calling by the application program

- 1. Open the file file name is an argument,

- 2. Transfer a byte of data,

- 3. Close the file,

one set for reading, another set for writing.

The data transfer phase transfers bytes to or from a RAM buffer of size one sector maintained by the filing system software. For writing, when all of the bytes from one sector have been supplied, the filing system writes out the RAM buffer to the device and chains to a new sector. For reading, the filing system first reads a sector from the device into the buffer, then suplies the bytes one at a time to the application. When all of the bytes from one sector have been supplied, the filing system chains to the next sector.

To write a file the following algorithm can be used (if the file existed before, then it should first be deleted):

#### Open:

- 1. Load the FAT into memory

- 2. Find a free sector to be the current sector

Data Write: (This is done as many times as needed)

- 3. Store bytes in a sector-sized memory buffer until full

- 4. Write the buffer to the disk at the current sector address

- 5. Find a nearby free sector as the current sector

- Make an entry in the memory copy of the FAT to link the old current sector to the new current sector.

#### Close:

- 7: Write partially filled buffer to current sector

- 8: Find an empty directory slot and make an entry.

- 9: Write out the memory copy of the FAT (twice).

To sequentially read a file

#### Open:

1: Scan the directory for the file name If not found then raise 'no such file' error. 2: Set the current sector to be the starting sector specified in the directory entry.

Data Read: (This is repeated until we reach the end of file)

- 3: Read the current sector into a memory buffer

- $4 \colon \operatorname{Supply}$  the bytes to the application

- 5: Chain to next sector.

# Close:

6: No disk activity - just mark buffer as free for use again.

# 9 System Busses

The performance of a computer is critically dependent on the bus cycle time, but the speed that a bus can reliably be operated at is inversely proportional to the number of devices connected and its physical extent.

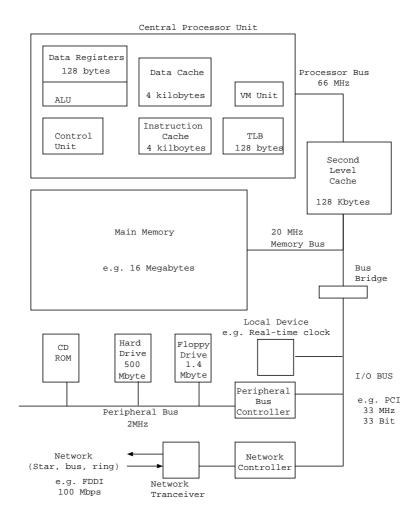

Two or more busses are used in all but the simplest imbedded microcontrollers rather than having a single bus which interconnects all system devices with a maximum of compromise.

#### 9.1 The Processor Bus

The fastest bus connects the processor to its cache. The cycle rate of this bus is also the processor clock cycle rate (e.g. 66 MHz) for modern processor designs. When a microprocessor and its cache are on the same chip, this bus is entirely on the chip too, but the processor must slow down to the external bus speed each time the cache misses.

## 9.2 The Memory Bus

The next speed bus is the main memory bus, which is optimised mainly for memory access cycles, and so runs at the speed of the memory system. Typical DRAM systems provide 32 bits at a time and require 120 nanoseconds to respond to a random request and 120 nanoseconds to recover afterwards. The cache controller for the main processor, after a miss, will often also fetch the surrounding 12 bytes, since many DRAM chips can supply these with a delay of 40 nanoseconds per 32 bit word.

On a high-performance computer, the width of this bus may be between 128 and 1024 bits. This enables use of the same DRAM chips as used widely in cheap computers, but gives greater memory bandwidth.

## 9.3 Peripheral and IO Busses

Only a fraction (e.g. 1 to 15 percent) of processor cycles are to IO devices, and IO devices tend to

- be slow

- quite big

- require modular instantiation (e.g. they're on plug in cards),

- have a design lifetime longer than the processor's

- come from various manufacturers.

The memory bus would suffer in performance if it had to directly meet these requirements. This leads us to adopt a slower, separate, well-defined, stable bus specification for IO devices.

The bus bridge connects the memory bus to the IO bus. When the processor accesses IO space, the bus bridge copies the address to the IO bus and the data in the appropriate direction (read or write) and also generates wait states for the processor to match the bus speeds.

Direct memory access (DMA) (see also section 7.1) is supported over the bus bridge. An IO device can temporarily deny the processor access to its memory when a block of data is streaming in from or out to a device.

Figure 9.1: A system with multiple busses

#### 9.3.1 IO Bus Examples

History is littered with bus specifications. Example IO busses in common use today are:

IDE

SCSI

VME

USB

S Bus

**ISA**

PCI

**EISA**

IBM Channels

Fibrechannel

SCI

**IEEE-488**

Multibus

Nubus

Many computers today have both a local IO bus and a separate peripheral bus. The local IO bus tends to be directly addressed by the processor during programmed IO cycles and can also support DMA. It is confined to a printed circuit backplane or motherboard. The separate peripheral bus (e.g. SCSI) is connected by a special, semi-intelligent controller device and physically consists of ribbon cables.

#### 9.3.2 Peripheral Bus Example - SCSI

The small computer systems interface (SCSI) bus was defined by IEEE committee X3.131 in 1986 to connect disk drives, CD ROMs, tape streamers and other similar peripherals within a computer. The SCSI bus is connected to the host bus using a SCSI controller which is typically a single chip.

The wires making up SCSI are

```

DB0-7

- 8 bit data path

DBP

- parity bit on the data

ATN

- attention

BSY

- busy

ACK

- acknowledge

RST

- reset

MSG

- message

SEL

- select

C/D

- command or data

REQ

- request

I/0

- in or out

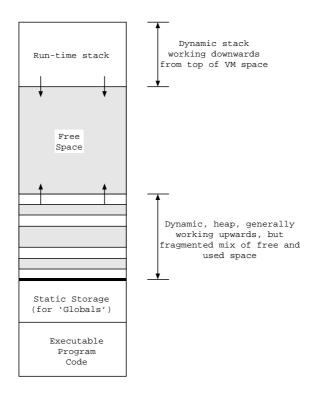

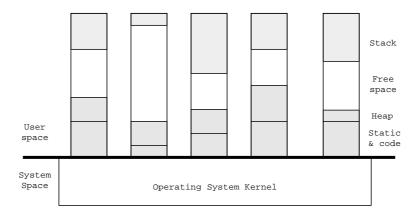

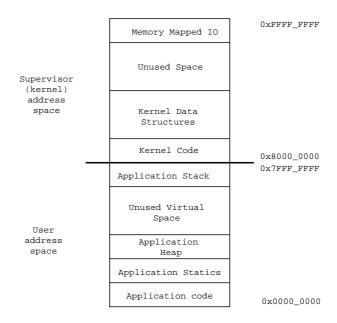

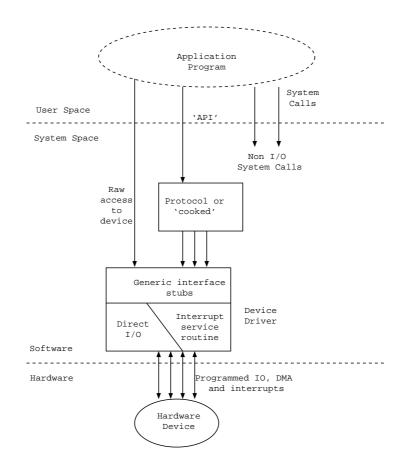

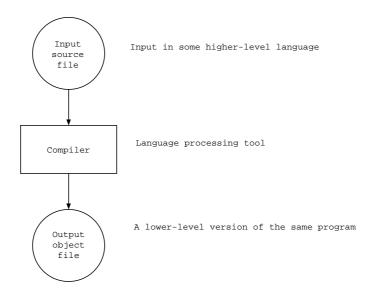

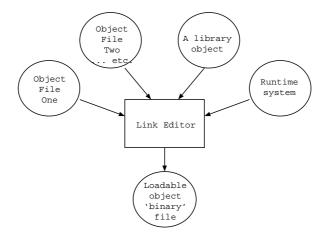

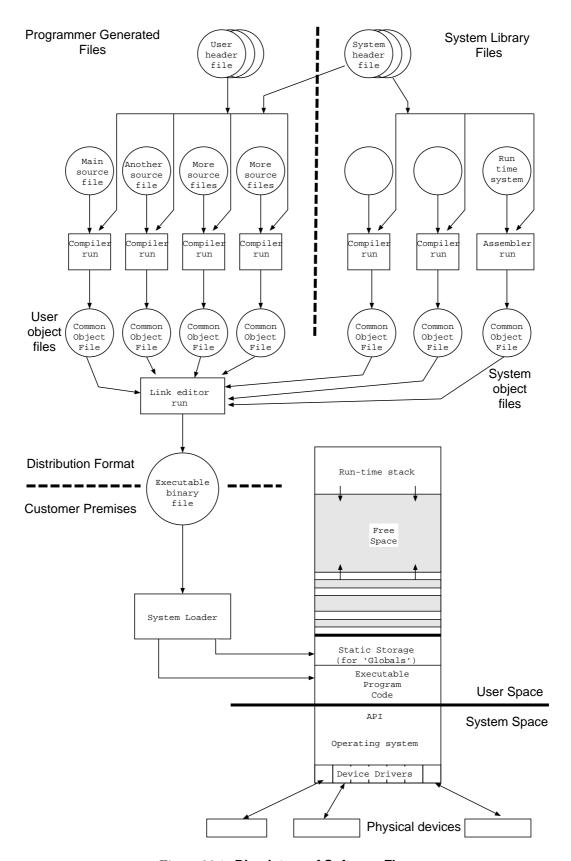

```