# TLM POWER3: Power Estimation Methodology for SystemC TLM 2.0

David Greaves Computer Laboratory University of Cambridge Cambridge CB3 0FD United Kingdom. David.Greaves@cl.cam.ac.uk

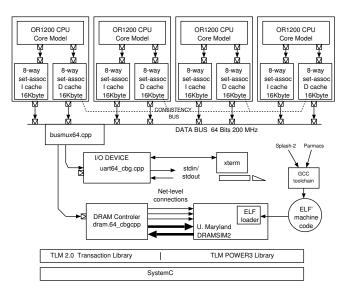

Fig. 1. Reference hardware platform for experiments (Quad-core OPENrisc with U. Maryland DRAM simulator.)

Abstract-We report on a SystemC add-on library which extends every SystemC module with non-functional data regarding power consumption and physical layout and which accumulates and estimates dynamic energy usage. It supports both phase/mode power modelling and energy-per-transaction logging for TLM (transactional-level modelling). Wiring energy is computed by counting bit-level activity within the TLM generic payload. Each leaf component can also register its physical dimensions to facilitate a wire length estimator that traverses the SystemC model hierarchy using either full placement or Rent's rule estimators. It also supports dynamic voltage islands and inter-chip wiring, where each transaction can consume energy according to the current supply voltage of the relevant islands and the nature of the interconnect. We report on basic peformance from some SPLASH-2 benchmarks running on a modelled OpenRISC quad-core platform.

With the current major emphasis on power consumption in electronic design it is important to be able to obtain power estimates during the architectural exploration phase. Power consumption is an emergent property arising once hardware Mehboob Yasin Computer Laboratory King Faisal University Al-Ahasa Saudi Arabia.

and software have been selected. For results to be numerically accurate, a detailed, net-level layout of the design is required in the chosen target technology. This level of detail is inconsistent with rapid prototyping. However, with wiring power becoming the dominant contributor in recent generations of VLSI technology, early indications of this aspect are becoming more essential. Indicators that are relatively accurate become useful. Relatively accurate indicators may have unknown linear error factors in the values they report, but they certainly have the correct polarity in their partial derivatives, thereby allowing the designer to tell whether a change is better or worse.

TLM modelling using SystemC permits high-performance models to be created. The greatest performance is facilitated by using the blocking transaction style with loose timing (LT) and DMI (direct memory interaction). Using blocking transactions, interactions between a CPU and a cache, memory or I/O device are modelled as a simple method invocation with handshaking overheads being modelled simply by the call and return of the relevant subroutine [3]. The loose timing method allows a given initiator to hog the modelling workstation for an extended period of time, called its quantum, and thereby avoid the overhead of context switching needed to keep transactions and bus cycles strictly in the order they would really occur. DMI allows an initiator, such as a CPU, to make backdoor access to the workstation memory used to model the contents of RAMs and DRAMs, thereby avoiding the overheads of modelling caches and busses or NoCs (networks on chip). However, previous modelling systems have become highly inaccurate in terms of reported performance and (especially) power when these advanced modelling features are enabled.

Two previous libraries for SystemC power modelling are TLM POWER2 [6] and PKtool [13]. Our own library is called TLM POWER3 owing to its direct reuse of some infrastructure from TLM POWER2, but ideally one might merge it with PKtool so that the styles and approaches from both previous libraries are concurrently available. Higher-level approaches might also be included. For example, the Sesame approach to estimating power consumption uses an abstract model of execution, based on *computational event signatures* [8]. A similar higher-level approach was presented in [10], but built on SystemC.

The TLM POWER2 library for SystemC associated groups of SystemC modules with a pair of power account records called static and dynamic. The association was maintained either by inheriting a pw\_module parent as well as the standard sc\_module inheritance, or by setting a SystemC attribute to point to the appropriate set of accounts.<sup>1</sup> TLM POWER2 used the mode/phase approach to power modelling.

In the mode/phase approach, the consumption of an IP block is determined from its current state. The state of the block is characterized by both its phase and its mode. A mode is a particular DPM (Dynamic Power Management) mode (e.g. on, sleep, off). A phase, basically a functional phase, is characterized by its power and time duration (e.g. wait, read, compute). The available modes and phases are defined in a technology/instance file that is inspected by the constructor for the component. The constructor can nominate a specific file for a specific instance or the kind() of the component can be looked up and the details set for all instances of that kind of component. The behavioural model for the block must change mode and phase explicitly using calls such as

Infact, in the mode/phase approach of TLM POWER2, there is no specific support for transactional modelling or loose timing. The TLM calls are unannotated and the SystemC kernel must be advanced for the appropriate period of time while a component is in a given power mode/phase for the correct energy accumulation to be logged.

PKtool is another SystemC library for power modelling, but its basic approach is to count transitions at the net level. Wrappers are provided for all of the common SystemC datatypes used for modelling wires, such as sc\_uint<7>. When SystemC kernel time advances, the hamming distance of each wrapped type is computed and added to its transition count. The hamming distance is the number of bits that have changed value. For energy modelling, only the zero-to-one transition needs to be considered. A net will consume energy from the supply each time it rises, according to the standard  $\frac{1}{2}CV^2$  formula, where C is the net capacitance, which is proportional to its length. (As explained below, we use the same approach for our TLM calls, but we then automatically disable it in favour of performance). However, PKtool library does not help estimate net length, and despite some recent extensions for TLM modelling, it has no support for the TLM generic payload. Directly relating the events in the model to the SystemC kernel timestamp cannot support loosely-timed models which locally run ahead of the kernel.

#### I. OUR APPROACH: TLM POWER3

TLM POWER2 defined physical units for power and energy in the same way as SystemC itself defines physical units for time. All of the standard arithmetic operators are overloaded to have the expected behaviour. For instance, a power multiplied by a time results in an energy. In TLM POWER3, we have added new physical units for voltage, distance and area, along with the appropriately overloaded operators. A component can describe its physical size in its constructor using one of the following TLM\_POWER3 calls:

```

//Set actual dimensions of current component

void set_fixed_dimensions(pw_length x, pw_length y);

// Set additional area of current component

void set_excess_area(pw_area a,

float max_aspect_ratio=2.5);

// Select chip/voltage island for current component

// and its children.

void set_chip_name(string chipname, string island);

```

The former sets the actual dimensions of the current component, leading to a warning if this is smaller than the sum of its components. The excess\_area call describes the additional area of the current component beyond that of the sum of its child components. The component is assumed to be flexible in shape from square up to an oblong of maximum aspect ratio specified. Aspect ratio is, however, ignored by our provided basic estimator that just sums areas within a component and does not attempt to give them co-ordinates within the component. Components can be specified to be placed on different chips or regions of chips but the default is to be on the same chip/region as their parent. This identifies which wiring crosses between chips and hence has different dimensions and technology. It can also be used to exclude logic from the current chip's dimensions, as is useful for example, when a DRAM bank model is instantiated inside the DRAM controller rather than exporting all of the connections (TLM or otherwise) up through the module hierarchy. The same partitioning approach defines dynamic supply voltage islands where voltage changes are applied to all members of a chip/region at once.

As well as supporting an external table of modes and phases for each instance/kind of component we enable the C model to contain explicit statements of power and energy. For instance, the constructor (or PVT callback, mentioned later) for an SRAM of  $m\_bits$  might contain the following, where the first line creates a constant power value and the second logs this power in the static power account of the current component.

```

pw_power leakage = pw_power(82.0 * m_bits, PW_nW);

set_static_power(leakage);

```

Rather than just supporting a fixed pair of power accounts, as in TLM POWER2, our library supports any number of accounts per group of components with the first three being nominally used for component static power, component dynamic power/energy and wiring dynamic energy. For full flexibility, each account can model both energy and power. Each account has energy as its primary accumulating representation and the power being a standing value that, form time to time, is converted to energy debits. Standing power is converted to energy when the standing power level is changed or at the end

<sup>&</sup>lt;sup>1</sup>We use the word *component* to denote an sc\_module that is so associated.) SystemC augments every sc\_module (or other entity that inherits sc\_object) with a key/value space where the values are void \* pointers.

of simulation, the energy being the previous standing power level multiplied by the time since the last standing power change. An error is raised if the simulation exits at infinite time with a non-zero standing power level in any account. Energy figures are converted back to average power in some forms of report.

Our library also supports utilisation and transaction logging for visualisation purposes. Although this might seem orthogonal, there are some overlaps. One feature of the PKtool TLM modelling style is that idle power in a component is not accumulated while a transaction is active, and hence details of component utilisation are needed for this style of modelling. By recording utilisation we can apply this correction if desired: it might be very useful to model dynamic power and clock gating. In addition, when our library generates a VCD (Verilog change dump) report, it is convenient to have a graphical illustration of the transactions alongside the energy use bumps.

## A. Extended Generic Payload: Distance+Hamming

Although our library can be used with the standard generic payload, more detail is captured using our extended version called PW\_TLM\_PAYTYPE. In TLM 2.0, sockets are templated types which default to use the standard generic payload, but we can instead use PW\_TLM\_PAYTYPE. Rather than explicitly extending the generic payload, we could have used the generic payload's own extensions (and these still work, as used for instance for extended commands such as load-linked/store conditional), but we chose not to for efficiency reasons. Socket definitions and calls now look like this (although CPP macros can tidy this up):

| <pre>//Providing the third template argument to a socket:<br/>tlm_utils::simple_initiator_socket<br/><mytype, 64,="" pw_tlm_types=""> ifetch_socket, data_socket;</mytype,></pre> |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| //Using the extended payload in the callbacks:<br>void b_access(PW_TLM_PAYTYPE &trans, sc_time &delay)                                                                            |

The extensions in PW\_TLM\_PAYTYPE assist with the following details:

- deciding which fields are active so that only the correct fields have their hamming distance processed for wiring power,

- 2) establishing the trajectory of the transaction through the system so that traversed wire length is estimated,

- keeping note of the components encountered so that the correct power and utilisation accounts can be incremented under DMI,

- 4) measuring the variance of metrics so that automated transition to DMI is enabled.

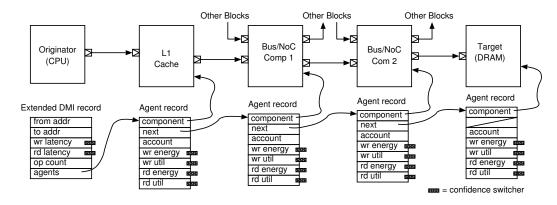

In a generic example, Fig. 2, the originator (CPU) will complete the address field of the payload and, for writes, also the data and byte-enabled fields. Generally, multi\_passthrough TLM sockets are used in complex system models: these support forwarding the transaction on-wards through bus, cache and NoC (network-on-chip) subsystems. The return path is always the reverse of the forward path owing to simple stack unwinding associated with method invocation. So intermediate components forward the payload,

perhaps with minor changes (e.g. address space manipulations at bus bridges or VM units) to the target destination. This target will reply with a low-cost acknowledgement for a write and with the data for a read.

Our TLM payload offers an API with three library calls for bus energy modelling. These are  $pw\_set\_origin$ ,  $pw\_log\_hop$  and  $pw\_terminus$ . Currently models invoke these on a payload at the beginning, intermediate steps and end of a its payload trajectory. Rather than manual application, building these invocations into the TLM convenience sockets would be more convenient (sic).

```

void pw_set_origin(sc_module *where,

uint flags=0,

bit_transition_tracker *transition_reference=0);

pw_agent pw_log_hop(sc_module *where,

uint flags=0,

bit_transition_tracker *transition_reference=0);

void pw_terminus(sc_module *where);

```

The first argument where is the this pointer for the current component. This is used to track the path through the system.

The second argument is the flags that denote which fields in the payload are active. They can also encode bidirectional data busses and multiplexed address-data busses. When the physical nets of busses are re-used the transition count increases but there are fewer busses (eg. the high order address bits might be mostly static on a dedicated address bus but are not if the same wires carry multiplexed address and data). Most flags are sticky and apply to subsequent hops that do not change that flag. In particular, if the flags argument is zero for the next hop then nothing has changed and the next hop has the same properties as the previous hop.

The third argument is a bus reference. Every transaction is considered to take place over a bus and a bus is a generic set of wires modelled with a bit\_transition\_tracker. Wires present (ie. payload fields) that are not used consume no energy, so it is not important to customise the instance of a bus to its use (e.g. the bus from CPU to memory has address and write data whereas the return bus has just read data). The bus reference is needed so as to check which physical nets are transitioning with respect to their previous value.

We could integrate a layout package to estimate wiring lengths in detail. Currently we use the Rentian approach of [4] that provides a simple estimate of average connection length in a well-placed implementation according to  $\alpha A^{\frac{1}{2}}$  where A is the area of the lowest common parent component to the source and destination of the signal and  $\alpha$  is typically 0.3. The capacitance per unit length of nets for on-chip and off-chip wiring is read from a configuration file (we use 0.3 pF/mm).

TLM 2.0 defined a DMI record called tlm::tlm\_dmi which stores the start and end addresses and access times for a region of memory that can be accessed via a fast backdoor mechanism: the client simply reads from the raw host memory that contains the memory contents. In addition, the target has a callback called invalidate\_direct\_mem\_ptr whereby this record can be retracted. However, using this DMI mechanism bypasses the target model and also all intermediate bus

Fig. 2. An example extended DMI record and agent list. An initiator may typically have several of these active at once for different targets or addressable regions in a target. The TLM return path is always the same as the forward path and the agent records are incremented for utilisation and energy in (the active phase of) both directions.

components, including caches, so their utilisation and energy accounts cannot be updated directly during DMI accesses. In TLM POWER3, we make the forward trajectory of a TLM DMI-allowed call instantiate a chain of account records that contain the energy and utilisation and account number for each intermediate agent and the target. The energy and utilisation are also updated on the return transit of the thread. (For nonblocking calls, the updates are just made on the significant protocol phases.) At the initiator we augment the DMI record with a count of the number of DMI calls made (scaled by the relative size of the transaction if the payload burst size is varying). Aperiodically (eg. at end of LT quantum), and on DMI invalidate, the count field is reset with the appropriate credits being made to the utilisation and energy accounts of each referenced component. The invalidate DMI callback also performs such a flush and frees the agent list. Operations such as store conditionals must not use DMI, so can be used as flush points.

An alternative to building the agent records is to write DMI energy to a 'slush fund' account where it will appear (correctly) in the total for the system/subsystem but (incorrectly) in the slush fund of the originator of such transactions instead of the consuming component (which is ensured by our agent records). We would perhaps use account number 4 in each component for this purpose.

The energy and power figures in a call to the library can either be pre or post supply voltage scaling, where the former are multiplied by the supply voltage squared at the point of logging and the former are not scaled. Given that a component (sc\_module) inherits our pw\_module\_base, transaction energy logging in a component can be as simple as:

```

m_read_energy_op = pw_energy(5.0 +

1.5e-5 * m_bits, pw_energy_unit::PW_pJ);

m_read_energy_op *= get_current_vcc_squared();

this->record_energy_use(m_read_energy_op /*, 1*/);

this->record_utilisation(sc_time(1, sc_us), delay);

```

where the first line would typically be in the component's constructor, the second would be in the constructor or in the PVT (process/voltage/temperature) recalculate callback. The third line actually logs the energy and can specify an

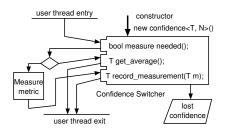

Fig. 3. General use pattern for the 'confidence switcher' component that first accumulates and then provides a mean value for a metric based on aperiodic measurements while raising an exception if accuracy is lost.

alternative account to the default of '1'. Multiplying by the supply voltage squared on every logging event is slow, and hence pre-computing this in the PVT method is preferred. Account one is the default intra-component dynamic energy account. The log of the utilisation itself takes the busy duration and an extra, optional second argument which is the advance over kernel simulation time needed for accurate rendering when loosely-timed. The 'this->' prefix would either be missed out, but preferable is is to replace it with the agent handle returned from log\_hop call. This applies the energy and utilisation debits to the current component but also inserts their values in the agent list (if one is being constructed) so that they are accounted when subsequent calls are replaced with DMI.

Using standard TLM 2.0, an initiator will start using DMI when calling get\_direct\_mem\_ptr on the initiating socket after a transaction instantiates a valid, local DMI record. Typically the initiator has no knowledge of the accuracy of the latency figures in its DMI record: naively, these will just be the result of the first call (which could be much slower owing to cache misses etc.). We provide and use a '*confidence switcher*' to ensure DMI is employed with fairly accurate values for latency as well as energy and utilisation in an extended DMI record.

The confidence switcher (Fig. 3) is a simple library component designed to capture the value of a presumed-stationary

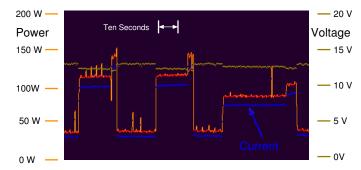

Fig. 4. Splash RADIX benchmark: probed processor power consumption. Two runs using two cores followed by one run on a single core. The end region of each run is the checking phase. Spikes are other unix processes on the dual-core workstation (Intel Pentium D 3GHz).

Fig. 5. Splash RADIX benchmark: TLM POWER3 total power consumption: we see one run using two cores followed by one run using a single core. No unix operating system was present.

statistic using a relatively small number of costly trials. It has internal state and three user methods and is parametrised by an integer N (default is 1000) that averages a generic statistic over the second N measurements and then reports that average from then onwards while making pseudo-random occasional further measurements (with mean spacing every 1/N) to check that the mean value has not significantly changed. The first Nmeasurements are not included in the average to avoid start-up transients. This gives a performance boost of approximately Ntimes in the overhead of this measurement. A change by more than one percent and more than 2/N is considered significant and this raises an SC\_ERROR or SC\_WARNING according to another construction parameter. Confidence switchers are used as much as possible, both in the POWER3 library and by the user models. They can record bit transition density counts, latency times and and power and energy units.

## B. Output Reports

Several kinds of report can be generated with the TLM\_POWER3 library. These cover power consumption, utilisation and physical layout.

The library will automatically add up the power and energy used globally, but further detail on individual sub-systems can also be reported by selecting other points in the hierarchy to trace and passing the associated component as an argument to a power trace function. Each item traced generates either a fresh set of accounts that include that item and all of its children, or that item alone, or a fresh set of totals for each component (i.e. for that item alone and recursively for all its children separately).

Energy consumption and average power are primarily reported in a plain text file emitted at the end of simulation (or at other user request dump points). This file can also

| Property      | Model Equation                       | Unit       |

|---------------|--------------------------------------|------------|

| Area          | 13359+40*bits                        | squm       |

| Read energy   | 5 + 1.5E-5                           | pJ per bit |

| Write energy  | 10 + 3.0E-5                          | pJ per bit |

| Access time   | $0.21 + 3.E - 4 \times (bits)^{0.5}$ | ns         |

| Leakage power | 82                                   | nW per bit |

TABLE I

INTERPOLATED CACTI 45NM RAM EQUATIONS

be written in spreadsheet-friendly SYLK (SYmbolic Link) form. As mentioned, utilisation, energy and transaction activity reports are available in VCD form. The VCD generator can also output in a gnuplot-friendly multi-column file format. The LT (loosely-timed) approach can upset the normal SystemC VCD report format owing to temporal decoupling (events are logged in their actual simulation order rather than their nominal correct order) but our VCD writer corrects this by writing the events to a circular RAM buffer whose temporal extent is greater than the LT quantum. This also enables sensible energy plots to be made: energy events would be like Dirac pulses if rendered directly and cumulative energy plots are not especially informative, but our VCD writer implements a single-pole low-pass filter for the energy events so that they appear like exponentially-decaying pulses. Alternatively it reports the flat average power given by the last energy quantum divided by the time to the next-logged quantum on that account.

Physical layout is currently printed as a text file which just reports which components are inside which others and the resulting area for each component. A graphical plot in .svg form is being implemented.

### II. PERFORMANCE

We examined the performance of the first two testbench programs in the Splash-2 suite [14]. These are a radix sort and a L/U matrix decomposition that can run on 1 to 16 cores. We compiled the Splash-2 programs to run bare metal supported by the standard linux libc and our own implementation of pthreads and a Simics/ANL (parmacs) shim layer [5]. Our testbench uses four OpenRISC processor cores [11] in verilated or fast ISS forms wrapped to use TLM 2.0 blocking calls served by an un-cached instance of DRAMSIM2 [9]. The cores log 250 pJ per instruction and run at 200 MHz unless paused waiting for other cores (50mW core power). Each core has separate I and D L1 caches that included 17 RAMs each (tag and data for 8-way set associative and a write buffer). Each Core, Cache and each of the other components shown in Fig 1 is a seprately annotated SystemC module that also inherits a TLM\_POWER3 base and communication between them is completely with blocking TLM 2.0 calls. There are sixteen SystemC modules in three levels of hierarchy. The individual RAMs had dimensions and power consumption computed according to the equations in Tab I which were formed from our own regression of 45nm CACTI runs [12].

Table II shows that simply taking the four-core ISS and putting it inside SystemC TLM degrades the performance by

| Configuration                | Instructions/sec    | Ratio |

|------------------------------|---------------------|-------|

| Fast ISS - No SystemC        | $11 \times 10^{6}$  | 1.0   |

| SystemC - LT=off, POWER3=off | $1 \times 10^{6}$   | 0.1   |

| SystemC - LT=max, POWER3=off | $4 \times 10^{6}$   | 0.4   |

| SystemC - LT=off, POWER3=on  | $0.5 \times 10^{6}$ | 0.05  |

TABLE II SIMULATION PERFORMANCE: GCC 4.43 INTEL x86\_64 3GHz/6000 BOGOMIPS, 8GBYTE RAM(NO PAGING) SYSTEMC-2.2.0.

about ten-to-one owing to SystemC kernel overhead (gprof reveals major costs (more than 20 percent of execution time) are in sc core::sc simcontext::crunch(bool) and b\_transport. This degradation occurs with and without the inclusion of caches but the performance of the modelled system does change as expected (ie. program completes much faster with caches). Using a maximal LT quantum so that the SystemC kernel is only entered during bus and mutex contention restores some of the performance. Turning on our power library with its hamming distance computations, when N = 1000 for the confidence switcher causes a further 50 percent degradation in throughput. This can perhaps be improved upon, but it is not overly bad. Interestingly, the degradation was much worse in an early version where the island voltage was squared at every use rather than recomputing the transaction energies just on each PVT change.

Fig. 4 shows the measured power consumption of the processor (excluding DRAM) on a real Linux workstation as three idential runs of the RADIX benchmark were executed, the third one using only one CPU core. A 0.05 ohm resistor was put in series with the 12 volt supply to the processor and its voltage drop and output voltage were logged at 60 Hz to record the energy consumption. Fig. 5 shows the total power plot when the same C program was run on the SystemC model. Some differences in general shape are obvious and need investigation.

#### **III.** CONCLUSION

Our framework provides an easy-to-use power estimation add on to SystemC TLM modelling. The use of the confidence switcher to dynamically disable detailed modelling is novel. The user may easily alter the system structure in radical ways, changing cache size, bus layout and so on. Standard ELF binaries can be easily generated with GCC/binutils tool chain. We also have a MIPS64 SMP system based around the same components. Because wiring power is becoming a dominant aspect it is important to include it in rapid exploration tools.

The benefit of rapidly exploring design options using SystemC was advocated in [1], but having performance predictions without power predictions is no longer acceptable. A fairly-detailed TLM model with power annotation was constructed by [2] for a PowerPC-based SoC. The activity for individual test transactions was extracted from VCD files and entered into a database. This approach can be applied in our framework to generate the individual transaction energies. Power estimation is also being performed for AMS (analog and mixed signal) subsystems within the SystemC framework [7].

We plan to further refine our API and library and release it for download. Including the log\_hop operations inside the convenience sockets would be sensible. Also, further support for power islands might be needed, but currently we can use our chip number concept with zero volt supply setting to disable static power in regions. Further work will be to integrate back-annotation flows from real layouts and compare these with the Rentian approach. We would also like to extract net-level activity from the Verilated models to gain additional insight and confidence.

We thank Matthieu Moy for providing the TLM POWER2 base platform.

#### REFERENCES

- Luca Benini, Davide Bertozzi, Alessandro Bogliolo, Francesco Menichelli, and Mauro Olivieri. Mparm: Exploring the multi-processor soc design space with systemc. J. VLSI Signal Process. Syst., 41:169– 182, September 2005.

- [2] Nagu Dhanwada. A power estimation methodology for SystemC transaction level models. In *In Proceedings of CODES-ISSS*, pages 142– 147, 2005.

- [3] Frank Ghenassia. Transaction-Level Modeling with SystemC: TLM Concepts and Applications for Embedded Systems. Springer-Verlag New York, Inc., Secaucus, NJ, USA, 2006.

- [4] Daniel Greenfield and Simon W. Moore. Fractal communication in software data dependency graphs. In SPAA '08: Proceedings of the twentieth annual symposium on Parallelism in algorithms and architectures, pages 116–118, New York, NY, USA, 2008. ACM.

- [5] P.S. Magnusson, M. Christensson, J. Eskilson, D. Forsgren, G. Hallberg, J. Hogberg, F. Larsson, A. Moestedt, and B. Werner. Simics: A full system simulation platform. *Computer*, 35(2):50–58, feb 2002.

- [6] Matthieu Moy. Mini power-aware TLM-platform. http://wwwverimag.imag.fr/~moy/?Mini-Power-Aware-TLM-Platform, 2010.

- [7] François Pêcheux, Khouloud Zine El Abidine, and Alain Greiner. Early power estimation in heterogeneous designs using soclib and systemcams. In Proceedings of the 20th international conference on Integrated circuit and system design: power and timing modeling, optimization and simulation, PATMOS'10, pages 252–252, Berlin, Heidelberg, 2011. Springer-Verlag.

- [8] Roberta Piscitelli and Andy D. Pimentel. A signature-based power model for mpsoc on fpga. VLSI Des., 2012:6:6–6:6, January 2012.

- [9] P. Rosenfeld, E. Cooper-Balis, and B. Jacob. Dramsim2: A cycle accurate memory system simulator. *Computer Architecture Letters*, 10(1):16 –19, jan.-june 2011.

- [10] M. Streubuhr, R. Rosales, R. Hasholzner, C. Haubelt, and J. Teich. Esl power and performance estimation for heterogeneous mpsocs using systemc. In *Specification and Design Languages (FDL), 2011 Forum* on, pages 1 –8, sept. 2011.

- [11] James Tandon. The openrisc processor: open hardware and linux. *Linux* J., 2011(212), December 2011.

- [12] Shyamkumar Thoziyoor, Jung Ho Ahn, Matteo Monchiero, Jay B. Brockman, and Norman P. Jouppi. A comprehensive memory modeling tool and its application to the design and analysis of future memory hierarchies. In *Proceedings of the 35th Annual International Symposium* on Computer Architecture, ISCA '08, pages 51–62, Washington, DC, USA, 2008. IEEE Computer Society.

- [13] G.B. Vece and M. Conti. Power estimation in embedded systems within a systemc-based design context: The pktool environment. In *Intelligent* solutions in Embedded Systems, 2009 Seventh Workshop on, pages 179 –184, june 2009.

- [14] Steven Cameron Woo, Moriyoshi Ohara, Evan Torrie, Jaswinder Pal Singh, and Anoop Gupta. The splash-2 programs: characterization and methodological considerations. SIGARCH Comput. Archit. News, 23:24– 36, May 1995.