Technical Report

Number 705

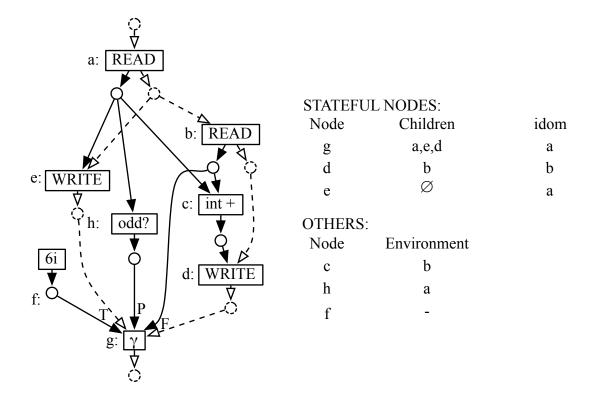

**Computer Laboratory**

# Optimizing compilation with the Value State Dependence Graph

Alan C. Lawrence

December 2007

15 JJ Thomson Avenue Cambridge CB3 0FD United Kingdom phone +44 1223 763500

http://www.cl.cam.ac.uk/

© 2007 Alan C. Lawrence

This technical report is based on a dissertation submitted May 2007 by the author for the degree of Doctor of Philosophy to the University of Cambridge, Churchill College.

Some figures in this document are best viewed in colour. If you received a black-and-white copy, please consult the online version if necessary.

Technical reports published by the University of Cambridge Computer Laboratory are freely available via the Internet:

http://www.cl.cam.ac.uk/techreports/

ISSN 1476-2986

# Abstract

Most modern compilers are based on variants of the Control Flow Graph. Developments on this representation—specifically, SSA form and the Program Dependence Graph (PDG)—have focused on adding and refining data dependence information, and these suggest the next step is to use a purely data-dependence-based representation such as the VDG (Ernst et al.) or VSDG (Johnson et al.).

This thesis studies such representations, identifying key differences in the information carried by the VSDG and several restricted forms of PDG, which relate to functional programming and continuations. We unify these representations in a new framework for specifying the *sharing* of resources across a computation.

We study the problems posed by using the VSDG, and argue that existing techniques have not solved the *sequentialization* problem of mapping VSDGs back to CFGs. We propose a new compiler architecture breaking sequentialization into several stages which focus on different characteristics of the input VSDG, and tend to be concerned with different properties of the output and target machine. The stages integrate a wide variety of important optimizations, exploit opportunities offered by the VSDG to address many common phase-order problems, and unify many operations previously considered distinct.

Focusing on branch-intensive code, we demonstrate how effective control flow—sometimes superior to that of the original source code, and comparable to the best CFG optimization techniques—can be reconstructed from just the dataflow information comprising the VSDG. Further, a wide variety of more invasive optimizations involving the duplication and specialization of program elements are eased because the VSDG relaxes the CFG's overspecification of instruction and branch ordering. Specifically we identify the optimization of nested branches as generalizing the problem of minimizing boolean expressions.

We conclude that it is now practical to discard the control flow information rather than maintain it in parallel as is done in many previous approaches (e.g. the PDG).

# Acknowledgements

Firstly, I would like to thank my supervisor, Professor Alan Mycroft, for his unending enthusiasm, sense of direction, encouragement, and occasional cracking-of-the-whip; and my parents, for their support and understanding throughout. Without these people this thesis would never have been possible. Thanks must also go to my grandmother for her help with accomodation, which has been invaluable.

I would also like to thank my fellow members of the Cambridge Programming Research Group, for the many discussions both on and off the subject of this thesis; and to many friends and officemates for their help throughout in preserving my sanity, or at least the will to go on...

# Contents

| 1 | Introduction 11            |                                                           |    |  |  |  |  |  |

|---|----------------------------|-----------------------------------------------------------|----|--|--|--|--|--|

|   | 1.1                        | Computers and Complexity                                  |    |  |  |  |  |  |

|   | 1.2                        | Compilers and Abstraction                                 |    |  |  |  |  |  |

|   | 1.3                        | Normalization: Many Source Programs to One Target Program | 12 |  |  |  |  |  |

|   | 1.4                        | Abstraction Inside the Compiler                           |    |  |  |  |  |  |

|   | 1.5                        |                                                           | 14 |  |  |  |  |  |

|   |                            | 1.5.1 Static Single Assignment                            | 15 |  |  |  |  |  |

|   |                            |                                                           | 15 |  |  |  |  |  |

|   |                            | 1.5.3 The Value (State) Dependence Graph                  | 17 |  |  |  |  |  |

|   | 1.6                        | Optimizations on the VSDG                                 | 17 |  |  |  |  |  |

|   | 1.7                        |                                                           | 18 |  |  |  |  |  |

|   |                            | 1.7.1 Sequentialization and Late Decisions                | 18 |  |  |  |  |  |

|   | 1.8                        | Chapter Summary                                           | 19 |  |  |  |  |  |

| 2 | The Nature of the Beast 21 |                                                           |    |  |  |  |  |  |

|   | 2.1                        | The VSDG by Example                                       | 21 |  |  |  |  |  |

|   |                            |                                                           | 27 |  |  |  |  |  |

|   |                            |                                                           | 27 |  |  |  |  |  |

|   | 2.2                        |                                                           | 27 |  |  |  |  |  |

|   |                            |                                                           | 27 |  |  |  |  |  |

|   |                            | 2.2.2 Encoding the VSDG as a Functional Program           | 28 |  |  |  |  |  |

|   |                            |                                                           | 29 |  |  |  |  |  |

|   |                            |                                                           | 31 |  |  |  |  |  |

|   | 2.3                        |                                                           | 32 |  |  |  |  |  |

|   | 2.4                        |                                                           | 32 |  |  |  |  |  |

|   |                            |                                                           | 34 |  |  |  |  |  |

|   |                            | 2.4.2 Three Phases or Two?                                | 35 |  |  |  |  |  |

|   |                            |                                                           | 36 |  |  |  |  |  |

|   | 2.5                        | Definition of the PDG                                     | 37 |  |  |  |  |  |

|   | 2.6                        |                                                           | 39 |  |  |  |  |  |

|   |                            | •                                                         | 39 |  |  |  |  |  |

|   |      | 2.6.2   | Transitions                                         | 40 |

|---|------|---------|-----------------------------------------------------|----|

|   |      | 2.6.3   | 8                                                   | 41 |

|   |      | 2.6.4   | Labels, Sets and Tuples                             | 41 |

|   |      | 2.6.5   | Hierarchical Petri-Nets                             | 42 |

|   |      | 2.6.6   | Loops                                               | 43 |

|   |      | 2.6.7   | Well-Formedness Requirements                        | 43 |

|   | 2.7  | Seman   | tics                                                | 44 |

|   |      | 2.7.1   | Sequentialization by Semantic Refinement            | 44 |

|   |      | 2.7.2   | The VSDG as a Reduction System                      | 45 |

|   |      | 2.7.3   | A Trace Semantics of the VSDG                       | 46 |

|   | 2.8  | Chapte  | r Summary                                           | 48 |

|   |      | 1       |                                                     |    |

| 3 | Proc | edurali | zation                                              | 51 |

|   | 3.1  | Choosi  | ng an Evaluation Strategy                           | 53 |

|   | 3.2  | Founda  | tions of Translation                                | 54 |

|   |      | 3.2.1   | Naïve Algorithm                                     | 54 |

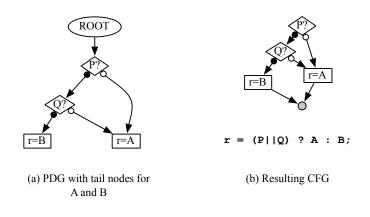

|   |      | 3.2.2   | Tail Nodes—an Intuition                             | 55 |

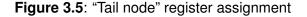

|   |      | 3.2.3   | Normalization of Conditional Predicates             | 57 |

|   | 3.3  | An Alg  | orithmic Framework                                  | 57 |

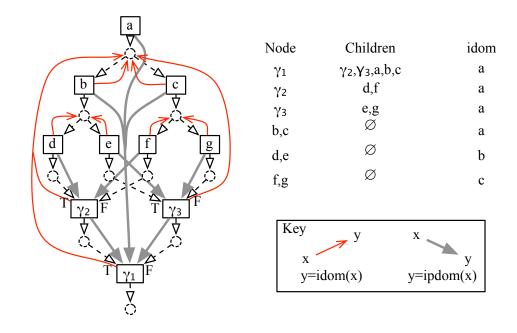

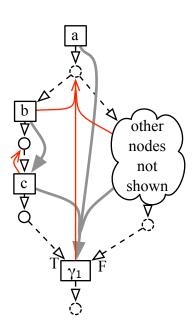

|   |      | 3.3.1   | Dominance and Dominator Trees                       | 58 |

|   |      | 3.3.2   | Gating Conditions                                   | 59 |

|   |      | 3.3.3   | The Traversal Algorithm                             | 60 |

|   | 3.4  | Additio | onal Operations                                     | 62 |

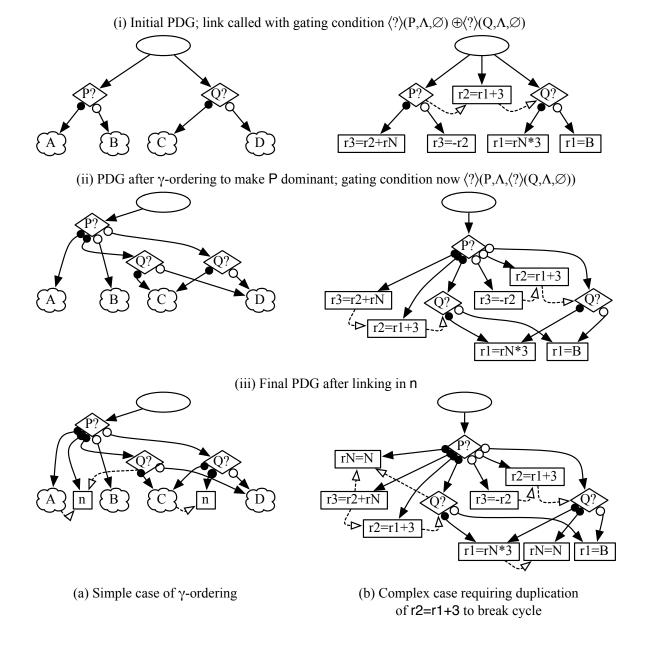

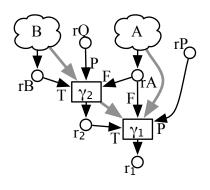

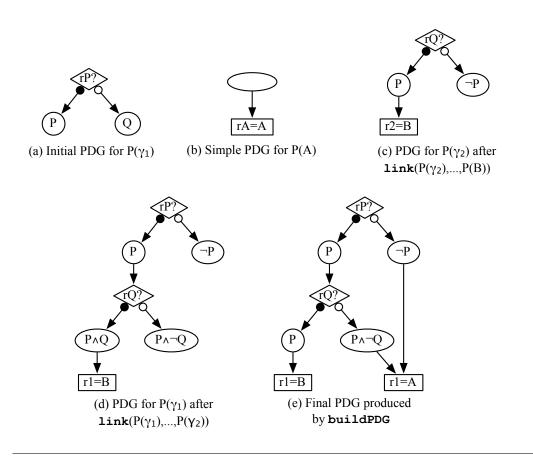

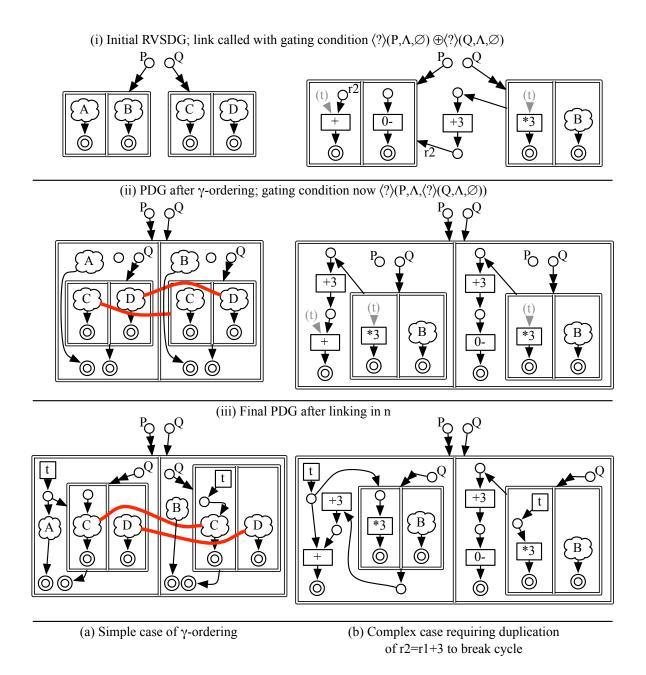

|   |      | 3.4.1   | The $\gamma$ -Ordering Transformation               | 62 |

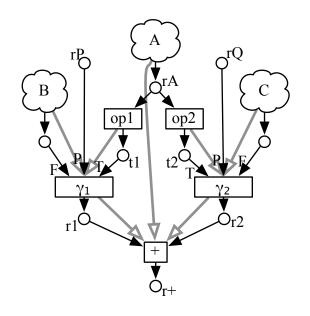

|   |      | 3.4.2   | Coalescing of $\gamma$ -Trees                       | 65 |

|   | 3.5  | Worked  | 1 Examples                                          | 67 |

|   | 3.6  | Chapte  | r Summary                                           | 71 |

|   |      |         |                                                     |    |

| 4 |      | -       | ntialization                                        | 73 |

|   | 4.1  | -       |                                                     | 73 |

|   |      |         |                                                     | 74 |

|   | 4.2  | A Spec  | ial Case of PDG Sequentialization                   | 75 |

|   |      | 4.2.1   | Bipartite Graphs and Vertex Coverings               | 77 |

|   |      | 4.2.2   | Unweighted Solution                                 | 78 |

|   |      | 4.2.3   | Weights and Measures                                | 80 |

|   | 4.3  | Compa   | rison with VSDG Sequentialization Techniques        | 82 |

|   |      | 4.3.1   | Johnson's Algorithm                                 | 82 |

|   |      | 4.3.2   | Upton's Algorithm                                   | 84 |

|   | 4.4  | Compa   | rison with Classical CFG Code Motion                | 85 |

|   |      | 4.4.1   | Suitable Program Points                             | 87 |

|   |      | 4.4.2   | Extra Tests and Branches                            | 87 |

|   |      | 4.4.3   | Program Points and Sequentialization Phases         | 87 |

|   |      | 4.4.4   | Lifetime Minimization                               | 88 |

|   |      | 4.4.5   | Variable Naming and Textually Identical Expressions | 89 |

|   |      | 4.4.6   | Optimal Code Motion on Running Examples             | 90 |

|   |      | 4.4.7   | Other Algorithms                                    | 90 |

|   |      |         | -                                                   |    |

| 5 | Inte              | rmediate Representations and Sharing 93                                               |  |  |  |  |

|---|-------------------|---------------------------------------------------------------------------------------|--|--|--|--|

|   | 5.1               | Shared Operators: the PDG & VSDG, Part 2                                              |  |  |  |  |

|   |                   | 5.1.1 Production of Shared Operators                                                  |  |  |  |  |

|   | 5.2               | An Explicit Specification of Sharing                                                  |  |  |  |  |

|   | 5.3               | A Semantics of Sharing Edges                                                          |  |  |  |  |

|   |                   | 5.3.1 An Alternative View of Proceduralization                                        |  |  |  |  |

|   | 5.4               | Loops                                                                                 |  |  |  |  |

|   |                   | 5.4.1 Proceduralization and Loops                                                     |  |  |  |  |

|   | 5.5               | The RVSDG: a Workable PDG Alternative                                                 |  |  |  |  |

|   |                   | 5.5.1 Strict Nets and $\gamma$ -Nets                                                  |  |  |  |  |

|   |                   | 5.5.2 Loops                                                                           |  |  |  |  |

|   |                   | 5.5.3 Sharing                                                                         |  |  |  |  |

|   |                   | 5.5.4 Explicit Representation of Register Moves                                       |  |  |  |  |

|   |                   | 5.5.5 Well-Formedness Conditions                                                      |  |  |  |  |

|   |                   | 5.5.6 Semantics                                                                       |  |  |  |  |

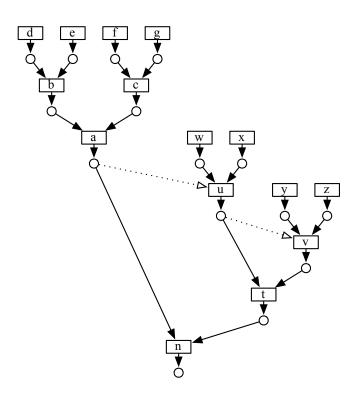

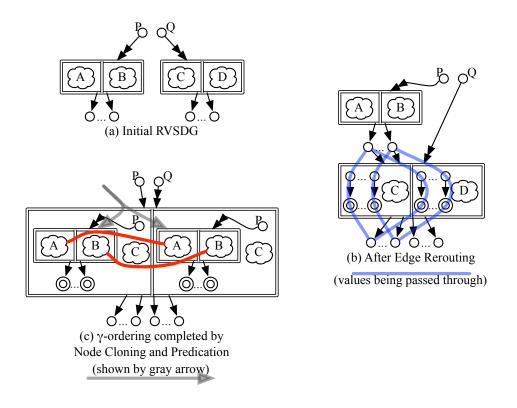

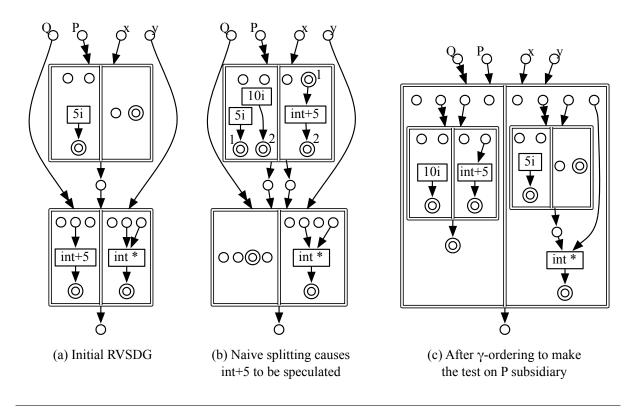

|   |                   | 5.5.7 Performing $\gamma$ -Ordering on the RVSDG                                      |  |  |  |  |

|   |                   | 5.5.8 Chapter Summary                                                                 |  |  |  |  |

|   |                   |                                                                                       |  |  |  |  |

| 6 |                   | e Scheduling 121                                                                      |  |  |  |  |

|   | 6.1               | Johnson's Algorithm                                                                   |  |  |  |  |

|   |                   | 6.1.1 Atomicity of $\gamma$ -Regions                                                  |  |  |  |  |

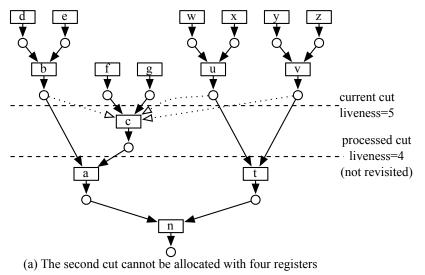

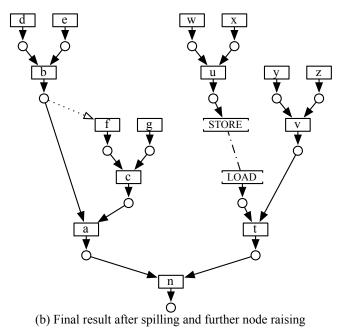

|   |                   | 6.1.2 Node Raising and Speculation                                                    |  |  |  |  |

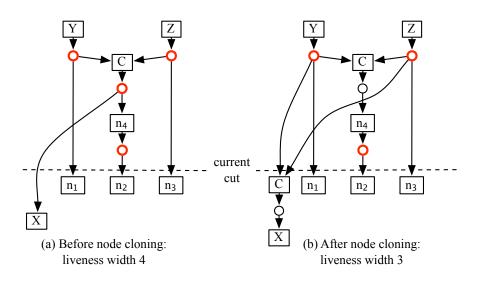

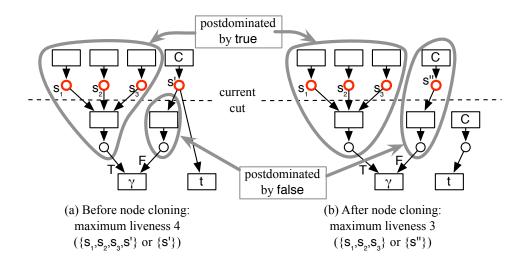

|   |                   | 6.1.3 Node Cloning and Dominance                                                      |  |  |  |  |

|   | 6.2               | Reformulating Johnson's Algorithm on the RVSDG                                        |  |  |  |  |

|   |                   | 6.2.1 Hierarchy                                                                       |  |  |  |  |

|   |                   | 6.2.2 Tail-Sharing Regions                                                            |  |  |  |  |

|   |                   | 6.2.3 Register Allocation                                                             |  |  |  |  |

|   | 6.3               | Simple Extensions                                                                     |  |  |  |  |

|   |                   | 6.3.1 Heuristics for Speed over Space                                                 |  |  |  |  |

|   |                   | 6.3.2 Instruction Latencies                                                           |  |  |  |  |

|   |                   | 6.3.3 Movement Between Regions                                                        |  |  |  |  |

|   | <i>.</i> .        | 6.3.4 Predicated Execution                                                            |  |  |  |  |

|   | 6.4               | Alternative Approaches                                                                |  |  |  |  |

|   | 6.5               | The Phase-Order Problem Revisited                                                     |  |  |  |  |

|   |                   | 6.5.1 Combining Proceduralization and Node Scheduling                                 |  |  |  |  |

|   | 6.6               | Chapter Summary                                                                       |  |  |  |  |

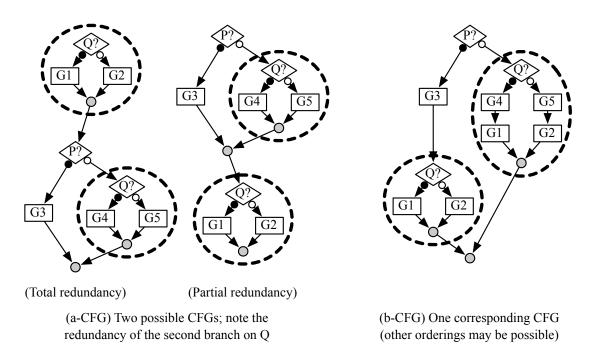

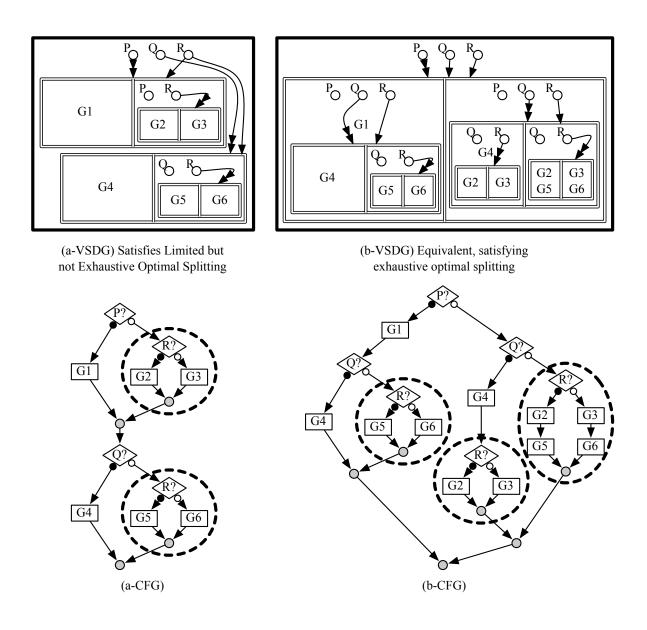

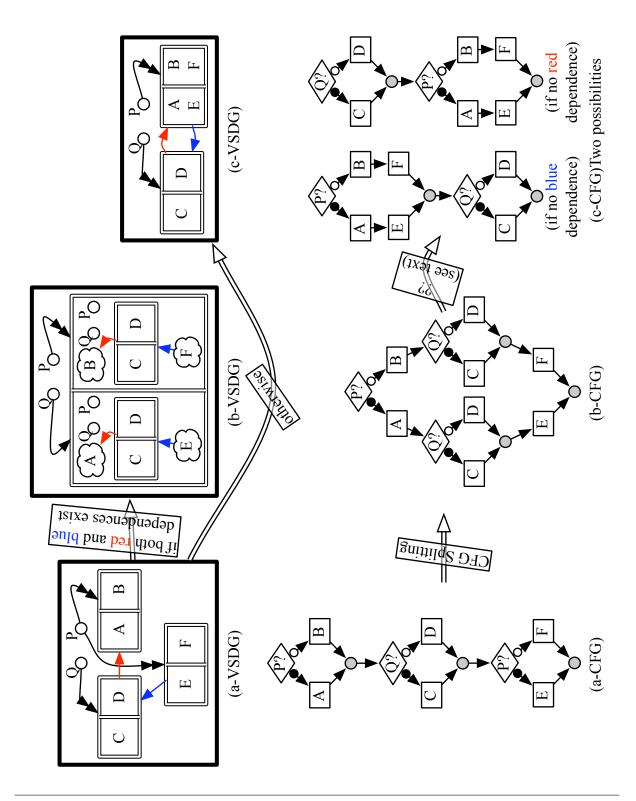

| 7 | Spli              | ting 139                                                                              |  |  |  |  |

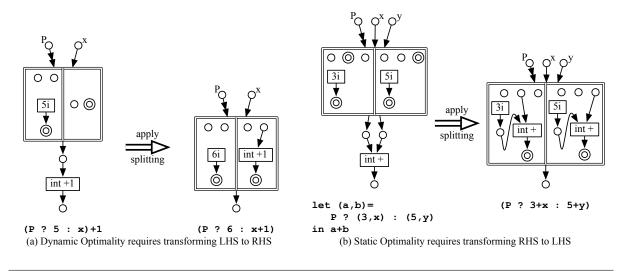

| / | <b>5pn</b><br>7.1 | Splitting, $\dot{a} \ la \ VSDG$                                                      |  |  |  |  |

|   | /.1               | 7.1.1       Enabling Optimizations       140                                          |  |  |  |  |

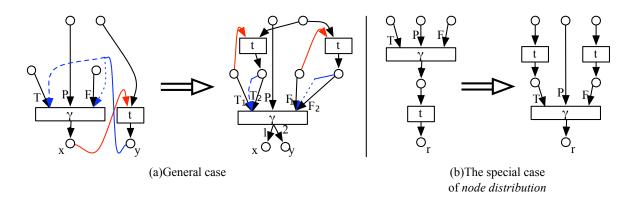

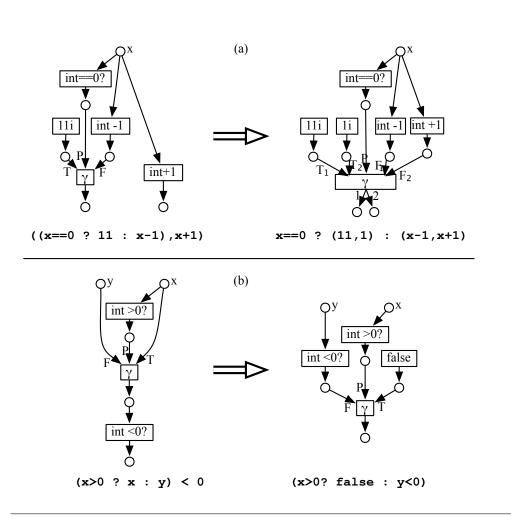

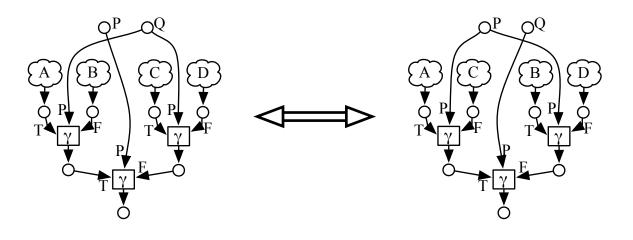

|   |                   | 7.1.2 Transformations on $\gamma$ -Nodes                                              |  |  |  |  |

|   | 7 2               |                                                                                       |  |  |  |  |

|   | 7.2<br>7.3        |                                                                                       |  |  |  |  |

|   |                   | Splitting: a Cross-Phase Concern    144      Optimality Criteria for Splitting    147 |  |  |  |  |

|   | 7.4               |                                                                                       |  |  |  |  |

|   |                   |                                                                                       |  |  |  |  |

|   |                   |                                                                                       |  |  |  |  |

|   |                   | 7.4.3 Limited Optimal Splitting                                                       |  |  |  |  |

|     | 7.5          | 7.4.4<br>Relatio | Exhaustive Optimal Splitting     |     |  |  |  |  |  |  |  |  |

|-----|--------------|------------------|----------------------------------|-----|--|--|--|--|--|--|--|--|

|     |              | 7.5.1            | Message Splitting                |     |  |  |  |  |  |  |  |  |

|     |              | 7.5.2            | Cost-Optimal Code Motion         |     |  |  |  |  |  |  |  |  |

|     |              | 7.5.3            | Speculative Code Motion          |     |  |  |  |  |  |  |  |  |

|     |              | 7.5.4            | Use of the PDG                   |     |  |  |  |  |  |  |  |  |

|     |              | 7.5.5            | Restructuring the CFG            |     |  |  |  |  |  |  |  |  |

| 8   | Conc         | lusion           |                                  | 161 |  |  |  |  |  |  |  |  |

|     | 8.1          | Open Q           | Questions                        | 162 |  |  |  |  |  |  |  |  |

| A   | Glos         | sary of '        | Terms                            | 165 |  |  |  |  |  |  |  |  |

| B   | State        | Edges            | and Haskell                      | 167 |  |  |  |  |  |  |  |  |

|     | <b>B</b> .1  | The Sta          | ate Monad                        | 167 |  |  |  |  |  |  |  |  |

|     | B.2          | Encodi           | ng Just the State Edges          | 168 |  |  |  |  |  |  |  |  |

|     | B.3          | Adding           | g Values                         | 170 |  |  |  |  |  |  |  |  |

|     | B.4          | Even th          | ne State Monad is Too Expressive | 172 |  |  |  |  |  |  |  |  |

|     | B.5          | Well-Fo          | ormedness Conditions             | 173 |  |  |  |  |  |  |  |  |

|     | B.6          | Derestr          | ricting State Edges              | 174 |  |  |  |  |  |  |  |  |

|     | B.7          | A Note           | on Exceptions                    | 174 |  |  |  |  |  |  |  |  |

| Bil | Bibliography |                  |                                  |     |  |  |  |  |  |  |  |  |

# CHAPTER 1

# Introduction

A modern digital computer is perhaps the most complex toy ever created by man. *The Computer Revolution in Philosophy*, Aaron Sloman, 1978

# 1.1 Computers and Complexity

Clearly, the complexity of computer systems has only increased in the years since the quote above. This complexity drives much of computer science, and can be seen as the composition of two forms:

- 1. The *inherent complexity* in working out and specifying what the system must do precisely and unambiguously. Work with formal specification languages shows that this is still difficult, even with no allowance made for hardware or implementation concerns.

- 2. The *incidental complexity* of expressing this specification in a form which can be executed by a computer—for example, in a particular programming language. This brings in additional concerns of the *efficiency* of execution.

# 1.2 Compilers and Abstraction

Abstraction is a powerful tool for managing complexity, so it is no surprise that the use of abstractions in the construction of computer systems, specifically software, has been increasing steadily. One vital source of abstraction for overcoming incidental complexity is the *compiler*, defined by Aho et al. [AU77] as:

A program that reads a program written in one language—the source language and translates it into an equivalent program in another language—the target language.

We see this as providing abstraction in two distinct ways.

Firstly, the conversion between programming languages provides the abstraction(s) of the source language: for example, features such as mnemonic instructions instead of binary opcodes, user-declared variables in place of registers, data types over untyped memory locations, higher-order functions, objects, garbage collection, etc...

Secondly, the translation into an *equivalent* program—meaning one which produces the same results and side effects, including termination or otherwise—allows the compiler to *op*-*timize* the result such that it is more efficient in space, time, or both. This moves concerns of efficiency—previously in the domain of the programmer—into the domain of the compiler, such that the programmer need think about less, and can concentrate more fully on the real-world task to be performed<sup>1</sup>.

# 1.3 Normalization: Many Source Programs to One Target Program

Thus, a maxim of compiler folklore is that:

"The most optimizing compiler is the most normalizing compiler."

Normalization refers to where many different source programs result in the same machine code after compilation—that is, where the same machine code is produced regardless of which form was written by the programmer. In this thesis, we refer to the input programs *being normalized* by the compiler. For the behaviour of the compiler to be considered correct, the two input code sequences must therefore do the same thing (and the output must implement this!), i.e. they have the same observable semantics, and so we can see them as different *representations* of the same underlying idea<sup>2</sup>.

This allows the programmer to select from such representations according to which is the easiest to comprehend or to fit his ideas or program into, and leave the compiler to select the output according to efficiency concerns. Thus, the level of abstraction is raised.

Of course, due to decidability issues, in general the compiler cannot select the "best" output, or even list all the possible equivalents; further, the efficiency of different possible outputs may be incomparable, depending on contextual factors such as intended library usage or likely program inputs that are not known at compile-time. Or, the programmer may have written his source code using knowledge of these factors that is merely unavailable to the compiler; in such cases, compiler attempts at "optimization" and normalization may in effect undo hours of work by programmers in hand-optimizing their code and make the code *worse*. This leads to the idea of *conservative* optimization: that which cannot make the program perform worse on *any* execution; clearly, conservatism is a major limitation. Hence, runtime profiling is a better solution: observe how the code is actually used at runtime, and use this information to optimize the code with runtime recompilation. Programmers' conceptions of how code is used are frequently ill-founded, and profiling is more accurate. Such techniques allow the compiler to select an appropriate output form; and where the same or equivalent program fragments

<sup>&</sup>lt;sup>1</sup>As William Wulf [Wul72] said: " More computing sins are committed in the name of efficiency (without necessarily achieving it) than for any other single reason—including blind stupidity."

<sup>&</sup>lt;sup>2</sup>Some programming languages emphasize orthogonality—the existence of exactly one program construct for each purpose—but even this does not rule out the possibility of combining the same structures in different ways to achieve the same end. Others even make it a feature that "There Is More Than One Way To Do It" (TIMTOWTDI or "Tim Toady") [Wal00]!

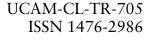

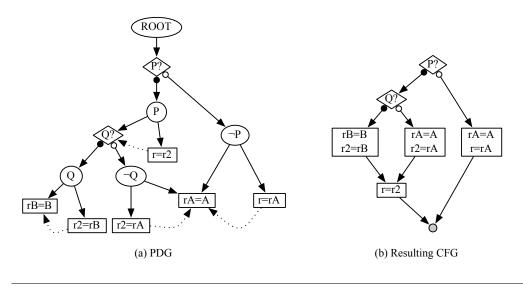

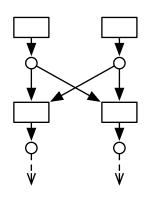

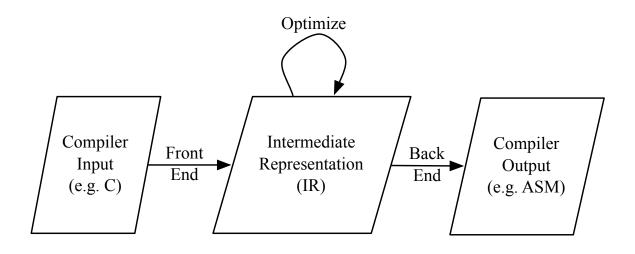

**Figure 1.1**: Structure of an optimizing compiler. In this thesis, the intermediate representation is the VSDG, and the compiler output can be considered a CFG of machine instructions with physical registers.

appear in multiple different places in the input, it may even choose a different output for each (so "normalization" may be a misleading term).

# 1.4 Abstraction Inside the Compiler

Because of this increasing demand for optimization, compilers are themselves becoming more and more complex. Correspondingly, the role of abstraction *inside* compilers is becoming more important.

Optimizing compilers are conventionally structured as shown in Figure 1.1: the *front end* of the compiler transforms the input program (e.g. source code) into an Intermediate Representation (IR); optimisation phases operate on the program in this form; and then the *rear end* transforms the program into the desired output format (e.g. a sequence of machine code instructions). *Construction* refers to the production of the IR from the input; paralleling this, we use the term *destruction* to refer to conversion of the program out of the IR to produce machine code. However, for a CFG of machine instructions with physical registers, destruction is trivial—requiring only the placement of the basic blocks into a single list—and thus we tend to see the output of the compiler as being such a CFG.

This thesis is concerned with the Intermediate Representation used, as representing the program in such an IR data structure is one of the main abstractions on which the compiler is based. In fact we can see "an Intermediate Representation" as an *abstract data type* (ADT), with operations of construction, destruction, and intervening optimization, much as "Priority Queue" is an ADT with operations of adding an element and examining and removing the smallest. Different IRs implement the ADT in different ways and are almost interchangeable, and a particular IR should be selected according to its costs for the operations that are expected—much as selecting a structure such as a Heap, Binomial Heap or Fibonacci Heap to implement a Priority Queue.

Specifically (and as a direct result of the increasing demands placed on compilers), the amount of time spent on optimization increases (in both programming and running the compiler), whereas construction and destruction continue to occur exactly once per compilation.

In most compilers, the IR used is the CFG (Control Flow Graph), whereas in this thesis,

we argue for the use of the VSDG (Value State Dependence Graph—both of these are outlined below in the next section). When we compare these two representations as to their costs, we see:

- In the **front end**, the VSDG is slightly more expensive to construct, but this is generally straightforward.

- In the **optimization** stage, although there are exceptions, generally optimizations are significantly cheaper in the VSDG, as well as being easier to write; this is discussed at more length in Section 1.6.

- In the **rear end**, the VSDG requires substantially more effort. Specifically, the VSDG must first be *sequentialized* into a CFG, and this has not previously been seen as straightforward. This is discussed in Section 1.7, and much of this thesis focuses on this problem.

As time progresses and more and more optimization is performed, an IR which facilitates optimization becomes more important, and it becomes worthwhile to spend more effort in conversion both into an IR and out of it, as this effort can be traded against increasing cost savings. Thus, we argue that switching to the VSDG as IR is a logical next step.

# 1.5 Trends in Intermediate Representations

Changes and augmentations to Intermediate Representations have followed a number of trends, but three main themes stand out:

Assignment becoming less important

Control flow becoming more implicit

Dependencies becoming more explicit

Early compilers used the CFG, as it was simple to construct and destruct. The CFG is a simple flow chart (familiar from process management and non-computer-science fields), with each node labelled with a machine instruction (or optionally series of instructions); for decision nodes (only) the final instruction is a branch instruction (hence in the CFG, such nodes are usually referred to as *branch nodes*). We can see that the CFG is quite primitive and very close to the hardware in all three themes:

- **Assignment** is the sole means by which information is carried from any (non-branch) operation to another, exactly as values are carried from one machine code instruction to another by being stored in registers.

- **Control Flow** is recorded explicitly by successor edges, thus (unnecessarily) ordering even independent statements. We can see the program counter of a traditional CPU as pointing to one node after another.

- **Dependencies** are highly implicit; to identify them, one must perform Reaching Definitions analysis to locate the other statement(s) potentially producing the value depended on. (This is similar to the work done by the reorder buffer in a superscalar processor in order to identify parallelizable statements.)

Branches control which statements are executed; we can see this as additionally encoding information (whether the branch was taken or not) into the PC. After paths merge together, information remains only in the values assigned to variables by statements which the branch caused to be executed (or not).

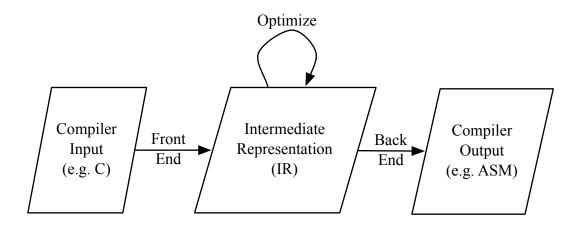

We now discuss some significant alternatives and refinements; these are shown in the diagram on page 16.

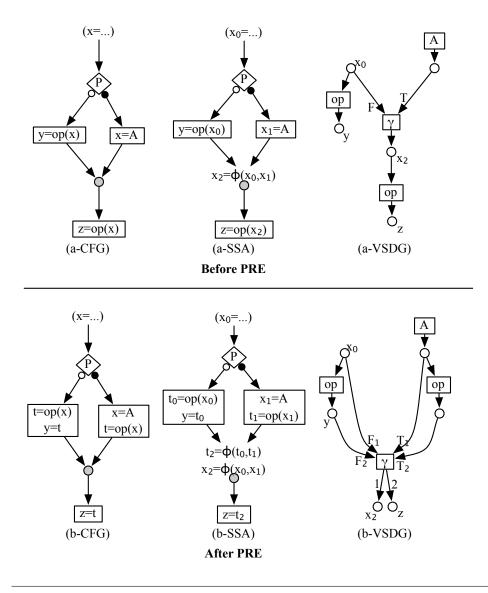

### 1.5.1 Static Single Assignment

Many "dataflow" analyses were developed to operate on the CFG: for example, live variables, available and busy expressions, reaching definitions. These eventually led to perhaps the first major increase in abstraction: Static Single Assignment, or SSA form [CFR<sup>+</sup>91]. This adds a restriction that for each variable appearing in the CFG, statically there is a single assignment to it (usually requiring the use of additional variables). At merge points,  $\phi$ -nodes allow merging the variables from different incoming edges to create new variables.

SSA form makes substantial advances in two of the three themes:

- **Assignment** Each variable has only one assignment to it, so the idea that a statement might affect the future by having a side effect onto some variable is avoided. (Information is still only carried by values assigned.)

- **Dependencies** thus become much more obvious, as for any use of a variable, the unique statement producing that value can easily be identified.

This greatly simplifies analysis and hence optimization, but some extra effort is required in production (and sequentialization, although not significantly). However, the same ordering restrictions remain.

### 1.5.2 The Program Dependence Graph

An independent development in IRs was the Program Dependence Graph (PDG), introduced in 1987 as a combined representation of both control and data dependence. It has been widely used in analysis tasks such as program slicing [HRB88, Bin99], in parallelization and vectorization optimizations [ZSE04, BHRB89], and as a software engineering and testing tool [OO84, BH93]. Many traditional optimizations operate more efficiently on the PDG [FOW87], and we can see it makes large steps forward in two of the themes outlined earlier:

- **Control Flow** Ordering requirements are substantially relaxed by treating statements such as x+=1 as atomic and allowing a *group node* which represents "execute all child nodes of this node" in some order. Thus edges no longer represent control flow.

- **Dependencies** are made more explicit than in the CFG by the use of a separate class of data dependence edges between siblings, which restrict the possible orderings. (These are analogous to the dependence edges between tasks used in project management to identify critical paths.)

(In terms of assignment, values are still carried by placing them into variables, much as in the CFG. Hence, SSA form can again be applied to simplify analysis tasks.) However, sequen-

tialization of the PDG is substantially more difficult, and some PDGs *cannot* be sequentialized without duplicating some of their nodes.

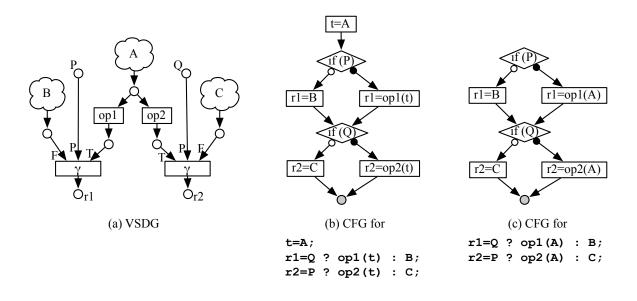

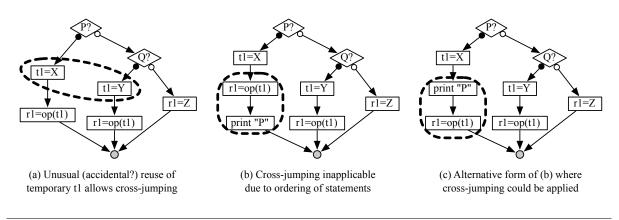

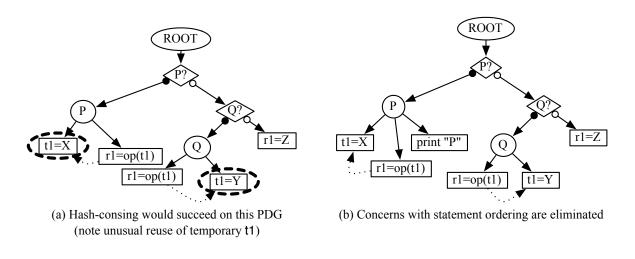

Some ordering restrictions—some specification of Control Flow—remain even in the PDG, however, as the following code sequences are treated as distinct:

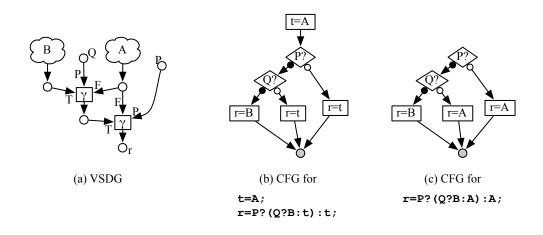

While this is very suitable in a machine-oriented intermediate code (because of the different timing effects), it is less appropriate for a general optimisation phase, as we may wish to make late decisions on which form to use based on, for example, register pressure *after* optimization.

#### 1.5.3 The Value (State) Dependence Graph

Another, more recent, IR—variously known as the Value Dependence Graph (VDG) [WCES94], Value State Dependence Graph (VSDG) [JM03], or more generally, as the class of Gated Data Dependence Graphs (Gated DDGs) [Upt06]—has also been proposed, but has yet to receive widespread acceptance<sup>3</sup>.

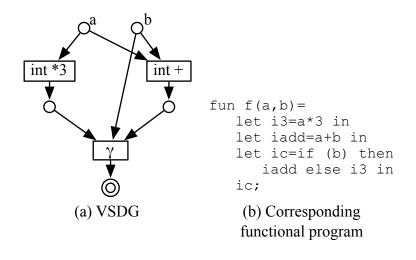

This IR can be seen as the logical culmination of all three trends:

- **Assignment** is entirely absent, as it replaces executable/imperative statements with functional operations.

- **Control Flow** is not indicated at all: the VSDG takes the viewpoint that control flow exists only to route appropriate values to appropriate operations, and records merely which values and operations are appropriate, not how this routing can be achieved.

- **Dependencies** are indicated explicitly, including the conditions under which each occurs (i.e. under which each value is selected).

### 1.6 Optimizations on the VSDG

Earlier, in Section 1.4, we said the VSDG makes the optimization stages—that is, many of the analyses and transformations on which CFG compilers spend their time—much simpler and easier.

An overview of how many traditional CFG optimizations can easily be applied to the VSDG is given by Upton [Upt06]: we summarize that those where the main difficulty is in the dataflow analysis (e.g. constant propagation and folding, algebraic simplification, escape analysis) become much easier in the VSDG. In other cases (e.g. type-like analyses, devirtualization, scalar replacement, loop unrolling) using the VSDG makes little difference, and we see many such optimizations as having clear VSDG equivalents or being able to be "ported" across the IR gap with minimal changes. Indeed, Singer [Sin05] has shown how many optimizations can be done in an identical fashion on CFGs satisfying different restrictions on variable naming and reuse,

<sup>&</sup>lt;sup>3</sup>The exact differences between these will be explained and reviewed later, but for now we can see the two being based on the same principles—in particular, every VDG is a VSDG. The VSDG adds explicit *state edges* to link operations which must have their ordering preserved (such as the indirect stores resulting from \*x=1; \*y=2; when the aliasing of x and y is unknown).

including SSA and SSI [Ana99] forms, and we see the same principle as applying equally to the selection of VSDG over CFG (the VSDG is implicitly in SSA form). In some cases (e.g. constant propagation), the precision of the result depends on the IR that was used, but others (e.g. dead-code elimination) work independently of the IR altogether.

Further, we argue that many optimizations can be made more effective and general by so changing or redeveloping them to take advantage of the VSDG's features. Where optimizations seem to occur implicitly by representation in the VSDG, this is a highly effective way of implementing them—although in some cases it may be merely delaying the issues until the sequentialization stage (discussed in Section 1.7.1).

# 1.7 The Sequentialization Problem

In Section 1.4 we also said that conversion of the VSDG to machine code was difficult. We argue previous attempts at VSDG sequentialization fall short of making use of the VSDG practical, and indeed, Upton suggests that the sequentialization problem is the major obstacle preventing the widespread usage of the VSDG in real compilers. We can see several reasons for this:

- Evaluation of nodes proceeds in a *wavefront*, i.e. a cut across the entire VSDG. This does not fit well with the sequential nature of execution in conventional computers, which have only a single program counter, identifying a single point or program location.

- Evaluation proceeds *nondeterministically*—that is, the VSDG does not specify how the wavefront moves, what nodes it passes over, or in what order (or even how many times). This issue is explored in more detail in Chapter 2, but is in stark contrast to the highly *deterministic* nature of conventional computers, where programs instruct the CPU exactly what to do and in what order<sup>4</sup>.

- The VSDG is highly normalizing. Whilst we have discussed the benefits of this already, it also implies a cost: somehow the compiler must choose the best representation to output; this may involve some element of search.

### 1.7.1 Sequentialization and Late Decisions

Normalization is normally done by the compiler translating all the different source code versions into the same form in its intermediate representation, *either* by some kind of normalizing transformation (which explicitly selects one of the corresponding IR versions), *or* because the IR *cannot* distinguish between them. An example is the ordering of independent instructions: in some IRs (e.g. the CFG), these are explicitly ordered (so a normalizing transformation would be some kind of sort), but in other IRs (e.g. the PDG), the ordering is not specified.

The VSDG tends towards the latter: many optimizations, which would be separate passes in a CFG compiler, seem trivial in a VSDG framework, due to the VSDG's normalizing properties. That is, they automatically (or implicitly) occur merely by representing a program as a VSDG.

However, this does not entirely avoid the problem: rather, it merely delays the decision until the IR is transformed into some form which does make the distinction, namely until the sequentialization stage. Thus, sequentialization wraps up many such optimizations together, and concentrates their difficulty into one place. However, this approach *does* seem helpful in

<sup>&</sup>lt;sup>4</sup>even if modern out-of-order CPUs may not always follow such instructions exactly!

addressing phase-order problems, which have been a particular problem for CFG compilers which (historically) tend to focus on implementing many distinct optimizations each in its own pass.

# 1.8 Chapter Summary

We have seen a number of trends suggesting that a switch to the VSDG would be an advantageous progression in intermediate representations and perhaps the logical "next step" in compilers. We also saw that this potential was being held back by of the difficulty of *sequentialization*: converting instances of the VSDG, perhaps highly optimized, back into good sequential CFG code.

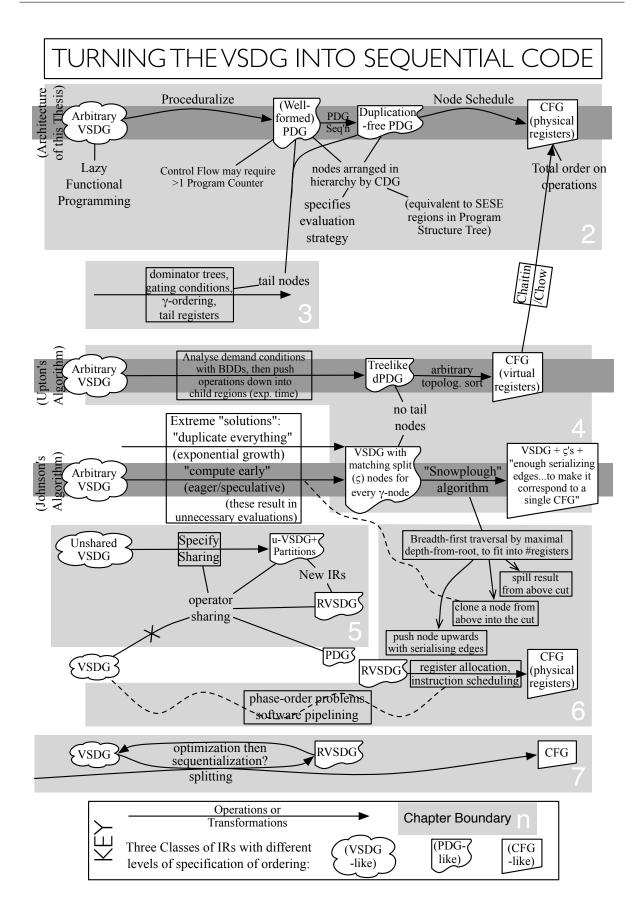

**Structure of this Thesis** We tackle the problem of sequentialization by breaking it into three phases; although previous attempts have used similar ideas implicitly, they have not properly distinguished between these phases. Key to this is the use of a special form of *duplication-free* PDG (df-PDG) as a midpoint between VSDG and CFG.

Chapter 2 explains our compiler architecture and the breakdown into phases by formally defining the VSDG and PDG and reviewing the significance of duplication-freedom. Chapter 3 describes how VSDGs may be converted into PDGs suitable for input to existing techniques of PDG sequentialization. Chapter 4 reviews how these existing techniques produce df-PDGs, and compares our approach with previous techniques for VSDG sequentialization as well as classical CFG code motion. Chapter 5 reconsiders the VSDG-to-PDG conversion process from a more theoretical standpoint, and defines a new data structure, the *Regionalized VSDG* (RVSDG), as a reformulation of the PDG. This is then used in Chapter 6 which considers how df-PDGs (df-RVSDGs) may be converted to CFGs, and critically reviews the earlier breakdown of sequentialization into phases. Chapter 7 reflects on the treatment of sequentialization as a separate stage after optimization (as shown in Figure 1.1) and the difficulties remaining in this structure by studying an optimizations. Finally, Chapter 8 concludes and suggests further research directions.

# CHAPTER 2

# The Nature of the Beast

What the VSDG is, and How it Makes Life Difficult

**In this Chapter** we will explain in detail how a program is represented as a VSDG; how this differs from other IRs, and thus what tasks the sequentialization phase must perform; and how we tackle this problem by breaking sequentialization apart into phases. The chapter concludes with formal definitions of both VSDG and PDG.

# 2.1 The VSDG by Example

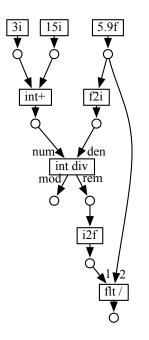

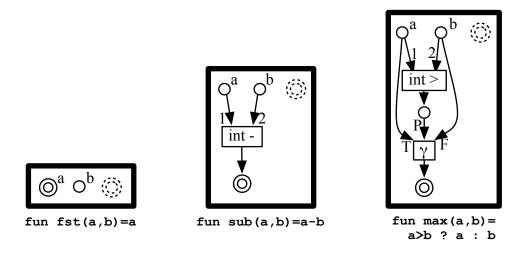

The VSDG represents programs graphically, using nodes and edges. Historically nodes have been computations, and edges represented values. However, for this work we borrow the notation (although not the exact semantics) of Petri-Nets [Pet81]. Nodes come in two forms: *places* (round, representing values) and *transitions* (square, representing operations such as ALU instructions). Such operations include constants—transitions with no predecessors:

and computations, which have incoming edges to indicate the values on which they operate:

As the above example shows, operations may have multiple operands, and/or produce multiple values, and these are distinguished by edge labels. However each place is the *result* of its unique *producer* transition (this is in contrast to regular Petri Nets). The exact set of operations available is a compiler implementation detail and may depend upon the target architecture.

There is no need for a VSDG to be treelike: a single result may be used many times, as in the above. However there must be no cycles; the following example is *not* legal:

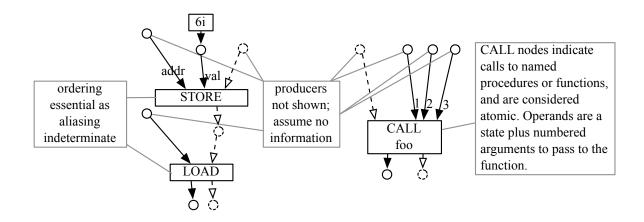

Instead of containing values, some *places* may instead contain *states*, which model both the contents of memory (seen as external to the VSDG) and termination (of both loops and function calls), and indicate the essential sequential dependencies between operations due to these. We draw states with dotted boundaries and connecting edges; *linearity* restrictions on the graph ensure that, dynamically, each state produced must be used exactly once:

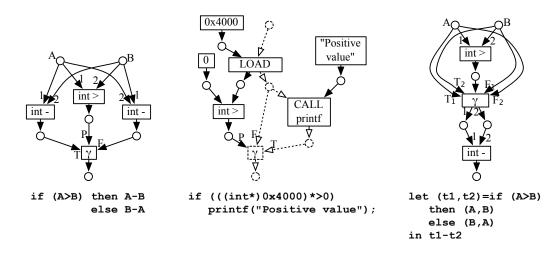

Choices between values, states, or tuples thereof, are represented using  $\gamma$ -nodes:

(Note how the third example differs from the first by having only a single static subtraction.)

Places may include *arguments*, identifiable by (uniquely) having no predecessor transitions, and also include the *results* of the VSDG, drawn with double outlines. These provide a way for values and/or state to be passed into and out of the VSDG, and may be named to distinguish between them. Note that the same place may be both argument and result, as shown in Figure 2.1.

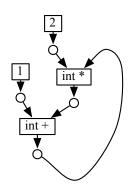

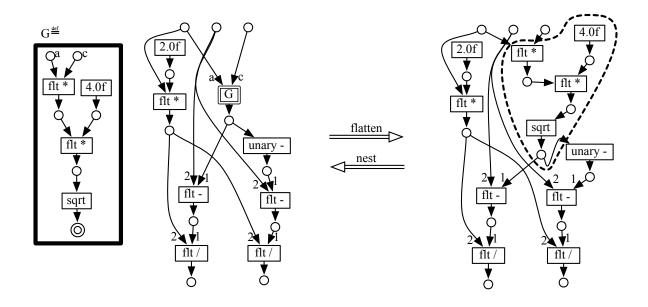

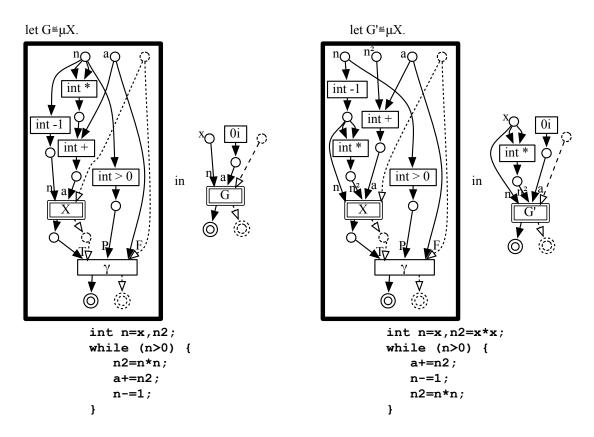

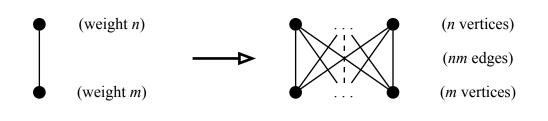

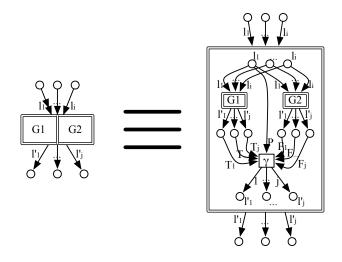

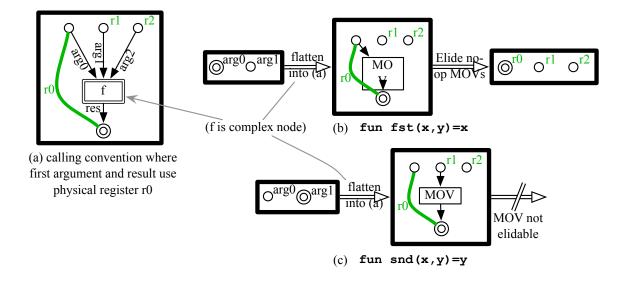

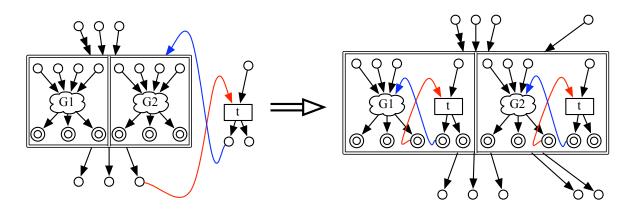

VSDGs can also be *hierarchical* graphs, in which individual *compound nodes*, drawn with a double outline, may contain entire graphs; the *flattening* operation merges such encapsulated graphs into the outer (containing) graph, as shown in Figure 2.2.

Flattening works by *quotienting* places in the containing graph with those in the contained graph, according to edge and place labels in the respective graphs. (Note that the kind—value or state—of an edge or place is a label.) The dotted group of nodes in the result records the extent of the contained group, allowing an inverse operation of *nesting*.

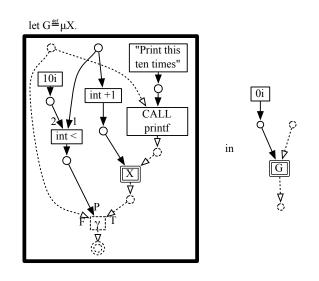

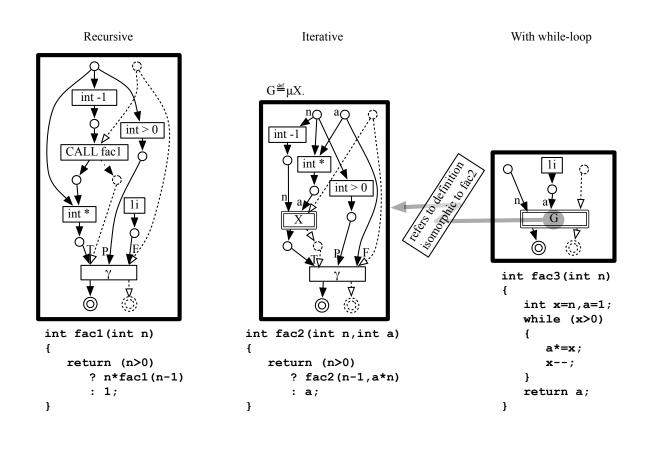

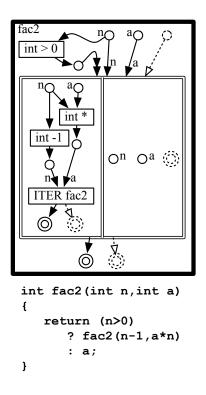

Figure 2.3 shows how this mechanism is used to represent loops, by using standard  $\mu$  fixpoint notation to write an infinite (regular, treelike) hierarchy. As Figure 2.4 shows, this is similar to the representation of functions.

Figure 2.1: Argument and Result places are drawn with double outlines

Figure 2.2: VSDGs can also be hierarchical graphs.

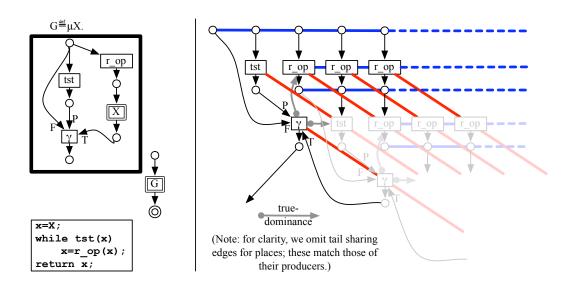

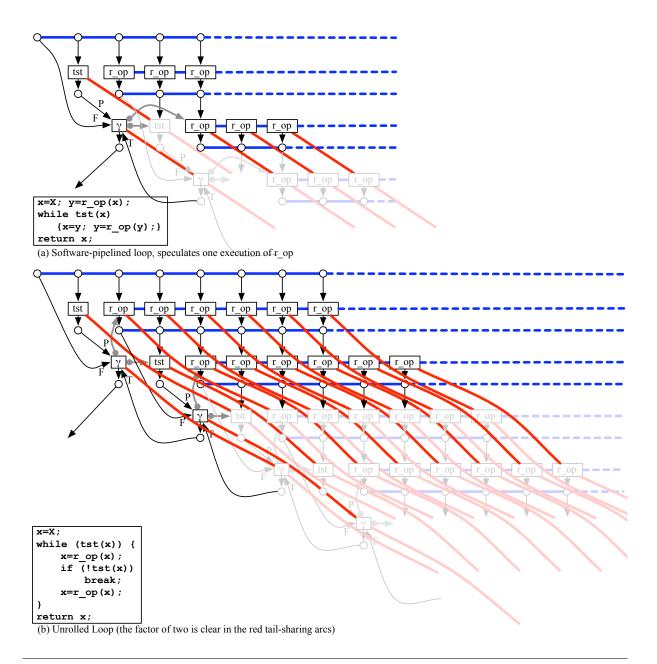

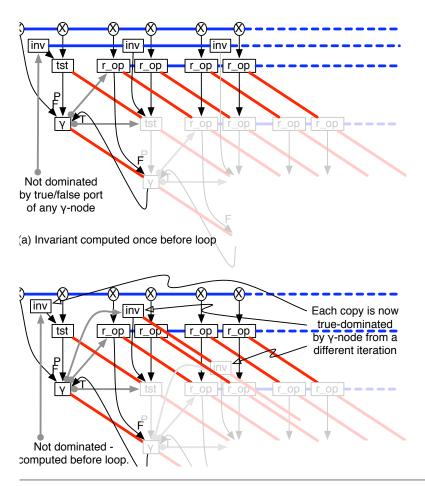

**Figure 2.3**: Loops are represented using the  $\mu$ -operator. (The syntactic definition  $G \stackrel{\text{def}}{=} \mu X...$  can alternatively be seen as a declaration let rec  $G=...[{}^{\mathbf{G}}_{X}]$ )

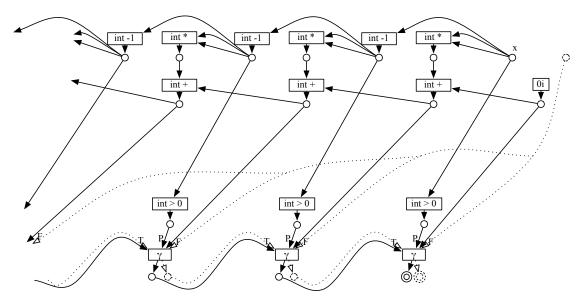

**Figure 2.4**: Three representations of the factorial function. Here only the first uses the stack, to make recursive function calls facl(...). The second instead uses iteration, which can be seen as a loop (*à la* tail calls in ML); the third wraps this loop in a procedure taking one fewer argument. A valid alternative form of the second VSDG exists in which the complex node in the recursive definition—shown textually as containing *X*—is replaced by CALL fac2; this would also use the stack (much as an "iterative" function might if it were not subject to the tail call optimization).

### 2.1.1 Uniformity of Expressions

A key feature of the VSDG is that  $\gamma$ -nodes—which implement choice between or selection of values (and states)—are just nodes like any other (arithmetic) operation. Thus, many transformations naturally treat expressions in the same way regardless of whether they are spread over multiple basic blocks or just one: the basic block structure is part of the expression. This contrasts with the CFG's two-level system where the *shape* of the graph (i.e. the structure of nodes and edges) specifies the control-flow—which implements choice between or selection of values (and states)—and the *labelling* of the nodes specifies the other (arithmetic) operations: thus, many transformations work by moving the labels (instructions) around within and between the nodes (basic blocks).

This ability to treat expressions uniformly is a recurring theme throughout this thesis, and is particularly important in Chapters 6 and 7.

### 2.1.2 Formal Notations

We use n to range over nodes (either places or transitions) generally;

r, s, x, y for arbitrary places or results, usually values, or  $\sigma$  to indicate specifically a state;

t, u, v or sometimes op for operations or transitions (functions in the mathematical sense). We tend to use foo and bar for external functions, especially those whose invocation requires and produces a *state* operand, as opposed to those which have been proven side-effect-free and always-terminating.

g ranges over  $\gamma$ -nodes;

P, Q range over predicates, both in the VSDG (where they are places containing value of boolean type) and more generally (including in the CFG and PDG, where P and Q can also identify a corresponding branch or predicate node);

G ranges over either graphs (including hierarchical VSDGs) or, according to context, PDG group nodes.

We borrow other notations from Petri-Nets, writing t for the set of *predecessors* (operands) to a transition t, and  $t^{\bullet}$  for the set of successors (results) of t. We also write  $s^{\bullet}$  for the set of successors (now *consumers*) of a place s, and by abuse of notation apply the same notation for sets of places, thus:  $S'^{\bullet} = \bigcup_{s \in S'} s^{\bullet}$ . (Hence,  $t^{\bullet \bullet}$  is the set of consumers of any result of t.) However we write s for the predecessor (producer) of a place s—recall this is a single transition not a set—and again implicitly lift this over sets of places.

# 2.2 The VSDG and Functional Programming

In this section we explore the connection between the VSDG and functional programming languages such as ML and Haskell. This yields some insight into the problem of sequentialising the VSDG.

### 2.2.1 SSA and Strict Languages

Appel [App98] has previously noted that, because SSA effectively removes the (imperative) notion of assignment, any program in SSA form is equivalent to a functional program; the equivalence can be seen as follows:

1. Liveness analysis is performed, to identify the SSA variables live at entry to each basic

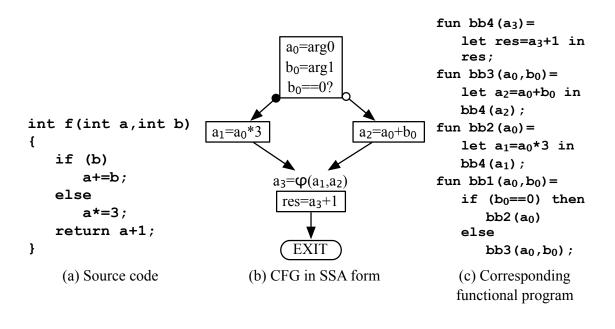

Figure 2.5: Correspondence between SSA Form and Functional Programming

block (including results of  $\phi$ -functions, not their operands)

- 2. For each basic block, there is a corresponding named function, with parameters being the live variables

- 3. Each assignment statement  $v_1 := op(v_2, v_3)$  corresponds to a let statement let  $v_1 = op(v_2, v_3)$

- 4. Each successor edge is converted into a call to the corresponding function, passing as arguments:

- For variables (parameters) defined in the CFG by a  $\phi$ -function, the corresponding *operand* to the  $\phi$ -function

- For other variables, the same variable in the calling function

An example of this correspondence is given in Figure 2.5. However, particularly interesting for us is the equivalence of evaluation behaviour. Execution of a basic block in a CFG proceeds by evaluating the RHS, and storing the result in the LHS, of each statement in turn. This is the same as the behaviour when evaluating the corresponding function *in a strict language* (such as ML): for each let statement in turn, the expression is evaluated and assigned to the variable, before proceeding to the body of the let (i.e. the next such statement)<sup>1</sup>. The functional program is in fact in Administrative Normal Form (ANF) [CKZ03].

### 2.2.2 Encoding the VSDG as a Functional Program

Since the VSDG is implicitly in SSA form (every value has a single producer!), it is not surprising that a translation to an equivalent<sup>2</sup> functional program exists. The translation for stateless

<sup>&</sup>lt;sup>1</sup>Even the ordering of side effects is thus preserved.

<sup>&</sup>lt;sup>2</sup>Having the same observable semantics—this is discussed in Section 2.7.

**Figure 2.6**: Correspondence between VSDG and Functional Programming (Source code given in Figure 2.5(a).)

(VDG) fragments is as follows:

- 1. Order the transitions of the V(S)DG into any topological sort respecting their dependence edges. (Such an order is guaranteed to exist because the VSDG is acyclic.)

- 2. Assign each place s a unique variable name  $v_s$

- 3. For each transition t in topological sort order, let  $\overrightarrow{v_i}$  be the set of variable names corresponding to t's operand places t, and let  $\overrightarrow{v_r}$  be the set of variable names corresponding to its results  $t^{\bullet}$ . Output the statement let  $(\overrightarrow{v_r}) = op(\overrightarrow{v_i})$  in where op is the function implementing the node's operation.  $(\overrightarrow{v_i} \text{ are guaranteed to be in scope because of the topological sort.)$

An example is given in Figure 2.6. (For stateful VSDGs, the same principles apply, but the translation is more complicated and given in Appendix B).

### 2.2.3 Evaluation Strategies

In Section 2.2.1 we observed that the evaluation behaviour of the CFG was the same as its corresponding functional program under *strict* language semantics. However, the semantics of the VSDG do not specify an exact evaluation behaviour, i.e. which transitions are executed—merely which places are *used* as part of the overall result. In fact stateless fragments of the VSDG, like expressions in pure functional programming languages, are *referentially transparent*:

**Referential Transparency** An expression E is referentially transparent if any subexpression and its value (the result of evaluating it) can be interchanged without changing the value of E.

Definition from FOLDOC, the Free On-Line Dictionary Of Computing, www.foldoc.org

A consequence of this is the Church-Rosser theorem:

**Church-Rosser Theorem** A property of a reduction system that states that if an expression can be reduced by zero or more reduction steps to either expression M or expression N then there exists some other expression to which both M and N can be reduced.

Such *reduction systems* include both the  $\lambda$ -calculus and the VSDG (we will use  $\lambda$ -calculus for this discussion, because its properties are well-known, even though we will not use any higherorder features until Chapter 5). From the perspective of the  $\lambda$ -calculus, this means that any term has at most one normal form, or (equivalently), any sequence of reductions that terminates in a normal form (i.e. value) will terminate in the same value. From the perspective of the VSDG, this means that the choice of which VSDG nodes are evaluated will not affect the result. Since the VSDG only describes the resulting value, *it does not specify which nodes are evaluated*.

Several *evaluation strategies* (or *reduction strategies*) have been suggested for  $\lambda$ -calculus terms, and these can also be applied to the VSDG:

Call-by-Name Recompute the value each time it is needed.

- **Call-by-Need** Compute the value if and only if it is needed; but if it is, store the value, such that on subsequent occassions the value will not be recomputed but rather the stored value will be returned.

- **Call-by-Value** Compute the value immediately, whether it is needed or not, and store the result ready for use.

We can see these strategies in a range of contexts. In the  $\lambda$ -calculus, call-by-value means reducing the RHS of any application *before* the application itself; call-by-name the opposite (thus, always performing the outermost reduction first); and call-by-need is as call-by-name but requires representing the expression using a DAG rather than a tree<sup>3</sup>. In functional programming languages, the strategies typically refer to the treatment of arguments to procedure calls; in a call-by-value language, arguments are evaluated *eagerly*, before calling, so evaluation of an expression is only avoided by it being on one arm of an *if*.

However, a more insightful perspective is obtained by considering let statements. These allow the same subexpression to be referenced in multiple places, for example let x=E in if E' then x else if E'' then x else E'''. In a call-by-value language (such as ML), evaluation of such a statement *first evaluates the argument to the* let (E in the example above); the body is then processed with x already containing a value. Contrastingly, in a call-by-need language such as Haskell, the argument E of the let-expr need be evaluated *only if* x *is used in the body*.

A great deal of work has been put into attempting to make lazy languages execute quickly. Observing that call-by-value is more efficient on today's sequential imperative hardware, optimizations attempt to use eager evaluation *selectively* in order to boost performance. The key issue in all cases is to preserve the termination semantics of the language, i.e. call-by-need. *Strictness analysis* [Myc80] attempts to identify expressions which *will definitely be evaluated*, and then computes their values early. Other techniques evaluate expressions *speculatively*, that is, before before they are known to be needed: termination analysis [Gie95] identifies subexpressions which will definitely terminate, and can thus be speculated safely; optimistic evaluation [Enn04] may begin evaluating any expression, but aborts upon reaching a time-limit.

<sup>&</sup>lt;sup>3</sup>Significantly, call-by-need terminates if and only if call-by-name terminates, but will do so in at most the same number of reduction steps, often fewer.

(Timeouts are then adjusted adaptively by a runtime system to avoid wasting excessive cycles on computations whose results may be discarded). However despite these efforts the performance of lazy languages generally lags behind that of strict ones.

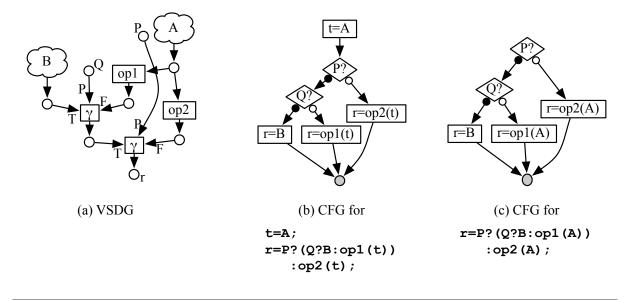

In the VSDG, the situation is similar: the compiler may select a non-lazy evaluation strategy to try to boost performance, so long as the termination semantics of call-by-need are preserved. *State edges* explicitly distinguish operations which may not be speculated—those with side-effects, or which may not terminate<sup>4</sup>—from all others, which may be; but just as for functional programs, the compiler must avoid *infinite* speculation, as this would introduce non-termination<sup>5</sup>. Moreover, the same choice remains, between the potential wasted effort of speculative evaluation, and the difficulty of arranging control flow for lazy evaluation.

Thus, whereas an (SSA) CFG corresponds to a functional program in a *strict* language, we see a VSDG as corresponding to its equivalent functional program in a *lazy* language.

### 2.2.4 Higher-Order Programming

*Higher-order programming* refers generally to the use of variables to store functions or computations, that is, to store code rather than values. Thus, a higher-order variable is one containing a *stored procedure*; this can be called or invoked as any other procedure, but the actual code that is executed depends upon the runtime value of the variable.

In the context of a programming language explicitly supporting higher-order programming, implementation probably involves such a variable containing a function pointer—i.e. the code's address in memory—with invocation being an *indirect* jump. This might seem to have little in common with the VSDG; the *Value* (State) Dependence Graph represents a computation in terms of the *values* involved, with edges showing which other values computation requires. That every node is a value, not a function, is quite clear in the Haskell translation of Section 2.2.2: every variable is of ground type.

However, as discussed in Section 2.2.3, the evaluation model of the VSDG means that *every* variable, although of ground type, implicitly stores not a value but rather the computation required to produce it. For call-by-need rather than call-by-name, we can see the stored computation as being of the form

```

if (!COMPUTED) {

VALUE=...;

COMPUTED=TRUE;

};

return VALUE;

```

In contrast to Haskell—we are using the VSDG for intraprocedural compilation and optimization—the implementation of such stored procedures will generally be to *inline* a copy of the stored procedure *into each call site*. (The possibility of using VSDG compilation techniques for first-order Haskell program fragments remains, however.)

<sup>&</sup>lt;sup>4</sup>Potentially also those which may raise exceptions—this is discussed in Appendix B.7.

<sup>&</sup>lt;sup>5</sup>Thus the semantics of the VSDG, in Section 2.7.2, insist on a *fairness* criterion which allows only a *finite* amount of speculation.

# 2.3 The VSDG and the Program Dependence Graph

The PDG has been mentioned already, and is defined formally in Section 2.5. We previously described the PDG as being an intermediate point between the CFG and VSDG in terms of its representation of control flow: whereas in the CFG nodes have explicit control flow successor edges, in the PDG there is *some* control flow information—roughly, "execute this under these conditions".

In comparison, the VSDG does not represent such details (recall its translation into a functional programming language, in Section 2.2.2): it deals only with the use of values (with each let-expr describing *how* each value may be computed from each other), rather than the execution of the statements or computations (implicitly stored in each variable) producing those values—by the principle of referential transparency, these may be executed at any time. Whereas the VSDG is functional, the PDG is *imperative*, with extra information in its CDG component. This describes *what* to compute and *when*—that is, *the Control Dependence subgraph encodes an evaluation strategy*.

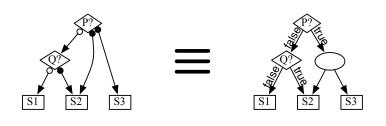

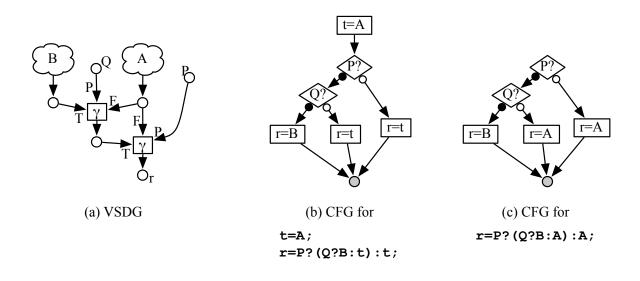

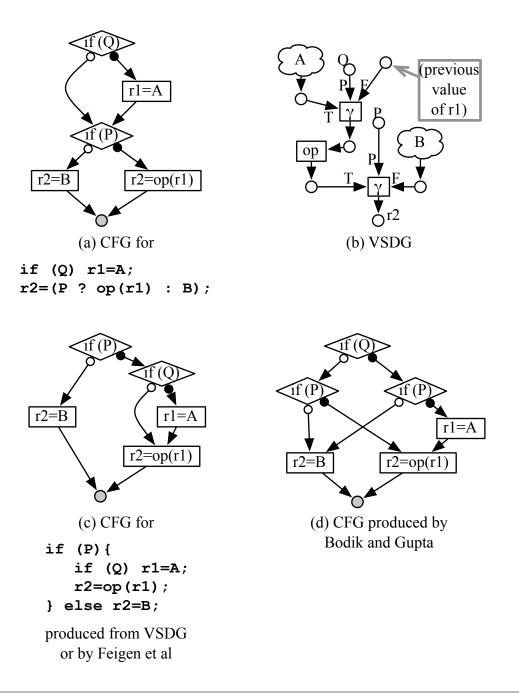

A particular insight stems from the *ill-formed* PDG of Figure 2.8 on page 38. This is seen as an incomplete specification of either of the following (semantically different—e.g. consider S as x+=1) programs:

```

{if (P) S;} {if (P') S;}

{if (P || P') S;}

```

Observe that the first of these corresponds to call-by-name, and the second to call-by-need. Hence, the graph of Figure 2.8 is not a valid PDG because it does not specify which evaluation strategy to use, and a PDG must do so. In contrast, VSDGs of similar structure *are* legal<sup>6</sup>, and the VSDG allows the *choice* of either strategy. (This poses problems for naïve sequentialization algorithms, considered in Section 3.2.1.)

# 2.4 An Architecture for VSDG Sequentialization

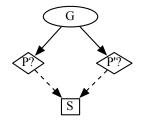

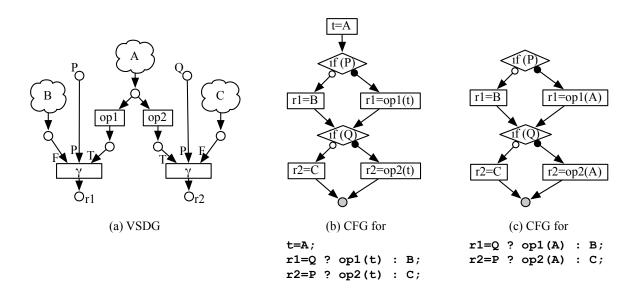

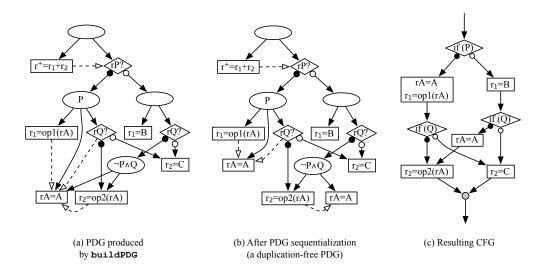

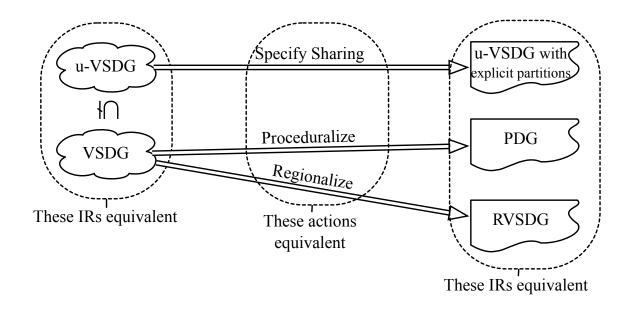

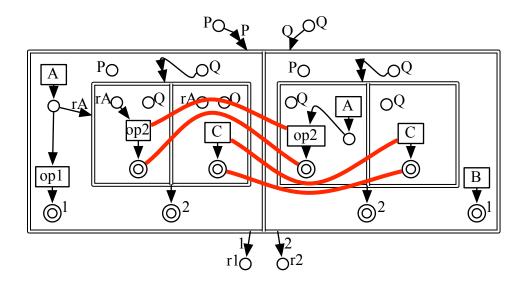

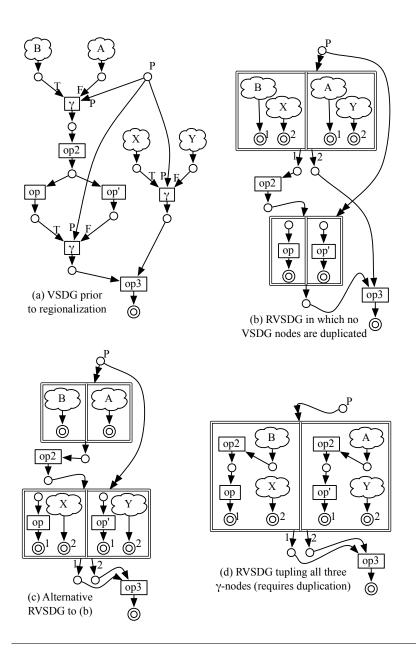

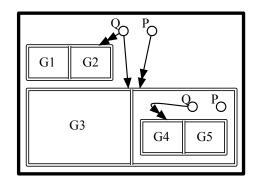

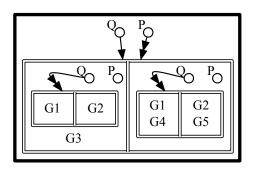

We tackle the sequentialization problem by breaking it into three phases, as shown in Figure 2.4:

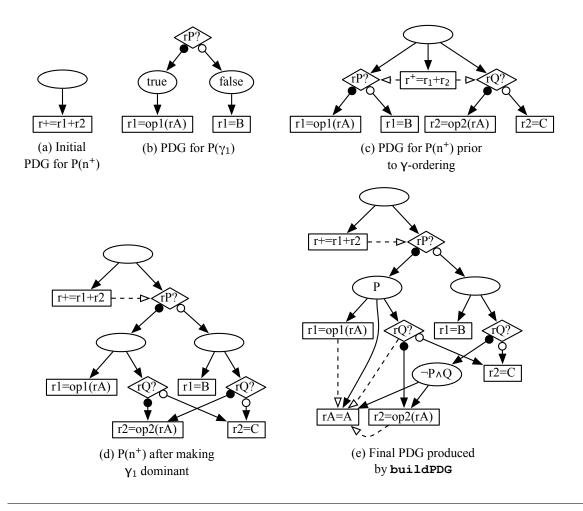

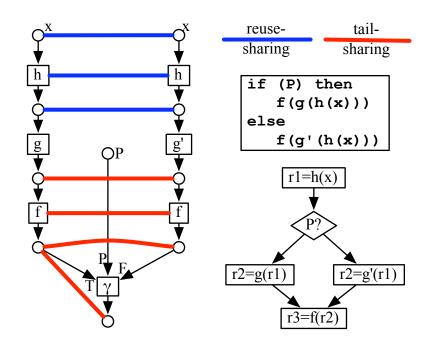

- **Proceduralization:** conversion from (parallel) *functional* to (parallel) *imperative* form—that is, from referentially-transparent expressions into side-effecting statements. From the VSDG, this produces a PDG, and requires selection of an *evaluation strategy*, working out a structure for the program to implement this strategy, and encoding that structure in the Control Dependence Graph subgraph of the PDG (missing from the VSDG). Chapter 3 covers this in detail.

- **PDG Sequentialization** (by existing techniques): we see this as converting from a PDG to a special form of *duplication-free* PDG or *df-PDG*, explained below. Chapter 4 reviews these techniques and discusses related issues.

- **Node Scheduling:** conversion from *parallel* (imperative) to *serial* (imperative) form—this consists of putting the unordered program elements of the df-PDG (statements and groups) into an order, producing a CFG. Chapter 6 covers this.

Key to our approach is the use of the Program Dependence Graph (PDG, defined in Section 2.5 below), including the integration of existing techniques of PDG sequentialization.

<sup>&</sup>lt;sup>6</sup>Except when S is stateful; in such cases linearity restrictions require that one behaviour is specified.

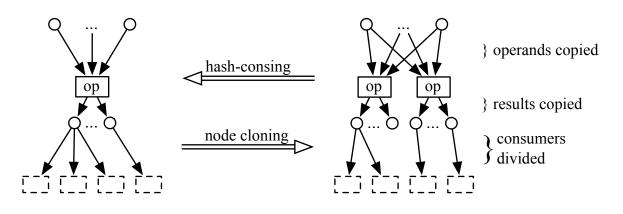

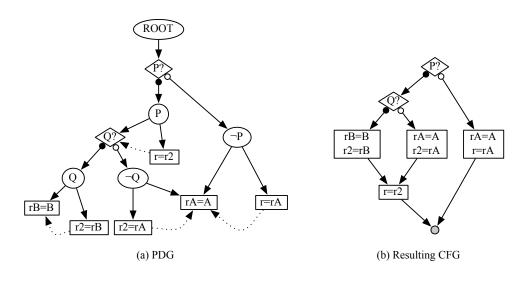

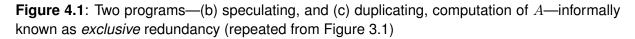

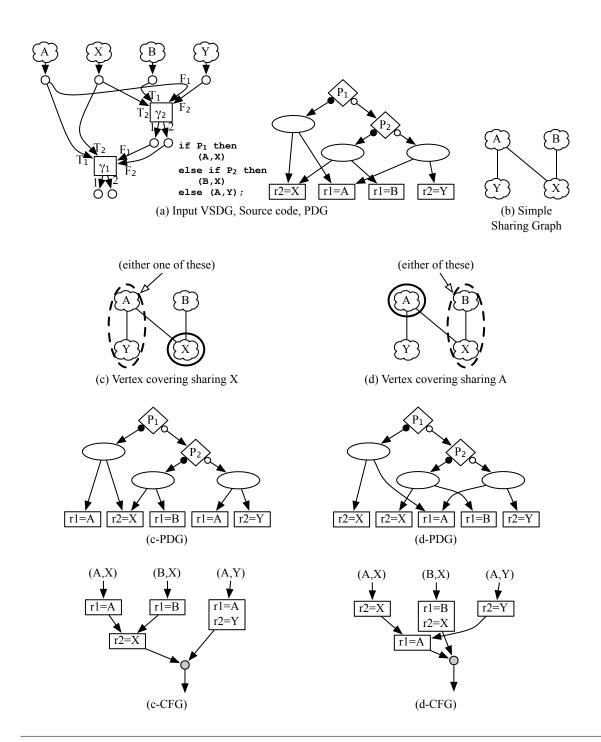

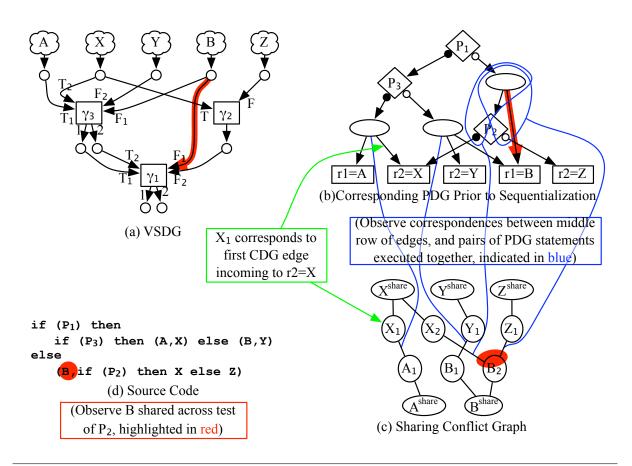

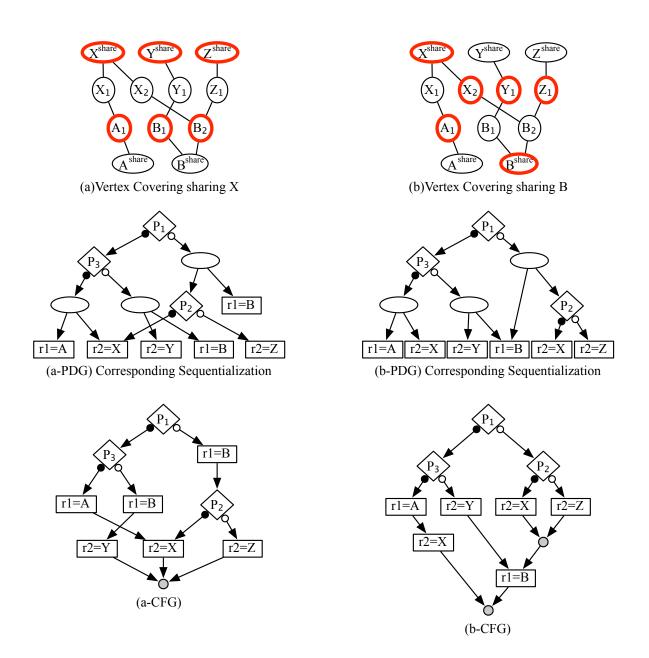

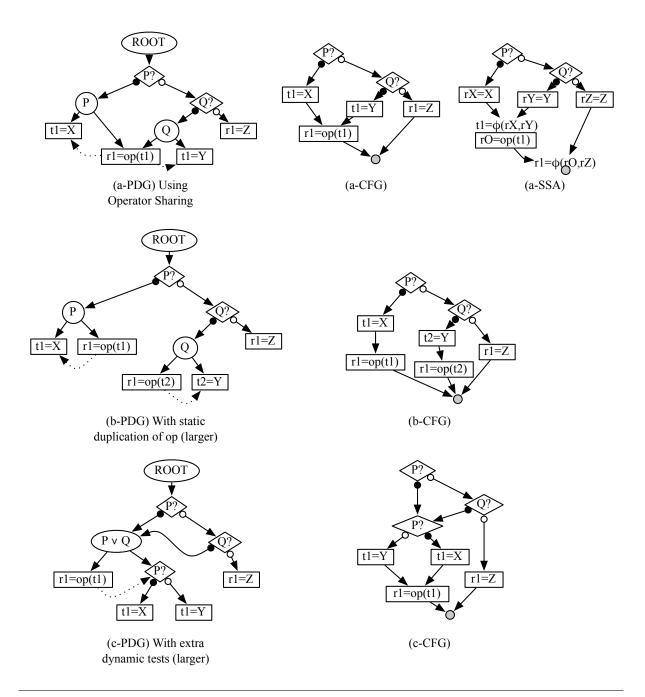

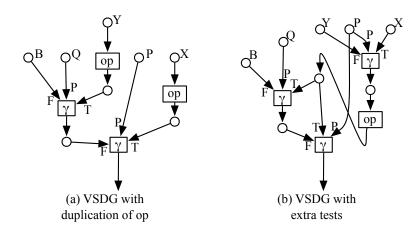

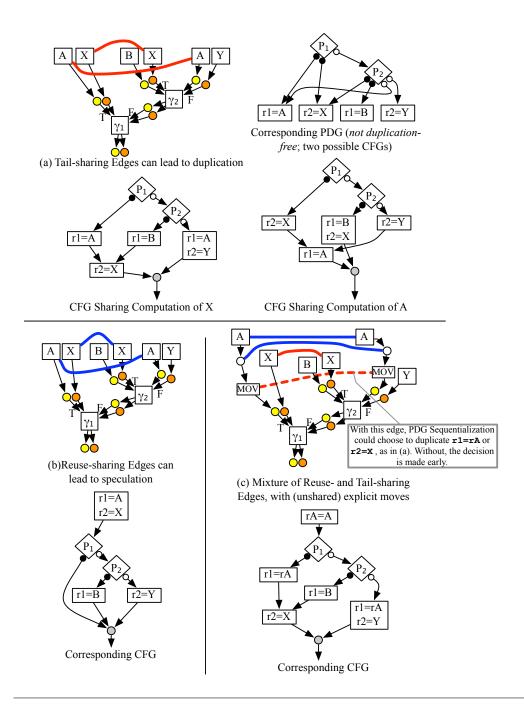

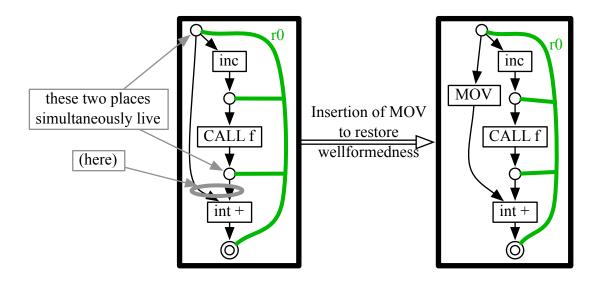

**PDG Sequentialization** is usually seen as converting from PDG to CFG; since the PDG already contains imperative statements which can be placed directly onto nodes of a CFG, the main task is in arranging the statements—specifically, ordering the children of each group node—so that all the children execute when the group does. A key question is:

Given a node n which is a child of two group nodes  $G_1$  and  $G_2$ , is it possible to route executions of n resulting from  $G_1$  and  $G_2$  through only a single copy of n in the CFG?

The intuition is that if n can be executed *last* among the children of both  $G_1$  and  $G_2$ , then a single CFG node suffices<sup>7</sup>; if not, then two copies of n—one for each parent—are required. Clearly, no ordering of the children of a group node can put every child last(!), but in a special class of PDGs known as *duplication-free* PDGs (df-PDGs), no nodes need be duplicated to make a CFG. Intuitively, these can be characterized as having control flow which can be implemented using only a single Program Counter (PC).

We mentioned above that PDG sequentialization is normally seen as transforming a PDG into a CFG: the task is to exhibit a *total ordering* of each group node's children, which can be naturally encoded into the successor relation of a CFG. However, it is possible for many different sequentializations (orderings) to exist: Ball and Horwitz [BH92] show that in any *duplication-free* PDG, every pair of siblings either *must* be placed in a particular order in the resulting CFG (property OrderFixed), or *may* be placed in either order (property OrderArbitrary). That is, the OrderFixeds form the elements of a *partial* ordering, and *every* total ordering respecting it is a valid (CFG) sequentialization.

In our compilation framework, we wish to preserve as much flexibility in ordering as possible for the node scheduler. Thus, we use existing PDG sequentialization techniques only to identify which pairs of nodes in a df-PDG are OrderFixed or OrderArbitrary; ordering within groups of OrderArbitrary nodes is left to the node scheduler. (That is, the node scheduler must take into account ordering restrictions resulting from PDG sequentialization as well as data dependence.) Instead, the main task of PDG sequentialization is to *make* the PDG duplicationfree. This problem has not been well-studied, but we consider it in Chapter 4.

### 2.4.1 The VSDG and Phase-Order Problems

The phase-order problem is a long-standing issue in optimising compilers.

**On the CFG,** individual optimizations—such as register allocation, instruction scheduling for removing pipeline bubbles, or code motion—are often implemented individually, as separate passes. The phase-order problem lies in that for many pairs of these phases, each can hinder the other if done first: register allocation prevents instruction scheduling from permuting instructions assigned to the same physical registers, whereas instruction scheduling lengthens variable lifetimes which makes allocation more difficult. Thus, there is *no* good ordering for these phases.

The alternative approach is to try to combine phases together—leading to register-pressuresensitive scheduling algorithms [NP95], for example. This makes the concept of optimality

<sup>&</sup>lt;sup>7</sup>This ordering of statements allows control flow to "fall through", capturing the desirable possibility of using *shortcircuit evaluation* and generalizing the *cross-jumping* optimization on CFGs.

harder to identify, and much harder to reach. However this is only because the goals of optimality in the individual phases are discarded; and we argue that these goals have always been somewhat illusory: ultimately it is the quality of the final code that counts.

**The VSDG** leans towards the second approach. Its increased flexibility, and the lack of constraints to code motion it offers, have proven helpful in combining profitably some phases which have been particularly antagonistic in the past: for example common-subexpression elimination and register allocation (dealt with by Johnson [JM03]), and instruction scheduling (in Chapter 6). Important here is the way the VSDG wraps up many normalizing transformations, which would be discrete phases in CFG compilers, into the sequentialization stage (Section 1.7.1).

In this way, many of the phase-order problems of CFG compilers are reduced. They are not entirely eliminated, in that the phases identified above are not perfectly separate, and so in a truly *optimising* compiler<sup>8</sup>, the phases would have to be combined and/or the interactions between them considered. Hence, our VSDG compiler will suffer similar, but different, phase-order problems to those of CFG compilers. However we argue that these are less severe in our case for two reasons:

- 1. We have fewer phases than traditional CFG compilers (as an extreme example, the Jikes RVM optimizing compiler has over 100 phases including many repetitions).

- 2. The phases we use have more orthogonal concerns. Specifically, proceduralization is concerned with the shape (or interval structure) of the graph (that is, nodes and subtrees are interchangeable), and is largely machine-independent, whereas node scheduling looks at the size or node-level structure of the graph, and deals with machine-dependent characteristics such as register file width and instruction latencies.

(We discuss the vestigial problems with our division into phases further in Section 6.5, including some possibilities for interleaving them at a fine level. However it is worth bearing in mind, in any attempt to truly "combine" the phases of proceduralization and node scheduling, that the task of putting unordered program elements into an order first requires knowing what program elements must be ordered!)

### 2.4.2 Three Phases or Two?

The division of VSDG sequentialization into three phases leaves PDG sequentialization sitting somewhat uncomfortably in the middle of the other two: at times it seems like the last part of proceduralization, and at other times like the first part of node scheduling.

PDG sequentialization seems part of node scheduling because it is converting from parallel to serial by *interleaving* the partial ordering of data dependences into a total ordering, taking into account tail-sharing. The data dependences are clearly a specification of "what to do next" *for each value*, and the total ordering is a specification of "what to do next" *with only a single program counter*. (Thus, that we need to interleave them at all, is a result of a machine-dependent characteristic—PDG sequentialization might be omitted on multicore architectures with lightweight fork-and-join mechanisms. Node Scheduling might then be used only to interleave multiple computations with identical control conditions, for which ILP suffices and thread-creation overhead may be avoided.)

<sup>&</sup>lt;sup>8</sup>Practical compilers might better be described as *ameliorating*.

However, PDG sequentialization also seems part of proceduralization, because it can be seen as part of the conversion from functional to procedural: it concerns the duplication *required* to encode (into any resulting CFG) an evaluation strategy. Moreover, many of the tasks performed by proceduralization concern themselves with the size of the output program *after* PDG sequentialization, and previous techniques for VSDG sequentialization have passed through a point equivalent to the *df-PDG*—this is useful for comparison purposes, covered in Chapter 4. (However, other techniques construct only restricted *treelike* PDGs, which are trivially duplication-free, and much of the power of our architecture comes from the ability to use more general df-PDGs.)

Thus, we find it neatest to leave PDG sequentialization as a separate phase.

### 2.4.3 A Fresh Perspective: Continuations

Much of the task of sequentialization relates to specifying *continuations*. One normally thinks of a continuation as a record of the calling context when making a procedure call (to an explicitly named procedure, using a direct jump, or indirectly to a function pointer), such that execution can resume there after the procedure completes; typically, the continuation is the return address, passed as an extra argument. However, as we saw in Section 2.2.4, each VSDG node implicitly stores a computation; and our approach of inlining calls to such procedures stores the return continuation in the CFG successor relation (one can see this as using the memory address of each copy to identify the "return continuation" after that call site).

- **In the VSDG** the nearest thing each node has to a continuation is the set of its consumers, i.e. the operations which *might* be performed on its value. However, this does not even make clear *which* of these consumers will ever execute in any program run.

- **In the PDG** group nodes add an additional level of specification: the continuation of a group node is to execute *all* of its children (in some order). Although still somewhat vague, this is more precise than the VSDG.

The effect of PDG sequentialization is to specify the continuations much more precisely, including specifying continuations for the statement nodes: when the children of a group node are totally ordered, each sibling's continuation is to go on to execute the next sibling<sup>9</sup>.

In the CFG each statement's continuation—"what to do next" after executing that statement is explicitly specified as its control flow successor<sup>10</sup>.

The perspective of continuations leads to two insights:

1. Whereas in PDG and VSDG, the (data) dependence edges specify *partial* orderings on sets of nodes (these can be seen as a set of continuations to be executed *in parallel*), imposing a *total ordering* (specified by a single continuation for each node, forming a chain to be executed *serially*) introduces the possibility that the "next" node in the ordering may not have been related by the partial order. That is (as in the CFG), the next node may not do anything with any value produced by the previous, but could merely perform some

<sup>&</sup>lt;sup>9</sup>For the final sibling, this is the next sibling of the next highest *ancestral* group node.

<sup>&</sup>lt;sup>10</sup>Branches have two continuations—one for true and one for false.

other computation which was placed afterwards arbitrarily or for some other reason. In this case, the two could have been interchanged in the total order, but this would have changed the continuation for each.

2. In both PDG and VSDG, nodes can have *multiple* continuations: in the VSDG, these correspond to program executions in which different subsets of the node's consumers will be evaluated; in the PDG, a node could have one continuation per parent group node (potentially all different, if each group node were to order its children independently). Contrastingly, in the CFG, each statement node stores *exactly one* continuation; hence, storing *i* distinct continuations for a node, requires *i* copies of that node in the CFG. A number of the optimization techniques we will see have the effect of reducing the number of distinct continuations identified for each node, and thus the number of copies of the stored procedure that are required.

**The Task of PDG Sequentialization** is to choose orderings such that nodes have few *distinct* continuations; duplication-freedom captures the condition under which each node has *exactly one* distinct continuation.

# 2.5 Definition of the PDG

A PDG consists of three kinds of nodes (below), and two kinds of edges: control dependence edges and data dependence edges. The *Control Dependence Graph* (CDG) is the subgraph consisting of all the nodes, and only the control dependence edges; the *Data Dependence Graph* (DDG) is the subgraph of all the nodes and only the data dependence edges. It is convenient to describe control dependence edges as pointing from parents to children, even though the CDG is not strictly treelike in that it may contain cross-links (and back-edges, creating cycles). The number of children depends upon the type of node:

- **Group Nodes** G, drawn as ovals, have multiple children  $(n \ge 0)$ ; execution of a group node entails execution of *all* its children, but in any (or an unspecified) order that respects the data dependence edges between them. While group nodes may have labels, these are not significant, being used merely for comments.

- **Predicate Nodes** P, Q, drawn as diamonds, have precisely two children: one for true and one for false. Execution of a predicate node entails execution of exactly one of its children, according to the runtime value of the predicate being tested, which is indicated by the node's label.

- **Statement Nodes** (or **Leaf Nodes**) *S*, drawn as rectangles, have no children, but each is labelled with an imperative three-address statement to execute.

Values are passed between statements (and to predicates) by storing them in variables; as in the CFG, SSA form may be used but is not generally a requirement<sup>11</sup>. Data dependence edges are used only to restrict possible orderings among statements (e.g. potentially due to antidependences as well as data dependences), and run between siblings of a group node. The DDG is acyclic even in the presence of program loops, but there may be cycles involving DDG as well as CDG edges in the whole PDG.

<sup>&</sup>lt;sup>11</sup>The PDG predates SSA form.

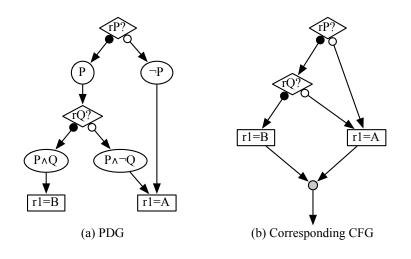

Figure 2.7: Shorthand for Children of Predicate Nodes in PDG

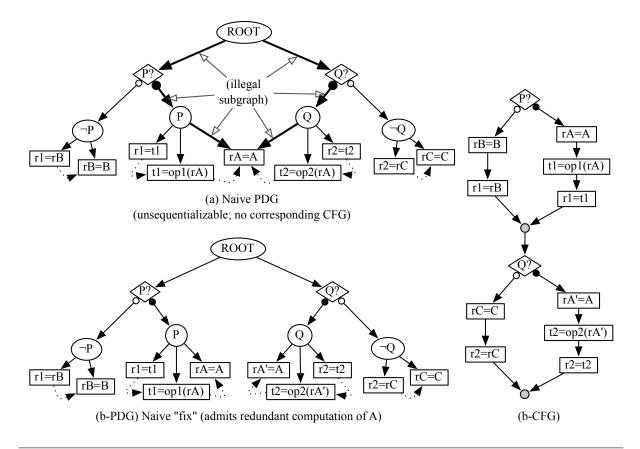

#### Figure 2.8: Forbidden CDG Subgraph

Note that graphically we indicate the true and false children of predicate nodes with filled and open dots, respectively, and sometimes draw multiple outgoing true or false edges rather than the single group node which must gather them together as a single child. These two shorthand notations are shown in Figure 2.7.

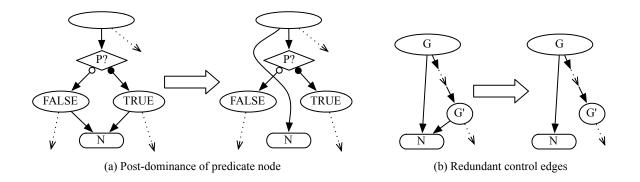

Several well-formedness constraints must be imposed to make a valid PDG. The first of these, which we refer to as *Ferrante-sequentializability*, is particularly important (and was discussed in Section 2.3): we require that the CDG part of the PDG must not contain subgraphs like Figure 2.8.

The remaining well-formedness constraints are easily enforced via transformations; thus, we treat these as being implicitly applied to any PDG:

- **Redundant Group Nodes** Whenever a group node G is a child of a group node G' but has no other parents besides G', it can be removed, and all its children made control dependent directly on G'.

- **Postdominance of Predicate Nodes** Whenever a node N is control dependent on both true and false group nodes of a single predicate P, it is said to *postdominate*<sup>12</sup> P. Ferrante et al. forbid the existence of such nodes [FMS88]. However, any such node can instead be made control dependent on P's parent, as shown in Figure 2.9(a). (If P has multiple parents  $G_1, \ldots, G_i$ , then a fresh group node can first be inserted as child of all the  $G_i$  and as unique parent of P).

- **Redundant Edges** Whenever a node N which is a child of a group node G, is also a child of another group node G' descending from G, the control dependence edge  $G' \rightarrow N$  can be removed. (The additional dependency serves no purpose, in that N will already necessarily be executed if G' is). This is shown in Figure 2.9(b).

<sup>&</sup>lt;sup>12</sup>The term is used loosely as a reference to the position of the resulting node in the CFG *after* sequentialization.

# 2.6 The VSDG: Definition and Properties

The VSDG is a directed labelled hierarchical Petri-net<sup>13</sup>  $G = (S, T, E, S_{in}, S_{out})$ , where:

- **Transitions** T represent operations, covered in Section 2.6.2. These may be *complex*, i.e. containing a distinct graph G'; this hierarchy is explained in Section 2.6.5.

- **Places** S represent the *results* of operations, covered in Section 2.6.1.