### Comparative Architectures

#### CST Part II, 16 lectures

Lent Term 2004

Ian Pratt

Ian.Pratt@cl.cam.ac.uk

OHP slides with extra notes for supervisors

#### **Course Outline**

- 1. Comparing Implementations

- Developments fabrication technology

- Cost, power, performance, compatibility

- Benchmarking

- 2. Instruction Set Architecture (ISA)

- Classic CISC and RISC traits

- ISA evolution

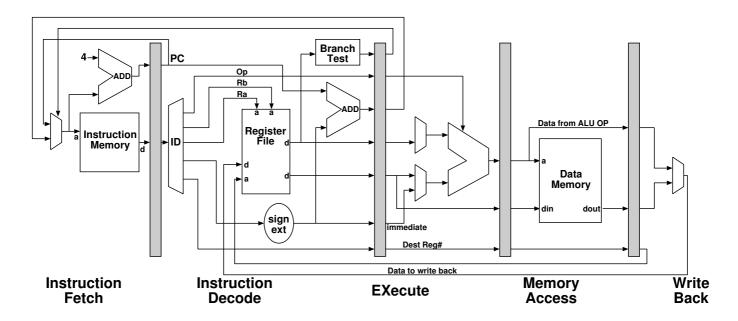

- 3. Microarchitecture

- Pipelining

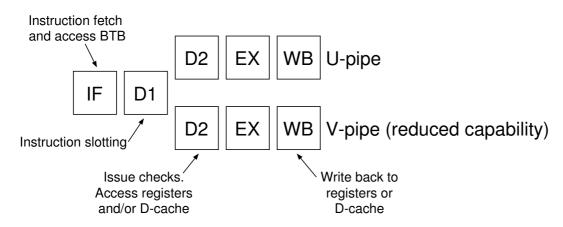

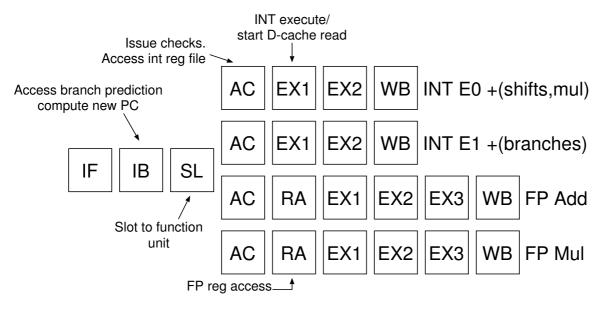

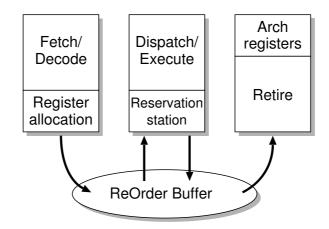

- Super-scalar

- static & out-of-order

- Multi-threading

- ullet Effects of ISA on  $\mu$ architecture and vice versa

- 4. Memory System Architecture

- Memory Hierarchy

- 5. Multi-processor systems

- Cache coherent and message passing

#### Understanding design tradeoffs

#### **Course Outline**

- 1. Instruction Set Architecture is the programmer-visible processor features.

- 2. ISA = Instruction Set Architecture, not Industry Standard Architecture (old PC I/O bus).

- 3. This course looks at processors and memory systems, not I/O.

- 4. Examines tradeoffs available to processor architects.

- 5. Every feature has costs. Some make chip more efficient, other less so.

- 6. Why you need to know this: even if not architect, comparing performance, optimisations under the hood easily factors of 10

- 7. How to make computers go fast, perhaps the sexiest part of computer science, atleast in my opinion

- 8. Don't get too bogged down in detail

- 9. But, some examples in essays are good.

- 10. This isn't all black and white. Many issues still undecided

- 11. Hard to compare the performance of architectures; depends on implementation. Depends on on how much money, fabrication technology, how smart..

#### Reading material

- OHP slides, articles

- Recommended Book:

John Hennessy & David Patterson,

Computer Architecture: a Quantitative Approach

(3rd ed.) 2002 Morgan Kaufmann

- The Web

```

http://bwrc.eecs.berkeley.edu/CIC/

http://www.chip-architect.com/

http://www.geek.com/procspec/procspec.htm

http://www.realworldtech.com/

http://www.anandtech.com/

http://www.arstechnica.com/

http://open.specbench.org/

```

- comp.arch News Group

- 1. 3rd ed. out soon

- 2. First few lectures, Notes for lecturer, not necessarily for you!

- 3. I intend to say a lot more than is on notes XX write on slides

- 4. Second part of notes in a couple of lectures time

- 5. will also be a version of the slides for supervisors, with additional notes to explain what I've said in lectures.

- 6. Active learning, not sitting falling asleep

- 7. Additional material in notes: don't need to understand it all

- 8. from the leaders of the RISC movement

- 9. each feature has a cost, quantitative technique to identify benefit and cost

- 10. CPU Info Center / Use Altavista

- 11. Paul De Mone's realworldtech articles are go

- 12. Lively discussion amongst knowledgeable people with the usual interjections by morons

## Further Reading and Reference

- M Johnson

Superscalar microprocessor design

1991 Prentice-Hall

- P Markstein

IA-64 and Elementary Functions

2000 Prentice-Hall

- A Tannenbaum,

Structured Computer Organization (2nd ed.)

1990 Prentice-Hall

- A Someren & C Atack, The ARM RISC Chip, 1994 Addison-Wesley

- R Sites,

Alpha Architecture Reference Manual,

1992 Digital Press

- G Kane & J Heinrich,

MIPS RISC Architecture

1992 Prentice-Hall

- H Messmer,

The Indispensable Pentium Book,

1995 Addison-Wesley

- Gerry Kane and HP, The PA-RISC 2.0 Architecture book, Prentice Hall

- 1. Course uses a range of architectures including x86,ARM,Alpha,MIPS,PowerPC,PA-RISC,IA-64,Transmeta and SPARC to illustrate points made

- 2. all ISA ref manuals are on web, available off Berkeley CPU Info Centre

#### Course Pre-requisites

- Computer Design (Ib)

- Some ARM/x86 Assembler

- Classic RISC pipeline model

- Load/branch delay slots

- Cache hierarchies

- Memory Systems

- Compilers (Ib/II)

- Code generation

- Linkage conventions

- Structured Hardware Design

- Critical paths

- Memories

- (Concurrent Systems)

- 1. Won't need these until next Tuesday, so time to brush up

## The Microprocessor Revolution

- Mainframe / Scalar Supercomputer

- CPU consists of multiple components

- performance improving at 20-35% p.a.

- often ECL or other exotic technology

- huge I/O and memory bandwidth

- Microprocessors

- usually a single CMOS part

- performance improving at 35-50% p.a.

- enabled through improvements in fabrication technology

- huge investment

- physical advantages of smaller size

- General Purpose Processors

- \* desktop / server

- \* SMP / Parallel supercomputers

- Embedded controllers / SoCs

- DSPs / Graphics Processors

## The Microprocessor Revolution

- 1. Scalar vs. Vector (SIMD) vs. Parallel (MIMD)

- 2. Many/some applications are unable to benefit from parallel processing, so fast scalar CPUs are still required

- 3. This course focuses on 'General Purpose' microprocessors and memory systems, e.g. as used in workstations

- 4. More I/O pins and specialist packaging techniques allow greater bandwidth for mainframe CPUs

- 5. Microprocessors have benefited over mainframe CPUs from greater financial investment, and from physical limits imposed by the speed of light benefiting smaller devices.

- 6. CMOS typically offers reduced time to market (more mature tools)

- 7. High performance embedded e.g. AMD 29K, ARM, Intel i960

- 8. Multiple embedded controllers in everything these days. 20+ in the average family car.

- 9. look at some of the technology advances that drive microprocessors

- 10. This course focuses on General Purpose CPUs and memory systems (rather than DSPs, embedded etc)

- 11. SoC: System on a Chip. Complete (simple) CPU (e.g. ARM) integrated with memory controller, peripherals and possibly even DRAM. (it is now possible to fabricate DRAM and logic on same die).

#### **Developments in CMOS**

- Fabrication line size reduction

- $-0.8\mu$ , 0.5, 0.35, 0.25, 0.18, 0.15, 0.13, 0.09

- 10-20% reduction p.a.

- switching delay reduces with line size

- → increases in clock speed

- \* Pentium 66Mhz @ 0.8 $\mu$ , 150Mhz @ 0.6 $\mu$ , 233MHz @ 0.35 $\mu$

- density increases at square of 1/line size

- Die size increases at 10-29% p.a.

- $\Rightarrow$  Transistor count increase at 55% p.a.

- enables architectural jumps

- 8, 16, 32, 64, 128 bit ALUs

- large caches

- \* PA-8500: 1.5MB on-chip

- new functional units (e.g. multiplier)

- duplicated functional units (multi-issue)

- whole System On a Chip (SoC)

#### **Developments in Technology**

- 1. See the Semiconductor Industry Association Technology Roadmap at the back of booklet. Historically, the predictions made by this document have been surpassed by the industry!

- 2. Disclaimer: past performance is not necessarily a good indicator to the the future....

- 3. (the value of stocks and shares can go up as well as down)

- 4. 'drawn line size' is the size of smallest drawn feature

- 5. drawn as opposed to effective (due to depletion) 25% difference

- 6. for comparison, wavelength of visible light is  $0.6\mu$

- 7. people have repeatedly predicted an end to line size reduction for years, but the technology just keeps improving... Quantum effects bellow  $0.1\mu$  may put an end to CMOS's progress. Will another technology be ready to take over over?

- 8. first 0.35 Pentium parts were 133MHz, process tweaking, 'stepping', and speed-grade binning has enabled 233. Pentium end of lined at 266MHz

- 9. 'stepping' is the name for creating new processor variants with minor changes e.g. to fix bugs or optimize a critical path.

- 10. continual performance leapfrogging of each of the different manufacturer's fab technology

- 11. But, wire propagation delay INCREASES with reduced line size. This is becoming increasingly a problem. IBM have developed a Cu (as opposed to AI) interconnect. 3D construction would be a better long-term solution.

- 12. PA-8500 will have greater than 150 million transistors—by far the vast majority of them will be in the huge 1.5MB L1 caches.

- 13. See the 'General Processor Information' sheet at back of booklet.

- 14. SoC means few components in a design, hence smaller, cheaper, lower power consumption.

# Developments in DRAM Technology

- DRAM density

- increases at 40-60% p.a.

- equivalent to 0.5-1 address bits p.a.

- cost dropping at same rate

- \* 16M, 64M, 256M, 1G

- Consequences for processor architectures:

- → May not be able to address whole of memory from a single pointer

- segmentation

- → May run out of physical address bits

- banked (windowed) memory

- DRAM performance

- just 35% latency improvement in 10 years!

- new bus interfaces make more sequential b/w available

- \* SDRAM, RAMBUS, DDR, DDR2

# Developments in DRAM Technology

- 1. Consume DRAM at same rate as development. Mainly due to software bloat.

- 2. Always pay \$200 for the 'standard' amount of ram in a PC. Now get over 256MB

- 3. 64Mb chips currently most common, but 256M chips ramping up. 1G chips working in the lab. SIA Roadmap says 256G in lab by 2012

- 4. High-end desktops are 256MB. Days of 32bit CPUS numbered? (PPro supports 36bit physical addresses, but only a 32bit flat addressing model)

- 5. segmentation: can't address all of memory in one go. Horrid.

- 6. banked memory: Switch between several banks of memory via some out-of-band signal. E.g. PC VGA cards/80286 Expanded Memory. Very, very horrid.

- 7. Fundamental density/latency tradeoff

- 8. New high clock rate synchronous interfaces (e.g. SDRAM,RAMBUS) enable much higher bandwidth to data in the same DRAM ROW.

- 9. SRAM is lower latency, but much more expensive (6T vs 1). Hence the need for caching.

- 10. CPU Memory gap widening, becoming more of a performance issue... (iRAM etc.)

# $\mu$ processor Development Cycle

- Fabrication technology has huge influence on power and performance

- → must use the latest fabrication process

- Full custom design vs. semi custom

- Keep development cycle short (3-4 years)

- Non CMOS technology leads to complications

- Advance teams to research:

- process characteristics

- key circuit elements

- packaging

- floor plan

- required performance

- microarchitecture

- investigate key problems

- Hope ISA features don't prove to be a handicap

- Keep up or die!

- Alpha architects planned for 1000x performance improvement over 25 years

# $\mu$ processor Development Cycle

- 1. The performance advantage of using ECL or GaAs is often squandered through extended time-to-market.

- 2. CPUs must be fabricated on a modern process to be competitive.

- 3. Intel/IBM beginning to get ahead of the competition on fab process introduction. (Having wads of cash to through at the problem helps...)

- 4. At the start of development, CPUs are being designed for a target manufacturing process that doesn't yet exist.

- 5. Most manufacturers aim to produce a new processor 'core' every 3 years (same 'P6' core in Pentium Pro, Pentium II and Pentium III). Pentium IV uses a new core. The core gets 'shrunk' for new fab processes, and may be tinkered with to optimise paths, add new instructions, or re-balance the cache hierarchy (usually increasing sizes of on-chip caches as die space becomes available).

- 6. Costs for each generation of chip are rising almost exponentially. New fab plant costs almost 5 billion dollars.

- 7. Ideally, architectures should be designed such that they contain no features that will hamper the ability of future implementations to make use of techniques enabled by developments in fabrication technology. This requires incredible foresight.

- 8. The Alpha architects, Sites and Witek, planned a 25 year life for Alpha, over which they expect to see a >1000x increase in performance. (10x on multiple issue, 10-100x on clock, 1-10x on thread level parallelism)

- 9. Many other architectures were not planned with so much forethought. They were optimal for the implementation at the time.

- 10. look at some of the reasons for choosing a given processor for a new product

#### **Power Consumption**

- Important for laptops, PDAs, mobile phones, set-top boxes, etc.

- 155W for Digital Alpha 21364 @ 1150MHz

- 130W for Itanium-2 @ 1500MHz

- 90W for AMD Opteron 148 @ 2GHz

- 81W for Pentium-IV @ 3GHz

- 12W for Intel Mobile Pentium M @ 1100Hz

- 420mW for Digital StrongArm @ 233MHz, 2.0V

- 130mW for Digital StrongArm @ 100MHz, 1.65V

- Smaller line size results in lower power

- lower core voltage, reduced capacitance

- greater integration avoids inter-chip signalling

- Reduce clock speed to scale power

- $-P = CV^2f$

- may allow lower voltage

- \* potential for cubic scaling

- \* better than periodic HALTing

#### Performance per Watt

### **Power Consumption**

- 1. increasingly important in some markets.

- 2. batteries wouldn't last too long in a palm top with a 21264!

- 3. Fan noise from set-top boxes would be a problem

- 4. Can dissipate up to about 100W in a desktop machine using heat pipes etc.

- 5. SIA Roadmap predicts 175W processors in 2012 (running on 0.6-0.9V)

- 6. Do need significant compute power in PDAs: handwriting recognition

- 7. Both SA and 21164 fabricated in Digital's  $0.35\mu m$  process. One designed for all out performance, the other for low power.

- 8. 'mobile processors' are often just 'under-clocked' desktop versions, possibly with L2 cache integrated on die to save inter-chip signalling power.

- 9. Sleep modes and clock frequency scaling to reduce power. (Some fully static components enable clock to be stopped)

- 10. Lowering supply voltage reduces power consumption but requires reduction of the operating clock speed. Power is proportional to V\*\*2, so can be very beneficial. This is what Transmeta do when there isn't enough work to warrant clocking the CPU at max.

- 11. Potential for cubic scaling, whereby a 10% reduction in clock frequency can produce a 27% reduction in power.

- 12. Need OS (or other s/w) to set CPU speed according to prevailing load. More effective than just halting CPU most instruction sets include an instruction that halts the processor until it is awoken by interrupts. OS sets the timer to wake the CPU up in so many milliseconds unless other IO activity wakes it beforehand.

#### **Cost and Price**

#### • E.g.:

- \$0.50: 8bit micro controller

- \$3: XScale (ARM) (400MHz,  $0.18\mu$ m, 20mm<sup>2</sup>, 2.1M[1M])

- \$500: Pentium IV Celeron (1.2GHz, 0.13 $\mu$ m, 131mm<sup>2</sup>, 28M[4M])

- \$150: Pentium IV (3.2GHz,  $0.09\mu m$ ,  $180mm^2$ , 42M[7M])

- \$2200: Itanium2 (1Ghz,  $0.18\mu\text{m}$ ,  $421\text{mm}^2$ , 221M[15M])

- Costs influenced by die size, packaging, testing

- Large influence by manufacturing volume

- Costs reduce over product life (e.g. 40% p.a.)

- Yield improves

- Speed grade binning

- Fab 'shrinks' and 'steppings'

- 1. logic vs. cache density. Figure in square brackets is number of core transistors.

- 2. Number of pins, packaging costs, memory bandwidth. Current BGA (solder Ball Grid Array) packages allow 600+pins. 3000 pins by 2012...

- 3. Need to recover R&D costs, and Fab Plant construction.

- 4. Design of a new CPU costs > 100M. > 150 people working for 3 years

- 5. Component prices aren't static, they reduce over product life, as much as factor of 10

- 6. Speed grade binning and marketing influence. Over clocking

- 7. 'Stepping': making minor changes to a design/layout to fix bugs and improve yield of higher frequency parts.

- 8. 'Shrink': Re-laying out a design for a new fab process.

### Compatibility

- 'Pin' Compatibility (second sourcing)

- Backwards Binary Compatibility

- 8086, 80286, 80386, 80486, Pentium,

Pentium Pro, Pentium II/III/IV, Itanium

- NexGen, Cyrix, AMD, Transmeta

- typically need to re-optimize

- Typically hard to change architecture

- Users have huge investment in s/w

- Binary translators e.g. FX!32, WABI

- \* typically interface to native OS

- Need co-operation from s/w vendors

- \* multi-platform support costs \$'s

- Most computer sales are upgrades

- Platform independence initiatives

- Source, p-Code, JAVA bytecode, .NET

#### Compatibility is very important

#### Compatibility

- 1. pin compatible: use same motherboard. (Though Intel have patented slot-1)

- 2. AMD K-7 uses 'Slot A', the first x86 clone NOT to be pin compatible with Intel.

- 3. Need to persuade s/w vendors to optimise their products for CPU. e.g. the Pentium IV has an entirely new set of FP instructions. Software flies if you use them, but performs horribly if you use the old 8087 instructions.

- 4. WABI is an x86 emulator available for a number of workstation platforms. FX!32 is Digital's x86 to Alpha binary translator.

- 5. binary2binary translators: hard to get software vendor to support translated product.

- 6. Transmeta's approach is to translate ALL software (including the OS) rather than just the applications. This makes sense because the x86 interface is MUCH simpler and better specified than the Windows API. Products such as Wine and FX!32 might theoretically offer better performance through native implementation of OS and API code, but keeping track of MS developments of the API is very difficult...

- 7. binary2binary optimisers: re-write old binary to produce an optimised one. Used by Digital to optimise Alpha NT versions of MS products that were compiled with a lousy compiler.

- 8. Changing arch e.g. Sun/HP/Apple from 68k, DEC from VAX and MIPS. Often loose customers.

- 9. Will we see Java bytecode / .NET versions of MSWord? How will they perform? I believe they could actually perform better, after some good virtual machine research...

#### Performance Measurement

- Try before you buy! (often not possible)

- System may not even exist yet

- use cycle-level simulation

- Real workloads often hard to characterize and measure improvements

- especially interactive

- Marketing hype

- MHz, MIPS, MFLOPS

- Algorithm kernels

- Livermore Loops, Linpack

- Synthetic benchmarks

- Dhrystones, Whetstones, iCOMP

- Benchmark suites

- SPEC-INT, SPEC-FP, SPEC-HPC, NAS

- Application Benchmarks

- TPC-C/H/R, SPECNFS, SPECWeb, Quake

## Performance is application dependent

#### Performance Measurement

- 1. Performance is often not particularly critical

- 2. Often not possible to try application: live system or no optimized binary available

- 3. desktop workloads are especially difficult: highly varied, idle much of the time, response time is important

- 4. cycle level simulators exist for CPUs long before they're actually fabbed. Need a good memory system model too.

- 5. simulate the 'kernel' (inner most loops) of important applications

- 6. fallacies of using MHz: 450MHz Alpha 21164 = 180MHz HP PA-8000

- 7. fallacies of using MIPS: Rarely able to occupy all functional units to achieve peak MIPS performance. PA-8000 better at doing this than Alpha 21164

- 8. livermore loops: good if that's your application, won't tell you much about anything else. (Livermore loops are an FP intensive algorithm that forms part of Gaussian elimination)

- 9. synthetic benchmarks: derived from instruction traces of real apps. They are usually too small, don't reward real compiler optimizations, and allow unrealistic ones.

- 10. eg. dhystone: 25%discarded by optimizing compiler. Function inlining had to be forbidden to enable 'fair' comparison.

- 11. whetstone: trick optimization sqrt(exp(x)) = exp(x/2)

- 12. NAS is a benchmark suite for HPC applications. It's interesting in that its a set of algorithms that you can implement however you like. (With SPEC-HPC you can't change the Fortran source) NAS is more realistic to how Supercomputers are actually used.

- 13. Application performance is not dependent on just the CPU performance, but on the compiler and memory system too.

- 14. Application performance may also depend on IO e.g. graphics, disk, network performance

- 15. TPC-C for transaction processing systems, TPC-D for 'decision support' database mining.

#### Standard Performance Evaluation Corporation

- SPEC is most widely used benchmark

- processor manufactures

- workstation vendors

- CPU INT / FP 89, 92, 95, 2000, (2004)

- Suite updated to reflect current workloads

- CINT95/2K: 8/12 integer C programs

- CFP95/2K: 10/14 floating point in C&Fortran

- measures:

- processor

- memory system

- compiler

- NOT OS, libc, disk, graphics, network

- 1. SPEC so important that it used to provide input into CPU design

- 2. SPEC-98 due to ship in '99.

- 3. execution time in non SPEC supplied code is minimal (i.e. not OS or libc)

- 4. disk, video, network performance can be very important—the CPU is often not the bottleneck.

- 5. Video performance has an important effect on how fast a system 'feels'.

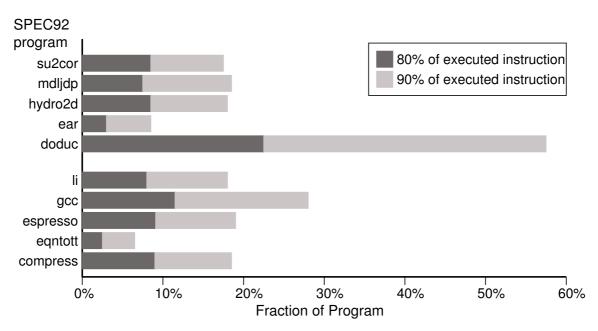

# Choosing programs for SPEC2000

- More programs than SPEC95

- Bigger programs than SPEC95

- Don't fit in on-chip caches

- Reflect some real workloads

- Run for several minutes

- Amortize startup overhead & timing inaccuracies

- Not susceptible to trick transformations

- Vendors invest huge s/w effort

- Fit in 256MB (95 was 64MB)

- Moving target...

- SPEC92, 95, 2K results not translatable

- 1. SPEC2000 very new only a few results available

- 2. 5K dollar bounty for submitting applications

- 3. one of the SPEC92 programs was susceptible to a trick transformation

- 4. huge amount of effort goes into SPEC benchmarks by vendors

- 5. compiler optimization some may even be useful for real progs!

- 6. I&D trace data, processors designed to execute SPEC

- 7. multiple submissions for same machine as compilers improve

- 8. Fit in 64MB: Becoming too small to really stretch modern workstation memory systems.

- 9. no simple relationship between SPEC 92 and 95 numbers 95 more demanding on memory systems.

#### CINT95 suite (C)

An AI go-playing program 099.qo A chip simulator for the Motorola 88100 124.m88ksim Based on the GNU C compiler version 2.5.3 126.gcc 129.compress An in-memory version of the utility 130.li Xlisp interpreter 132.ijpeg De/compression on in-memory images 134.perl An interpreter for the Perl language An object oriented database 147.vortex

#### CFP95 suite (Fortran)

Vectorized mesh generation 101.tomcatv 102.swim Shallow water equations 103.su2cor Monte-Carlo method 104.hydro2d Navier Stokes equations 107.mgrid 3d potential field Partial differential equations 110.applu Turbulence modelling 125.turb3d 141.apsi Weather prediction 145.fpppp Quantum chemistry 146.wave5 Maxwell's equations

#### CINT95 suite (C)

- 1. Considerable effort goes into selecting programs for SPEC. They are all (modified) real applications; Applications that someone, somewhere cares about the performance of.

- 2. 126.gcc cross compiles number of programs for SUN, not native

- 3. Jpeg and Gcc have large data sets, which do exercise filesystem I/O (eg. 13% worse over NFS, 5% better with RAM disk)

- 4. Which of these apps represent my workload? What will SPEC say about the performance of emacs, Netscape, MS Word, Quake?

### **SPEC** reporting

- Time each program to run

- Reproduceability is paramount

- Take mean of  $\geq$  3 runs

- Full disclosure

- Baseline measurements

- SPECint base95

- Same compiler optimizations for whole suite

- Peak measurements

- SPECint95

- Each benchmark individually tweaked

- Unsafe optimizations can be enabled!

- Rate measurements for multiprocessors

- SPECint\_rate95, SPECfp\_rate95

- time for N copies to complete x N

#### **SPEC** reporting

- 1. Take median of string of results

- 2. full disclosure: OS and compiler versions, system configuration

- 3. compiler and system must be for sale to be official

- 4. peak results: great long lists of cryptic compiler flags

- 5. base results: more likely what a real user would get

- 6. unsafe optimizations: but, must be correct for any input data set

- 7.  $\rightarrow$  Intel accidently cheated on one of the fp benchmarks, producing code that wouldn't work for all possible datasets.

- 8. SPECrate: copies run\*reference\*seconds in day / elapsed time=rate in jobs/day

- 9. SPECrate: important for batch processing systems

### **Totalling Results**

- How to present results?

- Present individual results?

- Arithmetic mean?

- Weighted harmonic mean?

- SPEC uses Geometric mean, normalised against a reference platform

- \* allows normalization before or after mean

- performance ratio can be predicted by dividing means

- SPEC95 uses Sun SS10/40 as reference platform

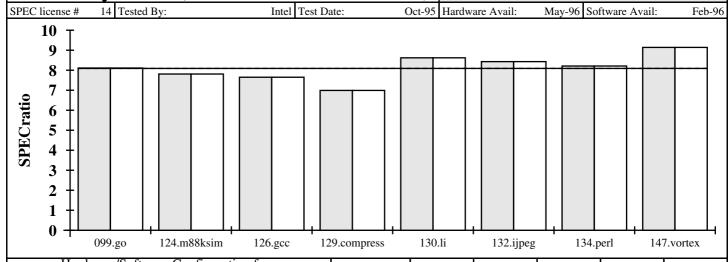

### SPEC CINT95 Results ©Copyright 1995, Standard Performance Evaluation Corporation

**Intel Corporation** Alder System (200MHz, 256KB L2) SPECint95 8.09

SPECint base95 = 8.09

| Hardware/Software Configuration for: Alder System (200MHz, 256KB L2) |                                                                          | Benchmark<br># and Name | Reference<br>Time | Base<br>Run Time | Base<br>SPEC Ratio | Run Time | SPEC Ratio |

|----------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------|-------------------|------------------|--------------------|----------|------------|

| Model Name:                                                          | <b>Hardware</b><br>Alder                                                 | 099.go                  | 4600              | 567              | 8.11               | 567      | 8.11       |

| CPU:                                                                 | 200MHz Pentium Pro Processor                                             | 124.m88ksim             | 1900              | 243              | 7.81               | 243      | 7.81       |

| FPU: Number of CPU(s):                                               |                                                                          | 126.gcc                 | 1700              | 222              | 7.65               | 222      | 7.65       |

| Primary Cache:<br>Secondary Cache:                                   |                                                                          |                         | 1800              | 258              | 6.99               | 258      | 6.99       |

| Other Cache: Memory:                                                 | ner Cache: None emory: 128MB (60ns fast page) sk Subsystem: 2GB ST32550W | 130.li                  | 1900              | 220              | 8.62               | 220      | 8.62       |

| Disk Subsystem:                                                      |                                                                          | 132.ijpeg               | 2400              | 285              | 8.43               | 285      | 8.43       |

| Other Hardware:                                                      |                                                                          | 134.perl                | 1900              | 232              | 8.21               | 232      | 8.21       |

| Operating System:                                                    | UnixWare 2.0, SDK                                                        | 147.vortex              | 2700              | 295              | 9.14               | 295      | 9.14       |

| Compiler:<br>File System:                                            | Intel C Reference Compiler 2.2 Beta ufs, vxfs (/tmp as 8MB /tmpfs)       | SPECint_base            | 95 (G. Mea        | n)               | 8.09               |          |            |

| System State:                                                        | Single user (root + killall)                                             |                         |                   | SPECint95        | (G. Mean)          |          | 8.09       |

#### **Notes/Tuning Information**

Base and non-base flags are the same and use Feedback Directed Optimization

Pass1: -tp p6 -ipo -xi -prof\_gen -ircdb\_dir /tmp/IRCDB

Pass2: -tp p6 -ipo -xi -prof\_use -ircdb\_dir /tmp/IRCDB

-ircdb\_dir is a location flag and not an optimization flag

Portability: 124: -DSYSV -DLEHOST 130, 134, 147: -lm 132: -DSYSV 126: -lm -lc -L/usr/ucblib -lucb -lmalloc

Memory subsystem is four-way interleaved.

For More Information Contact:

**SPEC** 10754 Ambassador Drive, Suite 201 Manassas, VA 22110 (703) 331-0180 info@specbench.org http://www.specbench.org

Volume: 7 Issue: 4

- 1. full disclosure of machine / compiler configuration

- 2. compiler options used

- 3. Feedback Directed Optimization. Optimization pass uses the SPEC95 Training input set - not allowed to use the Reference input set for training.

- 4. Base SPEC ratio = Ref time / Base run time

- 5.  $SPECint\_base = (r1*r2*r3...r8)**1/8$

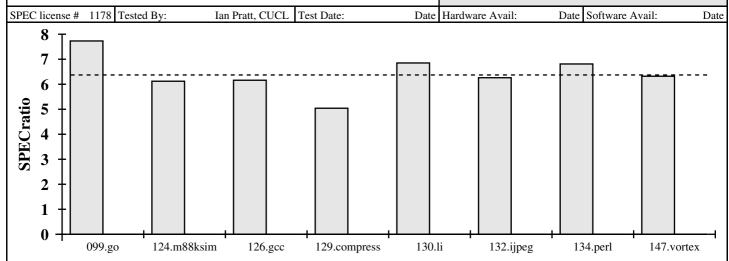

### SPEC CINT95 Results ©Copyright 1995, Standards Performance Evaluation Corporation

Intel 440LX motherboard Pentium Pro 200

SPECint95 = --

$SPECint_base 95 = 6.37$

| Hardware/Software Configuration for:<br>Pentium Pro 200 |                                  | Benchmark<br># and Name | Reference<br>Time | Base<br>Run Time | Base<br>SPEC Ratio | Run Time | SPEC Ratio |

|---------------------------------------------------------|----------------------------------|-------------------------|-------------------|------------------|--------------------|----------|------------|

| Model Name:                                             | Hardware<br>Intel 440LX          | 099.go                  | 4600              | 595              | 7.73               |          |            |

| CPU:<br>FPU:                                            | Pentium Pro 200                  | 124.m88ksim             | 1900              | 310              | 6.12               |          |            |

| Number of CPU(s)                                        |                                  | 126.gcc                 | 1700              | 276              | 6.16               |          |            |

| Primary Cache: Secondary Cache:                         | 8KB+8KB<br>256KB<br>128MB<br>4GB | 129.compress            | 1800              | 357              | 5.04               |          |            |

| Other Cache:<br>Memory:                                 |                                  | 130.li                  | 1900              | 277              | 6.85               |          |            |

| Disk Subsystem:<br>Other Hardware:                      |                                  | 132.ijpeg               | 2400              | 384              | 6.26               |          |            |

| Other Hardware.                                         | Software                         | 134.perl                | 1900              | 279              | 6.81               |          |            |

| Operating System:                                       | Linux 20.0.30                    | 147.vortex              | 2700              | 427              | 6.32               |          |            |

| Compiler:<br>File System:                               | gcc 2.7.2p<br>ext2<br>multiuser  | SPECint_base            | 95 (G. Mea        | n)               | 6.37               |          |            |

| System State:                                           |                                  | SPECint95 (G. Mean)     |                   |                  |                    |          |            |

#### **Notes/Tuning Information**

Portability flags were:

Baseline flags were: -02 -fomit-frame-pointer

Nonbase flags were:

For More Information contact SPEC c/o NCGA 2722 Merrilee Drive, Suite 200 Fairfax, VA 22031 (703) 698-9604 ext 318 spec-ncga@cup.portal.com

Prepared By: --

| <ol> <li>Compiler does make a difference:<br/>than the Intel reference compiler s</li> </ol> |  |

|----------------------------------------------------------------------------------------------|--|

|                                                                                              |  |

|                                                                                              |  |

|                                                                                              |  |

|                                                                                              |  |

|                                                                                              |  |

### CINT2000 Result

**Compaq Computer Corporation** AlphaServer ES40 Model 6/833

544 SPECint2000 = SPECint\_base2000 = 518

| SPEC license #: 2 | Tested by:        |                 | Compaq        | NH Test date: |       | Oct-2000 Hardware Avail: | Jan-2001 Softwa | are Avail: | Nov-2000 |

|-------------------|-------------------|-----------------|---------------|---------------|-------|--------------------------|-----------------|------------|----------|

| Benchmark         | Reference<br>Time | Base<br>Runtime | Base<br>Ratio | Runtime       | Ratio | 200                      | 400             | 600        | 800      |

| 164.gzip          | 1400              | 358             | 392           | 357           | 393   |                          | == ::           |            |          |

| 175.vpr           | 1400              | 309             | 452           | 307           | 456   |                          |                 |            |          |

| 176.gcc           | 1100              | 178             | 617           | 160           | 687   |                          |                 |            |          |

| 181.mcf           | 1800              | 408             | 441           | 340           | 529   |                          |                 |            |          |

| 186.crafty        | 1000              | 144             | 694           | 157           | 637   |                          |                 |            | 1        |

| 197.parser        | 1800              | 500             | 360           | 409           | 440   |                          |                 |            |          |

| 252.eon           | 1300              | 202             | 645           | 202           | 644   |                          |                 |            |          |

| 253.perlbmk       | 1800              | 342             | 526           | 332           | 543   |                          | 9               |            |          |

| 254.gap           | 1100              | 301             | 365           | 303           | 363   |                          | ∃               |            |          |

| 255.vortex        | 1900              | 282             | 673           | 249           | 763   |                          |                 |            |          |

| 256.bzip2         | 1500              | 268             | 560           | 264           | 568   |                          |                 |            |          |

| 300.twolf         | 3000              | 456             | 658           | 451           | 666   |                          | -               |            |          |

Hardware

CPU: Alpha 21264B

CPU MHz: 833

FPU: Integrated

CPU(s) enabled: CPU(s) orderable: 1 to 4

Parallel: No

Primary Cache: 64KB(I)+64KB(D) on chip

Secondary Cache: 8MB off chip

L3 Cache: None Other Cache: None Memory: 16**GB**

1x8GB BD0096349A Disk Subsystem:

Other Hardware: Ethernet

#### **Software**

Operating System: Tru64 UNIX V5.1 + Patch Kit 1 libc

Compaq C V6.3-129-44A8I Compiler: Compaq C++ V6.2-033-4298H

AdvÊS File System: System State: Multi-user

**Notes/Tuning Information**

Baseline C : cc -arch ev6 -fast GEMFB C++: cxx -arch ev6 -O2 ONESTEP

fdo\_pre0 = mkdir /tmp/pb; rm -f /tmp/pb/\${baseexe}\*

PASS1\_CFLAGS = -prof\_gen\_noopt -prof\_dir /tmp/pb GEMFB: fdo\_pre0 PASS2 CFLAGS = -prof use feedback -prof dir /tmp/pb

(base uses directory /tmp/pb; peak uses /tmp/pp)

SPIKEFB: fdo\_post2 = spike -feedback \${baseexe} -o tmp \${baseexe};

mv tmp \${baseexe}

Peak: cc [except eon: cxx] -arch ev6 ONESTEP plus:

164.gzip: -g3 -fast -O4 +GEMFB 175.vpr: -g3 -fast -O4 +GEMFB

176.gcc: -g3 -fast -O4 -xtaso\_short +GEMFB

181.mcf: -g3 -fast -xtaso\_short +GEMFB 186.crafty: -g3 -fast -O4 -inline speed

197.parser: -g3 -fast -O4 -xtaso\_short +GEMFB

252.eon: -02

253.perlbmk: -g3 -fast +GEMFB +SPIKEFB 254.gap: -g3 -fast -O4 +GEMFB

Standard Performance Evaluation Corporation info@spec.org http://www.spec.org

|    | Peak results   |            |             |    | base. | Note the |

|----|----------------|------------|-------------|----|-------|----------|

| 11 | nuge list of ( | Joagy Comp | oner option | 5. |       |          |

|    |                |            |             |    |       |          |

|    |                |            |             |    |       |          |

|    |                |            |             |    |       |          |

|    |                |            |             |    |       |          |

|    |                |            |             |    |       |          |

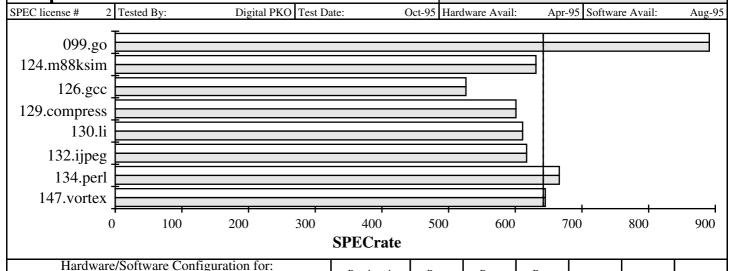

### SPEC CINT95 rate Results @Copyright 1995, Standard Performance Evaluation Corporation

Digital Equipment Corp. AlphaServer 8400 5/300

AlphaServer 8400 5/300

SPECint\_rate95 = 642 SPECint\_rate\_base95 = 642

| Alphaserver 6400 37300                         |                                                                     | # and Name    | Copies   | Run Time | SPEC Ratio | Copies  | Run Time | SPEC Ratio |

|------------------------------------------------|---------------------------------------------------------------------|---------------|----------|----------|------------|---------|----------|------------|

| CPU:                                           | Hardware<br>AlphaServer 8400 5/300<br>300 MHz 21164<br>Integrated   | 099.go        | 10       | 464      | 891        | 10      | 464      | 891        |

|                                                |                                                                     | 124.m88ksim   | 10       | 271      | 631        | 10      | 271      | 631        |

| Number of CPU(s): Primary Cache:               | 8KBI+8KBD on chip                                                   | 126.gcc       | 10       | 291      | 526        | 10      | 291      | 526        |

| Secondary Cache:<br>Other Cache:               | 4MB<br>none                                                         | 129.compress  | 10       | 270      | 601        | 10      | 270      | 601        |

| Memory:<br>Disk Subsystem:                     | 1 x 2GB                                                             | 130.li        | 10       | 280      | 611        | 10      | 280      | 611        |

| Other Hardware:                                |                                                                     | 132.ijpeg     | 10       | 350      | 617        | 10      | 350      | 617        |

|                                                |                                                                     | 134.perl      | 10       | 257      | 666        | 10      | 257      | 666        |

| Operating System:<br>Compiler:<br>File System: | Software Digital UNIX V3.2C (Rev 148) DEC C V5.0-106 UFS Multi User | 147.vortex    | 10       | 377      | 645        | 10      | 377      | 645        |

|                                                |                                                                     | SPECint_rate_ | base95 ( | G. Mean) | 642        |         |          |            |

| System State:                                  |                                                                     |               |          | SPECint_ | rate95 (G  | . Mean) |          | 642        |

Benchmark

Base

Base

Base

#### **Notes/Tuning Information**

Baseline Optimizations: -05 -ifo -non\_shared -om

Portibility Flags: 124.m88ksim: -DLEHOST 134.perl: -DI\_TIME

147.vortex: -D\_\_\_RISC\_64\_\_

Compiler invokation: cc -migrate -std1 (DEC C with -std1 for strict ANSI)

For More Information Contact: SPEC 10754 Ambassador Drive, Suite 201 Manassas, VA 22110 (703) 331-0180 info@specbench.org http://www.specbench.org

94 Volume: 7 Issue: 4

- 1. Running 10 copies on a 10 CPU machine

- 2. Base SPEC ratio = copies run\*reference\*seconds in day / elapsed time (=rate in jobs/day)

### Top SPEC2000 Results for each ISA

| machine        | processor    | cpu MHz | cache sizes       | int  | fp   |

|----------------|--------------|---------|-------------------|------|------|

| Intel D875     | Pentium IV-X | 3200    | 12*/8+256+2M      | 1620 | 1516 |

| AMD/ASUS       | Opteron148   | 2200    | 64/64+1M          | 1477 | 1514 |

| Intel D875     | Pentium IV   | 3200    | 12*/8+512         | 1330 | 1287 |

| HP rx2600      | Itanium2     | 1500    | 16/16+256+6M      | 1322 | 2119 |

| IBM p690       | Power4+      | 1700    | 64/32+1.5M+(128M) | 1113 | 1699 |

| HP Alpha ES45  | 21264C       | 1250    | 64/64+(16M)       | 928  | 1482 |

| Fujitsu        | SPARC64-V    | 1350    | 128+128/2M        | 905  | 1340 |

| Apple          | PPC970 (G5)  | 2000    | 64/32+512         | 800  | 840  |

| HP             | Pentium-M    | 1000    | 32/32+1024        | 687  | 552  |

| HP c3750       | PA-8700      | 875     | 768/1.5M          | 678  | 674  |

| SGI Orgin 3200 | R14000       | 600     | 32/32+(8M)        | 500  | 529  |

| HP rx4610      | Itanium      | 800     | 16/16+96+(4M)     | 379  | 701  |

#### **SPEC 95 Results**

- 1. cache sizes L1-I/L1-D + L2 + L3

- 2. First part of table shows current top scores for a range of CPUs and architectures. Notice how some RISC chips are beginning to fall behind...

- 3. although a uniprocessor benchmark, some auto-parallelizing compilers manage to reaps benefits from multiple CPUs

- 4. futility of MHz, even MIPS or FLOPS: compare PA8000 @180 and 21164 @400, or Pentium @200 and PPro @200

- 5. "Speed demons vs brainiacs": PA8000 gets better utilization from its 2 integer pipelines, and executes more expressive instructions than Alpha.

- 6. For a given processor core, SPEC does scale reasonably with MHz, providing Memory b/w is scaled comparably.

- 7. Note lousy x86 FP performance...

Selected SPEC95 Results

|                | CCCCG .    | <u> </u> | <u> </u>    |          |         |

|----------------|------------|----------|-------------|----------|---------|

| machine        | processor  | cpu MHz  | cache sizes | int_base | fp_base |

| Sun SS10/40    | SuprSP     | 40       | 20/16       | 1.00     | 1.00    |

| Intel 440BX    | Pentium II | 300      | 16/16+(512) | 12.2     | 8.4     |

| Intel 440EX    | Celeron A  | 300      | 16/16+128   | 11.3     | 8.3     |

| Intel 440EX    | Celeron    | 300      | 16/16       | 8.3      | 5.8     |

| Compaq PC164LX | 21164      | 533      | 8/8+96+(4M) | 16.8     | 20.7    |

| Compaq PC164SX | 21164PC    | 533      | 16/16+(1M)  | 12.2     | 14.1    |

| Intel 440BX    | Pentium II | 450      | 16/16+(512) | 17.2     | 11.8    |

| Intel 440BX    | Pentium II | 400      | 16/16+(512) | 15.8     | 11.4    |

| Intel 440BX    | Pentium II | 350      | 16/16+(512) | 13.9     | 10.2    |

| Intel 440BX    | Pentium II | 330      | 16/16+(512) | 13.0     | 8.8     |

| Intel 440BX    | Pentium II | 300      | 16/16+(512) | 11.9     | 8.1     |

| Intel 440BX    | Pentium II | 266      | 16/16+(512) | 10.7     | 7.5     |

| Intel 440BX    | Pentium II | 233      | 16/16+(512) | 9.4      | 6.7     |

| DEC 4100/5/400 | A21164     | 400/75   | 8/8+96+4M   | 10.1     | 16.0    |

| DEC 4100/5/400 | 2xA21164   | 400/75   | 8/8+96+4M   | 10.1     | 20.7    |

| DEC 4100/5/400 | 4xA21164   | 400/75   | 8/8+96+4M   | 10.1     | 26.6    |

| Intel XXpress  | Pentium    | 200      | 8/8+1M      | 5.47     | 2.92    |

| Intel Alder    | PentPro    | 200      | 8/8+256     | 8.09     | 5.99    |

#### **SPEC 95 Results**

- 1. cache sizes L1-I/L1-D + L2 + L3

- 2. First part of table shows current top scores for a range of CPUs and architectures. Notice how some RISC chips are beginning to fall behind...

- 3. although a uniprocessor benchmark, some auto-parallelizing compilers manage to reaps benefits from multiple CPUs

- 4. futility of MHz, even MIPS or FLOPS: compare PA8000 @180 and 21164 @400, or Pentium @200 and PPro @200

- 5. "Speed demons vs brainiacs": PA8000 gets better utilization from its 2 integer pipelines, and executes more expressive instructions than Alpha.

- 6. For a given processor core, SPEC does scale reasonably with MHz, providing Memory b/w is scaled comparably.

- 7. Note lousy x86 FP performance...

# Comparing Implementations Summary

- Fabrication technology has a huge influence

- Exponential improvement in technology

- Processor for a product chosen on:

- Instruction Set Compatibility

- Power Consumption

- Price

- Performance

- Performance is application dependent

- Avoid MIPS, MHz

- Benchmark suites

- Processor s/w interface

- Externally visible features

- Word size

- Operation sets

- Register set

- Operand types

- Addressing modes

- Instruction encoding

- Introduction of new ISAs now rare

- ISAs need to last several generations of implementation

- How do you compare ISAs ?

- yields 'best' implementation

- \* performance, price, power

- \* are other factors equal?

- 'aesthetic qualities'

- \* 'nicest' for systems programmers

- 1. In the early days, new architectures were introduced on a regular basis. Today, after IA-64 we're unlikely to see the introduction of another main-stream architecture for some time.

- 2. difficult to quantitatively compare the effects of architecture upon implementation: Different implementations have different goals, different amounts of money spent on them, different people etc.

- 3. From time to time you may have to open a processor user manual in order say, to write compiler back end, optimize some code

- 4. ARM and Thumb, PPRO architecture volume, Alpha Arch volume Hold up PPro 3 volumes, daunting, complexity, only describes what it does, not how!

- 5. This section describes hoe to find your way around a processor User Manual, which sections to look at first

- 6. many of you will have only seen the ARM e.g. of what's called a 3 operand, load/store, general purpose register architecture

- 7. Tour of instrs, regs and addressing modes found in common archs

- 8. Look at the RISC decisions

- New implementations normally backwards compatible

- Should execute old code correctly

- Possibly some exceptions e.g.

- \* Undocumented/unsupported features

- \* Self modifying code on 68K

- May add new features e.g. FP, divide, sqrt, SIMD, FP-SIMD

- May change execution timings

- − → CPU specific optimization

- Can rarely remove features

- \* Unless never used

- \* software emulation fast enough

- → Layers of architectural baggage

- \* (8086 16bit mode on Pentium IV)

- Architecture affects ease of utilizing new techniques e.g.

- Pipelining

- Super-scalar (multi-issue)

- But x86 fights real hard!

- more T's tolerable unless on critical path

- 1. 68030 separate I and D cache broke self modifying code.

- 2. PPro still has to execute self modifying code correctly Too many old x86 programs rely on it

- 3. Can't remove features, but it may be acceptable to make them run slowly e.g. 16 bit mode on the PPro - MS assured Intel that the majority of code would be 32bit. At the time of the PPro's launch, this probably wasn't true...

- 4. utilizing new techniques made available by more transistors

- 5. older CISC architectures not ideal for pipelining -¿ more gates and gate delays

- 6. Super-scalar processors attempt to issue multiple instructions per cycle from a single threaded (scalar) program.

- 7. RISC was designed to fully utilize pipelining, but some RISC architectures made decisions which make super-scalar implementation slightly tricky

- 8. x86 (IA-32) wasn't designed to utilize these techniques, but has succeeded in doing so pretty well just through transistors at the problem.

- 9. Mike Johnson head of AMD K6 design team: The x86 isn't all that complex it just doesn't make a lot of sense. No show stoppers, just lots of special cases.

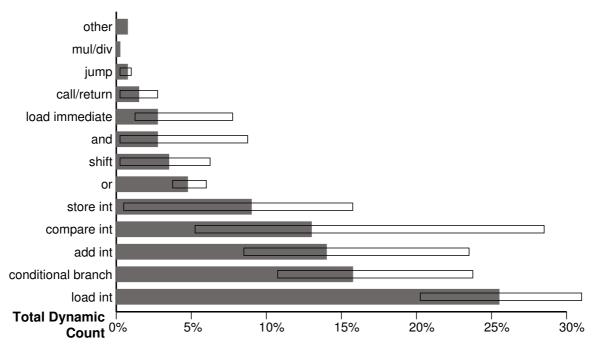

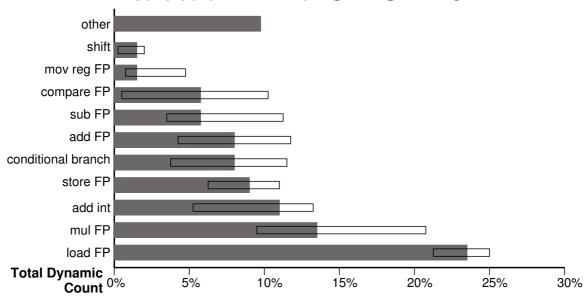

# Reduced Instruction Set Computers

- RISC loosely classifies a number of Architectures first appearing in the 80's

- Not really about reducing number of instructions

- Result of quantitative analysis of the usage of existing architectures

- Many CISC features designed to eliminate the 'semantic gap' were not used

- RISC designed to easily exploit:

- Pipelining

- \* Easier if most instructions take same amount of time

- Virtual Memory (paging)

- \* Avoid tricky exceptional cases

- Caches

- \* Use rest of Si area

- Widespread agreement amongst architects

- 1. Can be dangerous grouping architectures into CISC and RISC. Within each classification there are wide differences

- 2. semantic gap: 1970's, loop constructs, list and bit-field operators, procedure calls (these investigated further later on)

- 3. pre RISC, there was wide diversity in architecture. Even very new architectures have firm RISC-like foundations. e.g. IA-64

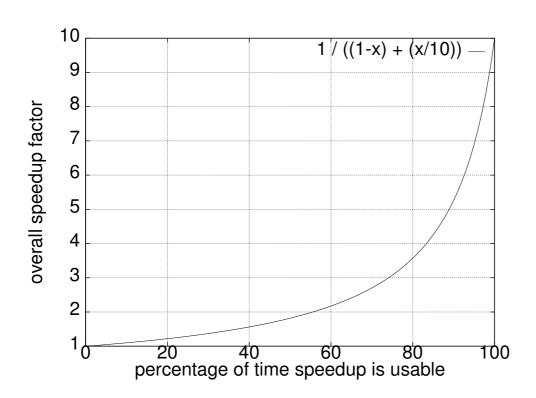

#### Amdahl's Law

- Every 'enhancement' has a cost:

- Would Si be better used elsewhere?

- \* e.g. cache

- Will it slow down other instructions?

- \* e.g. extra gate delays on critical path

- \* → longer cycle time

- Even if it doesn't slow anything else down, what overall speedup will it give?

- size and delay

$speedup = rac{execution \ time \ for \ entire \ task \ without \ using \ enhancement}{execution \ time \ for \ entire \ task \ using \ enhancment \ when \ possible}$

1. using enhancement when possible

#### Amdahl's Law:2

- How frequently can we use enhancement?

- examine instruction traces e.g. SPEC

- will code require different optimization?

- Fraction<sub>enhanced</sub>

- When we can use it, what speedup will it give?

- Speedup<sub>enhanced</sub>

- e.g. cycles before/cycles after

$$Speedup_{overall} = \frac{1}{(1 - Fraction_{enhanced}) + \frac{Fraction_{enhanced}}{Speedup_{enhanced}}}$$

## → Spend resources where time is spent

#### Optimize for the common case

1. Surprising: Speedup = 10, fraction = 0.5, speedup overall = only 1.82: not even double

# Amdahl's Law for Speedup=10

#### Amdahl's Law Example

- FPSQRT is responsible for 20% of execution time in a (fictitious) critical benchmark

- FP operations account for 50% of execution time in total

- Proposal A:

- New FPSQRT hardware with 10x performance

$$speedup_A = \frac{1}{(1-0.2) + \frac{0.2}{10}} = \frac{1}{0.82} = 1.22$$

- Proposal B:

- Use Si area to double speed all FP operations

$$speedup_B = \frac{1}{(1-0.5) + \frac{0.5}{2}} = \frac{1}{0.75} = 1.33$$

- → Proposal B is better

- (Probably much better for other users)

#### Word Size

- Native size of an integer register

- 32bits on ARM, MIPS II, x86 32bit mode

- 64bits on Alpha, MIPS III, SPARC v8, PA-RISC v2

- NOT size of FP or SIMD registers

- 64 / 128 bit on Pentium III

- NOT internal data-path width

- 64bit internal paths in Pentium III

- NOT external data-bus width

- 8bit Motorola 68008

- 128bit Alpha 21164

- NOT size of an instruction

- Alpha, MIPS, etc instructions 32bit

- But, 'word' also used as a type size

- 4 bytes on ARM, MIPS

- 2 bytes on Alpha, x86

- \* longword = 4 bytes, quadword = 8

#### 64bit vs 32bit words

- Alpha, MIPS III, SPARC v8, PA-RISC v2

- ✓ Access to a large region of address space from a single pointer

- large data-structures

- memory mapped files

- persistent objects

- ✔ Overflow rarely a concern

- require fewer instructions

- Can double a program's data size

- need bigger caches, more memory b/w

- ✗ May slow the CPU's max clock speed

- Some programs gain considerably from 64bit, others get no benefit.

- Some OS's and compilers provide support for 32bit binaries

- 1. 64 bits is over 10 million terabytes (1.8E19)

- 2. There now exists true 64bit versions of a number of architectures.

- 3. Alpha has always been 64bit

- 4. 32bit support: Versions of libc with both 32 and 64 bit APIs. Pointers are 32bits long.

- 5. See article on PA-RISC 64bit extensions

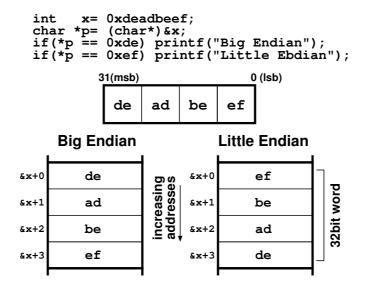

#### Byte Sex

- Little Endian camp

- Intel, Digital

- Big Endian camp

- Motorola, HP, IBM

- Sun: 'Network Endian', JAVA

- Bi-Endian Processors

- Fixed by motherboard design

- MIPS, ARM

- Endian swapping instructions

#### Byte Sex

- 1. There is no right or wrong...

- 2. PDP-11's used a strange combination of big and little endian

- 3. On a little-E machine, reading a byte from a word ptr gives the least significant byte. little-least.

- 4. personal view is that little is easier to wrap my head around

- 5. bit and byte endian. IBM/PowerPC use weird big bit-endian in manuals

- 6. Only programs that access the same value as both bytes and words care, or pass data to other processors.

- 7. MIPS: little-E on Digital Ultrix, big-E on SGI IRIX

- 8. processor XORs address bits A0 and A1 based on endian-mode. Motherboard data bus must also be wired accordingly. (endian mode cannot be changed on-the-fly)

- 9. NT currently only runs on Little Endian machines, and rumour has it that it is deeply ingrained within it, but JAVA...

- 10. Machines that only access data as words do not have an endian per se. e.g. Cray

- 11. Some old machines had 9bit bytes. Should really call a byte an octet...

- 12. instructions that swap the endian of a word have been added to several architectures particluar for little endian machines to enable them to translate in and out of 'Network endian' (which is big)

#### **Data Processing Instructions**

- 2's Complement Arithmetic

- add, subtract, multiply, compare, multiply

- some: divide, modulus

- Logical

- and, or, not, xor, bic, ...

- Shift

- shift left, logical shift right, arithmetic shift right

- some: rotate left, rotate right

- 1. add, sub: same ALU operation for signed and unsigned values

- 2. compare is a subtract in which throws result away

- 3. add overflow c: ignore, Fortran: need to know about it : exception vs test

- 4. divide: example of instruction that got added in Alpha

- 5. bic = and not

- 6. barrel shifters vs ALU (1 bit at a time shifts on old CISC e.g. 6502)

- 7. no rotate in C, but compilers can still synthesize it

- 8. rotates not in some RISC, 2 shifts and OR

- 9. arithmetic shift right replicates msb.

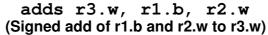

#### **Operand Size**

#### CISC

- 8,16,32 bit operations

- zero/sign extend sources

- \* need unsigned/signed instrs

- merge result into destination

- some even allow mixed size operands

#### RISC

- Word size operations only

- (except 64bit CPUs often support 32bit ops)

- Pad char and short to word

#### **Operand Size**

- 1. extension and merging can be a right pain on the critical path.

- 2. When doing truncation (part of merge), need to check for overflow

- 3. VAX and x86 allow operands of different sizes to be used in the same instruction.

- 4. Try to make Word size operations the common case

- 5. Compiler pads chars and shorts into words. (Can't be done for arrays).

- 6. Excluding 32bit ops from 64bit machines would result in too much performance loss on current code. But, Alpha always produces a 64bit result, avoiding merging.

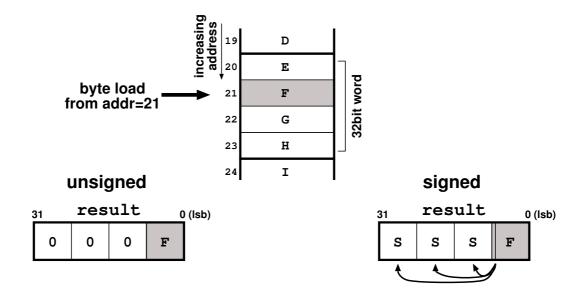

### (Zero/Sign Extension)

- Unsigned values: zero extend

- e.g. 8bit values to 32bit values

unsigned char a; int b;

and b ← a, #0xff

- Signed values: sign extend

- e.g. 8bit values to 32bit values

- Replicate sign bit char a; int b; lsl b  $\leftarrow$  a, #24 asr b  $\leftarrow$  b, #24

- C: 32bit to 8bit

- Just truncate

and b ← a, #0xff

- 1. All RISCs perform operations on 32 bit quantities: CISC

- 2. Languages other than C: Check for overflow

# CISC instructions RISC dropped

Emulated in RISC:

- Used too infrequently:

- POLY, polynomial evaluation (VAX)

- BCD, bit-field operations (68k)

- Loop and Procedure call primitives

- \* Not quite right for every HLL

- \* Unable to take advantage of compiler's analysis

- Exceptions & interrupts are awkward:

- memcpy/strcmp instructions

## CISC instructions RISC dropped

- 1. NB. Note use of  $\leftarrow$  to indicate source and destination. Some assemblers use src, dest other use dest, src. The  $\leftarrow$  convention is used in these notes to avoid this ambiguity.

- 2. nop, mov, zero would have had short instruction encodings on CISC

- 3. No execution time or opcode size advantage to be gained from having dedicated nop, mov, zero instructions on RISC. (would even result in more complicated decode logic).

- 4. Assembler may provide macros for mov, neg, clr etc.

- 5. Many 70's architectures attempted to close the 'semantic gap' between HLLs and machine code

- 6. Complex instructions that perform very specific functions

- 7. Although they are attractive to humans, Compilers often find them inconvenient to use.

- 8. Loop and procedure call primitives often weren't quite right

- 9. Procedure call primitives often were unable to make use of the compiler's static analysis to determine which registers to save and restore. (leaf procedures, call graph etc)

- 10. On more recent implementations, it is often slower to use the complex instruction than to use several standard ones. E.g. 'simple' instructions are executed directly by the Pentium P6 core, but complicated instructions require microcode to decode and execute.

- 11. memcpy: has intermediate state—has to be resumed after an interrupt or exception rather than restarted. VAX/x86 put intermediate state in GPRs.

- 12. However, fast memcpy would be very useful (though normally limited by memory bandwidth anyway)

#### **New Instructions**

- integer divide, sqrt

- popcount, priority\_encode

- Integer SIMD (multimedia)

- Intel MMX, SPARC VIS, Alpha, PA-RISC MAX

- MPEG, JPEG, polygon rendering

- parallel processing of packed sub-words

- E.g. 8x8, 4x16 bit packed values in 64b word

- arithmetic ops with 'saturation'

- \* s8 case: 125+4=127

- min/max, logical, shift, permute

- RMS error estimation (MPEG encode)

- Will compilers ever use these instrs?

- FP SIMD (3D geometry processing)

- E.g. 4x32 bit single precision

- streaming vector processing

- Intel SSE, AMD 3D-Now, PPC AltiVec

- prefetch / cache hints (e.g. non-temporal)

- Maintaining backwards compatiblity

- Use alternate routines

- Query CPU feature set

- 1. divide Now enough Si to justify it. (though IA64 doesn't have integer multiply or divide it relies on the FP unit)

- 2. popcount, priority used by OS, requested on Alpha by Cray

- 3. multimedia instructions: Probably won't be generated by compilers. (Months spent hand coding MPEG routines)

- 4. x86 MMX uses FP regs so as not to create more user state (thus no changes to the OS [MS Windows] are required)

- 5. software trap mechanism is slow—better to detect the new instructions absence (e.g. via the feature register), and branch to some code providing similar functionality.

- 6. MAX- see PA-RISC 2.0 Extensions article

- 7. Is adding all these instructions still adhering to the RISC philosophy? Given the increasing importance of multimedia, the answer is probably yes. It will be interesting to see if compilers ever manage to use these instructions (some evidence that they are). In the meantime, people are putting lots of effort into coding standard libraries with MMX/KNI/AltiVec instructions e.g. the OpenGL rendering library. Another alternative is to add language extensions that enable SIMD/vector operations to be specified in a HLL.

- 8. FP Single Instruction Multiple Data (SIMD) (vector) instructions added to improve 3D geometry processing. 'Streaming SIMD' on the Pentium III adds the first new architecturally visible CPU register state since the 386 (eight new 128bit regs). This will require some modification of the OS context switch code. Now this has happened, Intel are bringing out SIMD-2, which effectively replaces the original MMX.

- 9. Vector units repeat the same operations to streams (vectors) of operands. (unlike e.g. MMX which operates on a small fixed numbers of operands in a word).

- 10. Better to have an alternate routine than to try software emulation of the missing instructions. Taking illegal instruction traps is very slow.

- 11. Finished the survey of instructions available, next, taking a look at register sets...

#### **Registers and Memory**

- Register set types

- Accumulator architectures

- Stack

- GPR

- Number of operands

- **-** 2

- **-** 3

- Memory accesses

- any operand

- one operand

- load-store only

#### **Accumulator Architectures**

- Register implicitly specified

- E.g. 6502, 8086 (older machines)

LoadA foo AddA bar StoreA res

- Compact instruction encoding

- Few registers, typically  $\leq$  4 capable of being operands in arithmetic operations

- Forced to use memory to store intermediate values

- Registers have special functions

- e.g. loop iterators, stack pointers

- Compiler writers don't like non-orthogonality

- 1. historical perspective

- 2. 3 mem locs labelled foo, bar and res. (Offsets calculated by assembler)

- registers much faster for storing intermediates. registers not being used for their special functions can be used as temporaries.

- 4. never enough of the right type of register...

#### Stack Architectures

- Operates on top two stack items

- E.g. Transputer, (Java)

Push foo

Push bar

Add

Pop res

- Stack used to store intermediate values

- Compact instruction encoding

- Smaller executable binaries, good if:

- memory is expensive

- downloaded over slow network

- Fitted well with early compiler designs

- 1. Like accumulator architecture, tricky to make go fast (especially super-scalar implementations)

- 2. Stacks are easier to cache then general memory accesses, but spotting dependencies between instructions is still harder than with registers.

- 3. One advantage of stack architectures is that they do not impose a limit on the number of architecturally visible 'registers', thus allowing future scalability.

- 4. Back to something more familiar, the RISC approach

#### General Purpose Register Sets

- Post 1980 architectures, both RISC and CISC

- 16,32,128 registers for intermediate values

- Separate INT and FP register sets

- Int ops on FP values meaningless

- RISC: Locate FP regs in FP unit

- Separate Address/Data registers

- address regs used as bases for mem refs

- e.g. Motorola 68k

- not favoured by compiler writers  $(8 + 8 \neq 16)$

- RISC: Combined GPR sets

- 1. x86 32bit mode (IA-32) is basically an 8 register GPR set

- 2. AMD 29K embedded controller family (used in many laser printers) has 128 registers, as does Intel's IA-64 Merced

- 3. 32 may not be enough (look at register renaming later)

- 4. FP regs are used by different functional units from INT regs. Interpreting integers as FP values and vice versa is relatively rare. Makes sense to keep them separate, enabling a dedicated register file to be located next to the appropriate functional units.

- 5. Some ISAs have instructions to move values between FP and int regs. Alpha doesn't: transfer has to be achieved via a StoreFP followed by a Load (via L1 D-cache)

- 6. New 'media processors' (DSPs) tend to have common int and FP regs. They believe that conversion between int and fp will be a common operation.

- 7. Dedicated address registers may be mildly advantageous to implementation, as address registers could be located closer to the load/store unit.

- 8. But, Separate address and data registers can be a pain, as for some loops you wish you had more address registers, for other loops you wish you had more data. End up copying values back and forth between data and address.

#### **Load-Store Architecture**

- Only load/store instructions ref memory

- The RISC approach

- → Makes pipelining more straightforward

- Fixed instruction length (32bits)

- 3 register operands

- Exception: ARM-Thumb, MIPS-16 is two operand

- more compact encoding (16bits)

- 1. Only one port required on D-cache to avoid stalls due to structural hazards

#### Register-Memory

- ALU instructions can access 1 or more memory locations

- E.g. Intel x86 32bit modes

- 2 operands

- can't both be memory

```

Load r1 \leftarrow foo

Add r1 \leftarrow bar

Store res \leftarrow r1

```

- E.g. DEC VAX

- 2 and 3 operand formats

- fully orthogonal

```

Add res←bar,foo

```

- Fewer instructions

- Fewer load/stores

- Each instruction may take longer

- $\rightarrow$  Increased cycle time

- Variable length encoding

- May be more compact

- May be slower to decode

#### **Register-Memory**

- 1. Variable length encoding: Intel 32bit mode 1-17bytes, 16bit mode 1-9, VAX 1-19

- 2. orthogonal: any combination is legal

- 3. each instruction may be slower, harder to pipeline

- 4. Although most post 1980 architectures use GPR sets, there are still some special registers...

#### **Special Registers: 1**

- Zero register

- Read as Zero, Writes discarded

- e.g. Alpha, Mips, Sparc, IA-64

- Data move: add  $r2 \leftarrow r1$ , r31

- nop: add r31  $\leftarrow$  r31, r31

- prefetch: ldl r31 ← (r1)

- Zero is a frequently used constant

- Program Counter

- NOT usually a GPR

- Usually accessed by special instructions e.g. branch, branch and link, jump

- But, PC is GPR r15 on ARM

- 1. zero register: r0 on MIPS, r31 on Alpha

- 2. prefetch: Allows a value to be pulled into cache without risk of generating an exception

- 3. ARM's visible PC exposes the pipeline depth. This was a pain on the StrongArm which has a 5 stage pipe instead of 3.

#### Special Registers: 2

- Condition code (Flag) registers

- Carry, Zero, Negative, Overflow

- Used by branches, conditional moves

- Critical for pipelining and super-scalar

- CISC: one CC reg updated by all instructions

- ARM, SPARC: one CC reg, optionally updated

- PowerPC: multiple CC regs (instr chooses)

- IA64: 64 one bit predicate regs

- Alpha, MIPS: no special CC regs

- Link registers

- Subroutine call return address

- CISC: pushed to stack

- RISC: saved to register

- \* register conventions

- \* only push to stack if necessary

- Jump target/link regs (PowerPC, IA-64)

- fixed GPR (r14, ARM) (r31, MIPS)

- GPR nominated by individual branch (Alpha)

#### **Special Registers: 2**

- 1. Revision: meanings of the various CC flags.

- 2. ARM/SPARC: Bit in opcode to determine whether CC updated.

- 3. Single CC register poses problems for super-scalar implementation due to false dependencies.

- 4. Alpha and MIPS have no CC registers. GPRs used in their place, thus using the normal dependency analysis logic. Have to test for carry/overflow etc using ALU instructions.

- 5. IA64 has 64 single bit predicate registers. Compare instructions nominate two pred regs: one will be cleared, the other set.

- 6. More on the implications of CC regs for control flow later...

- 7. register conventions: args, result, temps, caller saves, callee saves

- 8. Wheeler Jumps

- 9. push to stack: eg if recursive

- 10. The link register typically has to be moved to a callee saves register before making another procedure call. Alpha avoids this by allowing the current PC to be stored in a nominated register.

- 11. IA64 has 8 branch target registers. Special registers are used in order to give hints to the instruction prefetch unit.

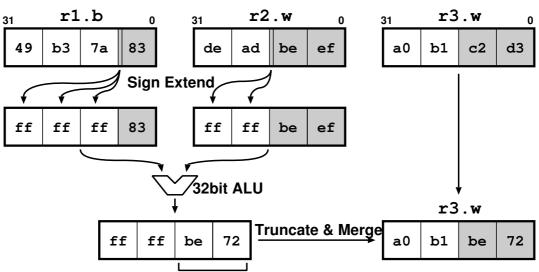

### **Register Conventions**

- Linkage (Procedure Call) Conventions

- Globals: sp, gp etc.

- Args: First (4-6) args (rest on stack)

- Return value: (1-2)

- Temps: (8-12)

- Saved: (8-9) Callee saves

- Goal: spill as few registers as possible in total

- Register Windows (SPARC)

- save and restore

- 2-32 sets of windows in ring

- 16 unique registers per window

- spill/fill windows to special stack

- IA-64: Allows variable size frames

- 32 globals

- 0-8 args/return, 0-96 locals/out args

- h/w register stack engine operates in background

### **Register Conventions**

- 1. languages can have different conventions for the same CPU

- 2. Caller saves its own args and temps

- 3. goal: save as few as possible in total. Don't save all before procedure call as callee may not use many. Don't save all after as caller may not have used many.

- 4. Compiler should allocate variables to 'Saved' registers, then put any that are left over in 'Temps'.

- 5. Call graph optimization can be used to tune which registers are actually saved.

- 6. When SPARC was designed, the Berkeley team felt that the current compiler technology was not up to the job of assigning arguments etc to registers.

- 7. Sparc: don't have to move incoming args to safety before making another call—it's done in hardware.

- 8. Sparc: running out of windows is bad normally need to save the full 16 registers in the window regardless of which are actually used.

- 9. Sparc: Total context is very large—painful to context switch.

- 10. Next, a look at addressing modes...

### Classic RISC Addressing Modes

- Register

- Mov r0 ← r1

- Regs[r0] = Regs[r1]

- Used when value held in register

- Immediate

- Mov r0  $\leftarrow$  42

- Regs[r0] = 42

- Constant value limitations

- Register Indirect

- Ldl r0  $\leftarrow$  [r1]

- Regs[r0] = Mem[ Regs[r1] ]

- Accessing variable via a pointer held in reg

- Register Indirect with Displacement

- Ldl r0 ← [r1, #128]

- Ldl r0  $\leftarrow$  128(r1)

- Regs[r0] = Mem[128 + Regs[r1]]

- Accessing local variables

#### Classic RISC Addressing Modes

- 1. First two not really addressing modes as don't access memory...

- 2. Different assemblers have different syntax Even for same arch!

- 3. register indirect obviously a special case of register indirect with displacement just a more compact encoding on CISC.

- 4. Explain arrays Regs and Mem

- 5. Pretty much all processors have the RISC addr modes

- 6. Immediate values: on most CISCs they must be prefixed with # or \$

- 7. reg indirect with displacement used for accessing local vars off stack pointer, or global variables from the GP register

- 8. displacement size is often limited on RISC architectures.

## Less RISCy addr modes

- ARM and PowerPC

- Register plus Register (Indexed)

- Ldl r0  $\leftarrow$  [r1,r2]

- Regs[r0] = Mem[Regs[r1] + Regs[r2]]

- Random access to arrays

- e.g. r1=base, r2=index

- Register plus Scaled Register

- Ldl r0  $\leftarrow$  [r1, r2, asl #4]

- Regs[r0] = Mem[ Regs[r1] + (Regs[r2] $\ll$ 4)]

- Array indexing

- sizeof(element) is power of 2, r2 is loop index

- Register Indirect with Displacement and Update

- Pre inc/dec Ldl r0  $\leftarrow$  [r1!, #4]

- Post inc/dec Ldl r0 ← [r1], #4

- C \*(++p) and \*(p++)

- Creating stack (local) variables

- Displacement with post update is IA-64's only addressing mode

### Less RISCy addr modes

- 1. can improve instruction density

- 2. reg+reg requires an extra read port on register file

- 3. ARM: shift unit can be used to scale one operand for any instruction.

- 4. syntax for displacement and update highly variable. For some architectures, displacement is fixed to the sizeof the value being loaded.

- 5. Full descending stack use: pre dec, post inc

- 6. Empty descending stack use: post dec, pre inc

- 7. Displacement with update requires an extra write port on register file.

- 8. IA-64 ONLY supports reg+disp with compulsory post update & reg+reg with compulsory update. Accessing structure members presumably requires the compiler to deal with a 'moving base pointer' as different elements are accessed. Understanding disassembled IA-64 code is going to be a nightmare...

## **CISC Addressing Modes**

- Direct (Absolute)

- Mov r0  $\leftarrow$  (1000)

- Regs[r0] = Mem[1000]

- Offset often large

- x86 Implicit base address

- Most CISCs

- Memory Indirect

- Mov r0  $\leftarrow$  0[r1]

- Regs[r0] = Mem[Mem[Regs[r1]]]

- Two memory references,

- C \*\*ptr, linked lists

- PC Indirect with Displacement

- Mov r0 ← [PC, #128]

- Regs[r0] = Mem[PC + 128]

- Accessing constants

### **CISC Addressing Modes**

- 1. Absolute mode: eq. 6502 Zero page

- 2. absolute mode synthesizable on RISC with zero register

- 3. absolute mode is not compatible with object oriented programming

- 4. Memory indirect: two memory references required, thus two possibilities for exceptions to occur.

- 5. Even more complicated modes exist e.g. 68020's Mem Indirect Pre Indexed mode: two displacement, a scale, two registers and two memory accesses. Abandoned on 68040?

- 6. PC indirect useful for Position Independent code, e.g. for single address space operating systems, shared libraries etc.

- 7. branch instructions are typically PC relative PC indirect mode enables relative access to data. Particularly useful for read-only data, which can be placed in the text segment (usually just after the function in which it is used).

- 8. Assembler can usually fills in the offset between the instruction doing the access and the data being accessed.

- 9. ARM supports PC indirect mode, as PC is just another GPR

- 10. Other RISC processors generally use other conventions to access literal constants in a position-independent manner. e.g. a register containing the 'procedure variable'

- 11. PC indirect mode can be synthesized on other RISC processors by doing a subroutine call to the following instruction, and using the PC value stored in the link register.

# Why did RISC choose these addressing modes?

Frequency of addressing modes (VAX)

- RISC

- immediate

- register indirect with displacement

- ARM, PowerPC reduce instruction counts by adding:

- register + register scaled

- index update

- 1. Quantitative approach

- 2. IA-64 allows only register indirect, but forces the base register to be incremented by either a Reg or an Immediate AFTER the load.

# Immediates and Displacements

- CISC: As instructions are variable length, immediates and displacements can be any size (8,16,32 bits)

- RISC: How many spare bits in instruction format?

- Immediates

- used by data-processing instructions

- usually zero extended (unsigned)

```

* add \rightarrow sub

```

- \* and  $\rightarrow$  bic

- For traces on previous slide:50-70% fit in 8bits, 75-80% in 16bits