## Digital Electronics – Sequential Logic

Dr. I. J. Wassell

#### **Sequential Logic**

- The logic circuits discussed previously are known as *combinational*, in that the output depends only on the condition of the latest inputs

- However, we will now introduce a type of logic where the output depends not only on the latest inputs, but also on the condition of earlier inputs. These circuits are known as *sequential*, and implicitly they contain *memory* elements

- A memory stores data usually one bit per element

- A snapshot of the memory is called the *state*

- A one bit memory is often called a *bistable*, i.e., it has 2 stable internal states

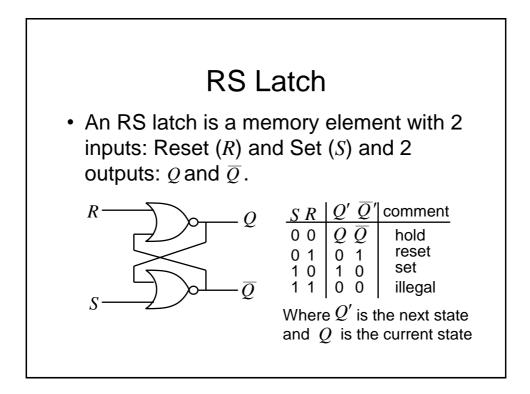

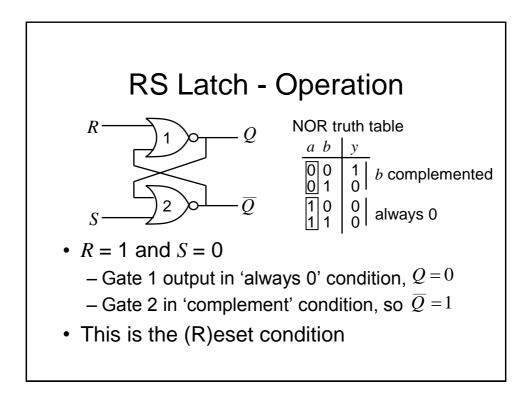

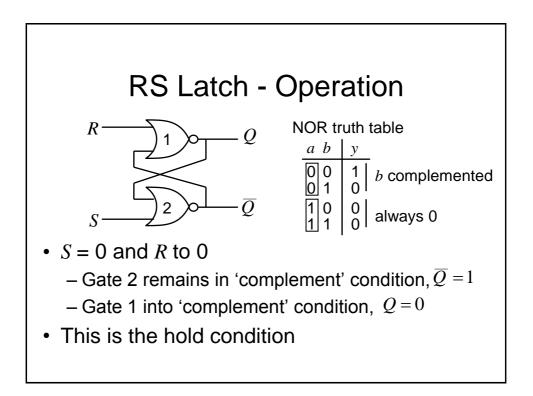

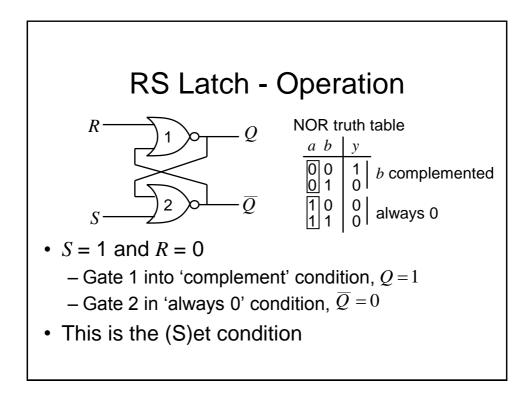

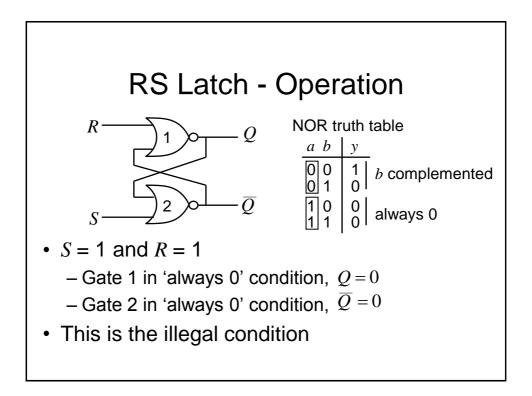

- *Flip-flops* and *latches* are particular implementations of bistables

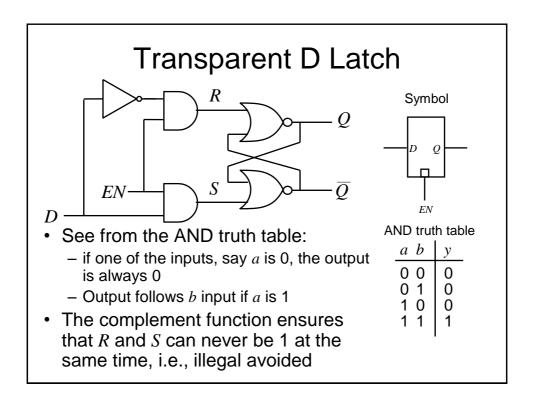

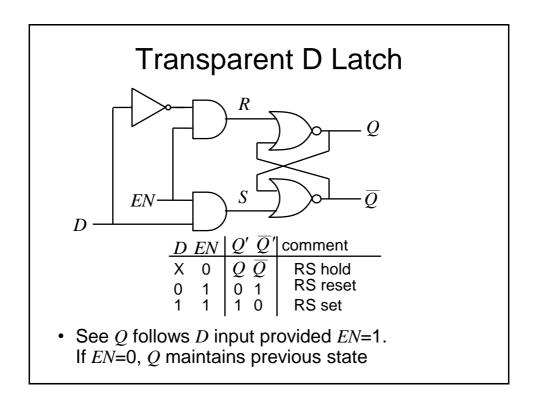

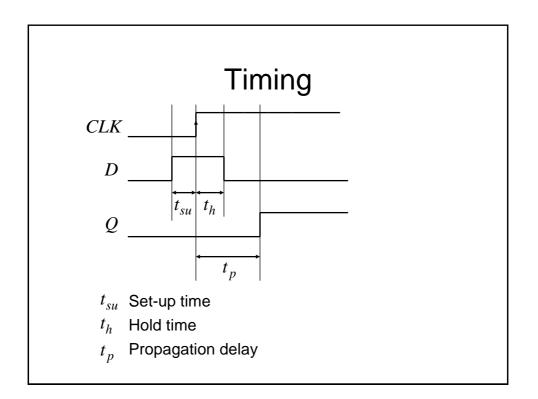

- The transparent D latch is so called '*level*' triggered. We can see it exhibits transparent behaviour if *EN*=1. It is often more simple to design sequential circuits if the outputs change only on the either rising (positive going) or falling (negative going) '*edges*' of the clock (i.e., enable) signal

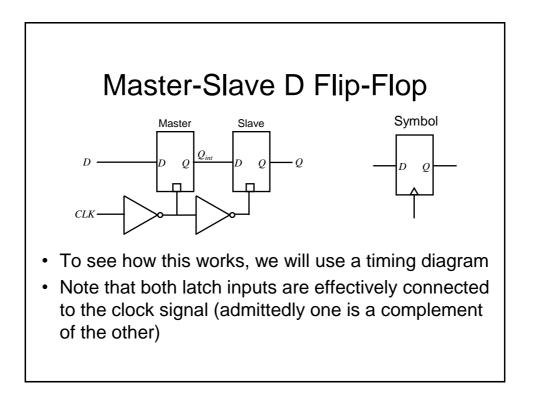

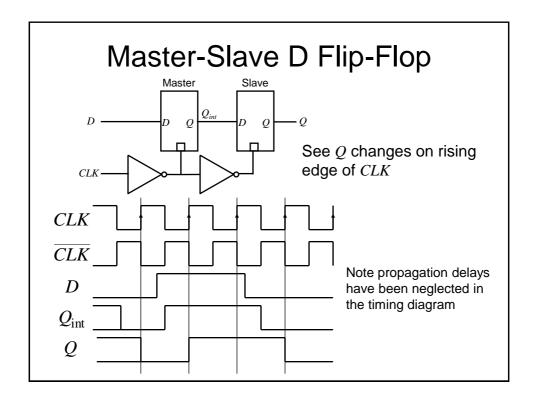

- We can achieve this kind of operation by combining 2 transparent D latches in a so called *Master-Slave* configuration

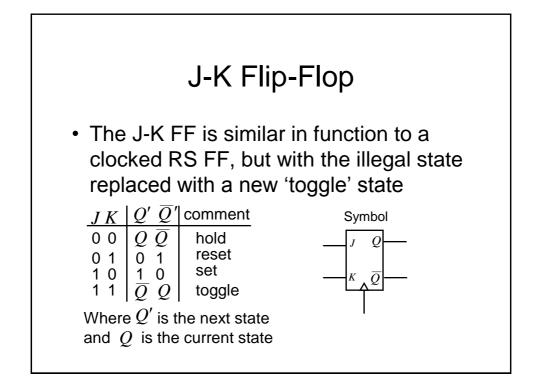

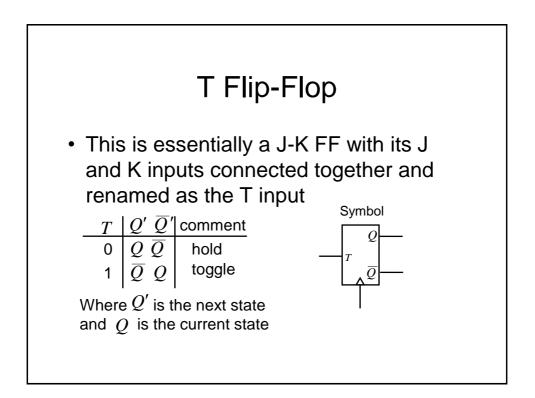

- Historically, other types of Flip-Flops have been important, e.g., J-K Flip-Flops and T-Flip-Flops

- However, J-K FFs are a lot more complex to build than D-types and so have fallen out of favour in modern designs, e.g., for field programmable gate arrays (FPGAs) and VLSI chips

#### Asynchronous Inputs

- It is common for the FF types we have mentioned to also have additional so called 'asynchronous' inputs

- They are called asynchronous since they take effect independently of any clock or enable inputs

- Reset/Clear force Q to 0

- Preset/Set force *Q* to 1

- Often used to force a synchronous circuit into a known state, say at start-up.

- Memories, e.g.,

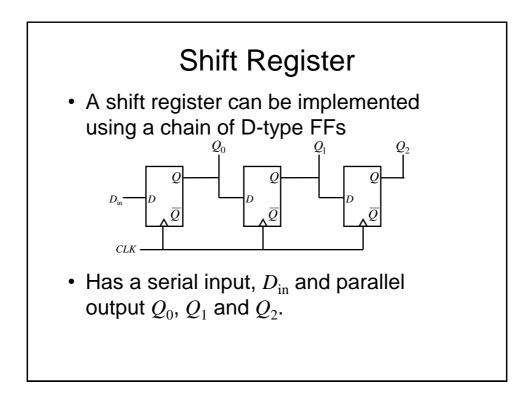

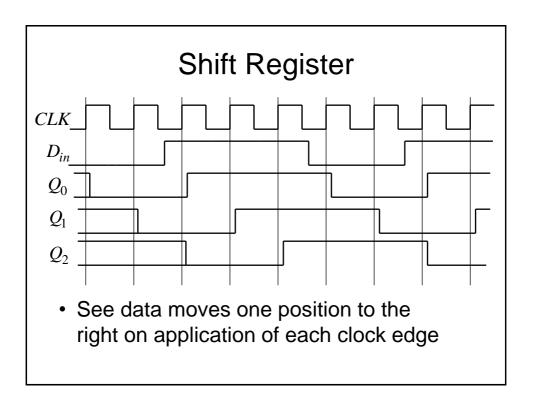

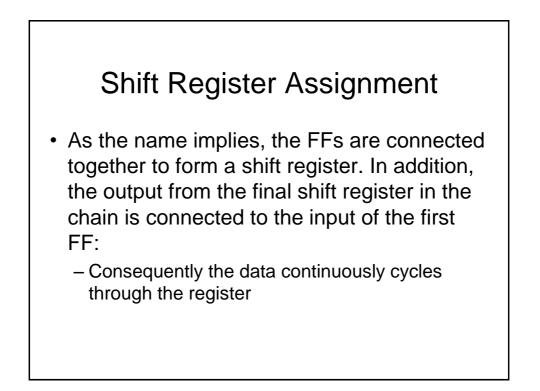

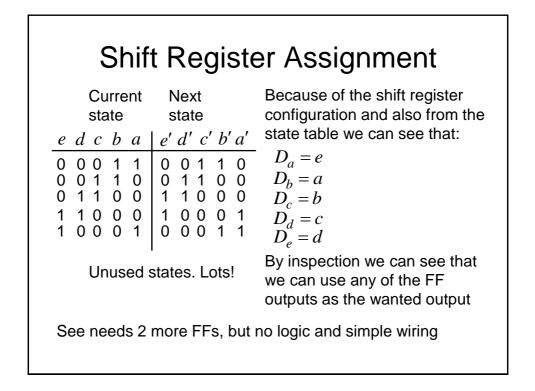

- Shift register

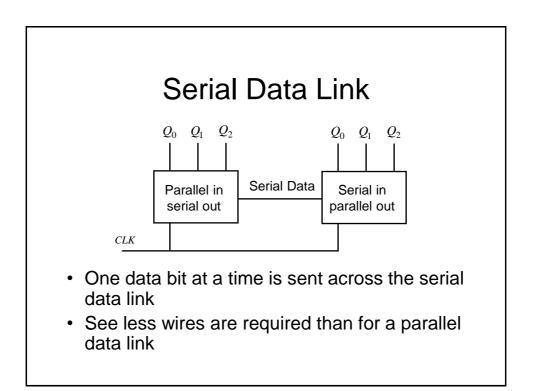

- Parallel loading shift register : can be used for parallel to serial conversion in serial data communication

- Serial in, parallel out shift register: can be used for serial to parallel conversion in a serial data communication system.

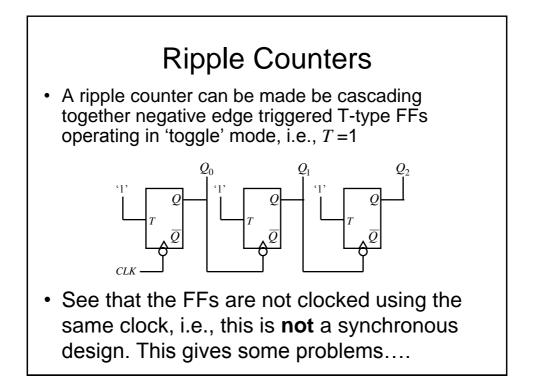

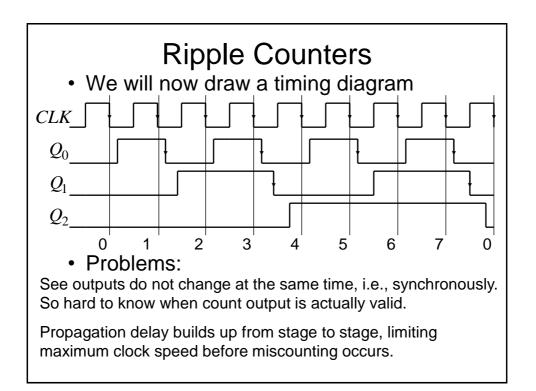

# **Ripple Counters**

- If you observe the frequency of the counter output signals you will note that each has half the frequency, i.e., double the repetition period of the previous one. This is why counters are often known as dividers

- Often we wish to have a count which is not a power of 2, e.g., for a BCD counter (0 to 9).To do this:

- use FFs having a Reset/Clear input

- Use an AND gate to detect the count of 10 and use its output to Reset the FFs

#### Synchronous Counters

- We will now investigate the design of synchronous counters

- We will consider the use of D-type FFs only, although the technique can be extended to cover other FF types.

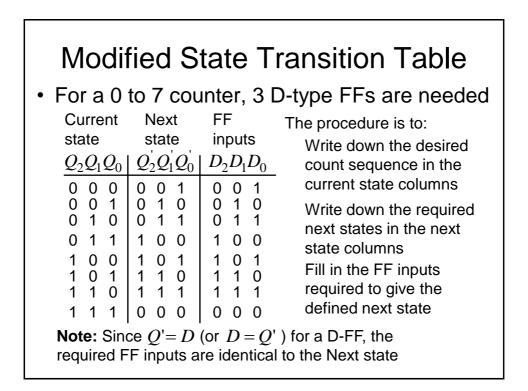

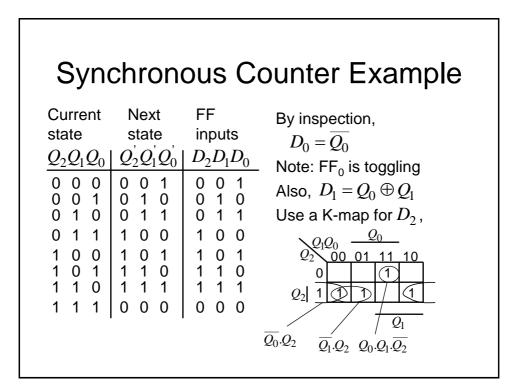

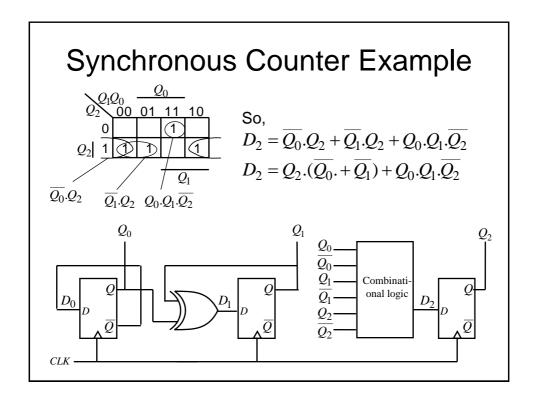

- As an example, we will consider a 0 to 7 up-counter

- To assist in the design of the counter we will make use of a modified *state transition table*. This table has additional columns that define the required FF inputs (or excitation as it is known)

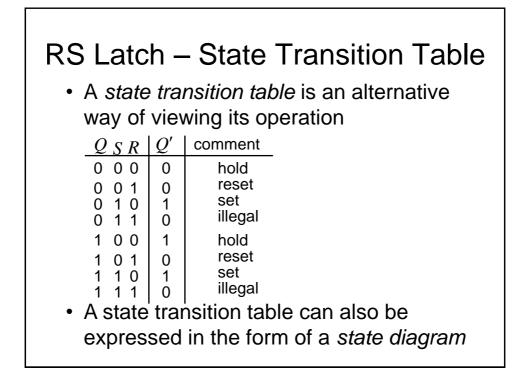

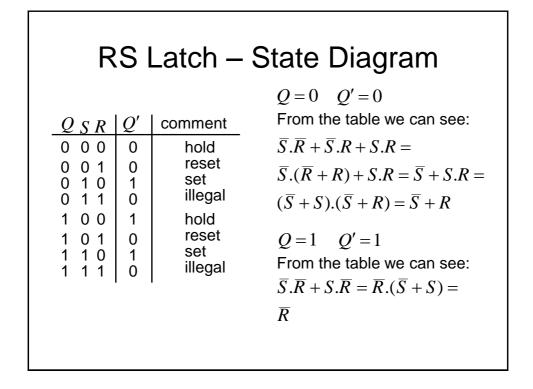

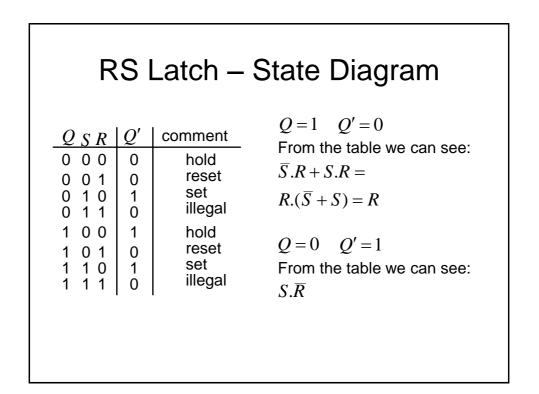

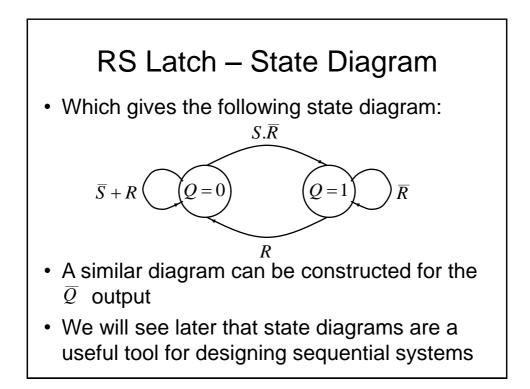

- Note we have used a state transition table previously when determining the state diagram for an RS latch

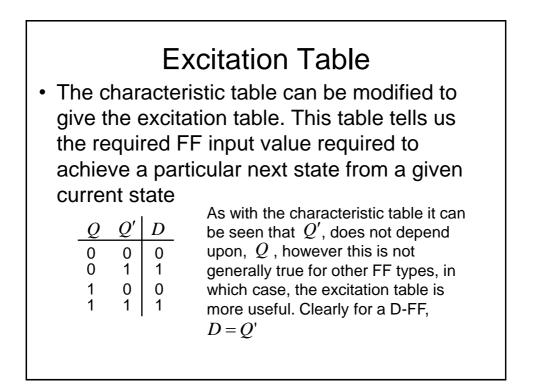

- We will also make use of the so called '*excitation table*' for a D-type FF

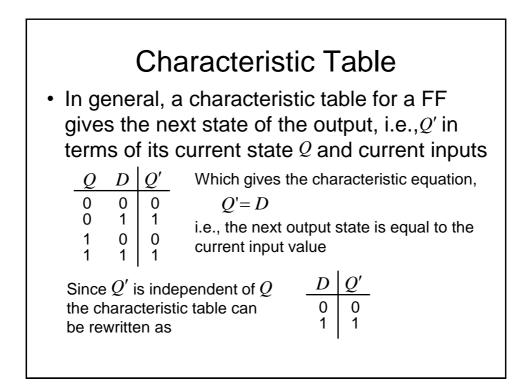

- First however, we will investigate the so called *characteristic table* and *characteristic equation* for a D-type FF

## Characteristic and Excitation Tables

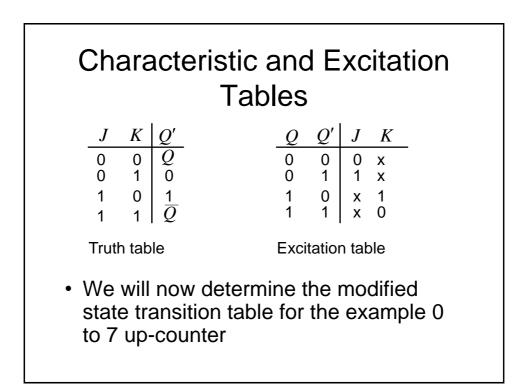

- Characteristic and excitation tables can be determined for other FF types.

- These should be used in the design process if D-type FFs are not used

- For example, for a J-K FF the following tables are appropriate:

#### Modified State Transition Table

In addition to columns representing the current and desired next states (as in a conventional state transition table), the modified table has additional columns representing the required FF inputs to achieve the next desired FF states

# Synchronous State Machines

## Synchronous State Machines

- We have seen how we can use FFs (D-types in particular) to design synchronous counters

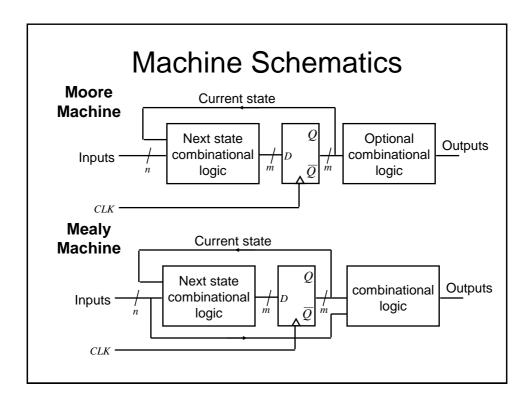

- We will now investigate how these principles can be extended to the design of synchronous state machines (of which counters are a subset)

- We will begin with some definitions and then introduce two popular types of machines

## Definitions

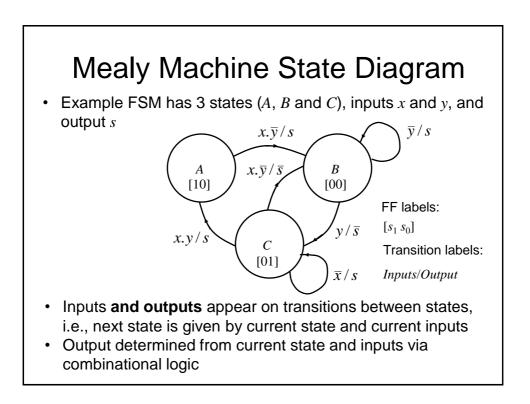

- Finite State Machine (FSM) a deterministic machine (circuit) that produces outputs which depend on its internal state and external inputs

- **States** the set of internal memorised values, shown as circles on the state diagram

- Inputs External stimuli, labelled as arcs on the state diagram

- Outputs Results from the FSM

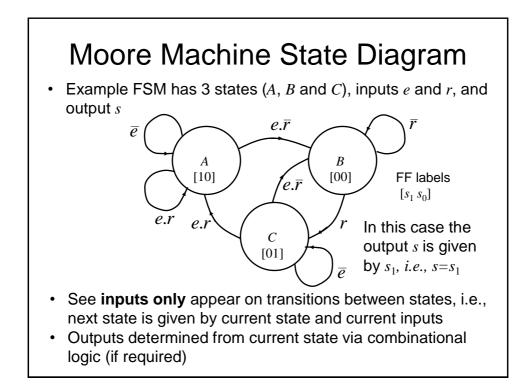

#### Moore Machine - Example

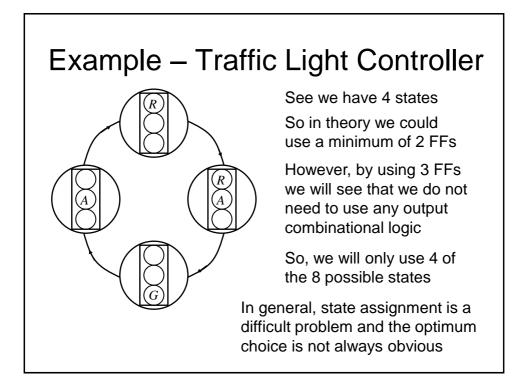

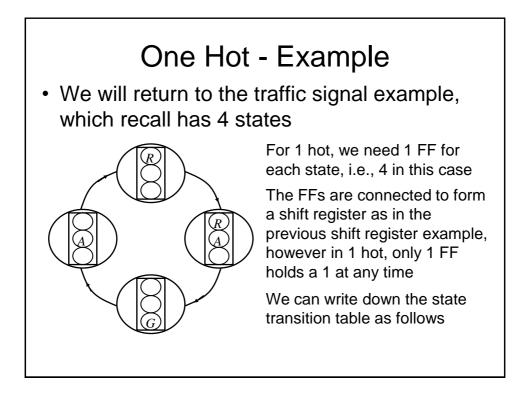

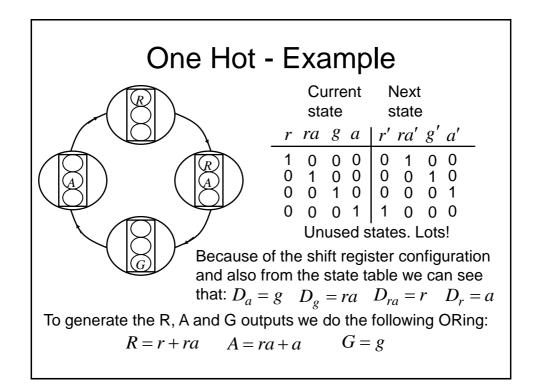

- We will design a Moore Machine to implement a traffic light controller

- In order to visualise the problem it is often helpful to draw the state transition diagram

- This is used to generate the state transition table

- The state transition table is used to generate

- The next state combinational logic

- The output combinational logic (if required)

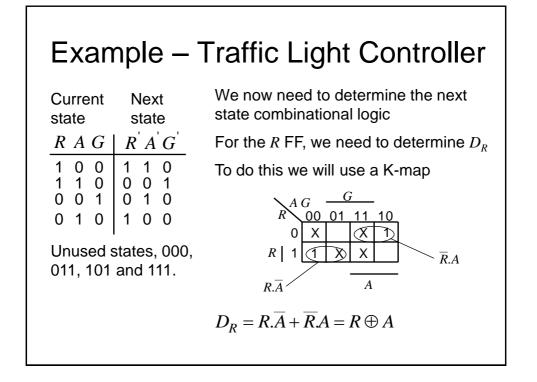

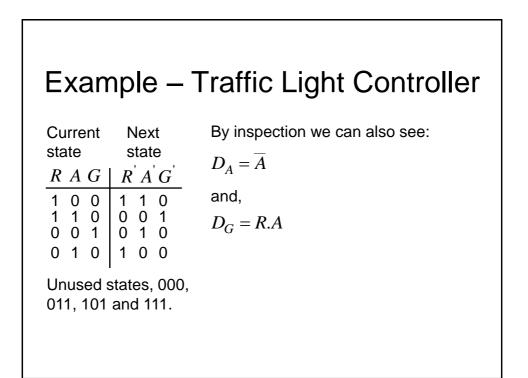

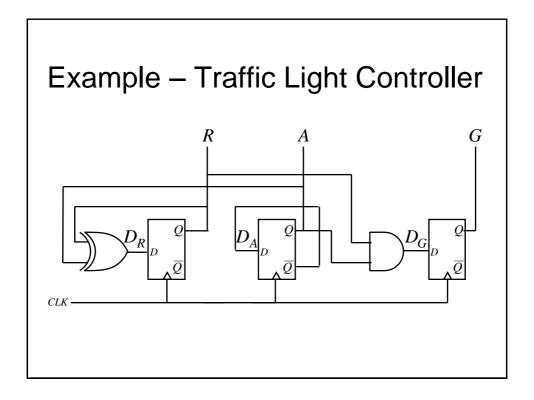

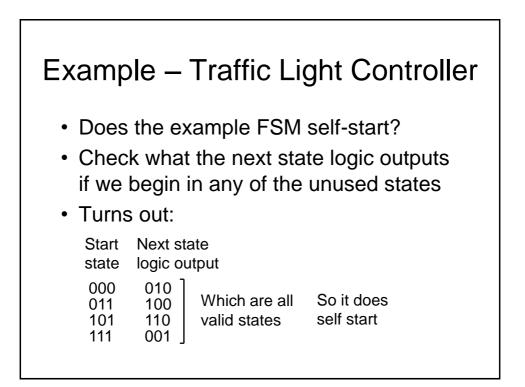

# Example – Traffic Light Controller

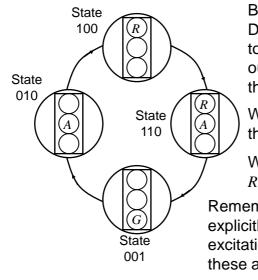

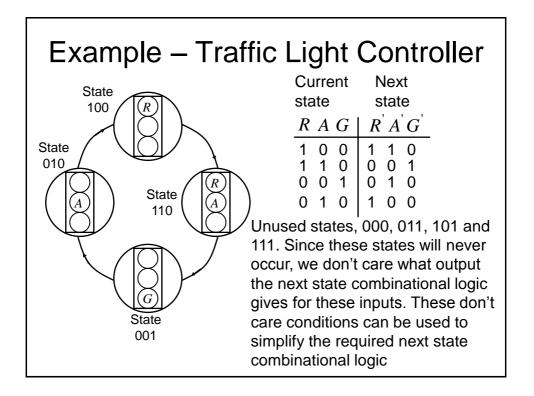

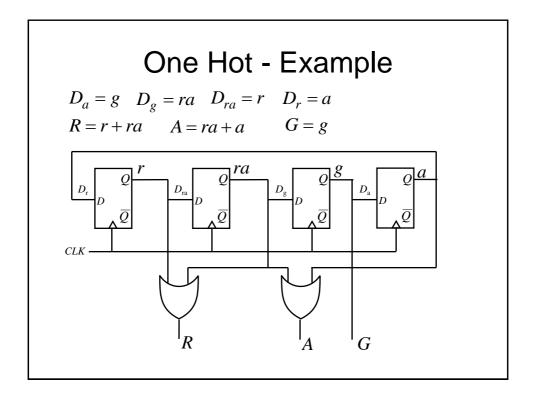

By using 3 FFs (we will use D-types), we can assign one to each of the required outputs (R, A, G), eliminating the need for output logic

We now need to write down the state transition table

We will label the FF outputs R, A and G

Remember we do not need to explicitly include columns for FF excitation since if we use D-types these are identical to the next state

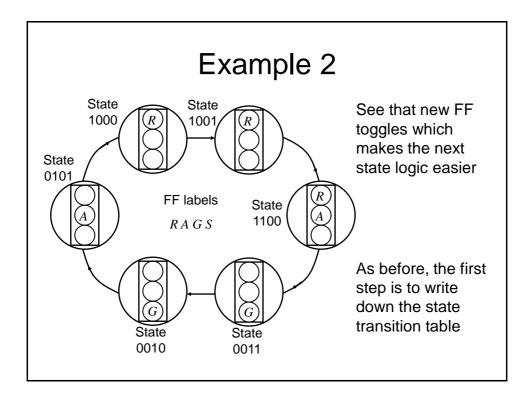

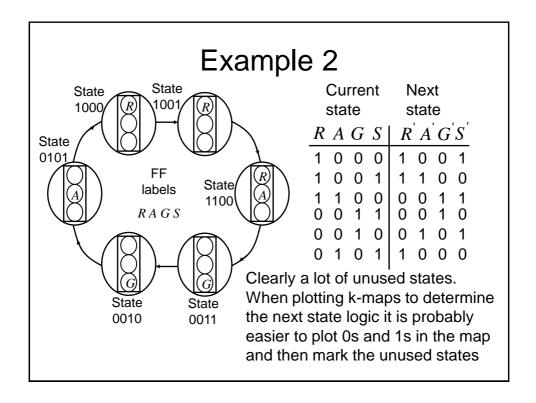

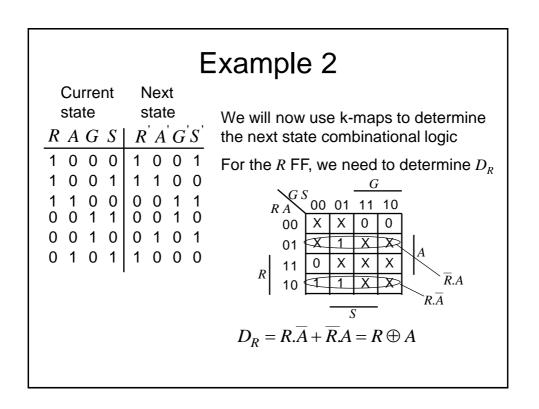

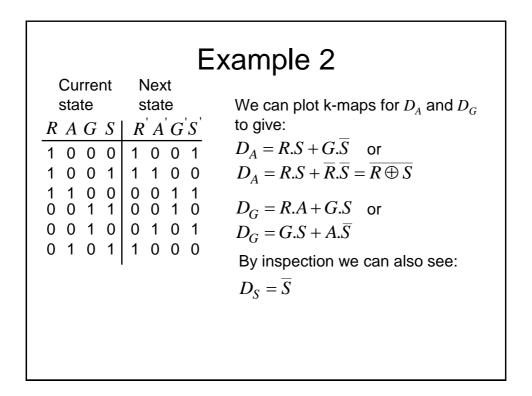

- We extend Example 1 so that the traffic signals spend extra time for the *R* and *G* lights

- Essentially, we need 2 additional states, i.e., 6 in total.

- In theory, the 3 FF machine gives us the potential for sufficient states

- However, to make the machine combinational logic easier, it is more convenient to add another FF (labelled *S*), making 4 in total

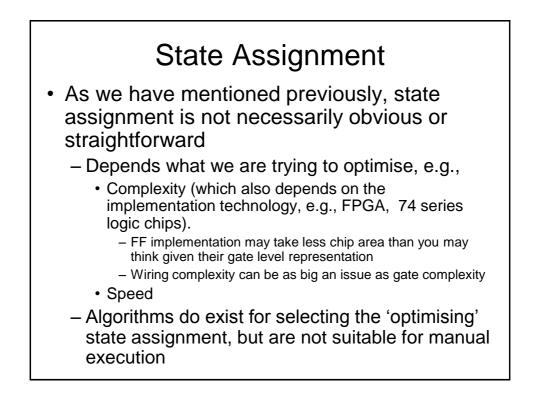

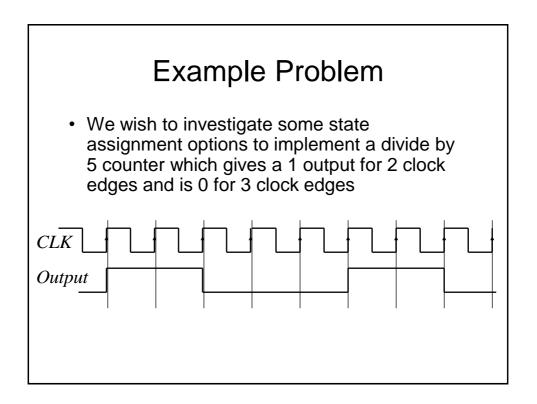

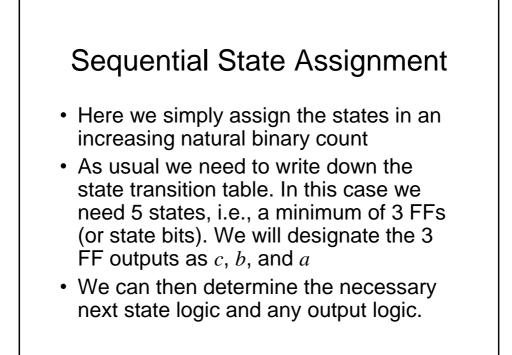

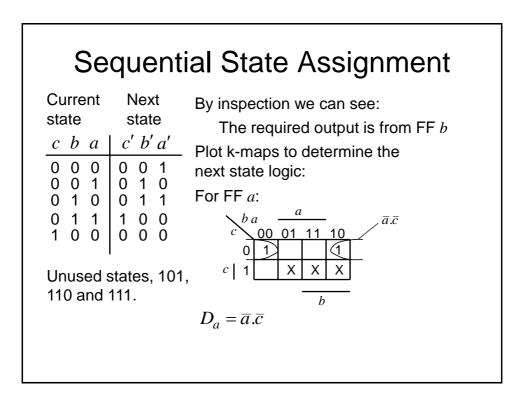

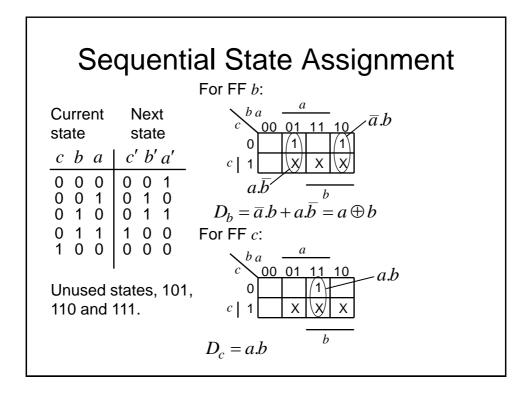

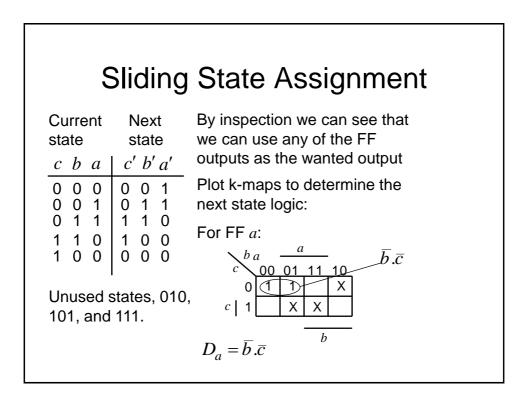

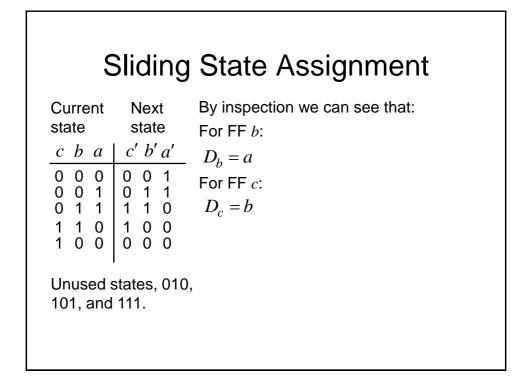

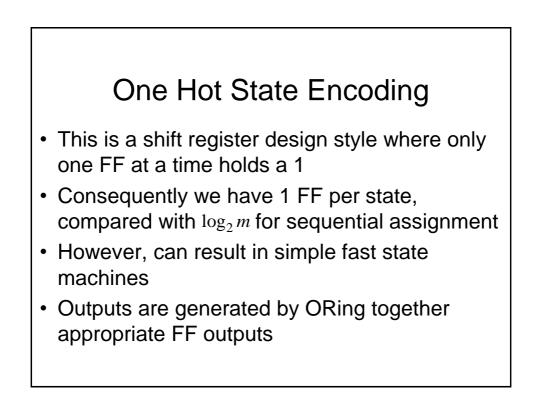

## State Assignment

- If we have *m* states, we need at least log<sub>2</sub>*m* FFs (or more informally, bits) to encode the states, e.g., for 8 states we need a min of 3

FFs

- We will now present an example giving various potential state assignments, some using more FFs than the minimum

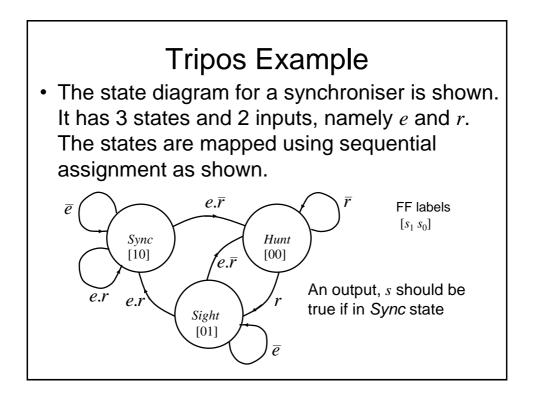

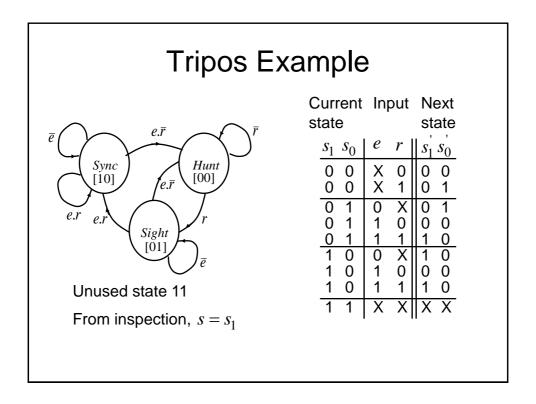

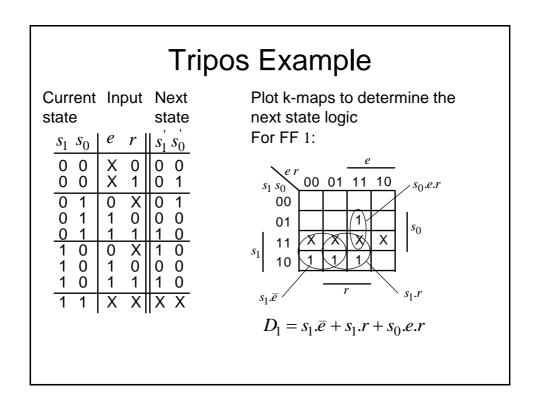

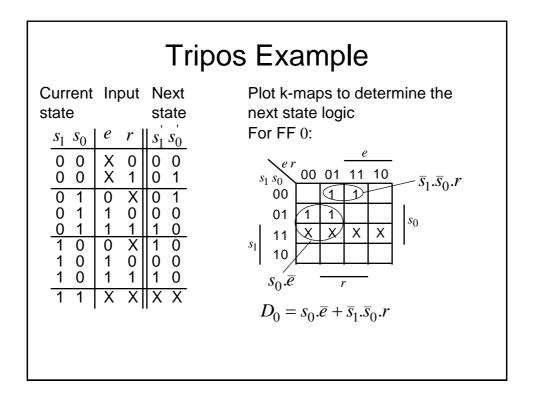

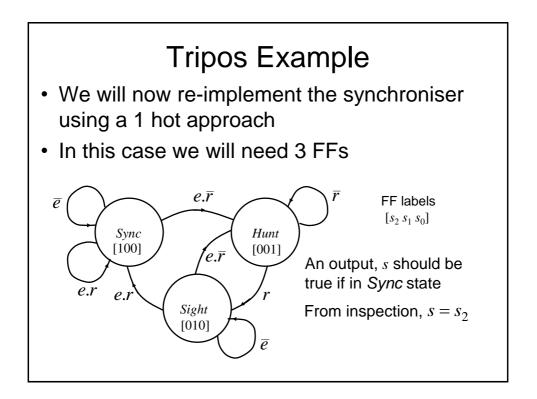

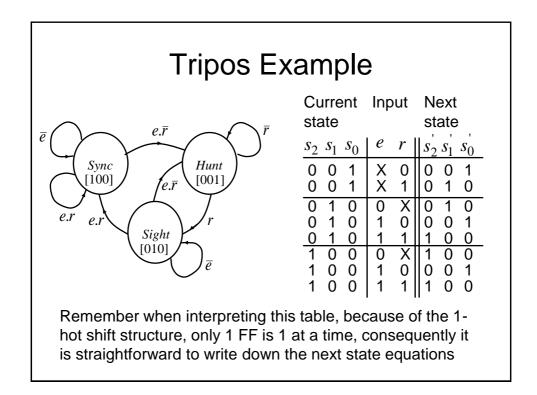

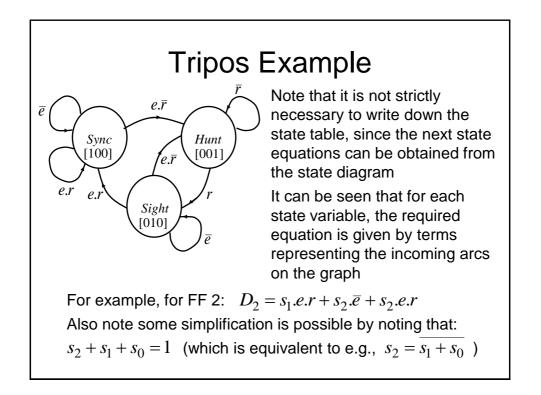

|                                                                                               | Tripos Example |                                                                                                                                                                 |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| $\begin{array}{c ccc} 0 & 0 & 1 \\ \hline 0 & 1 & 0 \\ 0 & 1 & 0 \\ 0 & 1 & 0 \\ \end{array}$ | state          | $D_1 = s_0 \cdot r + s_1 \cdot \overline{e}$<br>- For FF 0:<br>$D_0 = s_0 \cdot \overline{r} + s_1 \cdot e \cdot \overline{r} + s_2 \cdot e \cdot \overline{r}$ |  |  |  |  |  |  |  |

## Elimination of Redundant States

- Sometimes, when designing state machines it is possible that unnecessary states may be introduced

- In general, reducing the number of states may reduce the number of FFs required and may also reduce the complexity of the next state logic owing to the presence of more unused states (don't cares)

| Current<br>State | Sta    | ate    | Outp<br>X=0      | ut (Z)<br>X=1 | <ul> <li>From the table, we see<br/>that there is no way of</li> </ul> |  |  |  |  |  |

|------------------|--------|--------|------------------|---------------|------------------------------------------------------------------------|--|--|--|--|--|

| A                | В      | С      | 0                | 0             | telling states H and I apart,                                          |  |  |  |  |  |

| B<br>C           | D<br>F | E<br>G | 0                | 0<br>0        | so we can replace I with H                                             |  |  |  |  |  |

| D<br>E           | H<br>J | l<br>K | 0<br>0           | 0<br>0        | when it appears in the<br>Next State portion of the                    |  |  |  |  |  |

| F<br>G           | L<br>N | M<br>P | 0<br>0           | 0<br>0        | table                                                                  |  |  |  |  |  |

| H                | A      | A      | 0                | 0             |                                                                        |  |  |  |  |  |

|                  | A      | A      | 0                | 0             |                                                                        |  |  |  |  |  |

| J<br>K           | A      | A<br>A | 0                | 0             |                                                                        |  |  |  |  |  |

| L                | Â      | Â      | ŏ                | 1             |                                                                        |  |  |  |  |  |

| M                | A      | A      | 0<br>0<br>0<br>0 | 0             |                                                                        |  |  |  |  |  |

| N<br>P           | A<br>A | A<br>A | 0                | 0<br>0        |                                                                        |  |  |  |  |  |

| Current<br>State<br>A<br>B<br>C<br>D<br>E<br>F | Next<br>State<br>X=0 X=<br>B C<br>D E<br>F C<br>H H<br>J K | 1 X=0<br>0<br>0<br>0<br>0<br>0 | out (Z)                         | • | <b>The Second Seco</b> |

|------------------------------------------------|------------------------------------------------------------|--------------------------------|---------------------------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| H JKLZZP                                       | A A A A A A A A A A A A A A A A A A A                      |                                | 0<br>1<br>0<br>1<br>0<br>0<br>0 |   | state and output as H and can be replaced by H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Current<br>State<br>A<br>B<br>C<br>D<br>E<br>F<br>G | X=0<br>B<br>D<br>F<br>J<br>L<br>H | Ate<br>X=1<br>C<br>E<br>G<br>H<br>H<br>H<br>H | X=0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | out (Z)<br>X=1<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | <ul> <li>way to get to states K, M,<br/>N and P and so we can<br/>remove these rows from<br/>the table</li> <li>Also, the next state and<br/>outputs are identical for</li> </ul> |

|-----------------------------------------------------|-----------------------------------|-----------------------------------------------|----------------------------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                     | L<br>H<br>A                       | H<br>H<br>A                                   |                                        | 0<br>0<br>0                                       | -                                                                                                                                                                                 |

| J                                                   | A                                 | A<br>A                                        | 0                                      | 1<br>1                                            | be replaced by J and row L eliminated from the table                                                                                                                              |

|                                                     |                                   | / \                                           |                                        | I                                                 |                                                                                                                                                                                   |

| Current<br>State<br>A<br>B<br>C<br>D<br>E<br>F | B C<br>D E<br>F G<br>H H<br>J H<br>J H | Output (Z)<br>X=0 X=1<br>0 0<br>0 0<br>0 0<br>0 0<br>0 0<br>0 0<br>0 0 | <ul> <li>identical, as are rows E<br/>and F.</li> <li>Consequently, G can be<br/>replaced by D, and row G<br/>eliminated. Also, F can be</li> </ul> |

|------------------------------------------------|----------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| G<br>H<br>J                                    | H H<br>A A<br>A A                      | 0 0 0 0 0 0 1                                                          | replaced by E and row F eliminated from the table                                                                                                   |

| Current<br>State | Nex<br>Sta<br>X=0 X | te                                            |        | out (Z) | • | nple<br>The procedure employed                                                   |

|------------------|---------------------|-----------------------------------------------|--------|---------|---|----------------------------------------------------------------------------------|

| A                | B                   | <u>C C C C C C C C C C C C C C C C C C C </u> | 0      | 0       |   | to find equivalent states in<br>this example is known as                         |

| B<br>C           | D<br>E              | E<br>D                                        | 0<br>0 | 0<br>0  |   | row matching.                                                                    |

| D<br>E           | J<br>H              | H<br>H                                        | 0<br>0 | 0<br>0  |   | However, we note row<br>matching is not sufficient to<br>find all the equivalent |

| Н                | A                   | А                                             | 0      | 0       |   | states except for certain                                                        |

| J                | А                   | А                                             | 0      | 1       |   | special cases                                                                    |

|                  |                     |                                               |        |         |   |                                                                                  |

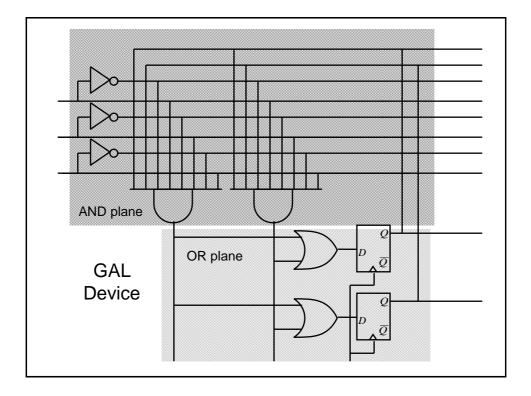

## GAL Devices

- They are similar in concept to PALs, but have the option to make use of a D-type flipflops in the OR plane (one following each OR gate). In addition, the outputs from the Dtypes are also made available to the AND plane (in addition to the usual inputs)

- Consequently it becomes possible to build programmable sequential logic circuits

## FPGA

- Field Programmable Gate Array (FPGA) devices are the latest type of programmable logic

- Are a sea of programmable wiring and function blocks controlled by bits downloaded from memory

- Function units contain a 4-input 1 output lookup table with an optional D-FF on the output