At early stages of design exploration, we may not know anything about the target technology. We do not wish to insert arbitrary delay figures in our source code, yet some sort of delay is needed to make synchronous hardware work correctly. The solution is the delta cycle.

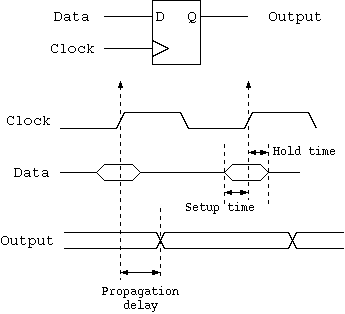

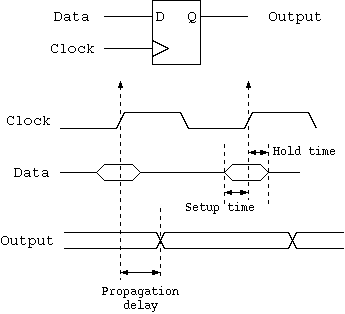

The following figure is replicated from elsewhere in the printed notes:

For correct behaviour of synchronous edge-triggered hardware, the propagation delay of D-types must be greater than their hold time.

Question : How can we ensure this in a technology-neutral model that does not have any specific numerical delays ?

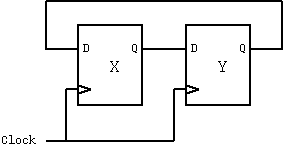

// Example: swap data between a pair of registers

reg [7:0] X, Y;

always @(posedge clock) begin

X <= Y;

Y <= X;

end

// E.g. if X=3 and Y=42 then Y becomes 3 and X becomes 42.

|  |

Answer: Hardware simulators commonly support the compute/commit or `signal' paradigm for non-blocking updates. The signal has current and next values.

| 37: (C) 2008-16, DJ Greaves, University of Cambridge, Computer Laboratory. | Flash Player Upgrade Needed |