HOME

UP

PREV

FURTHER NOTES

NEXT (Deep submicron and Dark Silicon)

90 Nanometer Gate Length.

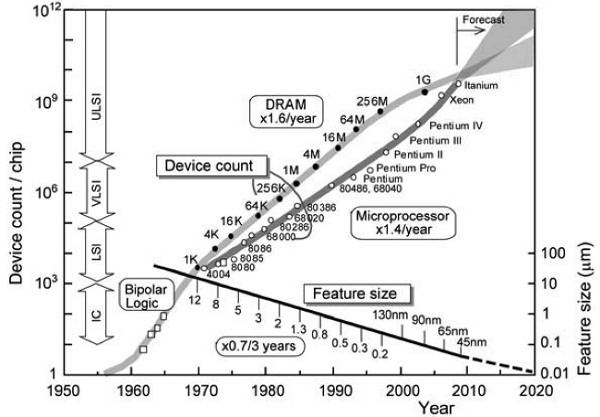

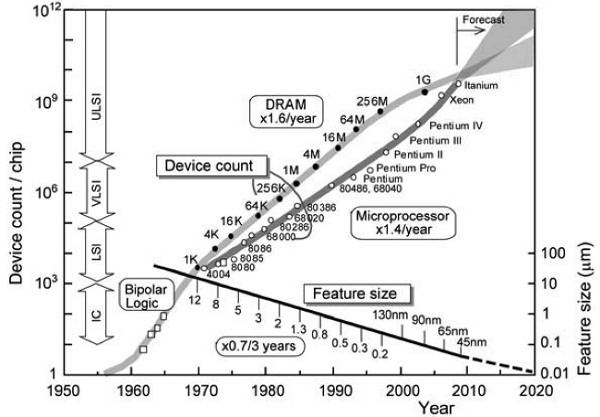

The mainstream VLSI technology in the period 2004-2008 was 90 nm.

Now the industry is using 22 nanometer and smaller.

Parameters from a 90 nanometer standard cell library:

| Parameter | Value | Unit |

| Drawn Gate Length | 0.08 | µm |

| Metal Layers | 6 to 9 | layers |

| Max Gate Density | 400K | gates/mm² |

| Finest Track Width | 0.25 | µm |

| Finest Track Spacing | 0.25 | µm |

| Tracking Capacitance | 1 | fF/mm |

| Core Supply Voltage | 0.9 to 1.4 | V |

| FO4 Delay | 51 | ps |

| Leakage current | | nA/gate |

|  |

Typical processor core: 200k gates + 4 RAMs: one square millimeter.

Typical SoC chip area is 50-100 mm² → 20-40 million gates (semi-custom/standard cell).

Actual gate and transistor counts are higher owing to full-custom blocks (RAMs mainly).

- 2007: Dual-core Intel Itanium2: 1.6 billion transistors (90 nm).

- 2010: 8-core Intel Nehalem: 2.3 billion transistors (45 nm).

- 2010: Altera Stratix IV FPGA: 2.5 billion transistors (40 nm).

- 2015: Intel Latest CPU: circa 10 billion transistors (19 nm).

» Moore's Law » Transistor Count

»Dimension Increase in Metal-Oxide-Semiconductor Memories and Transistors

Technology Scaling Prediction.