The bus protocol in the earlier slides that used addr, hwen, hren, wdata and rdata does not tolerate registering for reads, but if a ready or other acknowledgement signal were added, it would be like the four phase handshake and work correctly, but poorly for long distances over the chip.

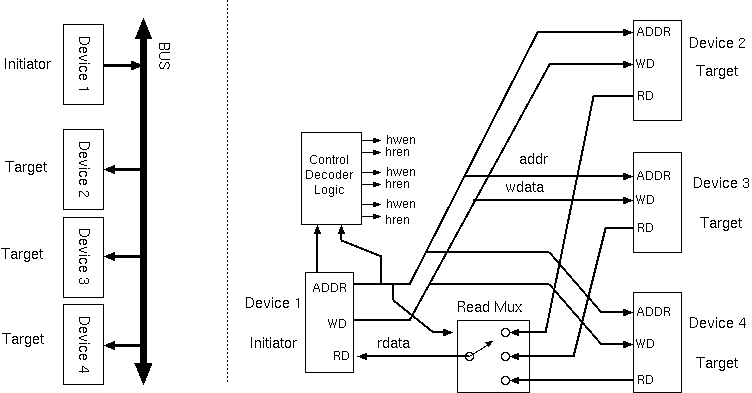

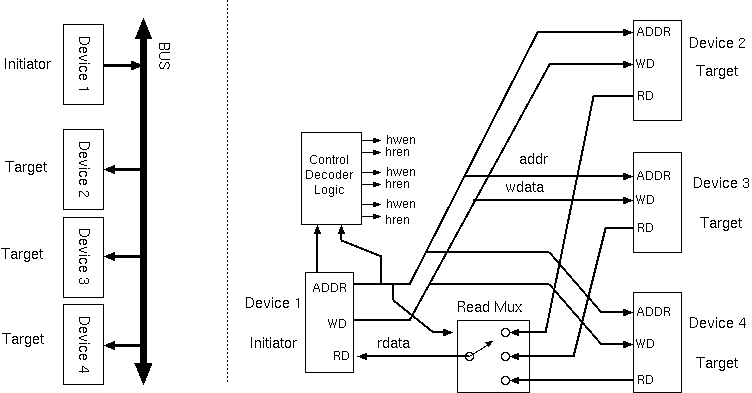

Basic bus illustration: one initiator and three targets.

No tri-states are used: address and write data outputs use wire joints or buffers, read data uses multiplexors.

There is only one initiator, so no bus arbitration is needed.

Max throughput is unity (i.e. one word per clock tick).

Typical SoC bus capacity: 32 bits × 200 MHz = 6.4 Gb/s, but owing to protocol degrades with distance. This figure can be thought of as unity (i.e. one word per clock tick) in comparisons with other configurations we shall consider.

The interrupt wiring is not shown. If device 1 is a processor, it might have a dedicated interrupt wire from each other device.

| 70: (C) 2008-16, DJ Greaves, University of Cambridge, Computer Laboratory. |