# System on Chip Design and Modelling

University of Cambridge Computer Laboratory Lecture Notes

# Dr. David J Greaves

(C) 2012-13 All Rights Reserved DJG.

Part II Computer Science Tripos Michaelmas Term 2013/14 CST-II SoC D/M Lecture Notes 2013/14

- (1) Verilog RTL: Modules, Protocols and Interfaces

- (2) SystemC: Hardware Modelling Library

- (3) Basic SoC Components

- (4) ESL: Electronic System Level Modelling

- (5) ABD: Assertion-Based Design

- (6) SoC Engineering and Associated Tools

# 0.0.1 SoC Design: 2013/14: Twelve Lectures for CST Part II

A current-day system on a chip (SoC) consists of several different microprocessor subsystems together with memories and I/O interfaces. This course covers SoC design and modelling techniques with emphasis on architectural exploration, assertion-driven design and the concurrent development of hardware and embedded software. This is the "front end" of the design automation tool chain. (Back end material, such as design of individual gates, layout, routing and fabrication of silicon chips is not covered.)

A percentage of each lecture is used to develop a running example. Over the course of the lectures, the example evolves into a System On Chip demonstrator with CPU and bus models, device models and device drivers. All code and tools are available online so the examples can be reproduced and exercises undertaken. The main languages used are Verilog and C++ using the SystemC library.

This course has seven main topics (SG1-SG7) and an optional final section on high-level synthesis may be lectured if time permits.

In addition to these topics, the running example will demonstrate a few practical aspects of device bus interface design, on chip communication and device control software. Students can run the examples on PWF or their own machine (please ask for links).

# 0.0.2 Recommended Reading

Subscribe for webcasts from 'Design And Reuse': www.design-reuse.com

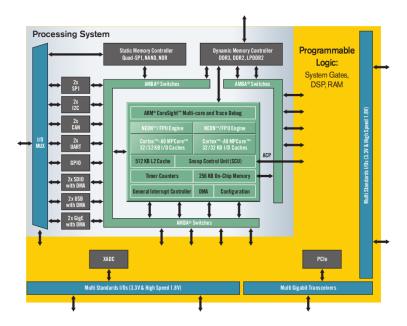

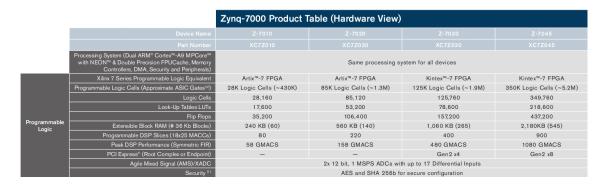

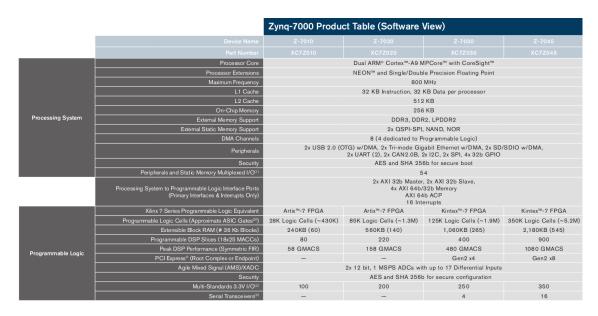

Multicore field-programmable SoC: Xilinx Zync Product Brief

Atmel, ARM-based Embedded MPU AT91SAM Datasheet

OSCI. System C tutorials and white papers . Download from OSCI www.accelera.org or copy from course web site.

Brian Bailey, Grant Martin. ESL Models and Their Application: Electronic System Level Design. Springer.

Ghenassia, F. (2006). Transaction-level modeling with SystemC: TLM concepts and applications for embedded systems. Springer.

Eisner, C. & Fisman, D. (2006). A practical introduction to PSL. Springer (Series on Integrated Circuits and Systems).

Foster, H.D. & Krolnik, A.C. (2008). Creating assertion-based IP. Springer (Series on Integrated Circuits and Systems).

Grotker, T., Liao, S., Martin, G. & Swan, S. (2002). System design with SystemC. Springer.

Wolf, W. (2002). Modern VLSI design (System-on-chip design). Pearson Education. LINK.

# 0.0.3 Introduction: What is a SoC?

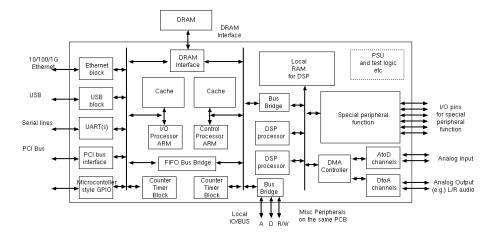

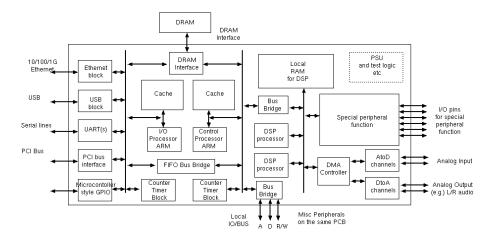

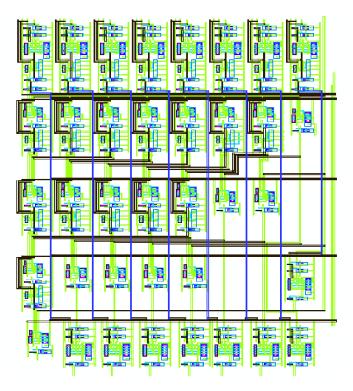

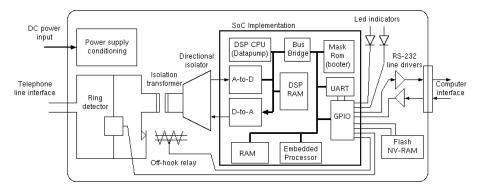

Figure 1: Block diagram of a multi-core 'platform' chip, used in a number of networking products.

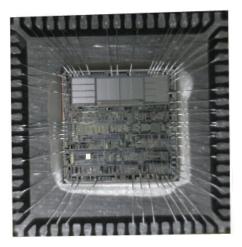

A System On A Chip: typically uses 70 to 140 mm<sup>2</sup> of silicon.

Multicore field-programmable SoC Xilinx Product Brief: PDFAtmel ARM-Based Platform Chip: PDF

A SoC is a complete system on a chip. A 'system' includes a microprocessor, memory and peripherals. The processor may be a custom or standard microprocessor, or it could be a specialised media processor for sound, modem or video applications. There may be multiple processors and also other generators of bus cycles, such as DMA controllers. DMA controllers can be arbitrarily complex, and are really only distinguished from processors by their complete or partial lack of instruction fetching.

Processors are interconnected using a variety of mechanisms, including shared memories and message-passing hardware entities such as specialised channels and mailboxes.

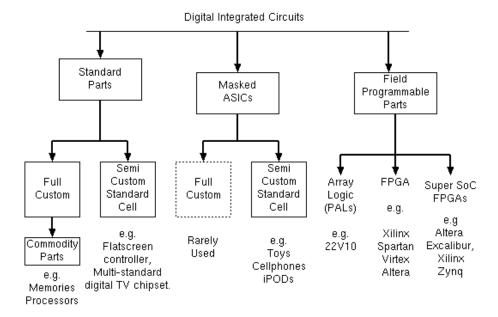

SoCs are found in every consumer product, from modems, mobile phones, DVD players, televisions and iPODs.

# 0.1 Design Flow

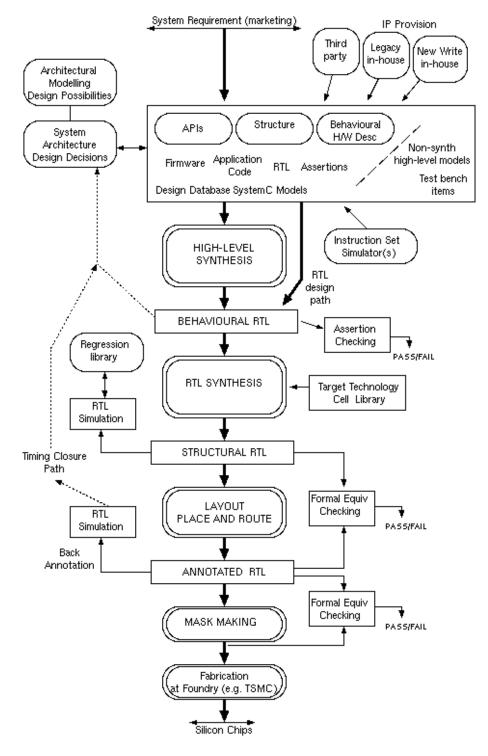

Design flow is divided by the **Structural RTL** level into:

- Front End: specify, explore, design, capture, synthesise  $\leadsto$  Structural RTL

- Back End: Structural RTL  $\leadsto$  place, route, mask making, fabrication.

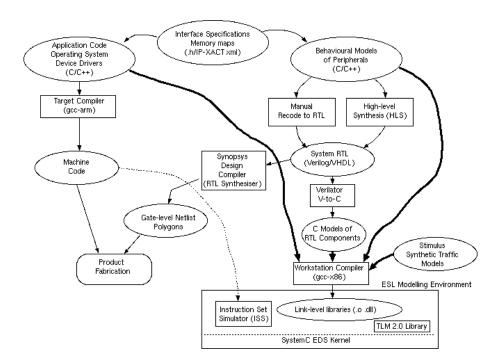

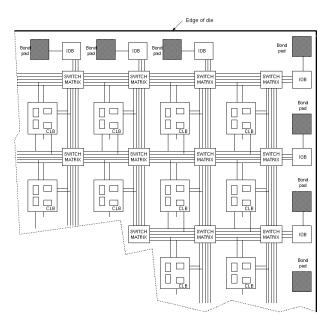

Figure 3 shows a typical design and maufacturing flow that leads from design capture to SoC fabrication.

#### 0.1.1 Front End

The design must be specified in terms of high-level requirements, such as function, throughput and power consumption.

Design capture: it is transferred from the marketing person's mind, back of envelope or or wordprocessor document into machine-readable form.

Architectural exploration will try different combinations of processors, memories and bus structures to find an implementation with good power and load balancing. A loosely-timed high-level model is sufficient to compute the performance of an architecture.

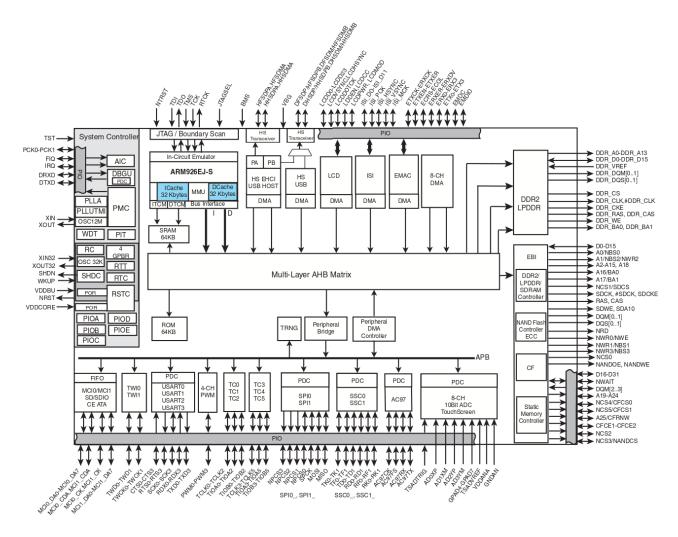

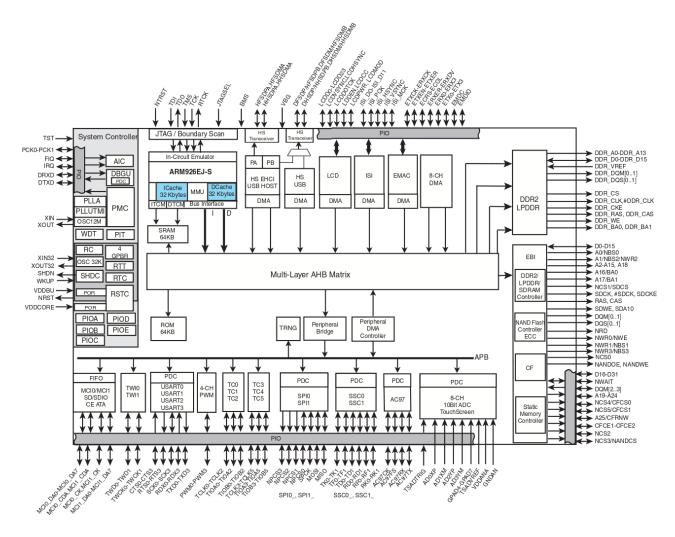

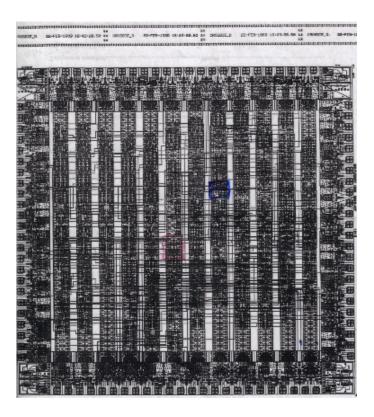

Figure 2: Platform Chip Example: Atmel SAM Series 9645.

Detailed design will select IP (interlectual property) providers for all of the functional blocks, or else they will exist from previous in-house designs and can be used without license fees, or else freshly written.

Logic synthesis will convert from behavioural RTL to structural RTL. Synthesis from formal high-level forms, including C,C++, SysML statecharts, formal specifications of interfaces and behaviour is beginning to be used.

Instruction set simulators (ISS) for embedded processors are needed: purchased from third parties such as ARM and MIPS, or as a by-product of custom processor design.

The interface specifications (register maps and other APIs) between components need to be stored: the IP-XACT format may be used.

High-level models that are never intended to be synthesisable and test bench components will also be coded, typically using SystemC.

#### 0.1.2 Back End

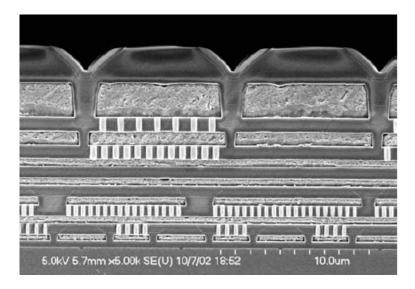

After RTL synthesis using a target technology library, we have a structural netlist that has no gate delays. Place and route gives 2-D co-ordinates to each component, adds external I/O pads and puts wiring between the components. RTL annotated with actual implementation gate delays gives a precise power and performance model. If performance is not up to par, design changes are needed.

Fabrication of masks is commonly the most expensive single step (e.g. one million pounds), so must be correct first time.

Fabrication is performed in-house by certain large companies (e.g. Intel, Samsung) but most companies use foundaries (UMC, TSMC).

At all stages (front and back end), a library of standard tests will be run every night and any changes that cause a previously-passing test to fail (regressions) will be automatically reported to the project manager.

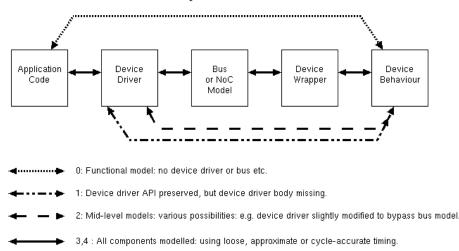

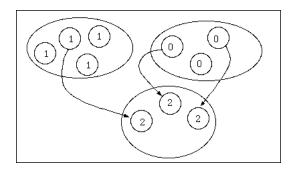

# 0.1.3 Levels of Modelling Abstraction

Our modelling system must support all stages of the design process, from design entry to fabrication. We need to mix components using different levels of abstraction in one simulation setup.

Levels commonly used are:

- Functional Modelling: The 'output' from a simulation run is accurate.

- Memory Accurate Modelling: The contents and layout of memory is accurate.

- Untimed TLM: No time stamps recorded on transactions.

- Loosely-timed TLM: The number of transactions is accurate, but order may be wrong.

- Approximately-timed TLM: The number and order of transactions is accurate.

- Cycle-Accurate Level Modelling: The number of clock cycles consumed is accurate.

- Event-Level Modelling: The ordering of net changes within a clock cycle is accurate.

Other terms in use are:

- **Programmer View Accurate:** The contents of visible memory and registers is as per the real hardware, but timing may be inaccurate and other registers or combinational nets that are not designated as part of the 'programmers view' may not be modelled accurately.

- Behavioural Modelling: Using a threads package, or other library (e.g. SystemC), hand-crafted programs are written to model the behaviour of each component or subsystem. Major hardware items such as busses, caches or DRAM controllers may be neglected in such a model.

The Programmer's View is often abbreviated as 'PV' and if timing is added it is called 'PV+T'.

The Programmer's View contains only architecturally-significant registers such as those that the software programmer can manipulate with instructions. Other registers in a particular hardware implementation, such as pipeline stages and holding registers to overcome structural hazards, are not part of the PV.

Figure 3: Design and Manufacturing Flow for SoC.

# SG 1 — Verilog RTL: Modules, Protocols and Interfaces

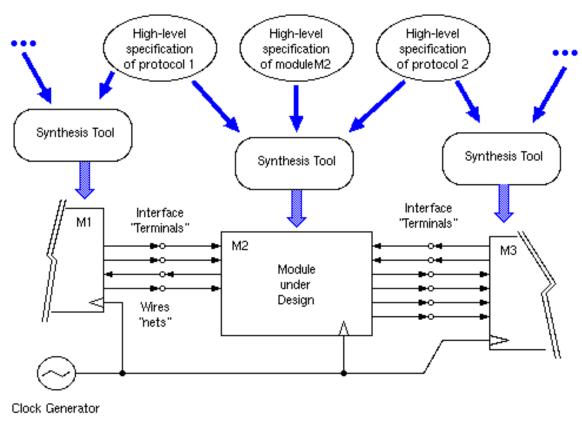

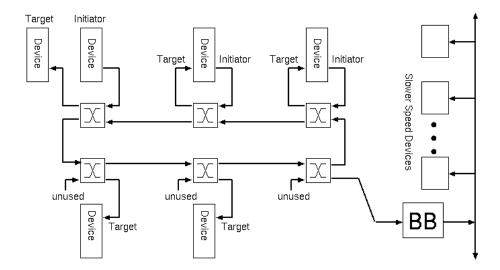

A hardware design consists of a number of modules interconnected by wires known as 'nets' (short for networks). The interconnections between modules are typically structured as mating interfaces. An interface nominally consists of a number of terminals but these have no physical manifestation.

In a modern design flow, the protocol at an interface is specified once in a master file that is imported for the synthesis of each module that sports it.

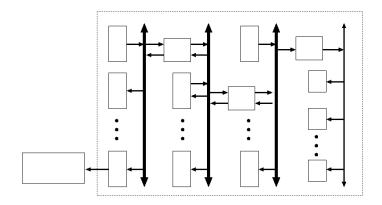

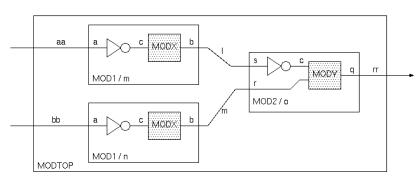

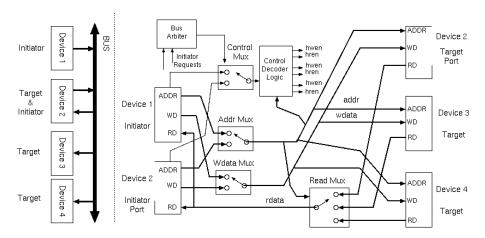

Figure 1.1: Generic (net-level) Module Interconnection Using Protocols and Interfaces.

A clock domain is a set of modules and a clock generator. Within a synchronous clock domain all flip-flops have their clocks commoned.

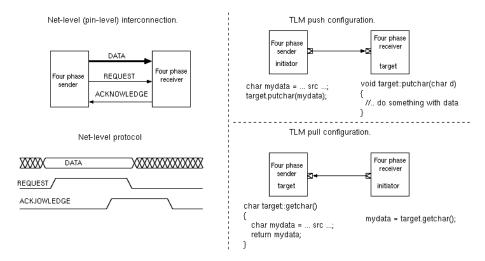

# 1.0.4 Protocol and Interface

At the electrical/net level, a **port** consists of an **interface** and a **protocol**. The interface is the set of pins or wires that connect the components. The protocol defines the rules for changing the logic levels and the meaning of the associated data. For example, an asynchronous interface might be defined in RTL as:

```

Transmit view of interface: Receive view of interface: // This is a four-phase asynchronous interface output [7:0] data; input [7:0] data; // where the idle state has strobe and ack output strobe; input strobe; // deasserted (low) and data is valid while input ack; output ack; // the strobe signal is asserted (high).

```

Ports commonly implement **flow-control** by handshaking. Data is only transferred when both the sender and receiver are happy to proceed.

A port generally has an **idle** state which it returns to between each transaction. Sometimes the start of one transaction is immediately after the end of the previous, so the transition through the idle state is only nominal. Sometimes the beginning of one transaction is temporally overlaid with the end of a previous, so the transition through idle state has no absolute time associated with it.

#### Additional notes: There are four basic clock strategies for an interface: Left Side Right Side Clocked Synchronous (such as Xilinx LocalLink) 1. Clocked 2. Clocked Different clock Clock Domain Crossing (see later) 3. Clocked Asynchronous Hybrid. 3. Asynchronous Clocked Hybrid (swapped). 4. Asynchronous Asynchronous Asynchronous (such a four-phase parallel port)

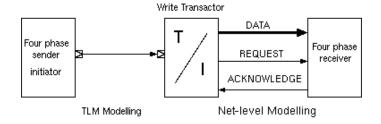

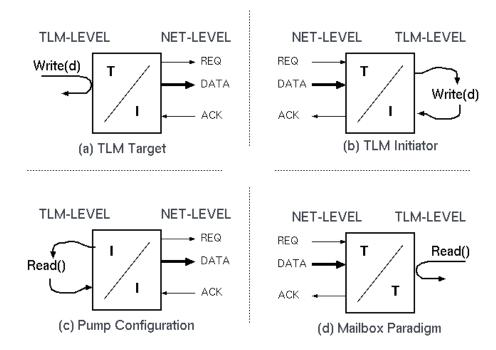

# 1.0.5 Transactional Handshaking

The mainstream RTL languages, Verilog and VHDL, do not provide synthesis of handshake circuits (but this is one of the main innovations in Bluespec). We'll use the word **transactional** for protocol+interface combinations that support flow-control. If synthesis tools are allowed to adjust the delay through components, all interfaces between components must be transactional and the tools must understand the protocol semantic.

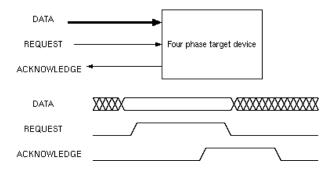

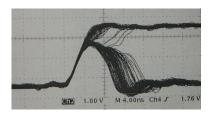

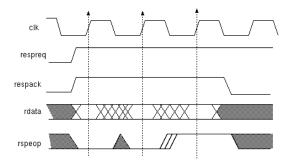

Figure 1.2: Timing diagram for an asynchronous, four-phase handshake.

Here are two imperative (behavioural) methods (non-RTL) that embody the protocol for Figure 1.2:

```

//Output transactor:

putbyte(char d)

{

wait_until(!ack); // spin till last complete.

data = d;

settle(); // delay longer than longest data delay

req = 1;

wait_until(ack);

req = 0;

}

```

```

//Input transactor:

char getbyte()

{

wait_until(req);

char r = data;

ack = 1;

wait_until(!req);

ack = 0;

return r;

}

```

Code like this is used to perform programmed IO (PIO) on GPIO pins (see later). It can also be used as an ESL transactor (see later). It's also sufficient to act as a formal specification of the protocol.

# 1.0.6 Transactional Handshaking in RTL (Synchronous Example)

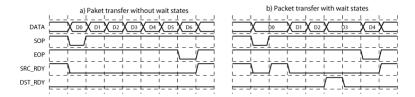

A more complex example is the LocalLink protocol from Xilinx. This is a synchronous packet proctocol (compare with the asynchronous four-phase handshake just described).

Like the four-phase handshake, LocalLink has contra-flowing request and acknowledge signals. But data is not

qualified by a request transition: instead it is qualified as valid on **any positive clock edge where both request and acknowledge are asserted**. The interface nets for an eight-bit transmitting interface are:

Figure 1.3: Timing diagram for the synchronous LocalLink protocol.

Start and end of frame signals delimit the packets. All control signals are active low (denoted with the underscore n suffix).

#### Additional notes:

Here is a data source in Verilog RTL for LocalLink that generates a stream of packets containing arbitrary data with arbitrary gaps.

```

module LocalLinkSrc( reset,

clk,

src_data,

src_sof_n,

src_eof_n,

src_src_rdy_n,

src_dst_rdy_n);

input reset;

input clk;

output [7:0] src_data;

output src_sof_n;

output src_eof_n;

output src_src_rdy_n;

input src_dst_rdy_n;

// The source generates 'random' data using a pseudo random sequence generator (prbs).

// The source also makes gaps in its data using bit[9] of the generator.

reg [14:0] prbs;

started;

reg

assign src_data = (!src_src_rdy_n) ? prbs[7:0] : 0;

assign src_src_rdy_n = !(prbs[9]);

// The end of packet is arbitrarily generated when bits 14:12 have a particular value.

assign src_eof_n = !(!src_src_rdy_n && prbs[14:12]==2);

// A start of frame must be flagged during the first new word after the previous frame has ended.

assign src_sof_n = !(!src_src_rdy_n && !started);

always @(posedge clk) begin

started <= (reset) ? 0: (!src_eof_n) ? 0 : (!src_sof_n) ? 1 : started;</pre>

prbs <= (reset) ? 100: (src_dst_rdy_n) ? prbs: (prbs << 1) | (prbs[14] != prbs[13]);</pre>

endmodule

```

And here is a corresponding data sink:

```

module LocalLinkSink(reset,

clk,

sink_data,

sink_sof_n,

sink_eof_n,

sink_src_rdy_n,

sink_dst_rdy_n);

input reset;

input clk;

input [7:0] sink_data;

input sink_sof_n;

input sink_eof_n;

output sink_src_rdy_n;

input sink_dst_rdy_n;

// The sink also maintains a prbs to make it go busy or not on an arbitrary basis.

reg [14:0] prbs;

assign sink_dst_rdy_n = prbs[0];

always @(posedge clk) begin

if (!sink_dst_rdy_n && !sink_src_rdy_n) $display(

"%m LocalLinkSink sof_n=%d eof_n=%d data=0x%h", sink_sof_n, sink_eof_n, sink_data);

// Put a blank line between packets on the console.

if (!sink_dst_rdy_n && !sink_src_rdy_n && !sink_eof_n) $display("\n\n");

prbs <= (reset) ? 200: (prbs << 1) | (prbs[14] != prbs[13]);

endmodule // LocalLinkSrc

```

### Additional notes:

And here is a testbench that wires them together:

```

module SIMSYS():

reg reset:

reg clk;

wire [7:0] data;

wire sof_n;

wire eof_n;

wire ack_n;

wire req_n;

// Instance of the src

LocalLinkSrc src (.reset(reset),

.clk(clk),

.src data(data).

.src_sof_n(sof_n),

.src_eof_n(eof_n),

.src_src_rdy_n(req_n)

.src_dst_rdy_n(ack_n));

// Instance of the sink

LocalLinkSink sink (.reset(reset),

.clk(clk),

.sink_data(data),

.sink_sof_n(sof_n),

.sink_eof_n(eof_n),

.sink_src_rdy_n(req_n),

. \verb|sink_dst_rdy_n(ack_n)|

initial begin clk =0; forever #50 clk = !clk; end

initial begin reset = 1; #130 reset=0; end

endmodule // SIMSYS

```

# 1.1 RTL: Register Transfer Language

Everybody attending this course is expected to have previously studied RTL coding or at least taught themselves the basics before the course starts.

The Computer Laboratory has an online Verilog course you can follow:

Cambridge SystemVerilog Tutor Please not that this now covers 'System Verilog' whereas most of my examples are in plain old Verilog. There are some syntax differences.

# 1.1.1 RTL Summary View of Variant Forms.

From the point of view of this course, Verilog and VHDL are completely equivalent as register transfer languages (RTLs). Both support simulation and synthesis with nearly-identical paradigms. Of course, each has its proponent's.

Synthesisable Verilog constructs fall into these classes:

- 1. Structural RTL enables an hierarchic component tree to be instantiated and supports wiring (a netlist) between components.

- 2. Lists of pure (unordered) register transfers where the r.h.s. expressions describe potentially complex logic using a rich set of integer operators, including all those found in software languages such as C++ and Java. There is one list per synchronous clock domain. A list without a clock domain is for combinational logic (continuous assignments).

• 3. Synthesisable behavioural RTL uses a thread to describe behaviour where a thread may write a variable more than once. A thread is introduced with the 'always' keyword.

However, standards for synthesisable RTL greatly restrict the allowable patterns of execution: they do not allow a thread to leave the module where it was defined, they do not allow a variable to be written by more than one thread and they can restrict the amount of event control (i.e. waiting for clock edges) that the thread performs.

The remainder of the language contains the so-called 'non-synthesisable' constructs.

#### Additional notes:

All the time values in the RTL are ignored for synthesis and zero-delay components are synthesisable. For them also to be simulatable in a deterministic way the simulator core implements the **delta cycle** mechanism.

One can argue that anything written in RTL that describes deterministic and finite-state behaviour ought to be synthesisable. However, this is not what the community wanted in the past: they wanted a simple set of rules for generating hardware from RTL so that engineers could retain good control over circuit structures from what they wrote in the RTL.

Today, one might argue that the designer/programmer should not be forced into such low-level expression or into the excessively-parallel thought patterns that follow on. Certainly it is good that programmers are forced to express designs in ways that can be parallelised, but the tool chain perhaps should have much more control over the details of allocation of events to clock cycles and the state encoding.

RTL synthesis tools are not normally expected to re-time a design, or alter the amount of state or state encodings. Newer languages and flows (such as Bluespec and Kiwi) still encourage the user to express a design in parallel terms, yet provide easier to use constructs with the expectation that detailed timing and encoding might be chosen by the tool.

#### Level 1/3: Structural Verilog: a structural netlist with hierarchy.

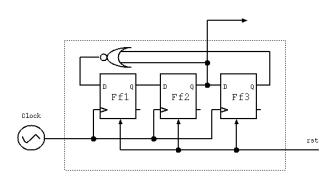

Figure 1.4: The circuit described by our structural example (a divide-by-five, synchronous counter).

Just a netlist. There are no assignment statements that transfer data between registers in structural RTL (but it's still a form or RTL).

Figure 1.5 shows structural RTL before and after flattening as well as a circuit diagram showing the component boundaries.

2a/3: Continuous Assignment: an item from a pure RT list without a clock domain.

# Heirarchic Netlist

```

module MOD1(output b, input a);

wire c;

INV inv1(c, a);

MODX modx1(b, c);

endmodule

module MOD2(output q, input s, input r);

wire c;

INV inv2(c, s);

MODY mody1(q, c, r);

endmodule

module MODTOP(output rr, input aa, input bb);

wire I, m;

MOD1 m(l, aa);

MOD1 n(m, bb);

MOD2 o(rr, I, m);

endmodule

```

# **Equivalent Flattened Netlist**

```

module MODTOP (output rr, input aa, input bb);

wire I, m;

wire m_c, n_c, o_c;

INV m_inv1(m_c, aa);

INV o_inv2(o_c, l);

MODX m_modx1(m_c, l);

MODX n_modx1(m_c, m);

MODY o_mody1(rr, o_c, m);

endmodule

For many designs the

flattened netlist is often bigger than the

hierarchic netlist owing

to multiple instances

of the same component.

Here it was smaller.

```

Figure 1.5: Example RTL fragment, before and after flattening.

```

// Continuous assignments define combinational logic circuit:

assign a = (g) ? 33 : b * c;

assign b = d + e;

```

- Order of continuous assignments is un-important,

- Loop free, otherwise: parasitic level-sensitive latches are formed (e.g. RS latch),

- Right-hand side's may range over rich operators (e.g. mux ?: and multiply \*),

- Bit inserts to vectors are allowed on left-hand sides (but not combinational array writes).

```

assign d[31:1] = e[30:0];

assign d[0] = 0;

```

#### **2b/3: Pure RTL:** unordered synchronous register transfers.

Two coding styles (it does not matter whether these transfers are each in their own always statement or share over whole clock domain):

```

always @(posedge clk) a <= b ? c + d;

always @(posedge clk) b <= c - d;

always @(posedge clk) c <= 22-c;

```

```

always @(posedge clk) begin

a <= b ? c + d;

b <= c - d;

c <= 22-c;

end

```

Typical example (illustrating pure RT forms):

Registers are assigned in clock domains (one shown called 'mainclk'). Each register is assigned in exactly one clock domain. RTL synthesis does not generate special hardware for clock domain crossing (described later).

In a stricter form of this pure RTL, we cannot use 'if', so when we want a register to sometime retain its current value we must assign this explicitly, leading to forms like this:

```

oldcount <= (din) ? count : oldcount;

```

#### 3/3: Behavioural RTL: a thread encounters order-sensitive statements.

In 'behavioural' expression, a thread, as found in imperative languages such as C and Java, assigns to variables, makes reference to variables already updated and can re-assign new values.

For example, the following behavioural code

```

if (k) foo = y;

bar = !foo;

```

can be compiled down to the following, unordered 'pure RTL':

```

foo <= (k) ? y: foo;

bar <= !((k) ? y: foo);

```

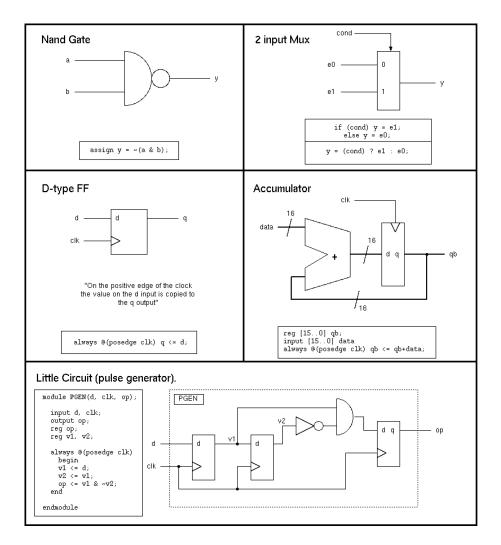

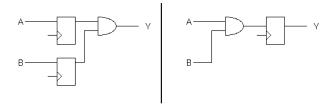

Figure 1.6 shows synthesisable Verilog fragments as well as the circuits typically generated.

The RTL languages (Verilog and VDHL) are used both for simulation and synthesis. Any RTL can be simulated but only a subset is standardised as 'synthesisable' (although synthesis tools can generally handle a slightly larger synthesisable subset).

Simulation uses a top-level test bench module with no inputs.

Synthesis runs are made using points lower in the hierarchy as roots. We should certainly leave out the test-bench wrapper when synthesising and we typically want to synthesise each major component separately.

Figure 1.6: Elementary Synthesisable Verilog Constructs

### 1.1.2 Synthesisable RTL

#### Additional notes:

Abstract syntax for a synthesisable RTL (Verilog/VHDL) without provision for delays:

Expressions:

```

datatype ex_t =

// Expressions:

Num of int

integer constants

Net of string

net names

Not of ex_t

!x - logical not

Neg of ex_t

- one's complement

g?t:f - conditional expression

Query of ex_t * ex_t * ex_t

//

Diadic of diop_t * ex_t * ex_t

a+b

- diadic operators + - * / << >>

a[b] - array subscription, bit selection.

Subscript of ex_t * ex_t

//

```

Imperative commands (might also include a 'case' statement) but no loops.

Our top level will be an unordered list of the following sentences:

The abstract syntax tree for synthesisable RTL supports a rich set of expression operators but just the assignment and branching commands (no loops). (Loops in synthesisable VHDL and Verilog are restricted to so-called structural generation statements that are fully unwound by the compiler front end and so have no data-dependent exit conditions).

An example of RTL synthesis:

Results in structural RTL netlist:

```

Example input:

```

```

module TC(clk, cen);

input clk, cen;

reg [1:0] count;

always @(posedge clk) if (cen) count<=count+1;

endmodule</pre>

```

```

module TC(clk, cen);

wire u10022, u10021, u10020, u10019;

wire [1:0] count;

input cen; input clk;

CVINV i10021(u10021, count[0]);

CVMUX2 i10022(u10022, cen, u10021, count[0]);

CVDFF u10023(count[0], u10022, clk, 1'b1, 1'b0, 1'b0);

CVXOR2 i10019(u10019, count[0], count[1]);

CVMUX2 i10020(u10020, cen, u10019, count[1]);

CVDFF u10024(count[1], u10020, clk, 1'b1, 1'b0, 1'b0);

endmodule

```

Here the behavioural input was converted to an implementation technology that included inverters, multiplexors, D-type flip-flops and XOR gates. For each gate, the output is the first-listed terminal.

#### Verilog RTL Synthesis Algorithm: 3-Step Recipe:

1. First we remove all of the blocking assignment statements to obtain a 'pure' RTL form. For each register we need exactly one assignment (that becomes one hardware circuit for its input) regardless of however many times it is assigned, so we need to build a multiplexor expression that ranges over all its sources and is controlled by the conditions that make the assignment occur.

```

For example:  \begin{array}{c} \text{if (a) b = c;} \\ d = b + e; \\ \text{if (q) d = 22;} \end{array} \text{ is converted to } \begin{array}{c} b <= (a) ? c : b; \\ d <= q ? 22 : ((a) ? c : b) + e; \end{array}

```

2. For each register that is more than one bit wide we generate separate assignments for each bit. This is colloquially known as 'bit blasting'. This stage removes arithmetic operators and leaves only boolean

operators. For example, if v is three bits wide and a is two bits wide:

```

v <= (a) ? 0: (v>>1) is

```

converted to

```

v[0] <= (a[0]|a[1]) ? 0: v[1];

v[1] <= (a[0]|a[1]) ? 0: v[2];

v[2] <= 0;

```

3. Build a gate-level netlist using components from the selected library of gates. (Similar to a software compiler when it matches operations needed against instruction set.) Sub-expressions are generally reused, rather than rebuilding complete trees. Clearly, logic minimization (Karnaugh maps and Espresso) and multi-level logic techniques (e.g. ripple carry versus fast carry) as well as testability requirements affect the chosen circuit structure.

#### Additional notes:

How can we make a simple adder?

The following ML fragment will make a ripple carry adder from lsb-first lists of nets:

```

fum add c (nil, nil) = [c]

| add c (a::at, b::bt) =

let val s = gen_xor(a, b)

val c1 = gen_and(a, b)

val c2 = gen_and(s, c)

in (gen_xor(s, c))::(add (gen_or(c2, c1)) (at, bt))

end

```

Can division be bit-blasted? Yes, and for some constants it is quite simple.

For instance, division by a constant value of 8 needs no gates - you just need wiring! For dynamic shifts make a **barrel shifter** using a succession of broadside multiplexors, each operated by a different bit of the shifting expression. See link Barrel Shifter, ML fragment.

To divide by a constant 10 you can use that 8/10 is 0.11001100 recurring, so if n and q are 32 bit unsigned registers, the following computes n/10:

```

q = (n >> 1) + (n >> 2);

q += (q >> 4);

q += (q >> 8);

q += (q >> 16);

return q>>3;

```

There are three ML fragments on the course web site that demonstrate each step of this recipe: 1: pure conversion 2: bit-blasting 3: gate building (The details of the algorithms and being able to reproduce them is not examinable but being able to draw the gate-level circuit for a few lines of RTL is examinable).

# 1.1.3 Behavioural - 'Non-Synthesisable' RTL

Not all RTL is officially synthesisable, as defined by language standards. However, commercial tools tend to support larger subsets than officially standardised.

RTL with event control in the body of a thread defines a state machine. This is compilable by some tools. This state machine requires a program counter (PC) register at runtime (implied):

```

input clk, din;

output req [3:0] q;

always begin

q <= 1;

@(posedge clk) q <= 2;

if (din) @(posedge clk) q <= 3;

q <= 4;

end</pre>

```

How many bits of PC are needed? Is conditional event control synthesisable? Does the output 'q' ever take on the value 4?

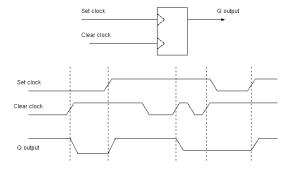

As a second non-synthesisable example, consider the dual-edge-triggered flip-flop in Figure 1.7.

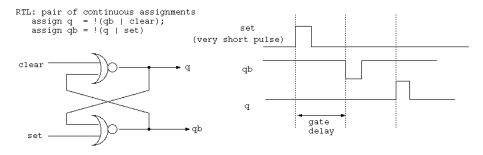

Figure 1.7: Schematic symbol and timing diagram for an edge-triggered RS flop.

```

reg q;

input set, clear;

always @(posedge set) q = 1;

always @(posedge clear) q = 0;

```

Here a variable is updated by more than one thread. This component is used mainly in specialist phase-locked loops. It can be modelled in Verilog, but is **not** supported for Verilog synthesis. A real implementation typically uses 8 or 12 NAND gates in a relatively complex arrangement. We do not expect general-purpose logic synthesis tools to create such circuits: they were hand-crafted by experts of previous decades.

Figure 1.8: Possible circuit for the edge-triggered RS flop.

Another common source of non-synthesisable RTL code is testbenches. Testbenches commonly uses delays:

```

// Typical RTL testbench contents:

reg clk, reset;

initial begin clk=0; forever #5 clk = !clk; end // Clock source 100 MHz

initial begin reset = 1; # 125 reset = 0; end // Power-on reset generator

```

# 1.1.4 Further Synthesis Issues

There are many combinational circuits that have the same functionality. Synthesis tools can accept additional guiding metrics from the user, that affect

- Power consumption,

- Area use,

- Performance,

- Testability.

(The basic algorithm in the additional material does not consider any guiding metrics.)

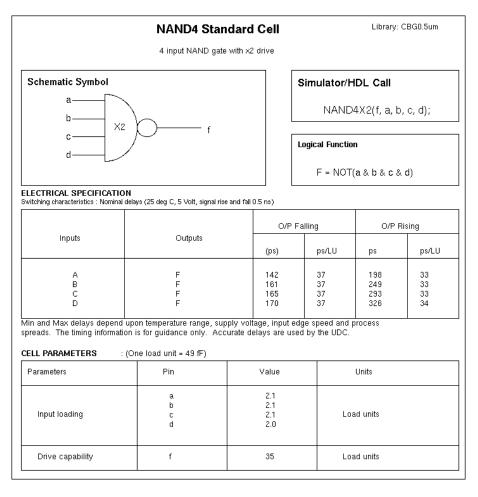

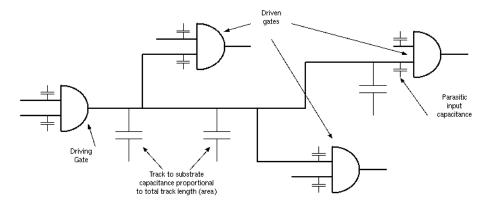

Gate libraries have high and low drive stength forms of most gates (see later). The synthesis tool will chose the appropriate gate depending on the fanout and (estimated) net length during routing. Some leaf cells are broadside and do not require bit-blasting.

The tool will use Quine/McCluskey, Espresso or similar for logic minimisation. Liberal use of the 'x' don't care designation in the source RTL allows the synthesis tool freedom to perform this logic minimisation. (Read up on 'Synopsys Evil Twins' FULL\_CASE and PARALLEL\_CASE if interested.)

```

reg[31:0] y;

... if (e1) y <= e2; else if (e3) y <= e4; else y <= 32'bx; // Note, assignment of 'x' permits automated logic minimisation.

```

Can share sub-expressions or re-compute expressions locally. Reuse of sub-expressions is important for locally-derived results, but with today's VLSI, sending a 32 bit addition result more than one millimeter on the chip may use more power then recomputing it locally! Can re-encode state (see later).

### 1.1.5 Conventional RTL Compared with Software

Synthesisable RTL (SRTL) looks a lot like software at first glance, but we soon see many differences.

SRTL is statically allocated and defines a finite-state machine.

Threads do not leave their starting context and all communication is through shared variables that denote wires.

There are no thread synchronisation primitives, except to wait on a clock edge.

Each variable must be updated by at most one thread.

Software on the other hand uses far fewer threads: just where needed. The threads may pass from one module to another and thread blocking is used for flow control of the data.

SRTL requires the programmer to think in a massively-parallel way and leaves no freedom for the execution platform to reschedule the design.

RTL is not as expressive for algorithms or data structures as most software programming languages.

The concurrency model is that everything executes in lock-step. The programmer keeps all this concurrency in his/her mind.

Users must generate their own, bespoke handshaking and flow control between components.

Higher-level entry forms are ideally needed, perhaps schedulling within a thread at compile-time and between threads at run time ? (See Bluespec and HLS remarks).

# 1.1.6 Logic Synthesis from Guarded Atomic Actions (Bluespec)

Using guarded atomic actions is an old and well-loved design paradigm. Recently Bluespec System Verilog has successfully raised the level of abstraction in RTL design using this paradigm.

Every operation has a guard predicate: says when it CAN be run.

Operations are grouped into rules for atomic execution where the rule takes on the conjunction of its atomic operation guards and the rule may have its own additional guard predicate. Operations have the expectation they WILL be run (fairness). A compiler can direct scheduling decisions to span various power/performance implementations for a given program.

- A Bluespec design is expressed as a list of declarative rules,

- Shared variables are not used

- All comunication to and from registers, FIFOs and user modules is via transactional/blocking 'method calls' for which argument and handshake wires are synthesised according to a global ready/enable protocol,

- Rules are allocated a static schedule at compile time and some that can never fire are reported,

- The current strict mapping to clock cycles (time/space folding) might be relaxed by future compilation strategies.

- The wiring pattern of the whole design is generated using an embedded functional language (like Lava HDL).

The term 'wiring' above is used in the sense of TLM models: binding initiators to target methods.

LINK: Small Examples Toy BSV Compiler (DJG)

First basic example: two rules: one increments, the other exits the simulation. This example looks very much like RTL: provides an easy entry for hardware engineers.

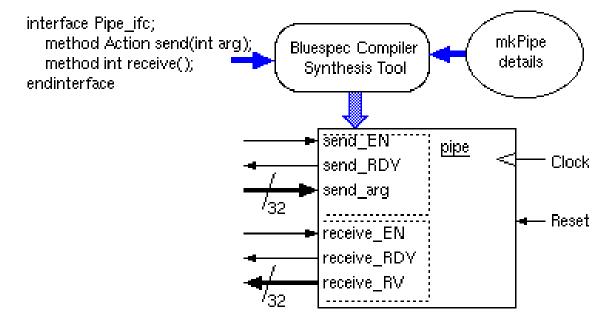

Second example uses a pipeline object that could have aribtrary delay. Sending process is blocked by implied handshaking wires (hence less typing than Verilog) and in the future would allow the programmer or the compiler to retime the implementation of the pipe component.

```

module mkTb2 (Empty);

Reg#(int) x <- mkReg ('h10);

Pipe_ifc pipe <- mkPipe;

rule fill;

pipe.send (x);

x <= x + 'h10; // This is short for x.write(x.read() + 'h10);

endrule

rule drain;

let y = pipe.receive();

$display (" y = %0h", y);

if (y > 'h80) $finish(0);

endrule

endmodule

```

But, behavioural expression using a conceptual thread is also useful to have, so Bluespec has a behavioural sub-language compiler built in.

# 1.2 Simulation

Simulation of real-world systems generally requires quantisation in time and spatial domains.

Figure 1.9: Synthesis of the 'pipe' Bluespec component with handshake nets.

There are two main forms of simulation modelling:

- (FES) finite-element simulation, and

- (EDS) event-driven simulation.

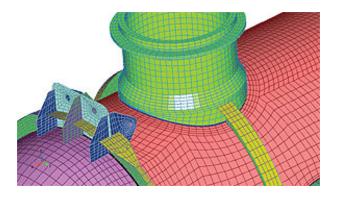

Finite-element simulation is used for analogue and fluid-flow systems. It is rarely used in SoC design (just for low-level electrical propagation and cross-talk modelling). Variable element size (and variable temporal step size) can be used to make finite-element simulations approximate even-driven behaviour.

Figure 1.10: Finite Elemenet Grid

```

Finite-element difference equations:

tnow += deltaT;

for (n in ...) i[n] = (v[n-1]-v[n])/R;

for (n in ...) v[n] += (i[n]-i[n+1])*deltaT/C;

```

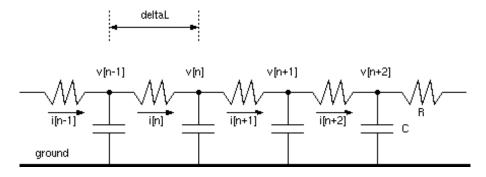

Basic finite-element simulation uses fixed spatial grid (element size is deltaL) and fixed time step (deltaT seconds). Each grid point holds a vector of instantatious local properties, such as voltage, temperature, stress, pressure, magnetic flux. Physical quantities are divided over the grid. Three examples:

1. Sound wave in wire: C=deltaL\*mass-per-unit-length, R=deltaL\*elasticity-per-unit-length

Figure 1.11: Baseline finite-element model for bidirectional propagation in one dimension.

- $\hbox{2. Heat wave in wire: $C$=$deltaL*$heat-capacity-per-unit-length, $R$=$deltaL*$thermal-conductance-per-unit-length} \\$

- 3. Electrical wave in wire: C=deltaL\*capacitance-per-unit-length, R=deltaL\*resistance-per-unit-length

Larger modelling errors with larger deltaT and deltaL, but faster simulation. Keep them less than 1/10th wavelength for good accuracy.

Generally use a 2D or 3D grid for fluid modelling: 1D ok for electronics. Typically want to model both resistance and inductance for electrical system. When modelling inductance instead of resistance, then need a '+=' in the i[n] equation. When non-linear components are present (e.g. diodes and FETs), SPICE simulator adjusts deltaT dynamically depending on point in the curve.

# 1.2.1 Event Driven Simulation

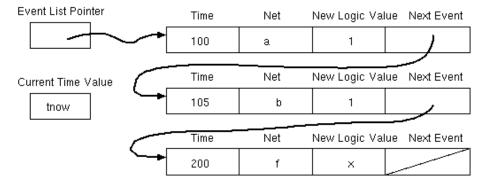

Figure 1.12: Event queue, linked list, sorted in ascending temporal order.

The following ML fragment demonstrates the main datastructure for an EDS kernel. EDS ML fragments

```

// A net has a string name and a width.

// A net may be high z, dont know or contain an integer from 0 up to 2**width - 1.

// A net has a list of driving and reading models.

type value_t = V_n of int | V_z | V_x;

type net_t = {

net_name:

string;

// Unique name for this net.

width:

int:

// Width in bits if a bus.

current value:

value t ref:

// Current value as read by others

Delay before changing (commonly zero)

net_inertia:

int;

model_t list ref; // Models that must be notified if changed.

// An event has a time, a net to change, the new value for that net and an

// optional link to the next on the event queue:

type event_t = EVENT of int * net_t * value_t * event_t option ref

```

This reference implementation of an event-driven simulation (EDS) kernel maintains an ordered queue of events commonly called the **event list**. The current simulation time, **tnow**, is defined as the time of the event at the head of this queue. An event is a change in value of a net at some time in the future. Operation takes the next event from the head of the queue and dispatches it. Dispatch means changing the net to that value and chaining to the next event. All component models that are sensitive to changes on that net then run, potentially generating new events that are inserted into the event queue.

We will cover two variations on the basic EDS algorithm: intertial delay and delta cycles.

```

Code fragments (details not examinable):

Create initial, empty event list:

val eventlist = ref [];

Constructor for a new event: insert at correct point in the sorted event list:

fun create_and_insert_event(time, net, value) =

let fun ins e = case !e of

(A as EMPTY) => e := EVENT(time, net, value, ref A)

(A as EVENT(t, n, v, e')) => if (t > time)

then e := EVENT(time, net, value, ref A)

else ins e'

in ins eventlist

Main simulation: keep dispatching until event list empty:

fun dispatch one event() =

if (!eventlist = EMPTY) then print("simulation finished - no more events\n")

else let val EVENT(time, net, value, e') = !eventlist in

( eventlist := !e';

tnow := time;

app execute_model (net_setvalue(net, value))

) end

```

# 1.2.2 Inertial and Transport Delay

Consider a simple 'NOR' gate model with 250 picosecond delay. It has two inputs, and the behavioural code inside the model will be something like (in SystemC-like syntax, covered later)

```

SC_MODULE(NOR2)

{    sc_in < bool > i1, i2;    sc_out < bool > y;

void behaviour()

{       y.write(!(i1.read() || i2.read()), SC_TIME(250, SC_PS));

}

SC_CTOR(NOR2) { SC_METHOD(behaviour); sensitive << i1 << i2;

}</pre>

```

The above model is run when either of its inputs change and it causes a new event to be placed in the event queue 250 picoseconds later. This will result in a pure **transport delay**, because multiple changes on the input within 250 picoseconds will potentially result in multiple changes on the output that time later. This is unrealistic, a NOR gate made of transistors will not respond to rapid changes on its input, and only decisively change its output when the inputs have been stable for 250 picoseconds. In other words, it exhibits inertia. To model **inertial delay**, the event queue insert function must scan for any existing schedulled changes before the one about to be inserted and delete them. This involves little overhead since we are scanning down the event queue anyway.

Consider the behaviour of the above RS-latch when a very short (runt) pulse or glitch tries to set it. What will it do with transport models?: the runt pulse will circulate indefinitely. What will it do with inertial models?: ignore the glitch.

Figure 1.13: RS-latch: behaviour of runt pulse when modelling with transport delay.

# 1.2.3 Modelling Zero-Delay Components - The Delta Cycle

At early stages of design exploration, we may not know anything about the target technology. We do not wish to insert arbitrary delay figures in our source code, yet some sort of delay is needed to make synchronous hardware work correctly. The solution is the **delta cycle**.

For correct behaviour of synchronous edge-triggered hardware, the propagation delay of D-types must be greater than their hold time. Question: How can we ensuse this in a technology-neutral model that does not have any specific numerical delays?

```

// Example: swap data between a pair of registers

reg [7:0] X, Y;

always @(posedge clock) begin

X <= Y;

Y <= X;

end

// E.g. if X=3 and Y=42 then Y becomes 3 and X becomes 42.

```

Answer: Hardware simulators commonly support the compute/commit or 'signal' paradigm for non-blocking updates. The signal has current and next values.

All three of VHDL, Verilog RTL and SystemC support the **compute/commit** paradigm (also known as evaluate/update) using **delta cycles**. Delta cycle: a complete compute/commit cycle that does not advance global time. Zero-delay models generate new events at the current time, thow. To avoid **shoot-through**, these need to be delayed until all current evaluation is complete. Models write such events to the **next** field of the signal and such writes add the signal to the pending list.

EDS kernel with pending queue (simplified):

# Raw EDS without deltacycles

```

while (eventlist <> EMPTY)

{ e = hd eventlist;

eventlist = tl eventlist;

tnow = e.time;

e.net.current = e.value;

for (m in e.net.models) do m.exec()

}

```

```

while (eventlist <> EMPTY)

{ e = hd eventlist;

if (e.time > tnow) and (pending<>EMPTY)

{ // Commit pendings and commence new delta cycle

for (net in pending) do net.current=net.next;

pending = EMPTY;

for (n in nets just updated) for (m in n.models)

} else

{ eventlist = tl eventlist;

tnow = e.time;

e.net.current = e.value;

for (m in e.net.models) do m.exec();

}

}

```

Details fully lectured by MJCG (slide 110 onwards): Temporal Logic Course

One implementation is to have an auxiliary list containing nets, called the pending queue. The net.write(value, when) method checks whether the new time is the same as the current time and if so, instead of inserting an event for the net in the event list, the net is placed on the pending queue and the new value stored in a 'next

value' field in the net. The kernel is then modified as shown above, to empty the pending queue when the next event would advance simulation time.

Note that committing a pending queue update can wake up a model sensitive to the updated net and cause further events to be generated. All pending updates must be committed atomically and new zero-delay events are added to a fresh pending queue.

Hence, when zero-delay models are active and the output of one feeds another (e.g. a zero delay gate in the clock path), the value of system time, tnow, may not advance for several consecutive delta cycles. Clock generators or other components for which we can put in delay figures operate normally, causing real advances in simulation time.

A net that is to have its updated deferred in VHDL (and SystemC) is called a **signal**, whereas immediate updates when variables are written to. In Verilog, all nets can be assigned in either way and instead two different assignment operators are provided (called blocking and non-blocking, denoted = and <= respectively).

(As we shall see, a SystemC 'sc\_signal' is implemented with a current and a next value and it is necessary to use the 'net.read()' method to read the value of a SystemC signal because C++ does not allow override of the read operator.)

# 1.3 Hazards

Definitions (some authors vary slightly):

- Data hazard when an operand's address is not yet computed or has not arrived in time for use,

- WaW hazard write-after-write: the second write must occur after the first otherwise its result is lost,

- RaW or WaR hazard write and read of a location are accidentally permuted,

- Control hazard when it is not yet clear whether an operation should be performed,

- Alias hazard we do not know if two array subscripts are equal,

- Structural hazard insufficient physical resources to do everything at once.

We have a structural hazard when an operation cannot proceed because a resource is already in use. Resources that might present structural hazards are:

- Memories with insufficient ports,

- Memories with variable latency, especially DRAM,

- (Synchronous RAM can be fully pipelined and so cause non-structural hazards),

- Insufficient number of ALUs for all of the operations to be schedulled in current clock tick,

- Anything non-fully pipelined i.e. something that goes busy, such as long multiplication (e.g. Booth Multiplier or division or a floating point unit).

A non-fully pipelined component cannot start a new operation on every clock cycle. Instead it has handshake wires that start it and inform the client logic when it is ready.

An example of a component that cannot accept new input data every clock cycle (i.e. something that is non-fully-pipelined) is a sequential long multiplier, that works as follows:

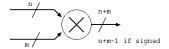

Figure 1.14: Multiplier schematic symbol.

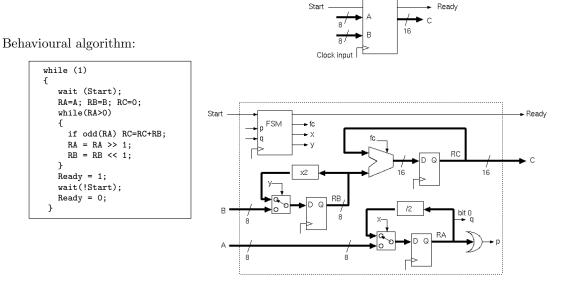

This implements conventional long multiplication. It is certainly not fully-pipelined, it goes busy for many cycles, depening on the log of the A input. The illustration shows a common design pattern consisting of a **datapath** and a **sequencer**. Booth's algorithm (see additional material) is faster, still using one adder but needing half the clock ticks.

**Exercise:** Write out the complete design, including sequencer, for the above multiplier, or that of Booth, or a long division unit, in Verilog or SystemC.

# 1.3.1 Multiplier Answer

```

module LONGMULT8b8(clk, reset, C, Ready, A, B, Start);

input clk, reset, Start;

output Ready;

input [7:0] A, B;

output [15:0] C;

reg [15:0] RC, RB, RA;

Ready;

reg

// Behavioural code:

while (1)

//

{

wait (Start);

RA=A; RB=B; RC=O;

while(RA>0)

{ if odd(RA) RC=RC+RB;

RA = RA >> 1; RB = RB << 1;

//

Readv = 1:

//

wait(!Start);

Ready = 0;

reg xx, yy, qq, pp; // Control and predicate nets reg [1:0] fc;

reg [3:0] state;

always @(posedge clk) begin

xx = 0; // default settings.

yy = 0;

fc = 0;

// Predicates

pp = (RA!=16'h0);

qq = RA[0];

// Sequencer

// Work while pp holds

// Odd if qq holds

if (reset) begin

state <= 0;

Ready <= 0;

end

else case (state)

0: if (Start) begin

xx = 1;

yy = 1;

fc = 2;

state <= 1;

1: begin

fc = qq;

if (!pp) state <= 2;

end

2: begin

Ready <= 1;

if (!Start) state <= 3;

end

3: begin

Ready <= 0;

state <= 0;

endcase // case (state)

// Datapath

RB <= (yy) ? B: RB<<1;

RA <= (xx) ? A: RA>>1;

RC <= (fc==2) ? 0: (fc==1) ? RC+RB: RC;

end

assign C = RC;

endmodule

```

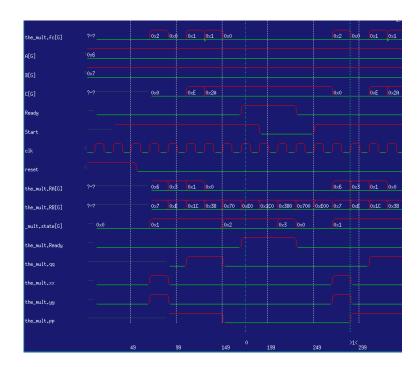

Suitable test wrapper:

```

module SIMSYS();

reg clk, reset, Start; wire Ready;

wire [7:0] A, B;

wire [15:0] C;

// Reset Generator

initial begin reset = 1; # 55 reset = 0; end

// Clock Generator

initial begin clk = 0; forever #10 clk = !clk; end

// Stimulus

assign A = 6;

assign B = 7;

// Handshake control

always @(posedge clk) Start <= !Ready;</pre>

// Console ouput logging:

always @(posedge clk) $display("Ready=%h C=%d");

LONGMULT8b8 the_mult(clk, reset, C, Ready, A, B, Start);

endmodule // SIMSYS

```

Figure 1.15: Long Multiplier Timing Waveforms

# 1.3.2 Hazards From Array Memories

A structural hazard in an RTL design can make it non synthesisable. Consider the following expressions that make liberal use of array subscription and the multiplier operator:

Structural hazard sources are numbered:

- 1. The RAMs or register files Foo Bar and Boz might not have two read ports.

- 2. Even with two ports, can Bar perform the double subscription in one clock cycle?

- 3. Read operations on Boz might be a long way apart in the code, so hazard is hard to spot.

- 4. The cost of providing two 'flash' multipliers for use in one clock cycle while they lie idle much of the rest of the time is likely not warranted.

A multiplier that operates combinationaly in less than one clock cycle is called a 'flash' multiplier and it uses quadratic silicon area.

Expanding blocking assignments can lead to **name alias** hazards:

Suppose we know nothing about xx and yy, then consider:

To avoid **name alias** problems, this must be compiled to non-blocking pure RTL as:

```

begin

...

if (g) Foo[xx] = e1;

r2 = Foo[yy];

```

```

begin

...

Foo[xx] <= (g) ? e1: Foo[xx];

r2 <= (xx==yy) ? ((g) ? e1: Foo[xx]): Foo[yy];

```

Quite commonly we do know something about the subscript expressions. If they are compile-time constants, we can decidedly check the equality at compile time. Suppose that at ... or elsewhere beforehand we had the line 'yy = xx+1;' or equivalent knowledge? Then with sufficient rules we can realise at compile time they will never alias. However, no set of rules will be complete (decidability).

# 1.3.3 Overcoming Structural Hazards using Holding Registers

A **holding register** is commonly inserted to overcome a structural hazard (by hand or by a high-level synthesis tool HLS). Sometimes, the value that is needed is always available elsewhere in the design (and needs forwarding) or sometimes an extra sequencer step is needed.

If we know nothing about e0 and e1:

```

then load holding register in additional cycle:

```

```

always @(posedge clk) begin

...

ans = Foo[e0] + Foo[e1];

...

end

```

```

always @(posedge clk) begin

pc = !pc;

...

if (!pc) holding <= Foo[e0];

if (pc) ans <= holding + Foo[e1];

...

end</pre>

```

If we can analyse the pattern of e0 and e1:

```

always @(posedge clk) begin

...

ee = ee + 1;

...

ans = Foo[ee] + Foo[ee-1];

...

end

```

then, apart from first cycle, use holding register to forward value from previous iteration:

```

always @(posedge clk) begin

...

ee <= ee + 1;

holding <= Foo[ee];

ans <= holding + Foo[ee];

...

end</pre>

```

We can implement the program counter and holding registers as source-to-source transformations, that eliminate

hazards, as just illustrated. One algorithm is to first to emit behavioural RTL and then to alternate the conversion to pure form and hazard avoidance rewriting processes until closure.

For example, the first example can be converted to behavioural RTL that has an implicit program counter (state machine) as follows:

```

always @(posedge clk) begin

holding <= Foo[e0];

@(posedge clk);

ans <= holding + Foo[e1];

end</pre>

```

The transformations illustrated above are NOT performed by mainstream RTL compilers today: instead they are incorporated in HLS tools such as Kiwi. KiwiC Structural Hazard ExampleSharing structural resources may require additional multiplexers and wiring: so not always worth it. A good design not only balances structural resource use between clock cycles, but also critical path timing delays.

These example fragments handled one hazard and used two clock cycles. They were localised transformations. When there are a large number of clock cycles, memories and ALUs involved, a global search and optimise procedure is needed to find a good balance of load on structural components. Although these examples mainly use memories, other significant structural resources, such as fixed and floating point ALUs also present hazards.

# 1.4 Folding, Retiming & Recoding

Generally we have to chose between high performance or low power. (We shall see this at the gate level later on). The **time/space fold** and **unfold** operations trade execution time for silcon area. A given function can be computed with fewer clocks by 'unfolding' in the time domain, typically by loop unwinding (and predication).

```

LOOPED (time) option: | UNWOUND (space) option: |

for (i=0; i < 3 and i < limit; i++) | if (0 < limit) sum += data[0] * coef[j];

sum += data[i] * coef[i+j]; | if (1 < limit) sum += data[1] * coef[1+j];

| if (2 < limit) sum += data[2] * coef[2+j];

```

The '+=' operator is an **associative reduction** operator. When the only interactions between loop iterations are outputs via such an operator, the loop iterations can be executed in parallel. On the other hand, if one iteration stores to a variable that is read by the next iteration or affects the loop exit condition then unwinding possibilities are reduced.

We can **retime** a design with and without changing its state encoding. We will see that adding a pipeline stage can increase the amount of state without **recoding** existing state.

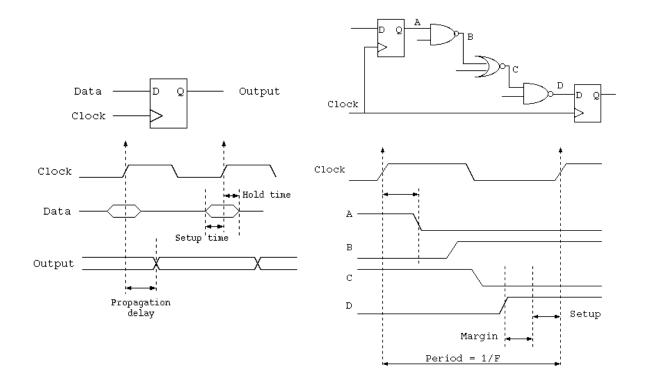

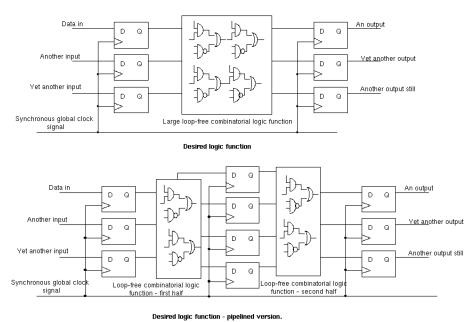

### 1.4.1 Critical Path Timing Delay

Meeting **timing closure** is the process of manipulating a design to meet its target clock rate.

The maximum clock frequency of a synchronous clock domain is set by its critical path. The longest path of combinational logic must have settled before the setup time of any flip-flop starts.

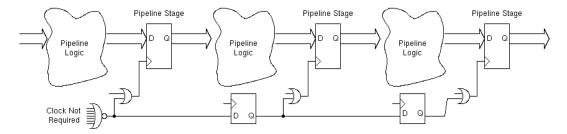

Figure 1.16: A circuit before and after insertion of an additional pipeline stage.

Pipelining is a commonly-used technique to boot system performance. Introducing a pipeline stage increases latency but also the maximum clock frequency. Fortunately, many applications are tolerant to the processing delay of a logic subsystem. Consider a decoder for a fibre optic signal: the fibre might be many kilometers long and a few additional clock cycles in the decoder increase the processing delay by an amount equivalent to a few coding symbol wavelengths: e.g. 20 cm per pipeline stage for a 1 Gbaud modulation.

Pipelining introduces new state but does not require existing state flip-flops to change meaning.

Flip-flop migration does alter state encoding. It exchanges delay in one path delay for delay in another. A

Figure 1.17: Flip-flop migration: two circuits of identical behaviour, but different state encoding.

sequence of such transformations can lead to a shorter critical path overall.

In the following example, the first migration is a local transformation that has no global consequences:

```

Before: Migration 1: Migration 2 (non causal):

a <= b + c; b1 <= b; c1 <= c; q1 <= (dd) ? (b+c): 0;

q <= (d) ? a:0; q <= (d) ? b1+c1:0; q <= q1;

```

The second migration, that attempts to perform the multiplexing one cycle earlier will require an earlier version of d, here termed dd that might not be available (e.g. if it were an external input we need knowledge of the future). An earlier version of a given input can sometimes be obtain by delaying all of the inputs (think of delaying all the inputs to a bookmakers shop), but this cannot be done for certain applications where system response time (in-to-out delay) is critical.

Problems arising:

- Circuits containing loops (proper synchronous loops) cannot be pushed with a simple algorithm since the algorithm loops.

- External interfaces that do not use transactional handshakes (i.e. those without flow control)(see later) cannot tolerate automatic re-timing since the knowledge about when data is valid is not explicit.

- Many structures, including RAMs and ALUs, have a pipeline delay, so the hazard on their input port needs resolving in a different clock cycle from hazards involving their result values.

but retiming can overcome structural hazards (e.g. the 'write back' cycle in RISC pipeline).

Other rewrites commonly used: automatically introduce one-hot and gray encoding, or invert for reset as preset.

### 1.4.2 Back Annotation and Timing Closure

Once the system has been placed and routed, the length and type of each conductor is known. These facts allow fairly accurate delay models of the conductors to be generated (Section 7.0.22).

The accurate delay information is fed into the main simulator and the functionality of the chip or system is checked again. This is known as **back annotation**. It is possible that the new delays will prevent the system operating at the target clock frequency.

The marketing department have commonly pre-sold the product with an advertised clock frequency. Making the actual product work at this frequency is known as meeting **timing closure**.

The normal means to achieve timing closure is to migrate logic either side of an existing register or else to add a new register - but not all protocols are suitable for registering (Section 3.1.4).

FIFOs are either synchronous or clock-domain crossing. Synchronous FIFOs are either bubble-free (simultaneous read and write operations are always possible) or internally-pipelined (effect of a read or write is only visible at the

Figure 1.18: FIFO schematic symbols: Synchronous and Clock Domain Crossing.

opposite port a clock cycle later, also known as *fully-registered*). (Bluespec users' note: the default BSV FIFO is fully-registered and so introduces bubbles in both directions: it provides two variants with combinational paths which avoid bubbles in each direction respectively, called bypass and pipelined, but note that neither variant is fully-pipelined/fully-registered using the above definitions.)

A FIFO can help achieve timing closure, but again the protocol must be transactional and a *bubble-free* FIFO cannot always be used owing to its combinational path(s), hence latency is introduced.

# SG 2 — SystemC: Hardware Modelling Library

SystemC is a free library for C++ for hardware SoC modelling. Download from www.accelera.org SystemC was developed over the last ten years. There have been two major releases, 1.0 and 2.0. Also of importance is the TLM sub-library, TLM 2.0. (SystemC using transactional-level modelling (TLM/ESL) is covered later).

Greaves developed the  $TLM_POWER3add - onlibrary for power modelling$ .

It can be used for detailed net-level modelling, but today its main uses are:

- Architectural exploration: Making a fast and quick, high-level model of a SoC to explore performance variation against various dimensions, such as bus width and cache memory size.

- Transactional level (TLM) models of systems, where handshaking protocols between components using hardware nets are replaced with subroutine calls between higher-level models of those components.

- Synthesis: RTL is synthesised from from SystemC source code using a so-called 'C-to-gates' compiler. SystemC Synthesis

SystemC includes (at least):

- A module system with inter-module channels: C++ class instances are instantiated in a hierarchy, following the circuit component structure, in the same way that RTL modules instantiate each other.

- An eventing and threading kernel that is non-preemptive and which allows user code inside components to run either in a trampoline style, returning the thread without blocking, or to keep the thread and hold state on a stack.

- Compute/commit signals as well as other forms of channel for connecting components together. The compute/commit signals are needed in a zero-delay model of hardware to avoid 'shoot-thru': i.e. the scenario where one flip-flop in a clock domain changes its output before another has processed the previous value.

- A library of fixed-precision integers. Hardware typically uses all sorts of different width busses and counters that wrap accordingly. SystemC provides classes of signed and unsigned variables of any width that behave in the same way. For instance the user can define an sc\_int of five bits and put it inside a signal. The provided library includes overloads of all the standard arithmetic and logic operators to operate on these types.

- Plotting output functions that enable waveforms to be captured to a file and viewed with a program such as gtkwave.

- A transactional modelling sub-library: TLM 1.0 provided separate blocking and non-blocking interfaces prototypes that a user could follow and in TLM 2.0 these are rolled together into 'convenience sockets' that can convert between the two forms.

Problem: hardware engineers are not C++ experts but they can be faced with complex or advanced C++ error messages when they misuse the library.

Benefit: General-purpose behavioural C code, including application code and device drivers, can all be modelled in a common language.

SystemC enables a user class to be defined using the the SC\_MODULE macro. Modules inherit various attributes appropriate for an hierarchic hardware design including an instance name, a type name and channel binding capability. The sensitive construct registers a callback with the EDS kernel that says when the code inside the module should be run. An unattractive feature of SystemC is the need to use the .read() method when reading a signal.

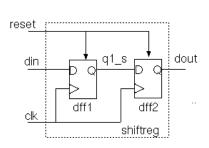

# 2.0.3 SystemC Structural Netlist

```

//Example of structural hierarchy and wiring between levels:

SC_MODULE(shiftreg) // Two-bit shift register

sc in < bool >

clk, reset, din;

sc_out < bool >

dout;

sc_signal < bool >

dff dff1, dff2;

// Instantiate FFs

SC_CTOR(shiftreg) : dff1("dff1"), dff2("dff2")

dff1.clk(clk);

dff1.reset(reset);

dff1.d(din);

dff1.q(q1_s);

dff2.clk(clk);

dff2.reset(reset):

dff2.d(q1_s);

dff2.q(dout);

};

```

A SystemC templated **channel** provides general purpose interface between components. We rarely use the raw channels: instead we use the derived forms sc\_in, sc\_out and sc\_signal. These channels implement compute/commit paradigm required for **delta cycles**. This avoids non-determinacy from races in zero-delay models (see earlier).

Other provided channels include the buffer, fifo, mutex, semaphore and clock (non-examinable). Users can overload the channel class to implement channels with their own semantics if needed. A user-defined channel type can even contain other SystemC components but the importance of this is reduced when using the TLM libraries.

When the scheduler blocks with no more events in the current time step, the pending new values are committed to the visible current values.

For faster system modelling, we do not want to enter EDS kernel for every change of every net or bus: so is it possible to pass larger objects around, or even send threads between components, like S/W does?

Yes, it is possible to put any datatype inside a signal and route that signal between components (provided the datatype can be checked for equality to see if current and next are different and so on). Using this approach, a higher-level model is possible, because a complete Ethernet frame or other large item can be delivered as a single event, rather than having to step though the cycle-by-cycle operation of a serial hardware implementation.

Even better: SystemC 2.0 enabled threads to be passed along the channels, allowing intermodule thread calling, just like object-oriented software. This will enable TLM modelling (described later). Hence we have three inter-module communication styles:

- 1. Pin-level modelling: an event is a change of a net or bus,

- 2. Abstract data modelling: an event is delivery of a complete cache line or other data packet,

- 3. Transactional-level modelling: avoid events as much as possible: use intermodule software calling.

# 2.0.4 SystemC Abstracted Data Modelling

Here we raise the modelling abstraction level by passing an abstract datatype along a channel. the abstract data type must define a few basic methods, such as the equality operator overload this is shown:

```

sc_signal < bool > mywire; // Rather than a channel conveying just one bit,

struct capsule

{ int ts_int1, ts_int2;

bool operator== (struct ts other)

{ return (ts_int1 == other.ts_int1) && (ts_int2 == other.ts_int2); }

int next_ts_int1, next_ts_int2; // Pending updates

void update()

{ ts_int1 = next_ts_int1; ts_int2 = next_ts_int2; }

...

... // Also must define read(), write() and value_changed()

};

sc_signal < struct capsule > myast; // We can send two integers at once.

```

For many basic types, such as bool, int, sc\_int, the required methods are provided in the SystemC library, but clearly not for user-defined types.

```

void mymethod() { .... }

SC_METHOD(mymethod)

sensitive << myast.pos(); // User must define concept of posedge for his own abstract type.</pre>

```

#### 2.0.5 Threads and Methods

SystemC enables a user module to keep a thread and a stack but prefers, for efficiency reasons if user code runs on its own upcalls in a trampoline style.

- An SC\_THREAD has a stack and is allowed to block.

- An SC\_METHOD is just an upcall from the event kernel and must not block.

Comparing SC\_THREADs with trampoline-style methods we can see the basis for two main programming TLM styles to be introduced later: blocking and non-blocking.

The user code in an SC\_MODULE is run either as an SC\_THREAD or an SC\_METHOD.

An SC\_THREAD has a stack and is allowed to block. An SC\_METHOD is just an upcall from the event kernel and must not block. Use SC\_METHOD wherever possible, for efficiency. Use SC\_THREAD where important state must be retained in the program counter from one activation to the next or when asynchronous active behaviour is needed.

The earlier 'mycounter' example used an SC\_METHOD. Now an example using an SC\_THREAD: a data source that provides numbers using a net-level four-phase handshake:

A SystemC thread can block for a given amount of time using the wait function in the SystemC library (not the Posix namesake). NB: If you put 'wait(4)' for example, you will invoke the unix system call of that name, so make sure you supply a SystemC time unit as the second argument.

#### Additional notes:

Waiting for an arbitrary boolean expression to hold hard to implement on top of C++ owing to its compiled nature:

- C++ does not have a reflection API that enables a user's expression to be re-evaluated by the event kernel.

- Yet we still want a reasonably neat and efficient way of passing an uninterpreted function.

- Original solution: the delayed evaluation class:

```

waituntil(mycount.delayed() > 5 && !reset.delayed());

```

Poor user had to just insert the **delayed** keyword where needed and then ignore it when reading the code. It was too unwieldly, now removed. So today (pre C++11) use the less-efficient:

```

do { wait(10, SC_NS); } while(!((mycount > 5 && !reset)));

```

### 2.0.6 SystemC Plotting and GUI

We can plot to industry standard VCD files and view with gtkwave (or modelsim).

```

sc_trace_file *tf = sc_create_vcd_trace_file("tracefile");

// Now call:

// sc_trace(tf, <traced variable>, <string>);

sc_signal < int > foo;

float bar;

sc_trace(tf, foo);

sc_trace(tf, foo);

sc_trace(tf, bar, "bar"); // Give name if anon constuctor

sc_start(1000, SC_NS); // Simulate for one microsecond

sc_close_vcd_trace_file(tr);

return 0;

```

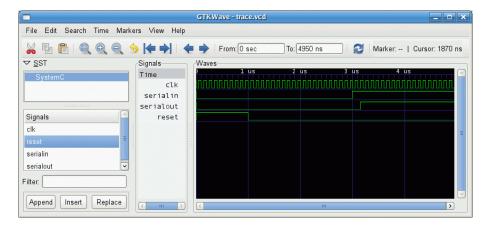

Figure 2.1: Waveform view plotted by gtkwave.

VCD can be viewed with **gtkwave** or in **modelsim**. There are various other commercial interactive viewer tools...

Try-it-yourself on PWF

# SG 3 — Basic SoC Components

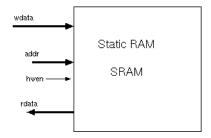

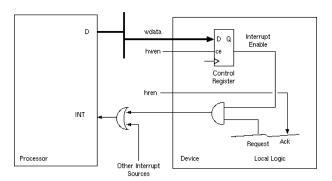

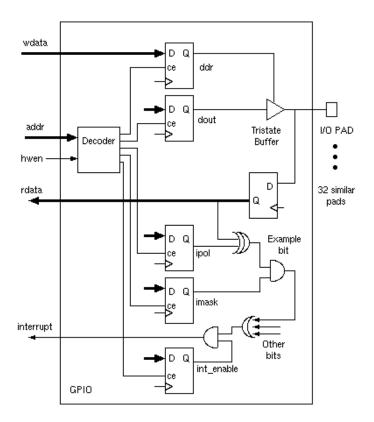

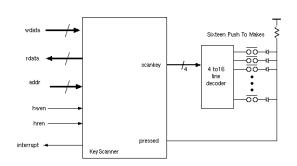

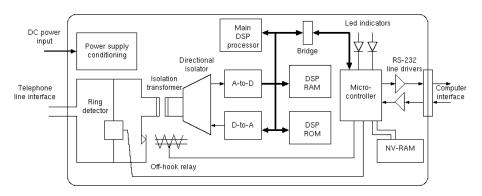

This section is a tour of actual hardware components (IP blocks) found on chips, presented with schematics and illustrative RTL fragments, and connected using a simple bus. Later we will look at other busses and networks on chip.

In the old-fashioned approach, we notice that the hand-crafted RTL used for the hardware implementation has no computerised connection with the firmware, device drivers or non-synthesisable models used for architectural exploration. Today, XML representations of IP-block metainfo resolve this (IP-XACT and OVM/UVM will be mentioned in the last lecture if time permits).

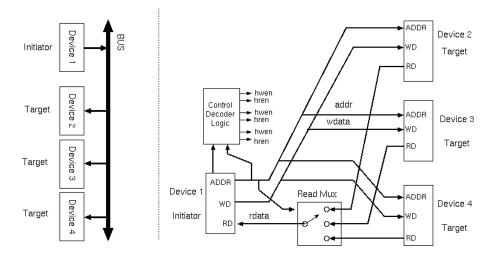

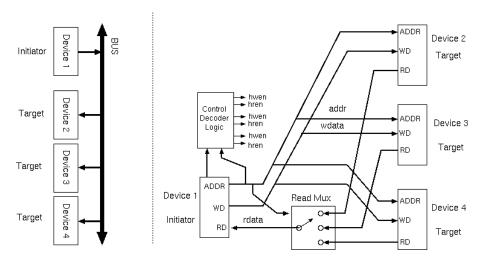

### 3.0.7 Simple Microprocessor: Bus Connection and Internals

Figure 3.1: Schematic symbol and internal structure for a microprocessor (CPU).

This device is a bus master or *initiator* of bus transactions. It makes a load/read by asserting host read enable: **hren**. It writes to addess space (a store) by asserting host write enable **hwen**. In this course we are concerned with the external connections only.

A central processor unit (CPU) is an execution unit and a control unit. A microprocessor (MPU) is a processor (CPU) on a chip. Early microprocessors such as the original Intel 8080 device had a 16 bit address bus and an 8 bit data bus so can address 64 Kbytes of memory. We say it had an A16/D8 memory architecture. Modern MPUs commonly have on-chip caches and an MMU for virtual memory.

It executes a handshake with external devices using the hren/hwen signals as requests and the ack signal as an acknowledge. In the following slides every device can respond immediately and so no ack signal is shown. In practice, contention, cache misses and operations on slow busses will cause wait states for the processor. Simple processors stall entirely during this period, whereas advanced cores carry on with other work and can receive responses out of order.

The interrupt input makes it save the current PC and load an agreed value that is the entry point for an interrupt service routine.

The high-order address bits are decoded to create chip enable signals for each of the connected peripherals, such as the RAM, ROM and UART.

As we shall see, perhaps the first SoCs, as such, were perhaps the microcontrollers. The Intel 8051 used in the mouse shipped with the first IBM PC is a good example. For the first time, RAM, ROM, Processor and I/O

devices are all on one piece of silicon. We all now have many of these such devices : one in every card in our wallet or purse. Today's SoC are the same, just much more complex.

### 3.0.8 A canonical D8/A16 Micro-Computer

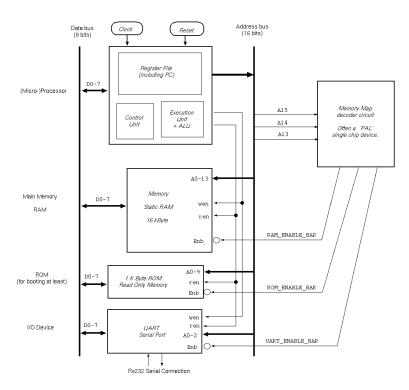

Figure 3.2: Early microcomputer structure, using a bidirectional/tri-state data bus.

Figure 3.2 shows the inter-chip wiring of a basic microcomputer (i.e. a computer based on a microprocessor).

```

Start

End

Resource

0000

03FF

EPROM

0400

3FFF

Unused images of EPROM

//F —7—addr—

4000

8000

BFFF

Unused

C000

C001

Registers in the UART

C002

FFFF

Unused images of the UART

```

The following RTL describes the required glue logic for the memory map:

```

module address_decode(abus, rom_cs, ram_cs, uart_cs);

input [15:14] abus;

output rom_cs, ram_cs, uart_cs;

assign rom_cs = (abus == 2'b00); // 0x0000

assign ram_cs = (abus == 2'b01); // 0x4000

assign uart_cs = !(abus == 2'b11);// 0xC000

endmodule

```

The 64K memory map of the processor has been allocated to the three addressable resources as shown in the table. The memory map must be allocated without overlapping the resources. The ROM needs to be at address zero if this is the place the processor starts executing from when it is reset. The memory map must be known at the time the code for the ROM is compiled. This requires agreement between the hardware and software engineers concerned.

In the early days, the memory map was written on a blackboard where both teams could see it. For a modern SoC, there could be hundreds of items in the memory map. An XML representation called IP-XACT is being adopted by the industry and the glue logic may be generated automatically.

### 3.0.9 ROM - Read Only Memory

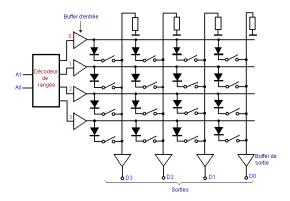

ROM is either mask programmed at manufacture or field-programmable.

Figure 3.3: ROM Structure - the switches have various implementation technologies.

An addressed row causes the column wires to become one or zero according to whether the diodes are installed (or connected) at the crosspoints. FLASH is a common type of ROM used in USB-sticks and SD cards. The 'switches' in FLASH are transistors with floating gates that are charged and discharged using electron tunnelling when ten or more volts are applied, but which retain their static charge for many years under normal conditions. By 'floating' we mean totally insulated from the rest of the electronic circuit (an envelope of silicon dioxide surrounds each floating gate).

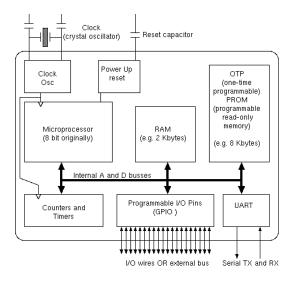

### 3.0.10 A Basic Micro-Controller

Figure 3.4: A typical single-chip microcomputer (microcontroller).

A microcontroller has all of the system parts on one piece of silicon. First introduced in 1979-85 (e.g. Intel 80C51). Such a microcontroller has an internal D8/A16 architecture and is used in things like a door lock, mouse or smartcard.

Figure 3.5: Contact plate for a smartcard.

### 3.0.11 Switch/LED Interfacing

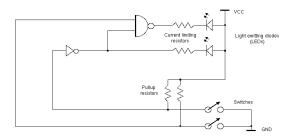

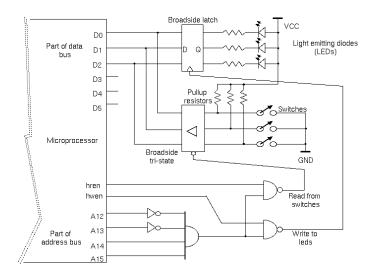

Figure 3.6: Connecting LEDs and switches to digital logic.

Figure 3.7: Connecting LEDs and switches for CPU programmed IO (PIO)

Figure 3.6 shows an example wiring structure for hardwired functionality with switches and LEDs. Figure 3.7 shows an example of memory address decode and simple LED and switch interfacing for programmed I/O (PIO) using a microprocessor. When the processor generates a read of the appropriate address, the tri-state buffer places the data from the switches on the data bus. When the processor writes to the appropriate address, the broadside latch captures the data for display on the LEDs until the next write.

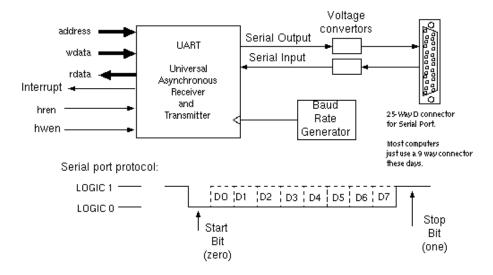

## 3.0.12 UART Device

The RS-232 serial port was widely used in the 20th century for character I/O devices (teletype, printer, dumb terminal). A pair of simplex channels (output and input) make it full duplex. Additional wires are sometimes used for hardware flow control, or a software Xon/Xoff protcol can be used. Baud rate and number of bits per words must be pre-agreed.

Figure 3.8: Typical Configuration of a Serial Port with UART

# 3.0.13 Programmed I/O

Programmed Input and Output (PIO). Input and output operations are made by a program running on the processor. The program makes read or write operations to address the device as though it was memory. Disadvantage: Inefficient - too much polling for general use. Interrupt driven I/O is more efficient.

Here is C preprocessor code to define the I/O locations in use by a simple UART device (universal asynchronous receiver/transmitter).

```

//Macro definitions for C preprocessor

//Enable a C program to access a hardware

//UART using PIO or interrupts.

#define IO_BASE 0xFFFC1000 // or whatever

#define U_SEND

0x10

#define U_RECEIVE 0x14

#define U_CONTROL 0x18

#define U_STATUS 0x1C

#define UART_SEND() \

(*((volatile char *)(IO_BASE+U_SEND)))

#define UART_RECEIVE() \

(*((volatile char *)(IO_BASE+U_RECEIVE)))

#define UART_CONTROL() \

(*((volatile char *)(IO_BASE+U_CONTROL)))

#define UART_STATUS() \

(*((volatile char *)(IO_BASE+U_STATUS)))

#define UART_STATUS_RX_EMPTY (0x80)

#define UART_STATUS_TX_EMPTY (0x40)

#define UART_CONTROL_RX_INT_ENABLE (0x20)

#define UART_CONTROL_TX_INT_ENABLE (0x10)

```

The receiver spins until the empty flag in the status register goes away. Reading the data register makes the status register go empty again. The actual hardware device might have a receive FIFO, so instead of going empty, the next character from the FIFO would become available straightaway:

```

char uart_polled_read()

{

while (UART_STATUS() &

UART_STATUS_RX_EMPTY) continue;

return UART_RECEIVE();

}

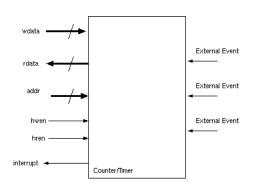

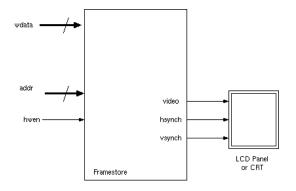

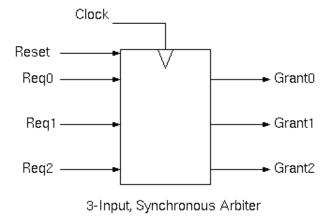

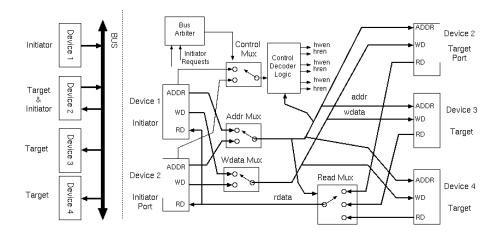

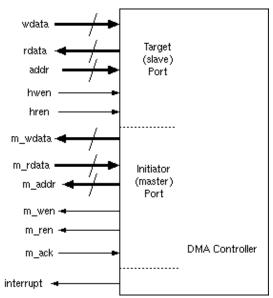

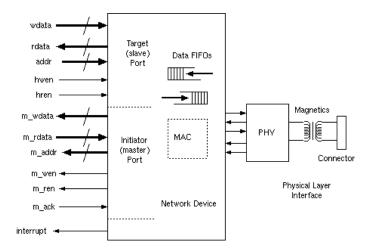

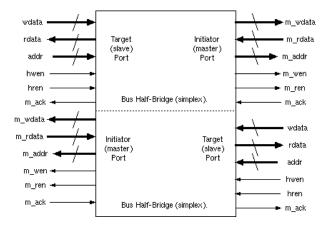

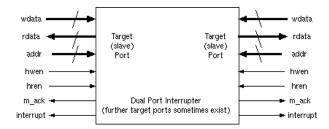

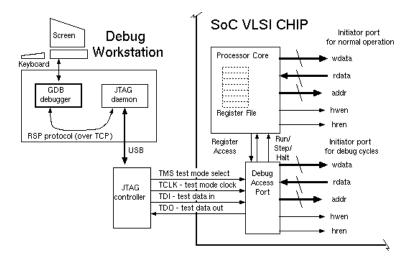

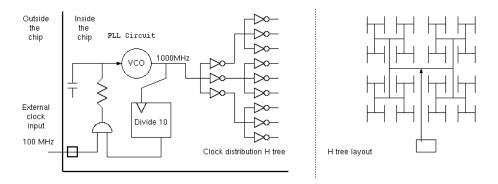

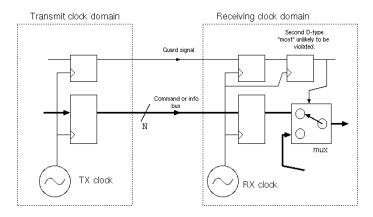

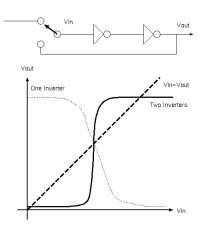

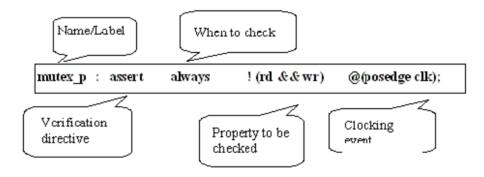

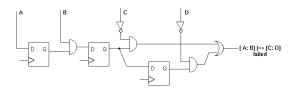

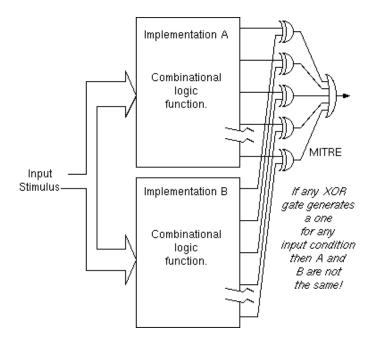

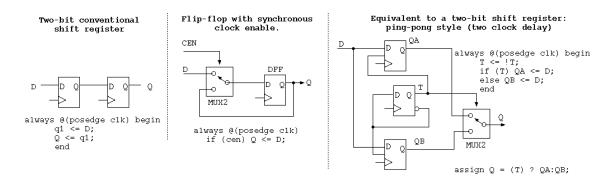

```