(Not lectured for part II).

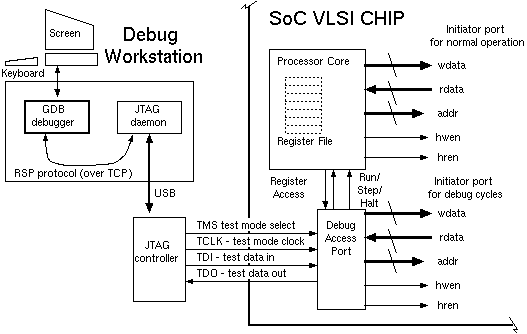

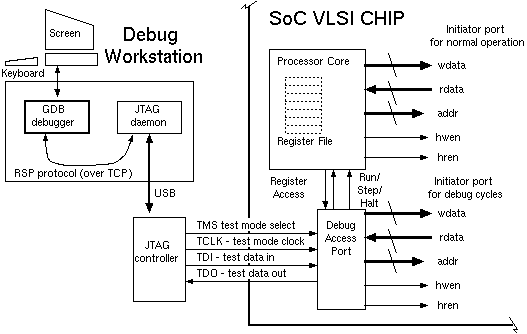

External access is often via the »JTAG port which is fairly slow, owing to bit-serial data format, so sometimes parallel bus connections are provided.

The basic facilities commonly provided are

In a typical setup the debugger (such as GNU gdb) runs on a remote workstation via a TCP connection carrying the RSP protocol to the debug target. For real silicon, the target is a JTAG controller (e.g. connected to the workstation via USB) whereas on a SystemC model it is an SC_MODULE that is listening for RSP on a unix socket.

| 38: (C) 2008-13, DJ Greaves, University of Cambridge, Computer Laboratory. |