# Computer Design

Computer Laboratory

Part Ib in Computer Science

Copyright © Simon Moore, University of Cambridge, Computer Laboratory, 2011

Contents:

- 17 lectures of the Computer Design course

- Paper on Chuck Thacker's Tiny Computer 3

- White paper on networks-on-chip for FPGAs

- Exercises for supervisions and personal study

- SystemVerilog "cheat" sheet which briefly covers much of what was learnt using the Cambridge SystemVerilog web tutor

Historic note: this course has had many guises. Until last year the course was in two parts: ECAD and Computer Design. Past paper questions on ECAD are still mostly relevant though there has been a steady move toward SystemVerilog rather than Verilog 2001. This year the ECAD+Arch labs have been completely rewritten for the new tPad hardware and making use of Chuck Thacker's Tiny Computer 3 (TTC). The TTC is being used instead of our Tiger MIPS core since it is simple enough to be easily altered/upgraded as a lab. exercise. As a consequence some of the MIPS material has been removed in favour of a broader introduction to RISC processors; and the Manchester Baby Machine in SystemVerilog has been replaced by an introduction to the TTC and its SystemVerilog implementation. A new lecture on system's design on FPGA using Altera's Qsys tool has been added.

#### Computer Design — Lecture 1 Introduction and Motivation

#### Overview of the course

How to build a computer:

- $\bullet~$  4  $\times$  lectures introducing Electronic Computer Aided Design (ECAD) and the Verilog/SystemVerilog language

- Cambridge SystemVerilog web tutor (home work + 1 lab. session equivalent to 4 lectures worth of material)

- 7 × ECAD+Architecture Labs

- 14 × lectures on computer architecture and implementation

#### Contents of this lecture

- Aims and Objectives

- Implementation technologies

- Technology trends

- The hardware design gap

#### Recommended books and web material

- Recommended book (both ECAD and computer architecture):

- D.M. Harris & S.L. Harris. Digital Design and Computer Architecture, Morgan Kaufmann 2007

- General Computer Architecture:

- J.L. Hennessey and D.A. Patterson, "Computer Architecture A Quantitative Approach", Morgan Kaufmann, 2002 (1996 edition also good, 1990 edition is only slightly out of date, 2006 edition good but compacted down)

- ◆ D.A. Patterson and J.L. Hennessey, "Computer Organization & Design — The Hardware/Software Interface", Morgan Kaufmann, 1998 (1994 version is also good, 2007 version now available)

- Web:

- http://www.cl.cam.ac.uk/Teaching/current/CompDesign/

#### **Revising State Machines**

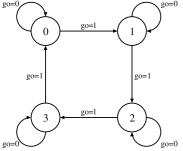

#### Start with a state transition graph

IF i.e. it is a 2-bit counter with enable (go) input

#### **Revising State Machines**

#### Then produce the state transition table

| input |    | rent<br>ate | next<br>state |             |  |  |

|-------|----|-------------|---------------|-------------|--|--|

| go    | n1 | n0          | n1'           | n0'         |  |  |

| 0     | 0  | 0           | 0             | 0           |  |  |

| 0     | 0  | 1           | 0             | 1           |  |  |

| 0     | 1  | 0           | 1             | 0<br>1<br>1 |  |  |

| 0     | 1  | 1           | 1             |             |  |  |

| 1     | 0  | 0           | 0             |             |  |  |

| 1     | 0  | 1           | 1             | 0           |  |  |

| 1     | 1  | 0           | 1             | 1           |  |  |

| 1     | 1  | 1           | 0             | 0           |  |  |

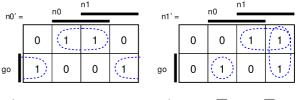

#### **Revising State Machines**

#### Then do Boolean minimisation, e.g. using K-maps

$n0' = n0 \oplus go$

$n1' = \overline{go}.n1 + \overline{n0}.n1 + n0.\overline{n1}.go$  $n1' = go.(n0 \oplus n1) + \overline{go}.n1$

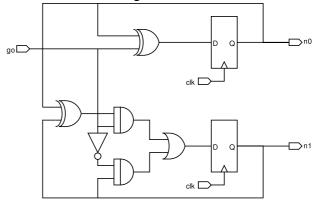

#### **Revising State Machines**

#### And the final circuit diagram

IP now implement...

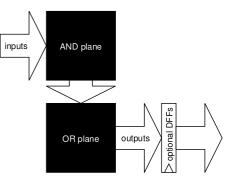

#### **Revising PLAs**

- PLA = programmable logic array

- advantages cheap (cost per chip) and simple to use

- disadvantages medium to low density integrated devices (i.e. not many gates per chip) so cost per gate is high

#### **Field Programmable Gate Arrays**

- a sea of logic elements made from small SRAM blocks

- $\diamond~$  e.g. a 16×1 block of SRAM to provide any boolean function of 4 variables

- often a D-latch per logic element

- programmable interconnect

- ♦ program bits enable/disable tristate buffers and transmission gates

- advantages: rapid prototyping, cost effective in low to medium volume

- disadvantages: 15 $\times$  to 25 $\times$  bigger and slower than full custom CMOS ASICs

#### **CMOS ASICs**

- CMOS = complementary metal oxide semiconductor

- ASIC = application specific integrated circuit

- full control over the chip design

- some blocks might be full custom

- ◊ i.e. laid out by hand

- other blocks might be standard cell

- cells (gates, flip-flops, etc) are designed by hand but with inputs and outputs in a standard configuration

- designs are synthesised to a collection of standard cells...

- $\diamond$   $\hfill \hfill \hf$

- blocks may also be generated by a macro

- typically used to produce regular structures which need to be packed together carefully, e.g. a memory block

- this material is covered in far more detail in the Part II VLSI course

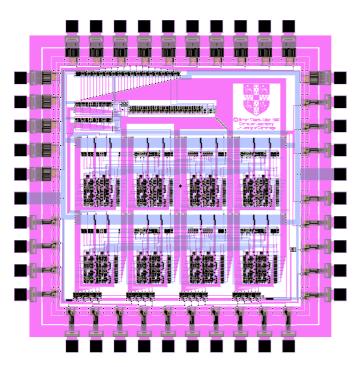

#### Example CMOS chip

• very small and simple test chip from mid 1990s

#### See interactive version at:

http://www.cl.cam.ac.uk/users/swm11/testchip/

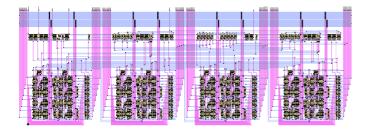

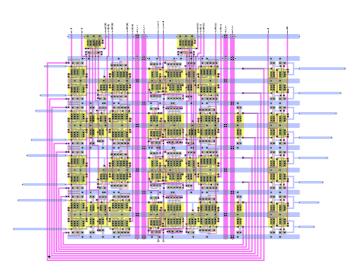

#### Zooming in on CMOS chip (1)

#### Zooming in on CMOS chip (2)

9

10

11

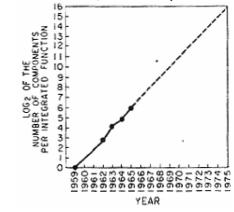

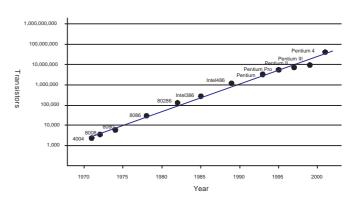

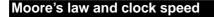

#### Trends — Moore's law & transistor density

- In 1965 Gordon Moore (Intel) identified that transistor density was increasing exponentially, doubling every 18 to 24 months

- Predicted > 65,000 transistors by 1975!

#### Moore's law more recently

12

13

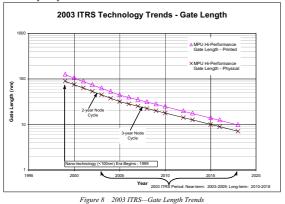

#### ITRS gate length

ITRS = International Technology Roadmap for Semiconductors

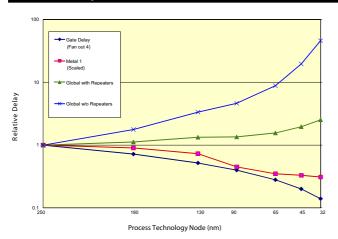

Figure 54 Delay for Metal 1 and Global Wiring versus Feature Size From ITRS 2003

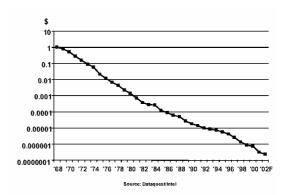

#### Moore's law and transistor cost

15

16

17

Amazing — faster, lower power, and cheaper at an exponential rate! ٠

#### Moore's Law in Perspective 1

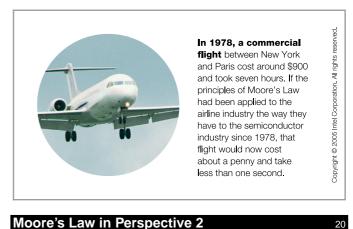

Moore's Law in Perspective 2

to such we Is connected to a or automobiles, a ipment. The elec be feasible today in the pro

that the price of a transistor is now about the same as that of one printed newspaper character.

Copyright @ 2005 Intel Corporation. All rights reserved.

#### Where is the end point?

- what will limit advancement?

- ♦ fabrication cost (cost per transistor remaining static)?

- $\diamond$ feature sizes hit atomic levels?

- power density/cooling limits?  $\diamond$

- design and verification challenge?  $\diamond$

- will silicon be replaced, e.g. by graphine?

18

#### Danger of Predictions

22

23

"I think there's a world market for about five computers.", Thomas J Watson, Chairman of the Board,  $\mathsf{IBM}$

"Man will never reach the moon regardless of all future scientific advances." Dr. Lee De Forest, inventor of the vacuum tube and father of television.

"Computers in the future may weigh no more than 1.5 tons", Popular Mechanics, 1949

Figure 13 Impact of Design Technology on SOC LP-PDA Implementation Cost From ITRS 2003 - Design

#### **Comments on Design Cost**

24

25

- design complexity

- ♦ exponential increase in design size

- transistors and wires are becoming harder to analyse and becoming less predictable

- engineering efficiency

- the number of engineers in the world is not going up exponentially!

- ♦ but numerous ways to improve matters, e.g. better design reuse

- ◊ parallels with the "software crisis"

- verification and test

٠

verifying functional correctness and identifying manufacturing defects is getting harder

#### Improving productivity: Verilog

```

the Verilog hardware description language (HDL) improves productivity

```

• example — counter with enable from earlier:

if(go) n <= n+1; // do the conditional counting

• wrapped up into a module + clock assignment + declarations:

```

module counter2b(clk, go, n);

input clk, go; // inputs: clock and go (count enable) signal)

output [1:0] n; // output: 2-bit counter value

reg [1:0] n; // n is stored in two D flip-flops

always @(posedge clk) // when the clock ticks, do the following...

if(go) n <= n+1; // do the conditional counting

endmodule

```

implement via automated synthesis (compilation) and download to FPGA

So Computer Scientists are needed to design hardware

#### Logic Modeling, Simulation and Synthesis

#### Lectures so far

• the last lecture looked at technology and design challenges

#### **Overview of this lecture**

this lecture introduces:

- modeling

- simulation techniques

- synthesis techniques for logic minimisation and finite state machine (FSM) optimisation

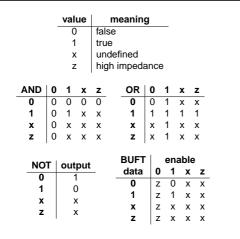

#### Four valued logic

#### Modeling a tri-state buffer

module BUFT(

output reg out,

input in,

input enable);

// behavioural use of always which activates whenever

// enable or in changes (i.e. both positive and negative edges)

always @(enable or in)

if(enable)

out = in;

else

out = 1'bz; // assign high-impedance

endmodule

Such models are useful for simulation purposes but cannot usually be synthesised. Rather, such a model would have to be replaced by a predefined cell/component.

#### Verilog and logic levels

- 'z' can be used to indicate tri-state (see previous example)

- '===' can be used to compare wires to see if they are tri-state

- similarly, !== is to === what != is to ==

IF these operators are only useful for simulation (not supported for synthesis)

${\ensuremath{\hbox{\sc vel }}} \ensuremath{\mathsf{z}}$  during simulation x and z are treated as false for conditional expressions

| ==               |   |   |   |   | ===              | 0 | 1 | x | z |

|------------------|---|---|---|---|------------------|---|---|---|---|

| 0                | 1 | 0 | Х | Х | 0                | 1 | 0 | 0 | 0 |

| 1                | 0 | 1 | х | х | 1                | 0 | 1 | 0 | 0 |

| х                | x | х | х | х | х                | 0 | 0 | 1 | 0 |

| 0<br>1<br>x<br>z | x | х | х | х | 0<br>1<br>x<br>z | 0 | 0 | 0 | 1 |

#### Verilog casex and casez statements

- casez z values are considered to be "don't care"

- casex z and x values are considered to be "don't care"

- example:

| reg  | [3:0]  | r; |   |                        |

|------|--------|----|---|------------------------|

| case | ex(r)  |    |   |                        |

|      | 4'ЪООО | )x | : | <pre>statement1;</pre> |

|      | 4'b10  | ٢1 | : | statement2;            |

|      | 4'b1x1 | L1 | : | statement3;            |

| endo | ase    |    |   |                        |

| some values of r | the outcome         |

|------------------|---------------------|

| 4'b0001          | matches statement 1 |

| 4'b0000          | matches statement 1 |

| 4'b000x          | matches statement 1 |

| 4'b000z          | matches statement 1 |

| 4'b1001          | matches statement 2 |

| 4'b1111          | matches statement 3 |

|                  |                     |

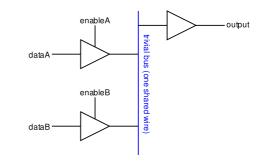

#### Problems when modeling a tristate bus

Scenario:

start: dataA=dataB=enableB=0 and enableA=1 step 1: enableAstep 2: enableB+

- ? what is that state of the bus between steps 1 and 2? 0 or z?

- ? should the output ever go to x and what might the implications be if it does?

#### Further logic levels

- to simulate charge holding elements (capacitors) we could introduce two additional logic levels:

- weak\_low indicates that the capacitor has been discharged to low but is not being driven by anything

- ♦ weak\_high indicates that the capacitor has been charged high but is not being driven by anything

- further logic levels can be added to account for larger capacitances, rise and fall times, etc.

- the standard VHDL (another HDL) logic library uses a 46 state logic called t\_logic

12

13

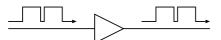

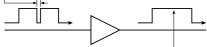

#### Modeling delays

adding delays to behavioural Verilog (typically for simulation only), e.g. to delay by 10 simulator time units:

assign #10 delayed\_value = none\_delayed\_value;

pure delay — signals are delayed by some time constant

• inertial delay - models capacitive delay

pulse is much less than a gate delay (runt pulse)

runt pulse has been filtered out by the gate capacitance

#### **Obtaining delay information**

- a design can be synthesised to gates and approximations of the gate delays can be used

- gates in the netlist can be placed and wires routed so that wire lengths and capacitances can be determined

- models of gates can vary

- e.g. input to output delay depends upon which input is changing (even on trivial gates like a 2 input NOR) and this variation may be modeled but often some simplifying assumption is made like taking the average case

- back annotation

- delay information can be back annotated, e.g. adding hidden information to a schematic diagram

- delay information and netlist can be converted back into a low level structural Verilog model

#### Naïve simulation

- simplifying assumptions for our naïve simulation:

- ◊ each gate has unit delay (1 virtual time unit)

- ♦ netlist held as a simple list of gates with enumerated wires to indicate interconnect

- ◊ an array of wires holds the state

- simulation takes the current state (wire information) and evaluates each gate to in turn to produce a new set of state. This process is then repeated.

- problems:

- many parts of the circuit are likely to be inactive at a given instant in time, so having to reevaluate each gate for every simulation cycle is expensive

- ♦ delays have to be implemented as long strings of buffers which is likely to slow things down

#### Introduction to discrete event simulation

sometimes called Delta simulation

only changes in state cause gates to be reevaluated

- data structures:

- ♦ gates are modeled as objects (including current state information)

- $\diamond$  state changes passed as (virtual) timed events or messages

- $\diamond$   $\;$  pending events are inserted into a time ordered event queue

- simulation loops around:

- o pick event with least virtual time off the event queue

- ♦ pass event to appropriate gate

- ◊ gate evaluates and produces an event if its output has changed

- issues:

- ♦ cancelling runt pulses (event removal)

- modeling wire delays (add wires as simple gates)

#### SPICE

- SPICE = Simulation Program with Integrated Circuit Emphasis

- used for detailed analog transistor level simulation

- models nonlinear components as a set of differential equations representing the circuit voltages, currents and resistances

- simulation is highly accurate (accuracy dependent upon models provided)

- but simulation is computationally expensive and only practical for small circuits

- sometimes SPICE is used to analyse standard cells in order to determine typical delays, etc, to enable reasonably accurate digital simulation to be undertaken

- there are various versions of commercial and free SPICE which vary in performance and accuracy depending on implementation details

#### Synthesis — Design metrics

many digital logic circuits achieve the same function, but vary in the:

number of gates

10

- total wiring length

- timing properties through various paths

- power consumption

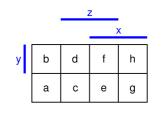

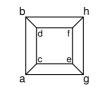

#### Karnaugh maps and Boolean n-cubes

implicants are sub n-cubes

#### Quine-McCluskey minimisation — step 1

- ♦ find all prime implicants using x.y + x.ȳ = x repeatedly

- ♦ first produce a truth table for the function and extract the minterms required (i.e. rows in the truth table where the output is 1)

- exhaustively compare pairs of terms which differ by 1 bit to produce a new term where the 1 bit difference is marked by a don't care X

- tick those terms which have been selected since they are covered by the new term

- repeat with new set of terms (X must match X) until no more terms can be produced

- terms which are unticked are the prime implicants

#### Quine-McCluskey minimisation — step 2

- select smallest set of prime implicants to cover function:

- ◊ prepare prime-implicants chart

- select essential prime implicants for which one or more of its minterms are unique (only once in the column)

- obtain a new reduced PI chart for remaining prime-implicants and the remaining minterms

- select one or more of remaining prime implicants which will cover all the remaining minterms

- computationally very expensive for large equations

- tools like Espresso use heuristics to improve performance but at the expense of not being exact

- ♦ there are better but far more complex algorithms for exact Boolean minimisation

#### QM example

#### An example truth table

| Code | ABCD | Term                                    | Output |

|------|------|-----------------------------------------|--------|

| 0    | 0000 | $\overline{ABCD}$                       | 0      |

| 1    | 0001 | $\overline{ABCD}$                       | 0      |

| 2    | 0010 | $\overline{AB}C\overline{D}$            | 0      |

| 3    | 0011 | $\overline{AB}CD$                       | 0      |

| 4    | 0100 | $\overline{A}B\overline{C}\overline{D}$ | 0      |

| 5    | 0101 | $\overline{A}B\overline{C}D$            | 1      |

| 6    | 0110 | $\overline{A}BC\overline{D}$            | 0      |

| 7    | 0111 | $\overline{A}BCD$                       | 0      |

| 8    | 1000 | $A\overline{BCD}$                       | 0      |

| 9    | 1001 | $A\overline{BC}D$                       | 0      |

| 10   | 1010 | $A\overline{B}C\overline{D}$            | 1      |

| 11   | 1011 | $A\overline{B}CD$                       | 1      |

| 12   | 1100 | $AB\overline{CD}$                       | 0      |

| 13   | 1101 | $AB\overline{C}D$                       | 1      |

| 14   | 1110 | $ABC\overline{D}$                       | 1      |

| 15   | 1111 | ABCD                                    | 1      |

|      |      |                                         |        |

#### QM example cont...

#### The active minterms

| Code | ABC1 |

|------|------|

| 5    | 0101 |

- 10 1010

- 11 1011 13 1101

- 14 1110

- 15 1111

#### QM example cont...

15

16

17

18

14

15

#### Find terms which differ by one bit

| Code | ABCD   | Notes           |

|------|--------|-----------------|

| 5    | 0101   | $\checkmark$    |

| 10   | 1010   | $\checkmark$    |

| 11   | 1011   | $\checkmark$    |

| 13   | 1101   | $\checkmark$    |

| 14   | 1110   | $\checkmark$    |

| 15   | 1111   | $\checkmark$    |

| New  | terms: |                 |

| А    | X101   | combining 5,13  |

| В    | 101X   | combining 10,11 |

| С    | 1X10   | combining 10,14 |

| D    | 1X11   | combining 11,15 |

| Е    | 11X1   | combining 13,15 |

| F    | 111X   | combining 14,15 |

|      |        |                 |

$\mathbf{k}$  where  $\checkmark$  indicates that a term is covered

#### QM example cont...

## Find terms which differ by one bit and have X's in the same place

| Code | ABCD   | Notes                               |

|------|--------|-------------------------------------|

| Α    | X101   |                                     |

| в    | 101X   | $\checkmark$                        |

| С    | 1X10   | $\checkmark$                        |

| D    | 1X11   | $\checkmark$                        |

| Е    | 11X1   |                                     |

| F    | 111X   | $\checkmark$                        |

| New  | terms: |                                     |

| G    | 1X1X   | combining B,F                       |

| Н    | 1X1X   | combining C,D — duplicate so remove |

|      |        |                                     |

### QM example cont...

1110

1111

#### The prime implicant chart

| active | minterms |              | terms        |              |

|--------|----------|--------------|--------------|--------------|

| Code   | ABCD     | A: X101      | E: 11X1      | G: 1X1X      |

| 5      | 0101     | $\checkmark$ |              |              |

| 10     | 1010     |              |              | $\checkmark$ |

| 11     | 1011     |              |              | $\checkmark$ |

| 13     | 1101     | $\checkmark$ | $\checkmark$ |              |

- where ✓ indicates that a term covers a minterm

- so terms A and G cover all minterms (i.e. they are essential terms) and term E is not required

- therefore the minimised equation is  $B.\overline{C}.D + A.C$

#### Further comments on logic minimisation

- if optimising over multiple equations (i.e. multiple outputs) with shared terms then the *Putnam and Davis* algorithm can be used (but not much more sophisticated than QM)

- sum of products form may not be simplest logic structure: multi-level logic structures are often more compact (ongoing research in this area)

- ♦ sometimes simplification in terms of XOR gates (rather than AND and OR gates) is more appropriate called *Read-Muller logic*

e.g. see "Hug an XOR gate today: an introduction to Read-Muller logic": http://www.reed-electronics.com/ednmag/archives/1996/030196/05df4.htm

don't-cares are very important for efficient logic minimisation so when writing Verilog it is important to indicate undefined values, e.g.:

20

21

#### Adding redundant logic

- 23

- adding redundant logic can reduce the amount of wiring required

#### Wire minimisation

24

25

- wire minimisation is largely the job of the place & route tool and not the synthesis tool

- the synthesis tools may include:

- ◊ redundant logic

- ◇ placement hints to guide place & route

- manual floor planning may also be performed to force the hand of the place & route tools

- ◊ increasingly important as chips get larger

#### Finite state machine minimisation

- state minimisation

- ◊ remove duplicate states

- remove redundant/unreachable states

- state assignment

- assign a unique binary code to each state

- ♦ the logic structure depends on the assignment, thus this needs to be done optimally (e.g. algorithms: NOVA, JEDI)

- BUT much Verilog code is explicit about register usage so little optimisation possible

- higher level behavioral Verilog introduces implicit state machines which the synthesis tool is in a better position to optimise

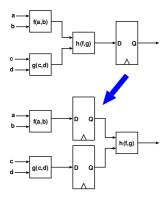

#### **Retiming and D-latch migration**

- if a path through some logic is too long then it is sometimes possible to move the flip-flops to compensate without altering the functional behaviour

- similarly, it is sometimes possible to add extra D-latches to make a pipeline longer

#### Testing

#### **Overview of this lecture**

Introduce:

- production test (fault models, test metrics, test pattern generation, scan path testing)

- functional test (in simulation and on FPGA)

- introduction to ECAD lab sessions

#### Objectives of production testing

- check that there are no manufacturing defects

- NOT to check whether you have designed the device correctly

- economics: cost of detecting a faulty component is lowest before it is packaged and embedded in a system

- for consumer products:

- faulty goods cost a lot to replace so require low defect rate (e.g. less that 0.1%)

- but testing costs money so don't exhaustively test 98% fault coverage probably acceptable

- for medical, aerospace and military (i.e. safety-critical) products:

- ♦ must have 100% coverage

- in some instances a design will contain redundant units (e.g. on DRAM) which can be selected, thereby improving yield

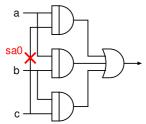

#### Fault models

- logical faults

- ♦ stuck-at (most common)

- ♦ CMOS stuck-open

- ♦ CMOS stuck-on

- ♦ bridging faults

- parametric faults

- ◊ low/high voltage/current levels

- ♦ gate or path delay-faults

- testing methods:

- ◇ parametric (electrical) tests also detect stuck-on faults

- logical tests detect stuck-at faults

- transition tests detect stuck-open faults

- timed transition tests detect delay faults

#### Testability

- controllability

- the ability to set and clear internal signals

- it is particularly useful to be able to change the state in registers inside a circuit

- observability

- the ability to detect internal signals

#### Fault reductions

- checkpoints

- ♦ points where faults could occur

- fault equivalence

- ◇ remove test for least significant fault

- fault dominance

2

- $\diamond$  if every test for fault  $f_1$  detects  $f_2$  then  $f_1$  dominates  $f_2$

- $\Rightarrow$  only have to generate test for  $f_1$

fault equivalence

#### fault dominance

#### Test patterns and path sensitisation

- test patterns are sequences of (input values, expected result) pairs

- path sensitisation

- inputs required in order to make a fault visible on the outputs

#### Test effectiveness

- undetectable fault --- no test exists for fault

- redundant fault undetectable fault whose occurrence does not affect circuit operation

- testability = <u>number of detectable faults</u> number of faults

- effective faults = number of faults redundant faults

- fault coverage = <u>number of detectable faults</u> number of effective faults

- test set size = number of test patterns

- I goal is 100% fault coverage (not 100% testability) with a minimum sized test set

13

14

#### Automatic Test Pattern Generation (ATPG)

Many algorithms developed to do ATPG, e.g. D-Algorithm, PODEM, PODFM-X etc. General idea:

- generate a sequence of test vectors to identify faults ٠

- test vector =  $\langle input vector, correct output vector \rangle$

- input and output vectors are typically 3 valued: (0, 1, X)

- simple combinatoric circuits (no feedback) can be supplied with test vectors in any order

- circuits with memory (latches/combinatoric feedback) require sequences of test vectors in order to modify internal state, e.g. consider having to test:

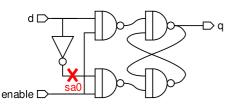

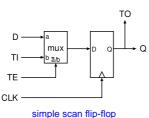

#### Scan path testing

- make all the D flip-flops (DFFs) in a circuit "scannable"

- G i.e. add functionality to every DFF to enable data to be shifted in and out of the circuit

- this is a significant aid to ATPG since testing latches is now easy and the flip-flops have sliced the circuit into small combinatoric blocks which are usually nice and simple to test

- boundary scan just have a scan path around I/O pads of chip or macrocell

#### JTAG standard

- the IEEE 1149 (JTAG) international standard defines 4 wires for boundary scan:

- $\diamond$ tms = test mode select (high for boundary scan)

- tdi = test data input (serial data in)  $\diamond$

- $\diamond$ tck = test clock (clock serial data)

- tdo = test data output (read back old data whilst new is shifted in)  $\diamond$

- also used for other things, e.g.:

- ◊ in-circuit programming of FPGAs (e.g. Altera)

- single step debugging of embedded microprocessors  $\diamond$

#### **Functional testing**

- objective: ensure that the design is functionally correct

- simulation provides great visibility and testability

- implementation on FPGA allows rapid prototyping and testing of I/O

#### Functional testing in simulation

gives good visibility of state

advantages:

$\diamond$

- allows test benches to be written to check many cases

- is quick to do some tests since no place & route required (unless you are simulating a post-layout design to check timing)

- disadvantages:

- slow if simulations need to be for billions of clock cycles (e.g. 10s or  $\diamond$ more of real-time)

- difficult to test if complex input/output behaviour is required (e.g. if  $\diamond$ your test bench had to look like a VGA monitor, mouse or Ethernet link)

#### Verilog test benches

Test benches can be written in Verilog (models in other languages, e.g. C, are also possible)

#### Example showing Verilog test bench constructs:

module testsim (output reg reg clk, rst; // clock a output reg [3:0] counter); // counte // clock and reset signals

- initial begin // start of sequence of initialisation steps

- clk = 0; rst = 1; // initialise registers in sequence using blocking assigment

- #100 rst = 0; #1000

- // wait 100 simulation cycles, then... // release the reset signal // wait 1000 simulation cycles, then...

- \$stop(); 11 ... stop simulation

- end

always #5 clk = !clk; // make clock oscillate at 10 simulation step rate

// Now illustrate two approaches to monitoring signals

always @(counter) // when ever counter changes \$display("at\_time\_%d:\_counter\_changed\_to\_=\_%d",\$time,counter);

- always @(negedge clk) // after clock edge \$display("at\_time\_%d:\_counter\_updated\_to\_%d",\$time,counter);

- // design under test (usually instatitated module)

- always\_ff @(posedge clk or posedge rst)

if(rst) counter <= 0;

else counter <= counter+1;</pre>

- endmodule

#### Functional testing on FPGA

advantages:

10

- ♦ fast implementation

- ◊ connected to real I/O

- disadvantages:

- ◊ lack of visibility on signals

- Partly solved with SignalTap see later

- difficlut to test side cases

- have to wait for complete place & route between changes  $\diamond$

#### Key debouncer example

```

module debounce(input clk,

input rst,

// clock at 50MHz

// reset

input bouncy,

output reg clean,

// bouncy signal

// clean signal

output reg [15:0] numbounces);

reg prev.syncbouncy;

reg [20:0] counter;

wire counterAtMax = &counter; // N.B. vector AND of the bits

Wire counterings = accenter, wire synchouncy;

synchroniser dosync(.clk(clk),.async(bouncy),.sync(syncbouncy));

always_ff @(posedge clk or posedge rst)

if(rst) begin

counter <= 0;

numbounces \leq = 0:

prev_syncbouncy

clean <= 0;

<= 0;

end else begin

prev_syncbouncy <= syncbouncy;

if (syncbouncy != prev_syncbouncy) begin // detect change

counter <= 0;

counter <= 0,

numbounces <= numbounces+1;

end else if (!counterAtMax) // no bouncing, so keep counting

counter <= counter+1;

else // output clean signal since input stable for

// 2°21 clock cycles (approx. 42ms)

clean <= syncbouncy;</pre>

end

endmodule

```

#### Synchroniser

module synchroniser( input clk, input async, output reg sync); reg metastable; always @(posedge clk) begin

metastable <= asvnc sync <= metastable; end endmodule

#### Test bench for key debouncer

module testbench ( output reg clk, output reg rst, output reg bouncy, output clean);

wire [15:0] numbounces;

## initial begin

|                            | clk=0;                                            |      |        |         |          |      |        |          |

|----------------------------|---------------------------------------------------|------|--------|---------|----------|------|--------|----------|

|                            | rst=1;                                            |      |        |         |          |      |        |          |

|                            | bouncy=0;                                         |      |        |         |          |      |        |          |

| #100                       | rst=0;                                            |      |        |         |          |      |        |          |

| #10000                     | bouncy=1;                                         | //   | 1e3    | ticks   |          |      |        |          |

| #10000                     | bouncy=0;                                         |      |        |         |          |      |        |          |

| #100000                    | bouncy=1;                                         | //   | 1e4    | ticks   |          |      |        |          |

| #100000                    |                                                   |      |        |         |          |      |        |          |

| #1000000                   |                                                   | //   | 1e5    | ticks   |          |      |        |          |

| #1000000                   | bouncy=0;                                         |      |        |         |          |      |        |          |

|                            | bouncy=1;                                         |      |        |         |          |      |        |          |

|                            | bouncy=0;                                         | //   | 3e6    | ticks   | (should  | have | gone   | high)    |

| #3000000                   | \$stop;                                           |      |        |         |          |      |        |          |

| end                        |                                                   |      |        |         |          |      |        |          |

| <b>always</b> #5 clk       | = !clk;                                           |      |        |         |          |      |        |          |

| always@(rst)<br>\$display( | "%09d:⊔rst.                                       | .=%  | 6d", 9 | \$time, | rst);    |      |        |          |

|                            | cy <b>or</b> clear<br>"%09d:_bour<br>\$time,bound | ncy. | .=_%   | dclea   | ın.⊒=_%d |      | ounces | s_=_%d", |

endmodule

Modelsim simulation output 0: bouncy = 0 clean = x numbounces = x 0: rst = 1 0: bouncy = 0 clean = 0 numbounces = 0 100: rst = 010100: bouncy = 1 clean = 0 numbounces = 0

| π. | 10100.     | bouncy -  | +   | crean - | 0 | numbounces | _ | 0 |

|----|------------|-----------|-----|---------|---|------------|---|---|

| #  | 10125:     | bouncy =  | 1   | clean = | 0 | numbounces | = | 1 |

| #  | 20100:     | bouncy =  | 0   | clean = | 0 | numbounces | = | 1 |

| #  | 20125:     | bouncy =  | 0   | clean = | 0 | numbounces | = | 2 |

| #  | 120100:    | bouncy =  | 1   | clean = | 0 | numbounces | = | 2 |

| #  | 120125:    | bouncy =  | 1   | clean = | 0 | numbounces | = | 3 |

| #  | 220100:    | bouncy =  | 0   | clean = | 0 | numbounces | = | 3 |

| #  | 220125:    | bouncy =  | 0   | clean = | 0 | numbounces | = | 4 |

| #  | 1220100:   | bouncy =  | 1   | clean = | 0 | numbounces | = | 4 |

| #  | 1220125:   | bouncy =  | 1   | clean = | 0 | numbounces | = | 5 |

| #  | 2220100:   | bouncy =  | 0   | clean = | 0 | numbounces | = | 5 |

| #  | 2220125:   | bouncy =  | 0   | clean = | 0 | numbounces | = | 6 |

| #  | 12220100:  | bouncy =  | 1   | clean = | 0 | numbounces | = | 6 |

| #  | 12220125:  | bouncy =  | 1   | clean = | 0 | numbounces | = | 7 |

| #  | 33191645:  | bouncy =  | 1   | clean = | 1 | numbounces | = | 7 |

| #  | 42220100:  | bouncy =  | 0   | clean = | 1 | numbounces | = | 7 |

| #  | 42220125:  | bouncy =  | 0   | clean = | 1 | numbounces | = | 8 |

| #  | 63191645:  | bouncy =  | 0   | clean = | 0 | numbounces | = | 8 |

| #  | Break in M | odule tes | tbe | nch at  |   |            |   |   |

|    |            |           |     |         |   |            |   |   |

#### On FPGA test

15

16

17

#

#

#

#

```

module keybounce (

input CLOCK.50,

input [17:0] SW,

input [3:0] KEY,

output [17:0] LEDR,

output [7:0] LEDG);

(* preserve, noprune *) reg [31:0] timer;

(* preserve, noprune *) reg [31:0] timer;

(* preserve, noprune *) reg [2:0] delayed_triggercondition;

(* preserve, noprune *) reg bouncy;

(* keep, noprune *) wire triggercondition = SW[0] ^ clean;

(* keep, noprune *) wire [15:0] numbounces;

always @(posedge CLOCK.50) begin

bouncy <= SW[0];</pre>

delayed_triggercondition <= {delayed_triggercondition[1:0], triggercondition};</pre>

end

always @(posedge CLOCK.50 or posedge rst)

if (rst) timer <=0; else timer <=timer +1;

synchroniser syncrst(.clk(CLOCK.50)..async(!KEY[0])..sync(rst));

debounce DUT(.clk(CLOCK.50)..rst(rst).bouncy(bouncy)..clean(clean).

..numbounces(numbounces));

assign LEDG[1:0] = clean ? 2'b11 : 2'b00;

assign LEDG[1:2] = SW[0] ? 2'b11 : 2'b00;

assign LEDG[7:4] = {delayed_triggercondition[2],bouncy,triggercondition,timer[31]}

assign LEDR[17:0] = {2'b00,numbounces[15:0]};

module

end

nodule

```

#### SignalTap

- motivation: provide analysis of state of running system

- approach: automatically add extra hardware to capture signals of interest

- SignalTap: Altera's tool to make this easier

- IF for further details see the Lab. web pages

#### SignalTap example

- probe the debouncer degin

- difficulty: bounce events happen infrequently and there is not enough memory on the FPGA to store a long trace of events every clock cycle

- solution: start and stop signal capture to observe the interesting bits (trigger signals added to the design to achieve this)

18

## SignalTap example setup

| <b>D</b>                                   | Quar                   | tus II -       | C:/swm11/AlteraTests/DE                | 2-keybounce            | /keybounce - key | /bounce - [stp1.s | tp*]                                   | -            | ALC: NO. 1 |               |            |   |            |                                           | -                     |            | × |

|--------------------------------------------|------------------------|----------------|----------------------------------------|------------------------|------------------|-------------------|----------------------------------------|--------------|------------|---------------|------------|---|------------|-------------------------------------------|-----------------------|------------|---|

| Eil                                        | e <u>E</u>             | dit <u>V</u> i | ew <u>P</u> roject P <u>r</u> ocessing | <u>T</u> ools <u>W</u> | indow            |                   |                                        |              |            |               |            |   |            |                                           |                       |            |   |

| 📾 🔌 🗣 🔳 🛍 Ready to acquire 🔄 🛛 👗 🕺 表 宏 🕆 📟 |                        |                |                                        |                        |                  |                   |                                        |              |            |               |            |   |            |                                           |                       |            |   |

| Ins                                        | tance                  | Manag          | jer: 🛛 🍬 🎝 🔳 🔛 Re                      | ady to acquire         |                  | (2)               |                                        |              |            |               |            | × | JTAG Chair | n Configuration:                          | JTAG ready            | - 😰        | × |

|                                            | tance                  |                | Status                                 |                        |                  | lemory: 54272     | M512,MLAB:                             |              | 9K: 14/105 | M-BAM,M       | 1144K: 0/0 |   |            |                                           |                       |            | 1 |

|                                            | auto                   | signalt        | ap_0 Not running                       |                        | 1876 cells       | 54272 bits        | 0 blo                                  | cks          | 14 blocks  |               | 0 blocks   |   | Hardware:  | USB-Blaster [L                            | JSB-0]                | Setup      |   |

|                                            |                        |                |                                        |                        |                  |                   |                                        |              |            |               |            |   | Device:    | @1: EP2C35 (                              | (0x020B40DD) 🔹        | Scan Chain |   |

|                                            |                        |                |                                        |                        |                  |                   |                                        |              |            |               |            |   | >>  SOF    | Manager 🙏                                 |                       |            | - |

|                                            | >>> SOF Manager. 📥 🖞 📃 |                |                                        |                        |                  |                   |                                        |              |            |               |            |   |            |                                           |                       |            |   |

| T                                          | trigge                 | er: 2009       | 9/08/20 12:32:20 #1                    |                        | Allow all char   | iges              | •                                      |              |            |               |            |   | Signa      | l Configuration:                          |                       |            | × |

| l r                                        |                        |                | Node                                   | Data Enable            | Trigger Enable   | Storage Enable    |                                        | Qualifier    | Trigger Co | nditions      |            |   |            | -<br>k: [CLOCK_50                         |                       |            |   |

|                                            | Гуре                   | Alias          | Name                                   | 52                     | 1                |                   | Start Basic -                          | //           | 1 Basic    | -             |            |   |            | (15)                                      |                       |            |   |

| 11                                         |                        |                | delayed_triggercondition[0]            | 2                      | ম                | ন                 | X                                      | 8            | x          |               |            |   | Da         |                                           |                       |            | = |

| [                                          | ø                      |                | delayed_triggercondition[2]            | 2                      | Г                | <u> </u>          |                                        | x            |            |               |            |   | Sa         | imple depth: 1 K                          | ▼ RAM type: Auto      | 7          |   |

|                                            | Ø                      |                | ⊕ numbounces                           | R                      |                  | ঘ                 | XXXXXh                                 | XXXXXh       |            |               |            |   |            | Segmented:                                | 1 K 1 sample segments | +          |   |

|                                            | 0                      |                | bouncy                                 | ন                      |                  | ঘ                 |                                        |              |            |               |            |   | 1.000      | - 99 9 7 19 9 9 9 9 9 9 9 9 9 9 9 9 9 9 9 | True compo cognicito  |            |   |

|                                            | 0                      |                | clean                                  | <b>v</b>               |                  | ঘ                 |                                        |              |            |               |            |   |            | Storage qualifier                         | -                     |            |   |

|                                            | 0                      |                | () timer                               | <b>v</b>               | Г                | <b>N</b>          | XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX | XXXXXXXXXXXX |            |               |            |   |            | Туре:                                     | Start/Stop            | _          |   |

|                                            |                        |                |                                        |                        |                  |                   |                                        |              |            |               |            |   | 8          | Input port:                               |                       | -          |   |

|                                            |                        |                |                                        |                        |                  |                   |                                        |              |            |               |            |   |            |                                           |                       |            |   |

|                                            |                        |                |                                        |                        |                  |                   |                                        |              |            |               |            |   |            | Record data of                            | discontinuities       |            | - |

| J                                          | D                      | ata 📘          | Setup                                  |                        |                  |                   |                                        |              |            |               |            |   |            |                                           |                       | 110.11     |   |

| E.                                         | ierarc                 | hy Disp        | lair                                   |                        |                  |                   |                                        |              | × 🗆 Data   |               |            |   |            |                                           |                       |            | × |

|                                            |                        |                | bounce                                 |                        |                  |                   |                                        |              |            | uto_signaltap | 0          |   |            |                                           |                       |            |   |

|                                            |                        |                |                                        |                        |                  |                   |                                        |              |            |               |            |   |            |                                           |                       |            |   |

|                                            |                        |                |                                        |                        |                  |                   |                                        |              |            |               |            |   |            |                                           |                       |            |   |

|                                            |                        |                |                                        |                        |                  |                   |                                        |              |            |               |            |   |            |                                           |                       |            |   |

|                                            |                        |                |                                        |                        |                  |                   |                                        |              |            |               |            |   |            |                                           |                       |            |   |

|                                            | aut                    | o_signa        | itap_0                                 |                        |                  |                   |                                        |              |            |               |            |   |            |                                           |                       |            |   |

| For                                        | Help                   | press          | F1                                     |                        |                  |                   |                                        |              |            |               |            |   |            |                                           |                       |            | 1 |

|                                            |                        |                |                                        |                        |                  |                   |                                        |              |            |               |            |   |            |                                           |                       |            |   |

22

#### SignalTap example trace

|  | 23 |

|--|----|

|  |    |

| Quartus          | II - C:/swm11/AlteraTests/D | E2-keybound | ce/keybounce   | - keybounce | - [stp1.stp  | p*]      |          |                |              |              |       |       |            |                |              |            |          | _ <b>D</b> × |

|------------------|-----------------------------|-------------|----------------|-------------|--------------|----------|----------|----------------|--------------|--------------|-------|-------|------------|----------------|--------------|------------|----------|--------------|

| ile <u>E</u> dit | View Project Processin      | <u> </u>    | <u>W</u> indow |             |              |          |          |                |              |              |       |       |            |                |              |            |          |              |

| P 10             | 🔛 🔳 🔛 Ready to acqu         | re          | - 2            | ata 🕰 🗄     | <b>e</b> 🗄 🗉 | * 💷 🗖    |          |                |              |              |       |       |            |                |              |            |          |              |

| nstance Ma       |                             |             |                |             | 2            |          |          |                |              |              |       | ×     | JTAG Chair | n Configuratio | n: JTAG      | ready      | 6        | ð            |

| nstance          | Status                      | 1           | LEs: 1876      | Memory: 54  |              | M512,MLA | B: 0/0   | M4K,M9K: 14/10 | 5 M-RAM      | M144K: 0/0   |       | -     |            |                |              |            |          | a            |

| auto_sig         | naltap_0 Not running        |             | 1876 cells     | 54272       | bits         | 0        | blocks   | 14 block       | s            | 0 blocks     | 8     | 200   | Hardware:  | USB-Blas       | ter [USB-0]  |            | <u> </u> | Setup        |

|                  |                             |             |                |             |              |          |          |                |              |              |       |       | Device:    | @1: EP2        | C35 (0x020B4 | 0DD)       | ▼ S      | can Chain    |

|                  |                             |             |                |             |              |          |          |                |              |              |       |       | . L. cor   | 1              |              |            |          |              |

|                  |                             |             |                |             |              |          |          |                |              |              |       |       | >>] 50F    | Manager:       | å (          |            |          |              |

|                  |                             |             |                |             |              |          |          |                |              |              |       |       |            |                |              |            |          |              |

| 10g: 200         | 9/08/20 12:34:22 #0         | 34          |                |             |              | 25       | _        |                |              | ert time bar | ·     |       |            | 27             |              |            | 20       |              |

| Type A           | Node<br>lias Name           | 110         | 111            | 112         | 113          | 35       |          | 115 11         |              | 6<br>17      | 118   | 119   |            | 37<br>120      | 121          | 122        | 38       |              |

|                  | delayed_triggercondition[0  | 1888        |                | 112         | 113          |          |          | 112 11         | •            |              | 110   | 112   |            | 120            | 121          | 144        | ,2,      |              |

| 0                | delayed_triggercondition[2  |             |                | _           |              |          |          | -              |              |              |       | _     |            |                |              |            |          |              |

|                  | bouncy                      |             | _              | _           |              |          |          | L              |              | _            |       |       |            | -              |              |            |          |              |

| 0                | clean                       | -           | -              | -           |              |          |          |                |              |              |       |       |            | -              |              |            |          |              |

| ē,               |                             |             | 0046h          | X 0047      | h X          | 0048h X  |          | 004Bh          |              | -            | 004Ch |       |            |                |              | 004Dh      |          |              |

|                  |                             | 2438600     | 10 \ 2438600   |             |              |          | 24420475 |                | 244204761    | 24520192     |       | 3 X 2 | 245201924  | 2472990        | 78 X 24729   | 9079 X 247 | 299080 X | 422463954    |

|                  |                             |             |                |             |              |          |          |                |              |              |       |       |            |                |              |            |          |              |

|                  |                             |             |                |             |              |          |          |                |              |              |       |       |            |                |              |            |          | +            |

| Data             | E Setup                     |             |                |             |              |          |          |                |              |              |       |       |            |                |              |            |          |              |

| Hierarchy        | Display:                    |             |                |             |              |          |          | × Г            | Data Log: 🖸  |              |       |       |            |                |              |            |          | ×            |

|                  | keybounce.                  |             |                |             |              |          |          |                | auto_signalt |              |       |       |            |                |              |            |          |              |

| auto_s           | ignaltap_0                  |             |                |             |              |          |          | -1             |              |              |       |       |            |                |              |            |          |              |

| r Help, pr       | ress F1                     |             |                |             |              |          |          |                |              |              |       |       |            |                |              |            |          |              |

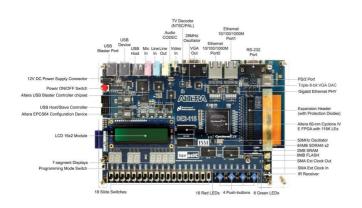

#### Design for FPGAs

#### **Overview of this lecture**

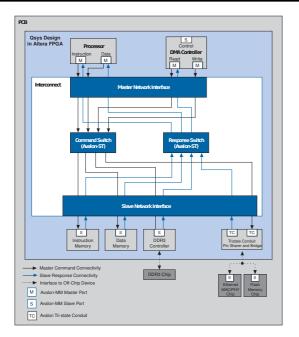

this lecture:

- introduces the tPad FPGA board

- gives some more SystemVerilog design examples

- presents some design techniques

- explains some design pitfalls

#### ECAD+Architecture lab. teaching boards (tPads)

#### **FPGA** design flow

Lab 1 shows you how to use the following key components of Quartus:

- Text editor

- Simulator

- ♦ Compiler

- ♦ Timing analyser

- ♦ Programmer

- The web pages guide you through some quite complex commercial-grade tools

#### Specifying pin assignments

Import a qsf file (tPad\_pin\_assignments.qsf) which tells the Quartus tools an assignment of useful names to physical pins.

```

set_location_assignment PIN_Y2 -to CLOCK_50

set_location_assignment PIN_H22 -to HEX0[6]

set_location_assignment PIN_J22 -to HEX0[5]

...

set_location_assignment PIN_AC27 -to SW[2]

set_location_assignment PIN_AC28 -to SW[1]

set_location_assignment PIN_AB28 -to SW[0]

...

set_location_assignment PIN_E19 -to LEDR[2]

set_location_assignment PIN_F19 -to LEDR[1]

set_location_assignment PIN_G19 -to LEDR[0]

...

set_location_assignment PIN_R6 -to DRAM_ADDR[0]

set_location_assignment PIN_V8 -to DRAM_ADDR[1]

set_location_assignment PIN_V8 -to DRAM_ADDR[2]

```

#### Example top level module: lights

module lights(

input CLOCK\_50, output [17:0] LEDR, input [17:0] SW); logic [17:0] lights; assign LEDR = lights; // do things on the rising edge of the clock always\_ff @(posedge CLOCK\_50) begin lights <= SW[17:0]; end endmodule

#### Advantages of simulation

- simulation is main stay of debugging on FPGA and even more so for ASIC

- new ECAD labs emphasise simulation

- ◊ better design practise test driven development

- ◊ better for you avoid lots of long synthesis runs

- old ECAD labs relied on generating video which is difficult to get helpful results from in simulation

#### Problems with simulation

- simulation is of an abstracted world which may hide horrible side cases!

- emulation of external input/output devices can be tricky and time consuming

- ♦ e.g. video devices or an Ethernet controller

- semantics of SystemVerilog are not well defined

- results in discrepancies between simulation and synthesis

- ♦ simulation and synthesis tools typically implement different a subset of the language

- but even with these weaknesses, simulation is still very powerful

- simulation can even model things that the real hardware will not model, e.g. D flip-flops that are not reset properly will start in 'x' state in simulation so can easily be found vs. real-world where some "random" state will appear

13

14

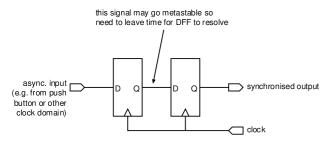

## The danger of asynchronous inputs and bouncing buttons

- I asynchronous inputs cause problems if they change state near a clock edge

- ♦ metastability can arise

- ♦ sampling multiple inputs particularly hazardous

- ♦ where possible, sample inputs at least twice to allow metastability to resolve (resynchronisation)

- never use an asynchronous input as part of a conditional without resynchronising it first

#### Two flop synchroniser

mean time between failure (MTBF) can be calculated:

$$MTBF = \frac{e^{\frac{t}{\tau}}}{f_d f_c T_u}$$

- where:

- t is the time allowed for first DFF to resolve, so allowing just a small amount of extra time to resolve makes a big difference since it is an exponential term

- ♦ \(\tau=\mathcal{gain}\) of DFF

- $\diamond$   $f_d$  and  $f_c$  are the frequencies of the data and clock respectively

- $\diamond$   $T_w$  is the metastability time window

#### Example: Two DFF Synchroniser

```

module synchroniser(

input clk,

input asyncIn,

output reg syncOut);

```

```

reg metastableFF;

```

```

always @(posedge clk) begin

metastableFF <= asyncIn;

syncOut <= metastableFF;

end

```

endmodule

Quartus understands this construct and can optimise placement of the DFFs — see Chapter 11 of the Quartus manual

#### **Resetting your circuits**

- the Altera PLDs default to all registers being zero after programming

- but in other designs you may need to add a reset signal and it is often handy to have your FPGA design resettable from a button

- most Verilog synthesis tools support the following to perform an asynchronous reset:

```

always @(posedge clk or posedge reset)

if(reset)

begin

// registers which need to be assigned a reset value go here

end

else

```

```

begin

```

10

11

// usual clocked behaviour goes here

end

note that distribution of reset is an issue handled by the tools like clock distribution

#### Signalling protocols

- often need a go or done or new\_data signal

- pulse

- ◇ pulse high for one clock cycle to send an event

- problem: the receiving circuit might be a multicycle state machine and may miss the event (e.g. traffic light controller which stops only at red if sent a "stop" event)

- 2-phase

- every edge indicates an event

- ◊ can send an event every clock cycle

- 4-phase

- ◇ level sensitive rising and falling edges may have a different meaning

- ◊ or falling edges might be ignored

- ◊ can't send an event every clock cycle

#### Example: 2-phase signalling

module delay( req, ack, clk );

```

input req; // input request

output ack; // output acknowledge

input clk; // clock

[15:0] dly;

reg

reg

prev_req;

reg

ack;

always @(posedge clk) begin

prev_req <= req;</pre>

if(prev_req != req)

dly <= -1;

// set delay to maximum value

else if(dly != 0)

dly <= dly-1;

// dly>0 so count down

if(dly == 1)

ack <= !ack;

end

endmodule

```

#### Example: 4-phase signalling

```

module loadable_timer(count_from, load_count, busy, clk);

input [15:0] count_from;

input load_count;

output busy;

input clk;

reg

busy;

[15:0] counter;

reg

always @(posedge clk)

if(counter!=0)

counter <= counter - 1;</pre>

else

begin

busy <= load_count; // N.B. wait for both edges of load_count

if(load_count && !busy)

counter <= count_from;</pre>

end

```

endmodule

#### **Combination control paths**

- typically data-paths have banks of DFFs inserted to pipeline the design

- sometimes it can be slow to add DFFs in the control path, especially flow-control signals

- examples: fifo\_one\_A which latches all control signals and fifo\_one\_B which has a combinational backward flow-control path

- design B is faster except when lots of FIFO elements are joined together and the combinational path becomes long

#### Example: FIFO with latched control signals

```

module fifo_one_A(

// clock & reset

input clk,

input rst,

// input side

input logic [7:0] din,

input logic din_valid,

output logic din_ready,

// output side

output logic dout_valid,

input logic dout_valid,

input logic dout_valid,

input logic dout_valid;

din_ready = !full;

end

always_ff @(posedge clk or posedge rst)

if (rst) begin

dout_valid <= 1'b0;

dout_valid <= 1'b0;

dout_valid <= 1'b1;

else if (din_ready & din_valid) begin

dout_valid <= 1'b1;

end

endmodule</pre>

```

#### Example: FIFO with combination reverse control path 18

```

module fifo_one_B(

// clock & reset

input clk,

input rst,

// input side

input logic [7:0] din,

input logic [7:0] din,

input logic [7:0] dout,

output logic dout_valid,

input logic dout_valid,

input logic dout_valid,

input logic dout_valid,

input logic dout_valid;

din_ready = !full || dout_ready;

end

always_ff @(posedge clk or posedge rst)

if(rst) begin

dout_valid <= 1'b0;

dout_<= 8'hxx;

end else if(dul.ready && dun_valid)

dout<= din;

dout<= 1'b0;

else if(din_ready && dun_valid)

dout<= din;

dout<= din;

dout<= din;

dout<= 1'b1;

end

endmodule</pre>

```

#### Example: FIFO test bench

15

16

```

module test_fifo_one_A();

logic clk, rst;

initial begin

clk = 1;

rst = 1;

#15 rst = 0;

end

always #5 clk = !clk;

logic [7:0] din, dmiddle, dout;

logic (/:0) ain, amiadie, dout;

logic din_valid, din_ready;

logic dout_valid, dout_ready;

fifo_one_A stage0(.clk, .rst, .din, .din_valid, .din_ready,

.dout(dmiddle), .dout_valid(dmiddle_valid),

.dout_ready(dmiddle_ready));

fifo_one_A stage0(.clk

fifo_one_A stage1(.clk, .rst,

.din(dmiddle), .din_valid(dmiddle_valid),

.din_ready(dmiddle_ready),

.dout, .dout_valid, .dout_ready);

logic [7:0] state;

always_ff@(posedge clk or posedge rst)

if(rst) begin

state <= 8'd0:

din_valid <= 1'b0;

dout_ready <= 1'b1;

end else begin

if (dout_valid && dout_ready)

$display("%05t:_fifo_output_=_%1d", $time, dout);

if (din_ready) begin

din <= (state+1)*3;

din_valid <= 1'b1;</pre>

state <= state+1;

if (state >8) $stop;

end else

din_valid <= 1'b0;

end // else: !if(rst)

endmodule

```

23

21

25

#### Example: one hot state encoding

- states can just have an integer encoding (see last lecture)

- $\diamond$   $\;$  but this can result in quite complex if expressions, e.g.:

```

if(current_state== 'red)

//...stuff to do when in state 'red

if(current_state== 'amber)

```

- //...stuff to do when in state 'amber

- an alternative is to use one register per state vis:

```

reg [3:0] four_states;

wire red = four_states[0] || four_states[1];

wire amber = four_states[1] || four_states[3];

wire green = four_states[2];

always @(posedge clk or posedge reset)

```

if(reset)

```

four_states <= 4'b0001;

```

else

four\_states <= {four\_states[2:0],four\_states[3]}; // rotate bits</pre>

#### SystemVerilog pitfalls 1: passing buses around 21

- automatic bus resizing

- buses of wrong width get truncated or padded with 0's

wire [14:0] addr; // oops got width wrong, but no error generated wire [15:0] data; CPU the\_cpu(addr,data,rw,ce,clk); MEM the\_memory(addr,data,rw,ce,clk);

- wires that get defined by default

- if you don't declare a wire in a module instance then it will be a single bit wire, e.g.:

wire [15:0] addr; // oops, no data bus declared so just 1 bit wide CPU the\_cpu(addr,data,rw,ce,clk); MEM the\_memory(addr,data,rw,ce,clk);

• you pass too few parameters to a module but no error occurs!

#### SystemVerilog pitfalls 2: naming and parameter ordering 22

- modules have a flat name space

- can be difficult to combine modules from different projects because they may share some identical module names with different functions

- parameter ordering is easy to get wrong

- but you can specify parameter mapping vis:

which is identical to:

loadable\_timer lt2(timerval, start, busy, clk);

provided nobody has changed <code>loadable\_counter</code> since you last looked!

in SystemVerilog there is a short hand for variables passing with identical names, e.g. .clk(clk) = .clk

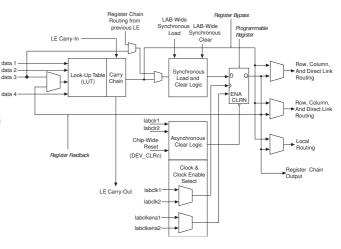

#### **FPGA** architecture

20

- FPGAs are made up of several different reconfigurable components:

- ♦ LUTs look-up tables (typically 4 inputs, one output) can implement any 4-input logic function

- ♦ LABs LUT + DFF + muxes

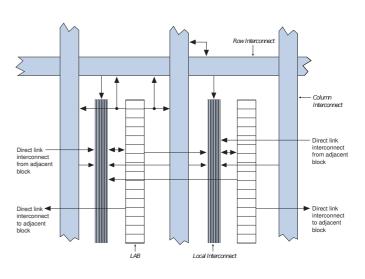

- ◊ programmable wiring (N.B. significant delay in interconnect)

- memory blocks (e.g. 9-kbits supporting different data widths, one or two ports, etc.)

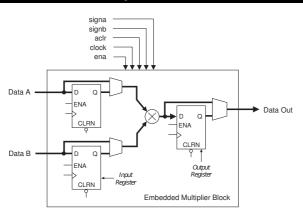

- DSP digital signal processing blocks, e.g. hard (i.e. very fast) multipliers

- I/O input/output blocks for normal signals, high speed serial (e.g. Ethernet, SATA, PCIe, ...), etc.

#### FPGA blocks — LABs

#### FPGA blocks — interconnect

#### FPGA blocks — multipliers

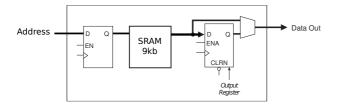

#### FPGA blocks — simplified single-port memory 27

- memory blocks called "Block RAM" BRAM

- dual-port mode supported, etc. + different data/address widths

#### Inferring memory blocks

28

26

٠

- SystemVerilog sometimes has to be written in a particular style in order that the synthesis tool can easily identify BRAM

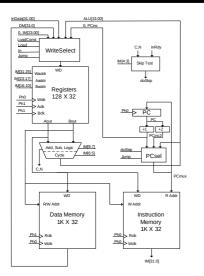

- e.g. on Thacker's Tiny Computer used in the labs, the register file is defined as:

Word rf\_block [0:(1<<\$bits(RegAddr))-1];</li>

```

RegAddr RFA.read.addr, RFB.read.addr;

always.ff @(posedge csi.clk.clk)

begin // register file port A

if (div)

rf.block[IM.pos.rw] <= WD;

else

RFA.read.addr <= IM.payload.ra;

end

assign RFAout = rf.block[RFA.read.addr];

```

```

always_ff @(posedge csi_clk_clk)

RFB_read_addr <= IM.payload.rb;

assign RFBout = rf_block[RFB_read_addr];

```

#### Static timing analysis

29

- place & route lays out logic onto FPGA

- static timing analysis determines timing closure, i.e. that we've met timing

- ♦ TimeQuest does this in Quartus

- ♦ looks at all paths from outputs of DFFs to inputs of DFFs

- max clock period = the worst case delay + DFF hold time + clock jitter margin

- ◇ Fmax determined critical that the circuit is clocked at a frequency below its Fmax

- much effort is made by Altera to ensure static timing analysis is accurate

#### Final words on ECAD

- Programmable hardware is here to stay, and it likely to become even more widespread in products (i.e. not just for prototyping)

- SystemVerilog is an improvement over Verilog, but a long way to go

- ◊ active research being undertaken into higher level HDLs

- e.g. more recent languages like Bluespec add channel communication mechanisms

- Hope you enjoy the Lab's and learning about hardware/software codesign

#### **Historical Computer Architecture**

#### Overview of this lecture

Review early computer design since they provide a good background and are relatively simple.

#### What is a "Computer"?

#### In the "iron age"

Early calculating machines were driven by human operators (this one's a Marchant).

#### Form factor?

#### Analogue Computers

- input variables are continuous and vary with respect to time

- output respond almost simultaneously to changes in input

- support continuous mathematical operators

- ♦ e.g. additions, subtraction, multiplication, division, integration, etc.

- BUT unable to store an manipulate large quantities of data, unlike digital computers

- electrical noise affects precision

- programs are hardwired

3

s

#### Hardwired Programming Digital Computers

• Programs (lists of orders/instructions) were hardwired into the machine.

#### Colossus

| Started/completed: | 1943/1943                                                    |

|--------------------|--------------------------------------------------------------|

| Project leader:    | Dr Tommy Flowers                                             |

| Programmed:        | pluggable logic & paper tape                                 |

| Speed:             | 5000 operations per second                                   |

| Power consumption: | 4.5 KW                                                       |

| Footprint:         | 360 feet <sup>2</sup> (approx) + room for cooling, operators |

| Notes:             | broke German codes, info. vital to success of D-day in       |

|                    | 1944                                                         |

|                    |                                                              |

#### ENIAC

| 1943/1945                           |

|-------------------------------------|

| John Mauchly and J. Presper Eckert. |

| plug board & switches               |

| 5000 operations per second          |

| 1000 feet <sup>2</sup>              |

|                                     |

#### Birth of the Stored Program Computer

- In 1945 John von Neumann wrote "First Draft of a Report on the EDVAC" in which the architecture of the stored-program computer was outlined.

- Electronic storage of programming information and data would eliminate the need for the more clumsy methods of programming, such as punched paper tape.

- This is the basis for the now ubiquitous control-flow model.

- ♦ Control-flow model is often called the von Neumann architecture

- However, it is apparent that Eckert and Mauchly also deserve a great deal of credit.

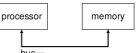

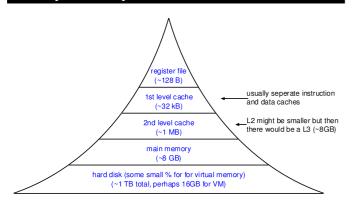

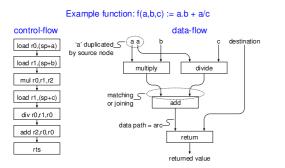

#### The Control-flow Model

bus \_\_\_\_\_the von Neumann bottleneck

The processor executes a list of instructions (order codes) using a program counter (PC) as a pointer into the list, e.g. to execute a=b+c:

order of executior

go and fetch the value of varaible b go and fetch the value of varaible c

add b and c together

store the result in variable a

#### What is a Processor?

- - $\diamond$  the "engine" of the computer if you like

- the processor is controlled by a program

- ◊ often a list of simple orders or instructions

- ♦ instructions (and other hardware mechanisms...) form the atomic building blocks from which programs are constructed

- executing many millions of instructions per second makes the computer look "clever"

#### A Quick Note on Programming

| very high level language (e.g. ML, Prolog)<br>high level language (e.g. Java)<br>assembler (mnemonics)<br>machine code (binary encoded numbers) |

|-------------------------------------------------------------------------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------------------------------------------------------------------------|

- programs are presented to the processor as machine code

- programs written in high level languages have to be compiled into machine code

#### Summer School of 1946

- the summer school on Computing at the University of Pennsylvania's Moore School of Electrical Engineering stimulated post-war construction of stored-program computers

- prompted work on EDSAC (Cambridge), EDVAC and ENIAC (USA)

- Manchester team had visited the Moore School but did not attend the summer school.

#### Manchester Mark I (The Baby)

| Input/Output: | June 1948<br>Tom Kilburn and F C (Freddie) Williams<br>buttons + memory is visible on Williams tube<br>William Tube |

|---------------|---------------------------------------------------------------------------------------------------------------------|

| memory.       |                                                                                                                     |

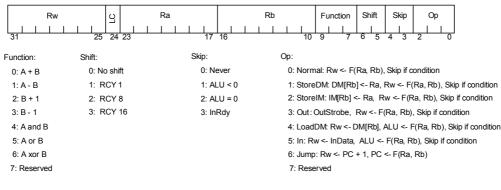

|               | $32 \times 32$ bit words                                                                                            |