# Multicore Programming: C++0x

#### Mark Batty

#### University of Cambridge

in collaboration with

Scott Owens, Susmit Sarkar, Peter Sewell, Tjark Weber

November, 2010

#### C++0x: the next C++

Specified by the C++ Standards Committee

Defined in The Standard, a 1300 page prose document

The design is a detailed compromise:

- performance, optimisations and hardware

- usability

- compatibility with the next C, C1X

- legacy code

### C++0x: the next C++

Our mathematical model is faithful to the intent of, and has influenced The Standard

The model:

- syntactically separates out expert features

- has a weak memory

- defines a happens-before relation

- requires non-atomic reads and writes to be DRF

- provides atomic reads and writes for racy programs

# The syntactic divide

#### An example of the syntax

```

// for regular programmers:

atomic_int x = 0;

x.store(1);

y = x.load();

```

```

// for experts:

x.store(2, memory_order);

y = x.load(memory_order);

atomic_thread_fence(memory_order);

```

#### With a choice of memory\_order

| mo_seq_cst | mo_release | mo_acquire |

|------------|------------|------------|

| mo_acq_rel | mo_consume | mo_relaxed |

### A model of two parts

An operational semantics:

Processes programs, identifying *memory actions*

Constructs candidate executions,  $E_{opsem}$

An axiomatic memory model:

Judges  $E_{\text{opsem}}$  paired with a memory ordering,  $X_{\text{witness}}$

Searches the consistent executions for races and unconstrained reads

# Judgement of the axiomatic model

$cpp\_memory\_model \ opsem \ (p : program) =$ let pre\_executions = { $(E_{\text{opsem}}, X_{\text{witness}})$ . opsem p  $E_{\text{opsem}} \wedge$ consistent\_execution  $(E_{\text{opsem}}, X_{\text{witness}})$  in if  $\exists X \in \text{ pre_executions}$ . (indeterminate\_reads  $X \neq \{\}$ )  $\lor$ (unsequenced\_races  $X \neq \{\}) \lor$  $(data_races X \neq \{\})$ then NONE **else** SOME pre\_executions

# The relations of a pre-execution

An  $E_{opsem}$  part containing:

sb — *sequenced before*, program order

asw — additional synchronizes with, inter-thread ordering

dd — data-dependence

An  $X_{\text{witness}}$  part containing:

rf — relates a write to any reads that take its value

sc — a total order over mo\_seq\_cst and mutex actions

mo — modification order, per location total order of writes

## A single threaded program

../examples/t1.c

# Memory actions

| ac | ction ::=                   |                          |

|----|-----------------------------|--------------------------|

|    | a:R <sub>na</sub> x=v       | non-atomic read          |

|    | a:W <sub>na</sub> x=v       | non-atomic write         |

|    | a:R <sub>mo</sub> x=v       | atomic read              |

|    | a:W <sub>mo</sub> x=v       | atomic write             |

|    | a:RMW <sub>mo</sub> x=v1/v2 | atomic read-modify-write |

|    | a:L x                       | lock                     |

|    | a:U x                       | unlock                   |

|    | a:F <sub>mo</sub>           | fence                    |

# Memory orders

Memory orders are shown as follows:

mo ::=

- SC memory\_order\_seq\_cst

- RLX memory\_order\_relaxed

- REL memory\_order\_release

- ACQ memory\_order\_acquire

- CON memory\_order\_consume

- A/R memory\_order\_acq\_rel

# Location kinds

location\_kind = MUTEX | NON\_ATOMIC | ATOMIC

```

actions_respect_location_kinds =

\forall a.

case location a of SOME l \rightarrow

(case location-kind l of

MUTEX \rightarrow is_lock_or_unlock a

\parallel NON_ATOMIC \rightarrow is_load_or_store a

\parallel ATOMIC \rightarrow is_load_or_store a \lor is_atomic_action a)

\parallel NONE \rightarrow T

```

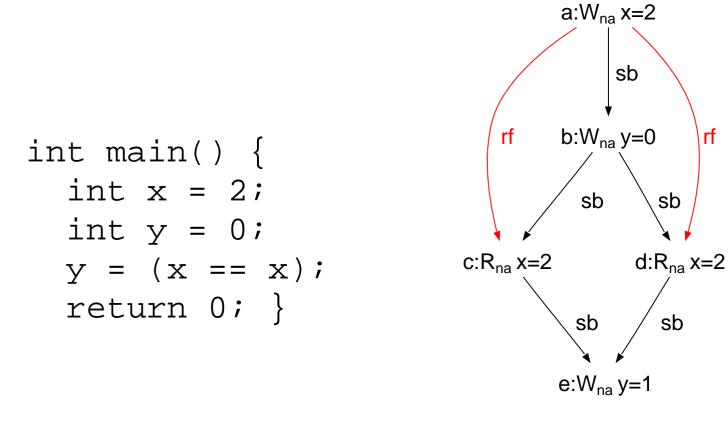

# That single threaded program again

$$int main() \{ int x = 2; int y = 0; y = (x == x); return 0; \}$$

$$a:W_{na} x=2$$

$$ff \quad b:W_{na} y=0$$

$$c:R_{na} x=2$$

$$d:R_{na} x=2$$

$$sb \quad sb$$

$$e:W_{na} y=1$$

../examples/t1.c

rf

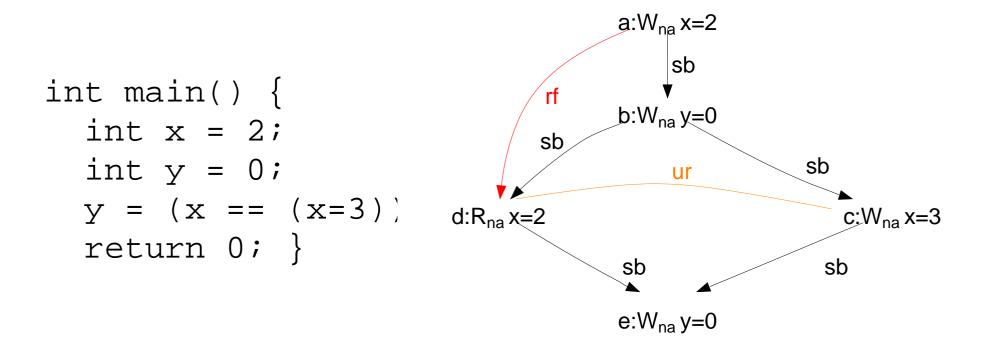

# Unsequenced race

unsequenced\_races = {(a, b). is\_load\_or\_store  $a \land is_load_or_store <math>b \land$   $(a \neq b) \land same_location \ a \ b \land (is_write \ a \lor is_write \ b) \land$ same\_thread  $a \ b \land$  $\neg(a \xrightarrow{sequenced-before} b \lor b \xrightarrow{sequenced-before} a)$ }

#### An unsequenced race

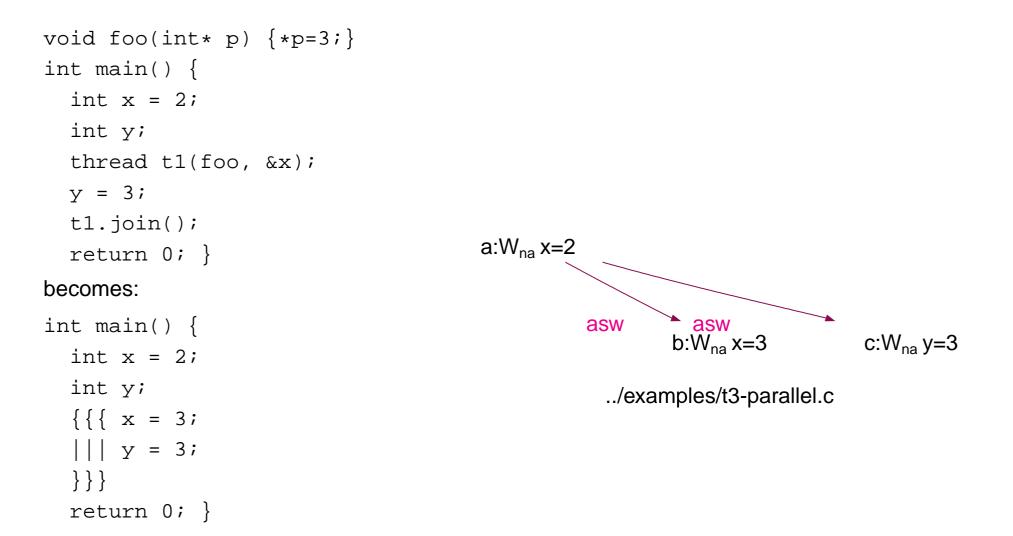

# A multi-threaded program

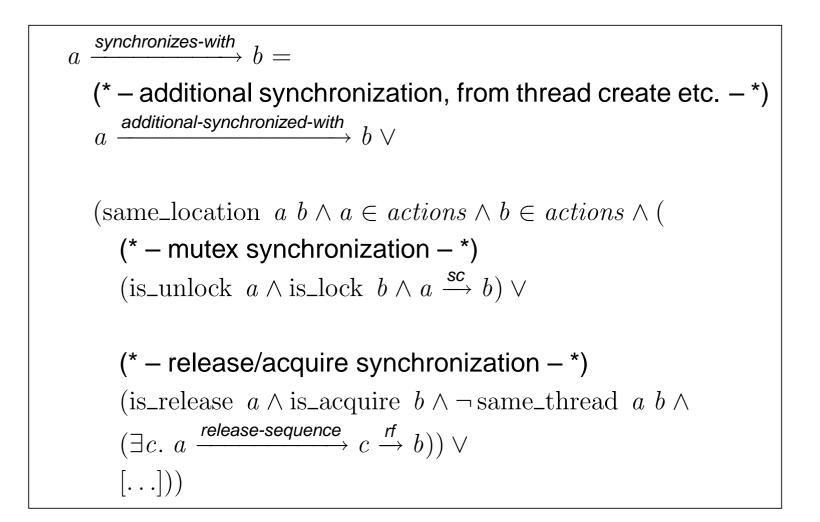

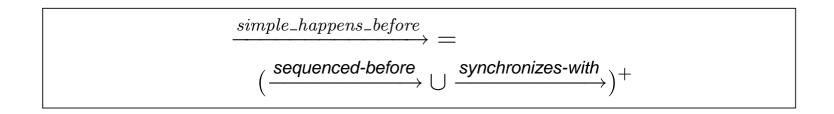

# Synchronizes-with and happens-before

The parent thread has synchronization edges, labeled asw, to its child threads. There are other ways to synchronize.

We will define the happens-before relation later. It contains the transitive closure of all synchronization edges and all sequenced before edges (amongst other things).

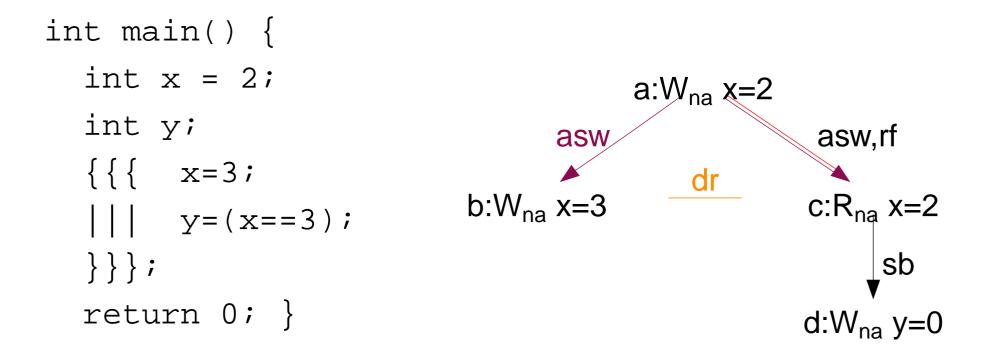

#### Data race

data\_races = {(a, b).

$$(a \neq b) \land \text{same_location } a \ b \land (\text{is\_write } a \lor \text{is\_write } b) \land$$

$\neg \text{same\_thread } a \ b \land$

$\neg(\text{is\_atomic\_action } a \land \text{is\_atomic\_action } b) \land$

$\neg(a \xrightarrow{happens-before} b \lor b \xrightarrow{happens-before} a)$ }

#### A data race

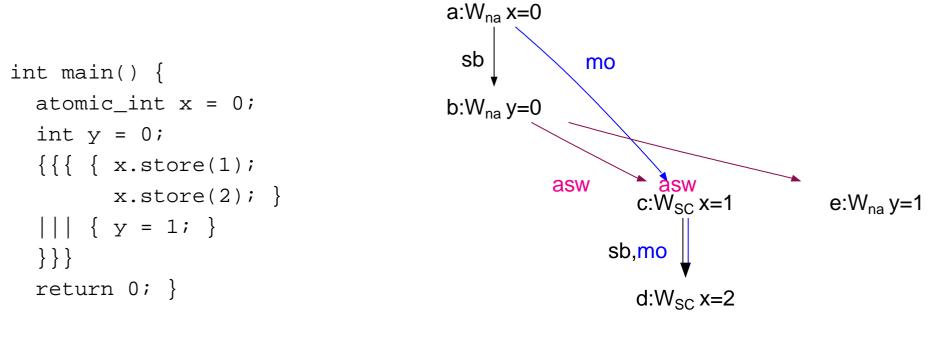

# Modification order

A total order of the writes at each atomic location, similar to coherence order on Power

../examples/t70-na-mo.c

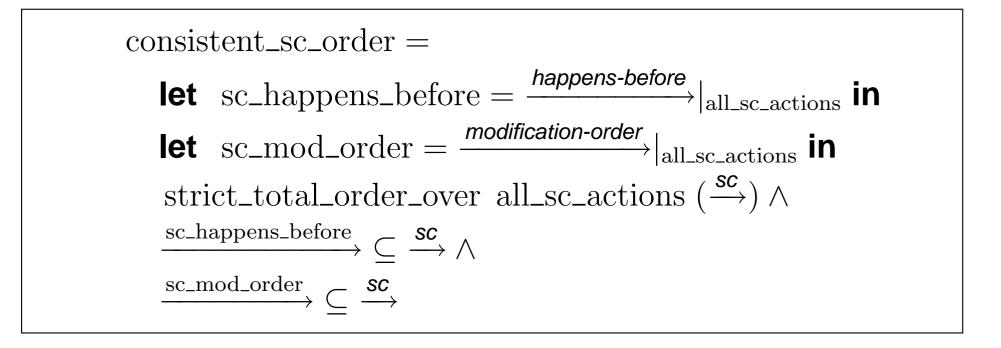

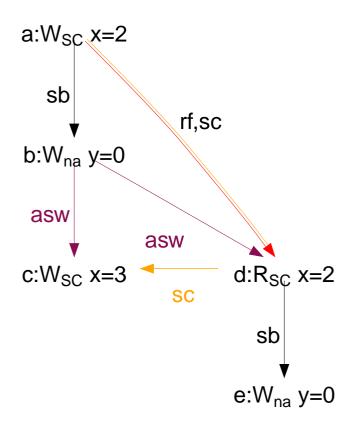

## SC order

There is a total order over all sequentially consistent atomic actions. SC atomics read the last prior write in SC order (or a non SC write).

#### Atomic actions do not race

```

int main() {

atomic_int x;

x.store(2, mo_seq_cst);

int y = 0;

{{{ x.store(3);

||| y = ((x.load()) == 3);

}};

return 0; }

```

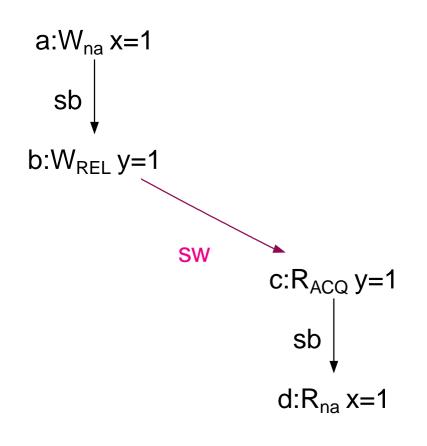

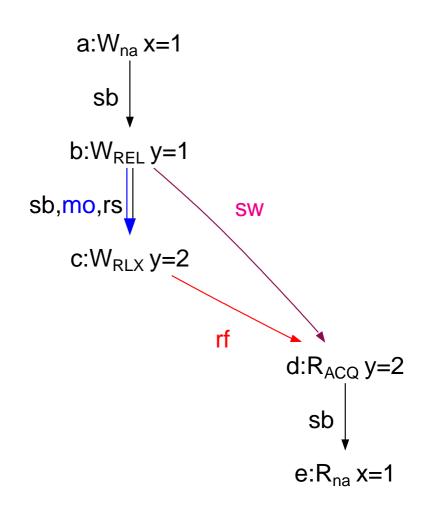

## The release-acquire idiom

| // sender | // receiver       |

|-----------|-------------------|

| x =       | while $(0 == y);$ |

| y = 1;    | r = x;            |

../examples/t15.c

#### **Release-acquire synchronization**

../examples/t8a.c

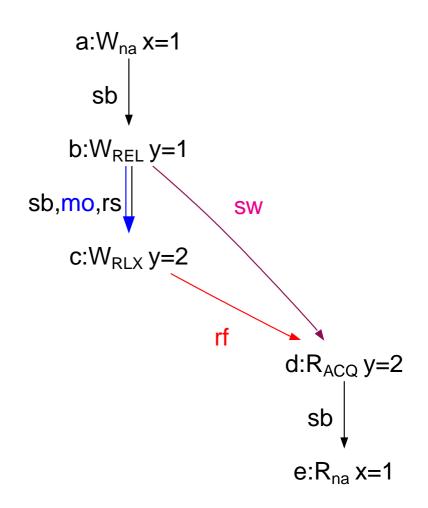

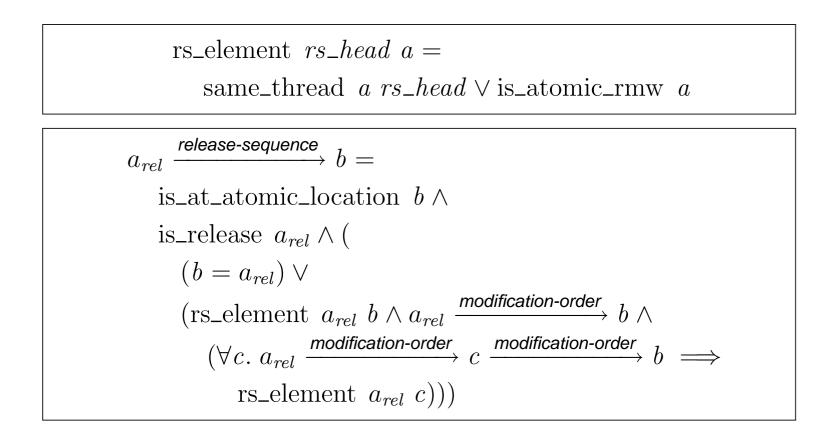

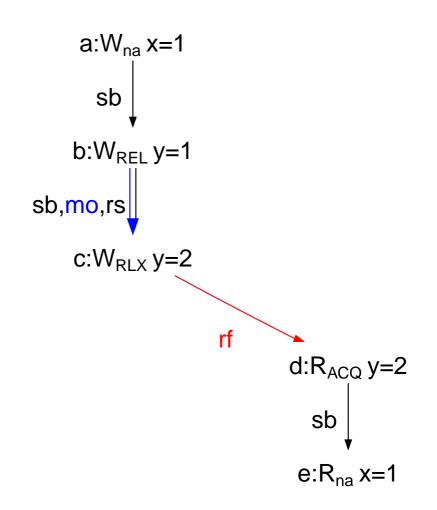

#### The release sequence

The release sequence is a sub-sequence of the the modification order following a release

#### An execution with a release sequence

../examples/t8a-no-sw.c

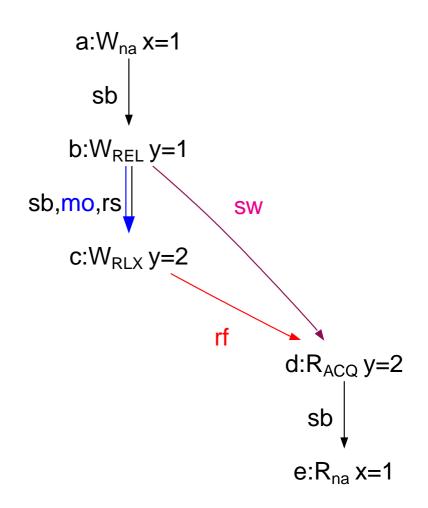

# Synchronizes-with

#### **Release-acquire synchronization**

../examples/t8a.c

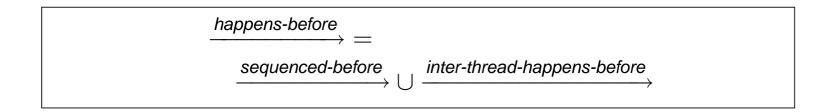

# Happens-before (without consume)

$consistent\_simple\_happens\_before =$ irreflexive  $(\xrightarrow{simple\_happens\_before})$

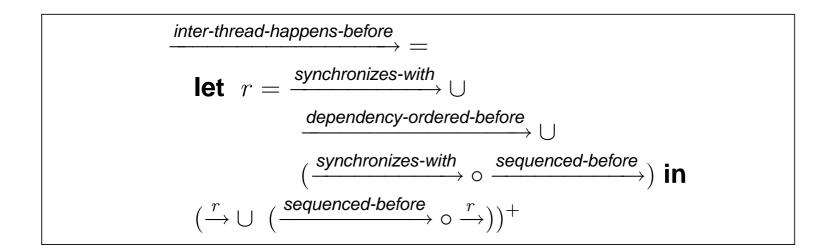

### Happens-before

| $consistent\_inter\_thread\_happens\_before =$            |  |

|-----------------------------------------------------------|--|

| irreflexive $(\xrightarrow{inter-thread-happens-before})$ |  |

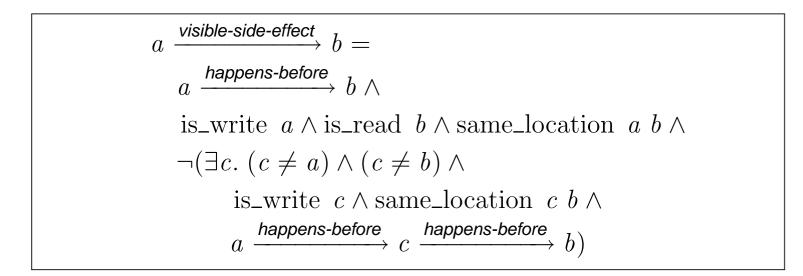

#### Visible side effect

Non-atomic reads read from one of their visible side effects

#### Visible sequence of side effects

Atomic reads read from a write in one of their visible sequences of side effects.

$$\begin{aligned} \text{visible\_sequence\_of\_side\_effects\_tail } vsse\_head \ b = \\ & \{c. \ vsse\_head \ \underline{\text{modification-order}} \ c \ \land \\ & \neg(b \ \underline{\text{happens-before}} \ c) \land \\ & (\forall a. \ vsse\_head \ \underline{\text{modification-order}} \ a \ \underline{\text{modification-order}} \ c \\ & \implies \neg(b \ \underline{\text{happens-before}} \ a)) \end{aligned}$$

#### An atomic read

../examples/t8a.c

### **Consistent reads-from mapping**

```

consistent_reads_from_mapping =

(\forall b. (is\_read b \land is\_at\_non\_atomic\_location b) \implies

(\text{if } (\exists a_{vse}. a_{vse} \xrightarrow{\text{visible-side-effect}} b)

then (\exists a_{vse}. a_{vse} \xrightarrow{visible-side-effect} b \land a_{vse} \xrightarrow{ff} b)

else \neg(\exists a. a \xrightarrow{f} b))) \land

(\forall b. (is\_read b \land is\_at\_atomic\_location b) \implies

(if (\exists (b', vsse) \in vsible-sequences-of-side-effects. (b' = b))

then (\exists (b', vsse) \in vsible-sequences-of-side-effects.

(b' = b) \land (\exists c \in vsse. \ c \xrightarrow{ff} b))

else \neg(\exists a. a \xrightarrow{\mathsf{rf}} b))) \land

(\forall (x, a) \in \stackrel{ff}{\rightarrow}.

\forall (y, b) \in \stackrel{ff}{\rightarrow}.

a \xrightarrow{\text{happens-before}} b \land

same_location a \ b \land is_at_atomic_location \ b

\implies (x = y) \lor x \xrightarrow{\text{modification-order}} y) \land

(\forall (a, b) \in \stackrel{n}{\rightarrow}. is_atomic_rmw b

\implies a \xrightarrow{\text{modification-order}} b) \land

(\forall (a, b) \in \stackrel{f}{\rightarrow} \text{ is_seq_cst } b

\implies \neg is\_seq\_cst \ a \lor

a \stackrel{sc}{\mapsto}_{\lambda c. \text{ is_write } c \land \text{same_location } b c } b) \land

[...]

```

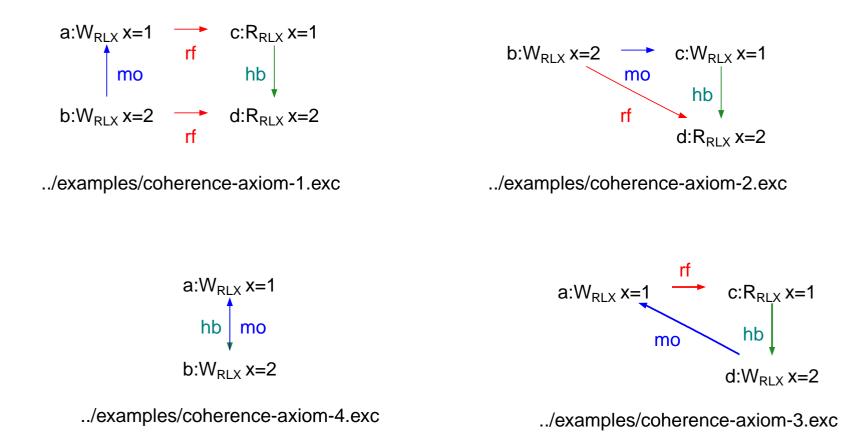

### Coherence

Coherence is defined an absence of four execution fragments:

Concurrency examples that can be observed

The model allows the following non-SC behaviour:

- message passing (RLX, REL-CON)

- store buffering (REL-ACQ, RLX, REL-CON)

- Joad buffering (RLX, CON)

- write-to-read causality (RLX, CON)

- IRIW (REL-ACQ, RLX, REL-CON)

...but DRF programs that use only the memory\_order\_seq\_cst atomics should be sequentially consistent

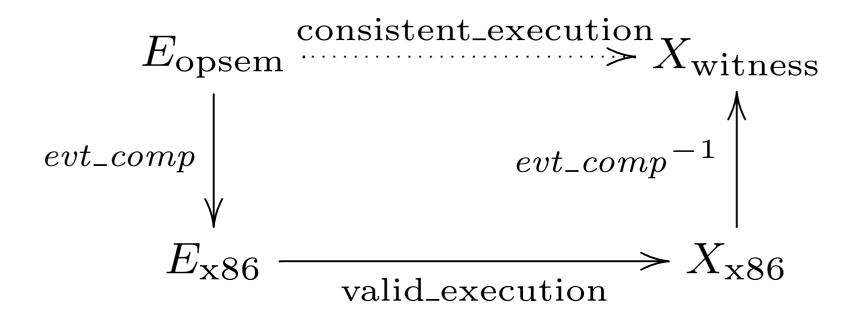

# An execution compiler

| Operation     | x86 Implementation |                  |

|---------------|--------------------|------------------|

| Load non-SC   | mov                |                  |

| Load Seq_cst  | lock xadd(0)       | OR: mfence, mov  |

| Store non-SC  | mov                |                  |

| Store Seq_cst | lock xchg          | OR: mov , mfence |

| Fence non-SC  | no-op              |                  |

| Fence Seq_cst | mfence             |                  |

#### Theorem

# Conclusion

C++0x offers a simple model to normal programmers while experts get a highly configurable language that abstracts the hardware memory model

we have arrived just in time to point out a few bugs, and many changes have been made as a result of our work

the intricacy of such models makes tools important, CPPMEM helps in exploring and understanding the model

formal models provide an opportunity to provide guarantees about programs based on the specification, like our compiler correctness result