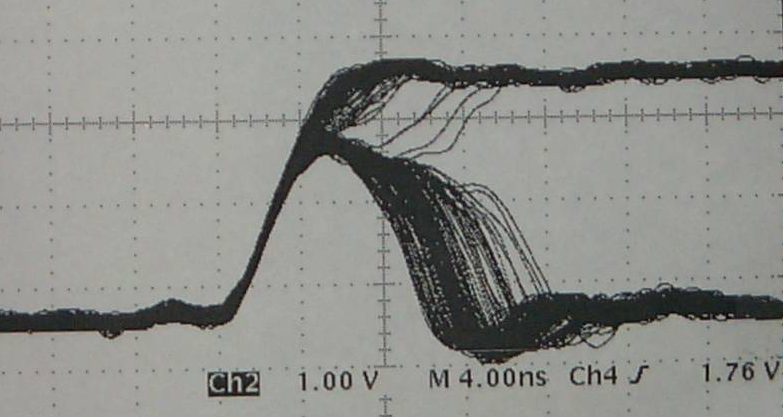

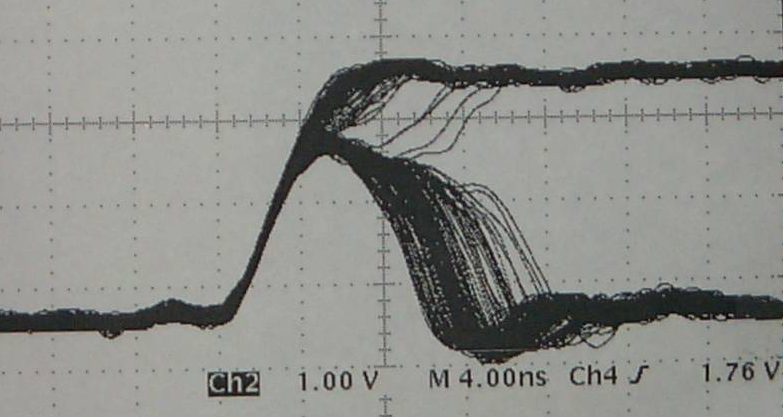

Metastable waveforms at the output of a D-type when set/hold times are sometimes violated.

A clock crossing bridge is like a bus bridge, but has different clock domains on each side.

A simplex clock domain crossing bridge carries information in only one direction. Duplex carries in both directions.

These are commonly needed when connecting to I/O devices that operate at independent speeds: for example, an Ethernet receiver sub-circuit works at the exact rate of the remote transmitter that is sending to it. Today's microprocessors also have separated clock domains for their cores viz their DRAM interfaces.

Basic idea:

The data signals can also suffer from metastability, but the multiplexer ensures that these metastable values never propagate into the main logic of the receiving domain.

Simplex: can never be sure about the precise delay.

We need a protocol with insertable/deletable padding symbols that have no semantic meaning. Or at a higher level, the protocol must have elidable idle states between transactions.

100 percent utilisation is impossible when crossing clock domains. The four-phase handshake limits utilisation to 50 percent (or 25 if registered at both sides) Other protocols can get arbitarily close to saturating one side or the other provided we know the maximum tolerance in the nominal clock rates.

Duplex: cannot reply on any precise timing relationship between the two directions. The protocol must rely on sequencing or expicit transaction tokens. In other words, we need a lot of temporal decoupling of requests and acks for crossing clock domains (and also network on chip later) (NB: This is not the same as the temporal decoupling in ESL modelling).